Устройство для преобразования массивов двоичных чисел в интервале значений 2, 2 -1

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1829073

Автор: Наумов

Текст

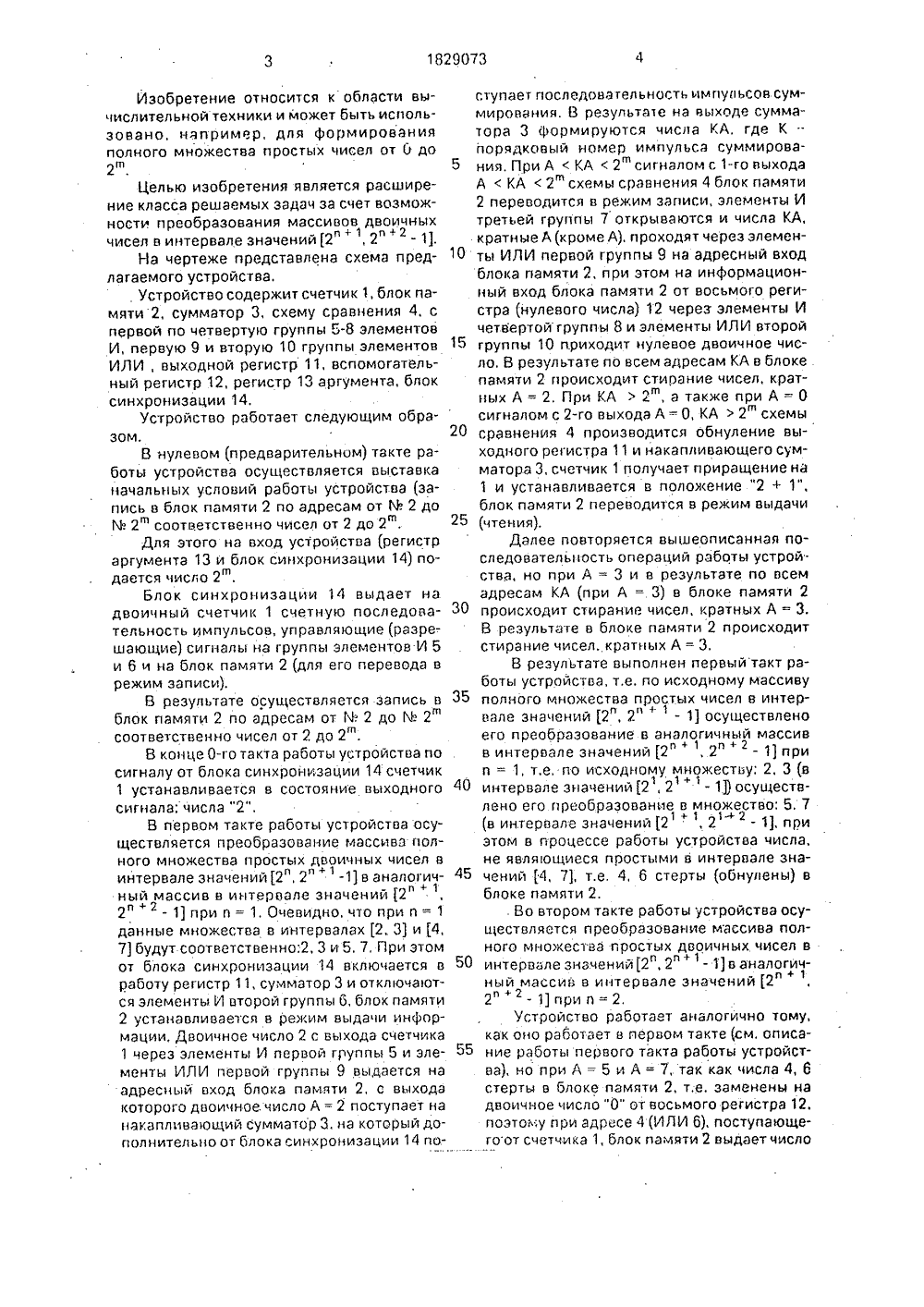

ОЮЭ СОВЕТСКИХОциАлистиче скихЕСПУБЛИК 1829073 А 1 юцз НОЗМ 7 ОПИСАНИЕ ИЗОБРЕТ 2 рукторское бюро) УС ИЯ М НТЕР ГОСУДАРСТВЕННОЕ ПАТЕНТНВЕДОМСТВО СССР(54 ТРОЙСТВО ДЛН АССИВОВ .ДВОИ ВАЛЕ ЗНАЧЕН ьство СССР /556, 1982, ьство СССР /556, 1982. Я ПРЕОБРАЗОВАИЧНЫХ ЧИСЕЛ В ИИ Рд,2 д 1-1)2 г(57) Устройство относится к вычислительной технике и может быть использовано, например, для формирования полного множества простых чисел от 0 до 2, Цель изобрете. ния - расширение класса решаемых задач зэ счет возможности преобразования мас; сивов двоичных чисел в интервале значений 2" + , 2" -1, Поставленная цель достигается благодаря введению в устройство, содержащее три регистра 11-13, блок памяти 2, сумматор 3 и блок синхронизации 14, счетчика 1, двух групп 9, 10, элементов ИЛИ, четырех групп 5-8, элементов И и схемы сравнения 4, 1 илИзобретение относится к области вычислительной техники и может быть использовано, например, для формированияполного множества простых чисел от 0 до2. 5Целью изобретения является расширение класса решаемых задач за счет возможности преобразования массивов двоичныхчисел в интервале значений 2, 2 - 1),и+1 и+2На чертеже представлена схема предлагаемого устройства.Устройство содержит счетчик 1, блок памяти 2, сумматор 3, схему сравнения 4. спервой по четвертую группы 5-8 элементовИ, первую 9 и вторую 10 группы элементов 15ИЛИ, выходной регистр 11, вспомогательный регистр 12, регистр 13 аргумента, блоксинхронизации 14,Устройство работает следующим образом. 20В нулевом (предварительном) такте работы устройства осуществляется выставканачальных условий работы устройства (запись в блок памяти 2 по адресам от М 2 доМ. 2 соответственно чисел от 2 до 2 и, 25Для этого на вход устройства (регистраргумента 13 и блок синхронизации 14) подается число 2 п,Блок синхронизации 14 выдает надвоичный счетчик 1 счетную последовательность импульсов, управляющие (разре-.шающие) сигналы на группы элементов И 5и 6 и на блок памяти 2 (для его перевода врежим записи).В результате осуществляется запись в 35блок памяти 2 по адресам от 1 Ф 2 до К. 2"соответственно чисел от 2 до 2.В конце 0-го такта работы устройства посигналу от блока синхронизации 14 счетчик1 устанавливается в состояние выходного 40сигнала: числа "2",В первом такте работы устройства осуществляется преобразование массива полного множества простых двоичных чисел винтервале значений 2", 2" -1) в аналогичи+1ный массив н интервале значений 2"2 - 1) при и = 1. Очевидно, что при и = 1п+2данные множества в интервалах 23) и 4,7) будут соответственно:2, 3 и 5, 7, При этомот блока синхронизации 14 включается в 50работу регистр 11, сумматор 3 и отключаются элементы И второй группы б, блок памяти2 устанавливается в режим выдачи информации, Двоичное число 2 с выхода счетчика1 через элементы И первой группы 5 и элементы ИЛИ первой группы 9 выдается наадресный вход блока памяти 2, с выходакоторого двоичное. число А = 2 поступает нанакапливающий сумматор 3, на который дополнительно от блока синхронизации 14 поступает последовательность импульсов суммирования, В результа 1 е на выходе сумматора 3 формируются числа КА. где К " порядковый номер импульса суммирования, При АКА2" сигналом с 1-го выхода АКА2" схемы сравнения 4 блок памяти 2 переводится в режим записи, элементы И третьей группы 7 открываются и числа КА, кратные А (кроме А), проходят через элементы ИЛИ первой группы 9 на адресный вход блока памяти 2, при этом на информационный вход блока памяти 2 от восьмого регистра (нулевого числа) 12 через элементы И четвертойгруппы 8 и элементы ИЛИ второй группы 10 приходит нулевое двоичное число. В результате по всем адресам КА в блоке памяти 2 происходит стирание чисел, кратных А=2, При КА 2,атакже при А=О сигналом с 2-го выхода А = О, КР2 схемы сравнения 4 производится обнуление выходного регистра 11 и накапливающего сумматора 3, счетчик 1 получает приращение на 1 и устанавливается в положение "2 + 1", блок памяти 2 переводится в режим выдачи (чтения).Далее повторяется вышеописанная последовательность операций работы устрой" ства, но при А = 3 и в результате по всем адресам КА (при А = 3) в блоке памяти 2 происходит стирание чисел, кратных А = 3. В результате в блоке памяти 2 происходит стирание чисел, кратных А = 3,В результате выполнен первый такт работы устройства, т,е. по исходному массиву полного множества простых чисел в интервале значений 2", 2 п - 1) осуществлено его преобразование в аналогичный массив в интервале значений 2" , 2" - 1) при и = 1, т.е. по исходному множеству; 2. 3 (в интервале значений 2, 2- 1 осуществ 1 1+1лено его преобразование в множество: 5, 7 (в интервале значений 2 , 2 - 1), при этом в процессе работы устройства числа, не являющиеся простыми в интервале значений 4, 7), т.е. 4, б стерты (обнулены) в блоке памяти 2.Во втором такте работы устройства осуществляется преобразование массива полного множества простых двоичных чисел в интервале значений 2, 2 - Ц в аналогичи и+1ный массив в интервале значений 2"и+1 2" -1) при п=2,Устройство работает аналогично тому, как оно работает в первом такте (см, описание работы первого такта работы устройства), но при А =. 5 и А = 7, так как числа 4, 6 стерты в блоке памяти 2, т,е. заменены на двоичное число "0" от восьмого регистра 12, поэтому при адресе 4 (ИЛИ б), поступающего от счетчика 1, блок памяти 2 выдает число1029073 Составитель Д,НаумовТехред М.Моргентал . Корректор М.Петрова Редактор Т.Иванова Заказ 2477 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101 А = 0 и счетчик 1 сигналол 1 со 2-го выхода А = О, КА2 блока сравнения 4 сразу переводится на число 5 (или 7). В блоке памяти 2 происходит стирание чисел, кратных 5 и 7,В результате выполнен второй такт работы устройства, т.е. по исходному массиву полного множества простых чисел в интервале значений 2", 2" - 11 осуществлено его преобразование в аналогичный массиви+1 п 4 2 в интервале значений 2, 2 - 11 при и = 2, т,е. по исходному множеству 5, 7 (в интервале значений 2, 2 - 1) осуществ 2 21лена его преобразование в множество 11, 13 (в интервале значений 2, 2 - 1) -2+1 2 2 при этом в процессе работы устройства во время первого и второго тактов работы числа. не являющиеся простыми в интервале значений 8, 15), т.е. 8, 9. 10, 12. 14, 15, стерты (обнулены) в блоке памяти 2,Далее процесс работы устройства продолжается аналогично первым двум тактам, но при и = 3, и .=- 4, т.д. соответственно при других больших) значениях чисел А. При А2 процесс работы устройства заканщчивается сигналом с 3-го выхода А2 блока сравнения 4 (при этом обнуляется входной счетчик 1 и блок синхронизации 14).При этом в блоке памяти 2 сформировано полное множество простых чисел в заданном интервале значений от 0 до 2",Формула изобрет ения Устройство для преобразования массивов двоичных чисел в интервале значений 2", 2" -1), содержащее регистр аргумента, выходной регистр, блок памяти, вспомогательный регистр, сумматор и блок синхронизаций, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач путем преобразования массивов двоичных чисел в интервале значений 2"2" - 11, в него введены счетчик, первая и вторая группы элементов ИЛИ, с первой по 5 10 15 20 25 30 35 40 четвертую группы элементов И и схема сравнения. причем выходы счетчика гоединены с информационными входяли элементов И первой и второй групп, управляющие входы и выходы элементов И ко 1 орых подключены к тактовому входу блока синхронизации и первым входам элементов ИЛИ первой и второй групп соответственно, вторые входы элементов ИЛИ которых соединены с выходами элемен гон ИЛИ соответственно третьей и четвертой групп, а выходы - соответственно с адресным и информационным входами блока памяти, вход записи которого объединен с вторыми входами элементов И третьей и четвертой групп и подключен к выходу АКА2 схемы сравнения (где А = 2 - выходное число блока памяти, К = 1, 2, Зп 1 - степень числа), выход К А2.(или А =, О); которой соединен с входами установки нуля сумматора, выходного регистра, входом чтения блока памяти, счетным входом счетчика и входом останова блока синхронизации, тактовый вход которого объединен с входом начальной установки счетчика и подключен к выходу А2" - 1 схемы сравнения, первый вход которой объединен с информационным входом сумл 1 атора и подключен к выходу выходного регистра, выход сумматора соединен с вторыми входами элементов И третьей группы и с вторым входом схемы сравнения, третий вход которой подключен к выходу регистра аргумента, вход которого подключен к входу запуска блока синхронизации и информационному входу устройства, выход регистра соединен свторыми входами элементов И четвертой группы, тактовый выход блока синхронизации подключен к входам синхронизации счетчика. блока памяти, сумматора и выходного регистра, выход блока памяти соединен с входом выходного регистра, выход которого является выходом устройства.

СмотретьЗаявка

4861552, 20.08.1990

ЦЕНТРАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО "АЛМАЗ"

НАУМОВ ДМИТРИЙ СТЕПАНОВИЧ

МПК / Метки

МПК: H03M 7/12

Метки: двоичных, значений, интервале, массивов, преобразования, чисел

Опубликовано: 23.07.1993

Код ссылки

<a href="https://patents.su/3-1829073-ustrojjstvo-dlya-preobrazovaniya-massivov-dvoichnykh-chisel-v-intervale-znachenijj-2-2-1.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для преобразования массивов двоичных чисел в интервале значений 2, 2 -1</a>

Предыдущий патент: Способ изготовления углеграфитовых щеток

Следующий патент: Комплектное распределительное устройство

Случайный патент: Устройство для испытания каната на износ