Устройство для суммирования-вычитания чисел с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

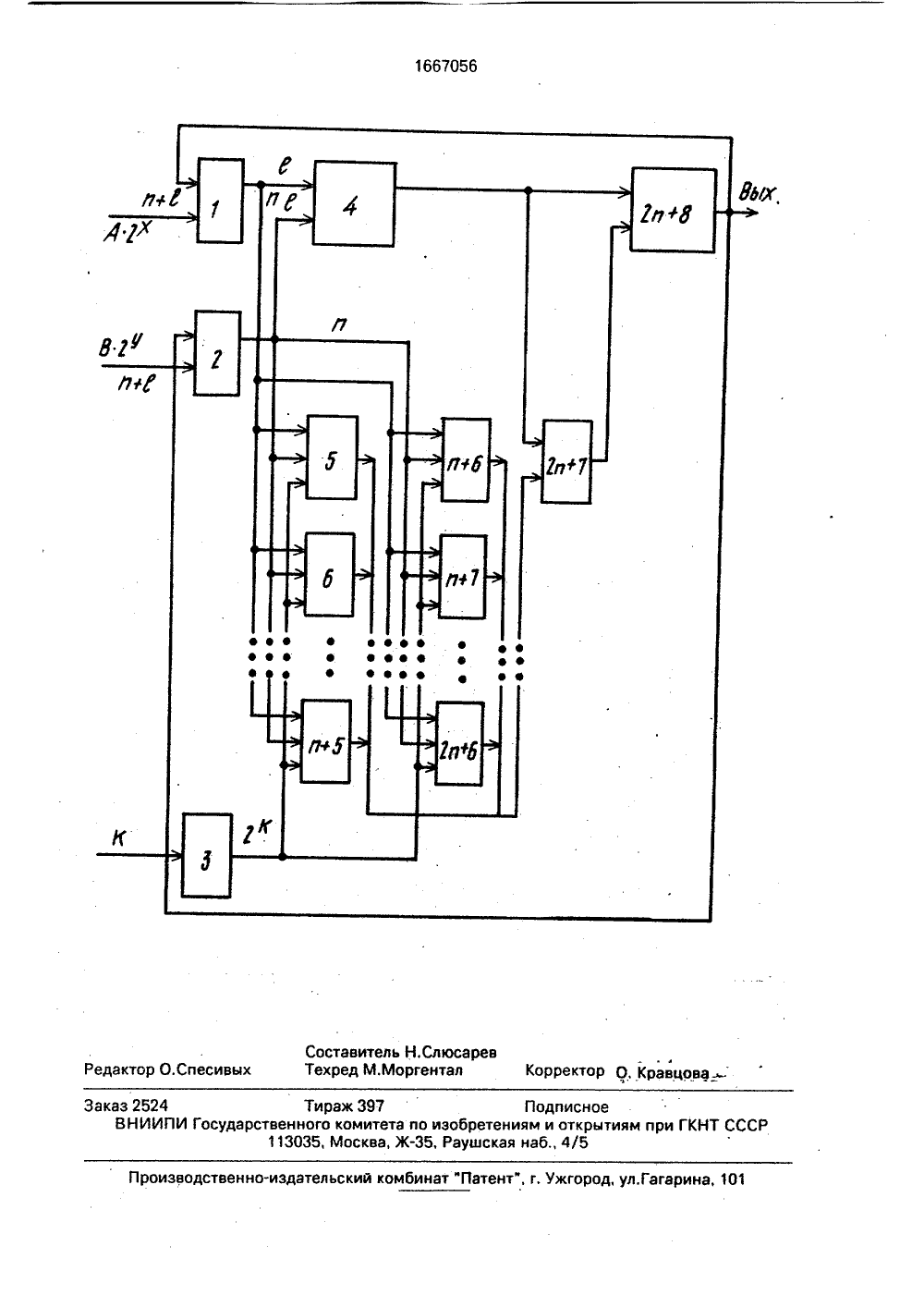

"с НИЕ ИЗОБРЕТЕН О и ско тура М и 01. ГОСУДАРСТВЕННЫЙ КОМИПО ИЗОБРЕТЕНИЯМ И ОТКПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Одесский политехнический инстиСпециальное проектно-конструкторбюро "Дискрет"(56) Малиновский Б.Н. Справочник поровой вычислительной технике, Киев:ника, 1974, с. 16.Самофалов К.Г., Луцкий Г.М. Струки организация функционирования ЭВсистем. Киев: Вища школа, 1978, с. 100 Авторское свидетельство СССРМ 1348825, кл. 6 06 Р 7/50, 1986,Изобретение относится к области вычислительной техники и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой,Цель изобретения - повышение быстройствия и расширение области примене На чертеже изображена структурная хема предложенного устройства.Устройство для суммирования/вычитаия чисел с плавающей запятой содержит регистры 1 и 2 первых и вторых слагаемых оответственно, двоичный дешифратор 3, лок 4 сравнения порядков, (2 п+ 2), где и - азрядность мантисс операндов, блоков потоянных запоминающих устройств с номеами 5, 6, , 2 п + 6, блок коммутаторов 2 п + , блок нормализации 2 п+ 8.(57) Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах машин с плавающей точкой, Целью изобретения является повышение быстродействия и расширение функций устройства. С этой целью в устройство, содержащее регистры первого и второго слагаемых, блок сравнения порядков, блок коммутаторов, блок нормализации, введены двоичный дешифратор и.2 п+2 блоков постоянных запоминающих устройств (и - разрядность мантисс слагаемых). 1 ил. Выходы разрядов порядков регистров 1 и 2 соединены с разрядами соответствующих входов блока 4, выход блока 4 соединен с управляющим входом блока 2 п+ 7, выходы разрядов блока 2 п + 7 соединены с входами разрядов мантиссы блока 2 п+ 8, а его входы разрядов порядка соединены с выходом блока 4, выходы разрядов блока 2 п + 8 соединены с выходом устройства и с разрядами первых входов регистров 1 и 2, вторые входы которых соединены со входами слагаемых устройства, первые адресные входы блоков 5, 6, , 2 п + б соединены с соответствующими разрядами выхода мантиссы регистра 1, вторые адресные входы блоков 5, 6, , 2 п+ 6 соединены с соответствующими разрядами выхода мантиссы регистра 2, третьи адресные входы блоков 5, 6, , 2 п+ 6 соединены с соответствующими выходами блока 3, входы которого соединены с соответствующими управляющими входами устройства, информационные входы блока 2 п+7 подключены к выходам блоков 5, 6, , 2 п+ 6.Устройство работает следующим образом.С выхода разрядов порядка регистров 1и 2 порядки первого и второго слагаемыхпоступают в блок 4. Из разрядов мантиссывыхода регистра 1 мантисса А поступает напервые адресные входы блоков 5, 6, , 2 п +6, Аналогично из разрядов мантиссы выхода; регистра 2 мантисса В поступает на вторыеадресные входы блоков 5, 6, , 2 п+ 6, при чем в блоках 5, 6, ., п+ 5 формируются (и +1) 2 п - разрядные предварительные суммы31, 32,Яп+1 при условии, что мантисса Востается неподвижной, а мантисса А последовательно сдвигается на О, 1, 2; , и разря дов, в блоках и + 6, ., 2 п + 6 формируются,(и+ 1) 2 п - разрядные предварительные счммы Яп+2, Яп+3, , Я 2 п+2 при условии, что, мантисса А остается неподвижной, а ман, тисса В последовательно сдвигается на О, 1,, блоке 3 и поступает на третьи адресные, входы блоков 5, 62 п + 6, В результатеэтого на выходах заранее запрогрэммиро, ванных блоков 5, 6, , 2 п + 6 формируютсяпредварительные суммы 31, 32, , оп + 2,. которые обхразчют все возможные разности, В,2 - А.2, либо А.2 - В,2, либо суммых, УА,2" +В,2" в прямом,дополнительномилиобратном коде, как при Х 4 У, так и приХ У(вид операции и код чисел задаютсякомбинацией соответствующих логиче ских значений сигналов, поданных на управляющие входы устройства),2 п+ 2 предварительные суммы поступа, ют на информационные входы блока(2 п+7)коммутаторов.В блоке 4 сравниваются порядки Х и Уи сохраняется больший из них, Определяется также разность порядков. которая сохраняется в качестве критерия выборанеобходимой предварительной суммы,Прямое и инверсное значение знака имодуль выравнивающей разности порядковпоступают на управляющий вход блока 2 п+7, В блоке 2 п+ 7 происходит вь 1 бор нужнойпредварительной суммы следующим образом: при Х)У выбирается результат из сформированных предварительных сумм, гдемантисса В сдвигается относительно мантиссы А, при ХУ выбирается результат из5 10 15 20 25 30 35 40 45 50 55 сформированных предварительных сумм, где мантисса А сдвигается относительно мантиссы В. Конкретный результат выбора зависит от величины модуля выравнивающей разности, показывающей на сколько разрядов одна мантисса сдвинута относительно другой, Выбранная предварительная сумма мантисс с выхода блока 2 п + 7 поступает на входы разрядов мантиссы блока 2 п + 8, больший порядок поступает на входы разрядов порядка блока 2 п + 8. В блоке 2 п + 8 происходит нормализация результата суммирования.Нормализованный результат передается на выход устройства.Формула изобретения Устройство для суммирования - вычитания чисел с плавающей запятой, содержащее регистры первого и второго слагаемых, блок сравнения порядков, блок коммутаторов, блок нормализации, причем выходь 1 разрядов первого и второго регистров соединены с разрядами соответствующих входов блока сравнения порядков, выход блока сравнения порядков соединены с управляющим входом блока коммутаторов, выходы разрядов блока коммутаторов соединены с входами разрядов мантиссы блока нормализации, входы разрядов порядка которого соединены с выходом блока сравнения порядков, выходы разрядов блока нормализации соединены с выходом устройства и с разрядами первых входов регистров первого и второго слагаемых, вторые входы которых соединены с входами слагаемых устройства, отл ича ю щееся тем, что, с целью повышения быстродействия и расширения функций, в него введены двоичный дешифратор и 2 п + 2 блока постоянных запоминающих устройств(где и - разрядность мантисс слагаемых), причем первые адресные входы каждого блока постоянного запоминающего устройства соединены с соответствующими разрядами выхода мантиссы регистра первого слагаемого, вторые адресные входы - с соответствующими разрядами выхода мантиссы регистра второго слагаемого, третьи адресные входы - соответственно с выходами двоичного дешифратора, входы которого соединены с соответствующими управляющими входами устройства, информационные входы блока коммутаторов подключены к выходам соответствующих блоков постоянных запоминающих устройств.. Кравцова рре Производственн аказ 2524 ВНИИП Тираж 397 ПодписноеГосударственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5 дательский комбинат "Патент", г, Ужгород, ул,Гагарина, 1

СмотретьЗаявка

4735415, 14.07.1989

ОДЕССКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ, СПЕЦИАЛЬНОЕ ПРОЕКТНО-КОНСТРУКТОРСКОЕ БЮРО "ДИСКРЕТ"

ПАУЛИН ОЛЕГ НИКОЛАЕВИЧ, СИНЕГУБ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: запятой, плавающей, суммирования-вычитания, чисел

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/3-1667056-ustrojjstvo-dlya-summirovaniya-vychitaniya-chisel-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования-вычитания чисел с плавающей запятой</a>

Предыдущий патент: Устройство для умножения чисел по модулю

Следующий патент: Устройство для деления

Случайный патент: Способ определения расстояния до места обрыва фазы в воздушных трехфазных электрических сетях с изолированной нейтралью