Устройство вычисления функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

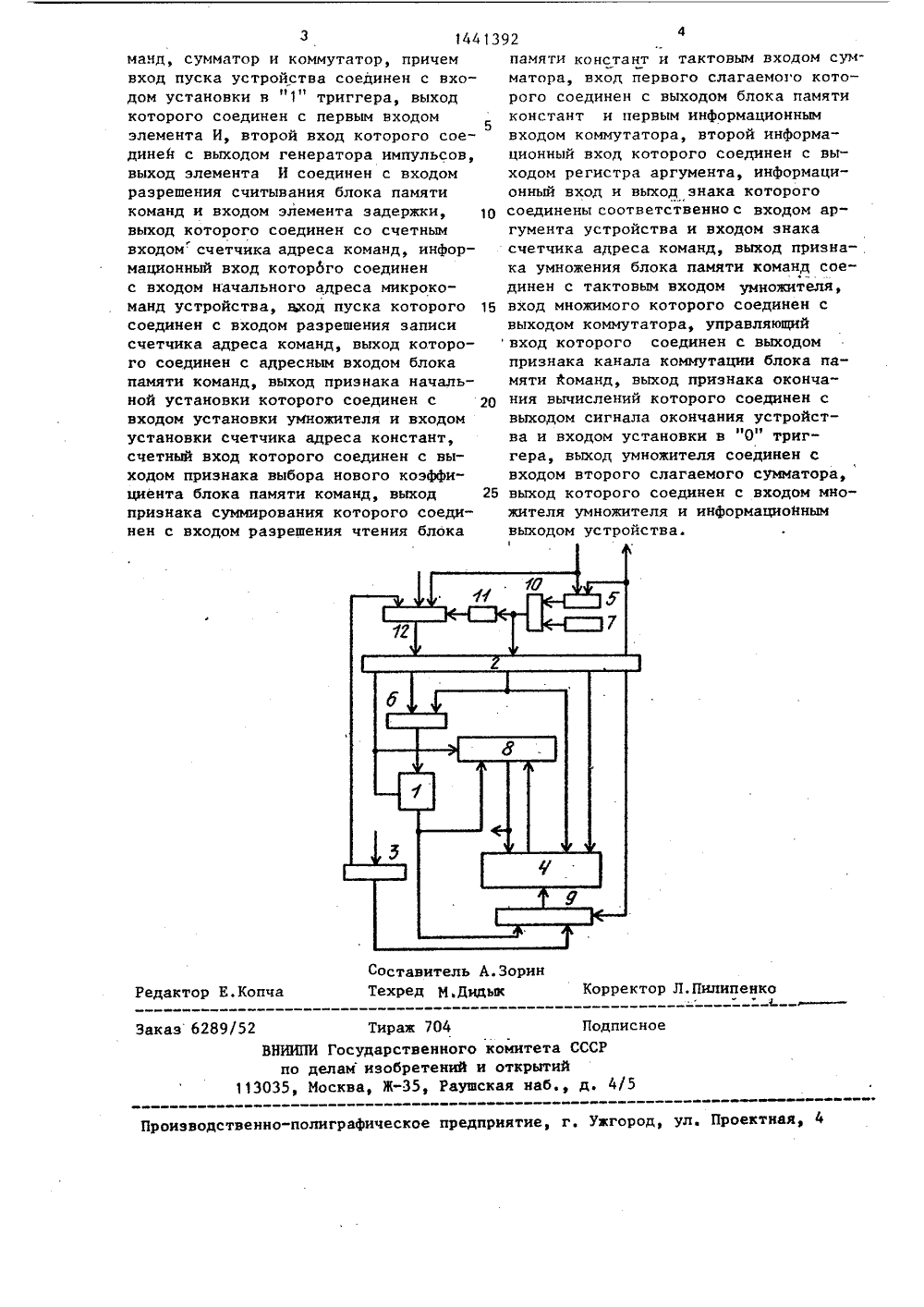

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 19) (11) 6 Г 7 548 ИЙ НИЯ ВТОРС ОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ ОПИСАНИЕ ИЗО У СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССУ 1260946, кл, С 06 Р 7/548, 198Авторское свидетельство СССРВ 1257639, кл. С 06 Р 7/548, 198 УСТРОЙСТВО ВЫЧИСЛЕНИЯ ФУ у-:(57) Устройство вычислени у = е может быть использова специальных цифровых устройс фиксированной запятой. Целью ретения является расширение применения устройства за сче чения диапазона изменения ар За счет введения в известное ство сумматора, мультиплексо мента И, линии задержки, сче адресов команд область приме устройства расширена в два р чем значения аргумента ле)кат зоне хс 1. 1 ил,но в твах с изобобласти т увелигумента. устройра, злетчика нения аеа, прив диапаИзобретение относится к вычислительной технике и может быть использовано в специальных цифровых устройствах с фиксированной запятой.Целью изобретения является расширение области применения устройстваза счет увеличения диапазона изменения аргумента.На чертеже изображена блок-схемаустройства.Устройство содержит блок 1 памятиконстант, блок 2 памяти команд, регистр 3 аргумента, умножитель 4,триггер 5, счетчик 6 адреса констант, 15генератор 7 импульсов, сумматор 8,коммутатор 9, элемент И 10, элемент1 1 задержки, счетчик 12 адреса ко.манд,Работа предлагаемого устройства 20основана на использовании алгоритмаприближенного вычисления функции епутем разложейия в ряд в диапазонех ( 1, Разложение реализуется посхеме Горнера. 25Аргумент функции х в устройствепредставлен в дополнительном коде ввиде0 х,п при х О1 х при х "- О, 301 х, если х ъ 0;где х,=11 фф 1+х, если х ( О,е ", если хО,откуда е = ц .,е е, если х с.О.35Устройство работает следующим образом.В исходном положении на вход регистра 3 аргумента подано значениеаргумента,в блоке 1 памяти константразмещены соответствующим образомкоэффициенты разложения, в блоке 2 па"мяти команд записаны .соответствующиемикрокоманды, триггер 5 находится внулевом состоянии. Управляющий сиг 45нал пуска устройства переводит триггер 5 в единичное состояние, сигналс выхода которого разрешает прохождение серии сигналов с генератора 7 импульсов через элемент И 10. Кроме того, по сигналу пуска устройства насчетчик 12 адреса команд заноситсяначальный адрес микропрограммы работы устройства.По сигналу с выхода элемента И 10на соответствующих выходах блока 255Формируются сигналы управления работыустройства. Последовательность сигналов в одном цикле следующая. Первым Формируется сигнал на выходе признака начальной установки, затем признака суммирования, далее признака выбора нового коэффициента и М раз на выходе признака умножения, где М - разрядность. Указанных циклов формируется К - по количеству членов разложения. Кроме того, при отрицательном аргументе дополнительно в последнем цикле одновременно с сигналом признака выбора нового коэффициента формируется признак канала коммутации. После выдачи последнего признака суммирования формируется сигнал признака окончания.Работа устройства для положительного аргумента функции происходит следующим образом.По сигналу с выхода признака суммирования блока 2 памяти команд производится считывание соответствующих констант из блока 1 памяти констант и сложение их на сумматоре 8 с результатом умножителя 4. По сигналу с выхода признака нового коэффициента на счетчике 6 адреса констант формируется новый адрес блока 1 памяти констант. По сигналам с выхода признака умножения блока 2 памяти команд на тактовомвходе умножителя формируется серия из тактовых сигналов, под действием которых в умножителе 4 формируется произведение содержимого сумматора 8 с аргументом, если на выходе признака канала коммутации блока 2 памяти команд сигнал отсутствует, или с константой е-ф в противном случае.По сигналу с выхода признака окончания блока 2 памяти команд триггер 5 устанавливается в исходное состояние и вырабатывается сигнал конца работы устройства.Формула изобретенияУстройство вычисления функции уе", содержащее триггер, генератор импульсов, блок памяти команд,вйсчетчик адреса коистант, блока памяти констант, регистр аргумента и умножитель, причем выход счетчика адреса констант соединен с адресным входом блока памяти констант, о т л ич а ю щ е е с я тем, что, с целью расширения области применения эа счет увеличения диапазона изменения аргумента, в него введены элемент И элемент задержки,счетчик адреса ко"Составитель А.ЗориТехред М.Дидык дактор Е.Копча рректор Л.Пилипенко Тираж 704 По ВНИИПИ Государственного комитета ССС по деламизобретений и открытий 113035, Москва, Ж, Раушская наб., д.аз 6289/52 исное прияти графическо зводственн 3 14413 манд, сумматор и коммутатор, причем вход пуска устройства соединен с входом установки в "1" триггера, выход которого соединен с первым входом5 элемента И, второй вход которого соединей с выходом генератора импульсов, выход элемента И соединен с входом разрешения считывания блока памяти команд и входом элемента задержки, 1 О выход которого соединен со счетным входом счетчика адреса команд, информационный вход которбго соединен с входом начального адреса микрокоманд устройства, щсод пуска которого 15 соединен с входом разрешения записи счетчика адреса команд, выход которого соединен с адресным входом блока памяти команд, выход признака начальной установки которого соединен с 2 О входом установки умножителя и входом установки счетчика адреса констант, счетный вход которого соединен с выходом признака выбора нового коэффициента блока памяти команд, выход 25 признака суммирования которого соединен с входом разрешения чтения блока 92 памяти констант и тактовым входом сумматора, вход первого слагаемого которого соединен с выходом блока памяти констант и первым информационным входом коммутатора, второй информационный вход которого соединен с выходом регистра аргумента, информационный вход и выход знака которого соединены соответственно с входом аргумента устройства и входом знака счетчика адреса команд, выход признака умножения блока памяти команд соединен с тактовым входом умножителя, вход множимого которого соединен с выходом коммутатора, управляющий вход которого соединен с выходом признака канала коммутации блока памяти команд, выход признака окончания вычислений которого соединен с выходом сигнала окончания устройства и входом установки в "О" триггера, выход умножителя соединен с входом второго слагаемого сумматора, выход которого соединен с входом множителя умножителя и информациойным выходом устройства. 1 жгород, ул. Проектная,

СмотретьЗаявка

4264063, 16.06.1987

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

ГАЛАБУРДА ИЛЬЯ ПЕТРОВИЧ, ИЛЬИН ПЕТР ВИКТОРОВИЧ

МПК / Метки

МПК: G06F 7/548

Метки: вычисления, функции

Опубликовано: 30.11.1988

Код ссылки

<a href="https://patents.su/3-1441392-ustrojjstvo-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство вычисления функции</a>

Предыдущий патент: Устройство для формирования периодических функций

Следующий патент: Устройство для возведения в квадрат -разрядных двоичных чисел

Случайный патент: Центробежно-дроссельный датчик давления