Устройство для обнаружения ошибок при передаче кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1403066

Авторы: Мартиросян, Свистельников

Текст

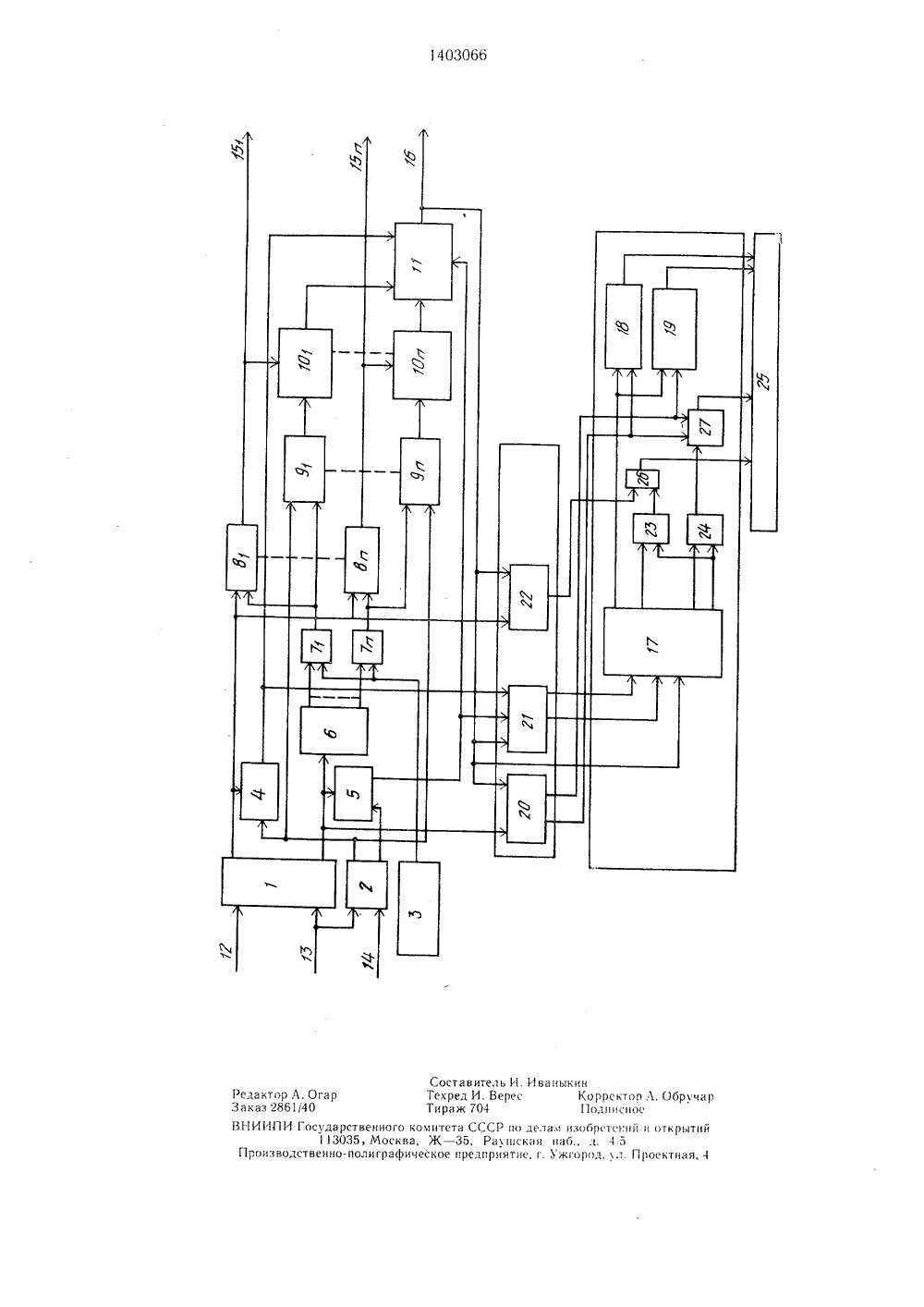

ОЮЗ СОВЕТСКИХОЦИАЛИСТИЧЕСКИЕСПУБЛИК 1403 14 6 06 Г 11/ г АН ТЕ ОРСНОМУ С ТЕЛЬСТВУ СО ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) (57) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК ПРИ ПЕРЕДАЧЕКОДОВ по авт св1091211 отличающееся тем, что, с целью повышенияинформативности контроля, в него введены блок индикации, второй, третий и четвертый дешифраторы, первый, второй и третий регистры, первый и второй блоки элементов И, (и+1)-й и (п+2)-й элементыИЛИ, причем входы разрешения записи первого, второго и третьего регистров и управляющий вход второго дешифратора объединены и подключены к выходу блока формирования сигнала ошибки, информационные входы первого и второго регистровсоединены соответственно с первым и вторымвыходами входного регистра, информационные входы третьего регистра соединены с выходами первого и второго блоков контроля по модулю два, выходы третьего регистра соединены с информационными входами второго дешифратора, первый выход которого соединен с управляющими входами третьего и четвертого дешифраторов, выходы которых соединены с первым и вторым входами блока индикации, третий и четвертый входы которого соединены с выходами соответственно первого и второго блоков элементов И, первая и вторая группы разрядных выходов второго регистра соединены с информационными входами третьего и четвертого дешифраторов соответственно и с первым входом первого блока элементов И, второй вход которого подключен к выходу (и+ 1)-го элемента ИЛИ, первый вход которого соединен с пер- Ж вым входом (п+2) -го элемента ИЛИ и с вторым выходом второго дешвфрвторв, тре. Щ тий и четвертый выходы которого соединены с вторыми входами (п+1) -го и (и+2) -го Ъэлементов ИЛИ соответственно, разрядные выходы первого регистра соединены с первым входом второго блока элементов И, второй вход которого подключен к выхо- ы ду (и+2)-го элемента ИЛИ.1Изобретение относится к вычислительной технике, может быть использовано в устройствах автоматизированного контроля узлов передачи информации и является усовершенствованием изобретения по авт. св. Мо 109121. 5Цель изобретения - повышение информативности контроля.На чертеже представлена структурная схема устройства для обнаружения ошибок при передаче кодов. ОУстройство содержит входной регистр 1, регистр 2 контрольных разрядов, блок 3 управления параллельной записью, блоки 4 и 5 контроля по модулю два, дешифратор 6, элементы ИЛИ 7. - 7.п, входные регистры 8.1 - 8.п, триггеры 9. - 9.п, блоки 10.1 - 10.п контроля на четность, блок1 формирования сигнала ошибки, информационный вход 12, стробирующий вход 13, вход 4 контрольных разрядов, информационные выходы 5. - 15.п, выход 16 сигнала ошибки, дешифраторы 17 - 9, регистры 20 - 22,20 элементы ИЛИ 23 и 24, блок 25 индикации и блоки 26 и 27 элементов И. Устройство работает следукнцнм образом.Информация, поступающая на входной 25 регистр 1 с входа 12 информации, и контрольные разряды, поступающие на регистр 2 контрольных разрядов с входа 13 контрольных разрядов, записываются в регистры 1 и 2 по стробу, поступающему со стробирующего входа 13. Информация по байтно контролируется в блоках 4 и 5 контроля по модулю два. Результат контроля с выходов блоков 4 и 5 посту пает на входы регистра 21 и блока 11 фор мирования сигнала ошибки, выход которого является выходом 6 сигнала ошибки уст 2ройства. Первый байт информации переписывается в выходной регистр 8, а соответствующий ему контрольный разряд - в триггер 9 по сигналу, поступающему через элемент ИЛИ 7 с выхода дешифратора 6, на вход которого поступает второй байт информации. В устройстве предусмотрена параллельная запись первого байта информации и его контрольного разряда во все регистры 8 и триггеры 9 по сигналу с блока 3 управления параллельной записью. Информация на выходах регистров 8 контролируется в блоках 10 контроля на четность. Результат контроля с выходов блоков 10 поступает на входы блока 11 формирования сигнала ошибки.Если устройством обнаружена ошибка, то блок 11 формирования сигнала ошибки формирует сигнал, который записывает первый и второй байты информации и результат их контроля блоками 4 и 5 в первый, второй и третий регистры соответственно и стробирует дешифратор 17.Если ошибка обнаружена блоком 4 контроля по модулю два, или блоком 5 контроля по модулю два, или блоками 4 и 5 одновременно, то дешифратор 17 формирует на своем выходе сигналы, разрешающие прохождение на блок 25 индикации первого байта, или второго байта, или одновременно первого и второго байтов информации соответственно.Если ошибка обнаружена блоком 10 контроля на четность, то дешифратор 17 формирует на своем выходе сигнал, который стробирует дешифраторы 18 и 19. С выходов дешифраторов 18 и 19 информация о номере платы и номере регистра в плате, в которых произошел отказ, поступает на блок 25 индикации.гя и тета Ж - -3 еское и Релактор Л. Огар3 а к аз 286140ВНИИПИ Государственного3035, МосквГ 1 роизводственно-полиграфи Составитель Р. ИваныкинТехред И. Верес Кор 1)сктор Л. Обручар Тираж 704 11 олниснос СССР по ледам изцорстский и открытийРаугиская наб., л. 4 5елириятис, г. Ужгород,и Проектная, 4

СмотретьЗаявка

3904249, 03.06.1985

ПРЕДПРИЯТИЕ ПЯ А-7240

МАРТИРОСЯН СЕРГЕЙ ЛЕВОНОВИЧ, СВИСТЕЛЬНИКОВ ЮРИЙ АНТОНОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: кодов, обнаружения, ошибок, передаче

Опубликовано: 15.06.1988

Код ссылки

<a href="https://patents.su/3-1403066-ustrojjstvo-dlya-obnaruzheniya-oshibok-pri-peredache-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок при передаче кодов</a>

Предыдущий патент: Анализатор сигнатур параллельного потока данных

Следующий патент: Устройство для контроля интерполяционного кода

Случайный патент: Устройство для замены валков