Формирователь импульсов записи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

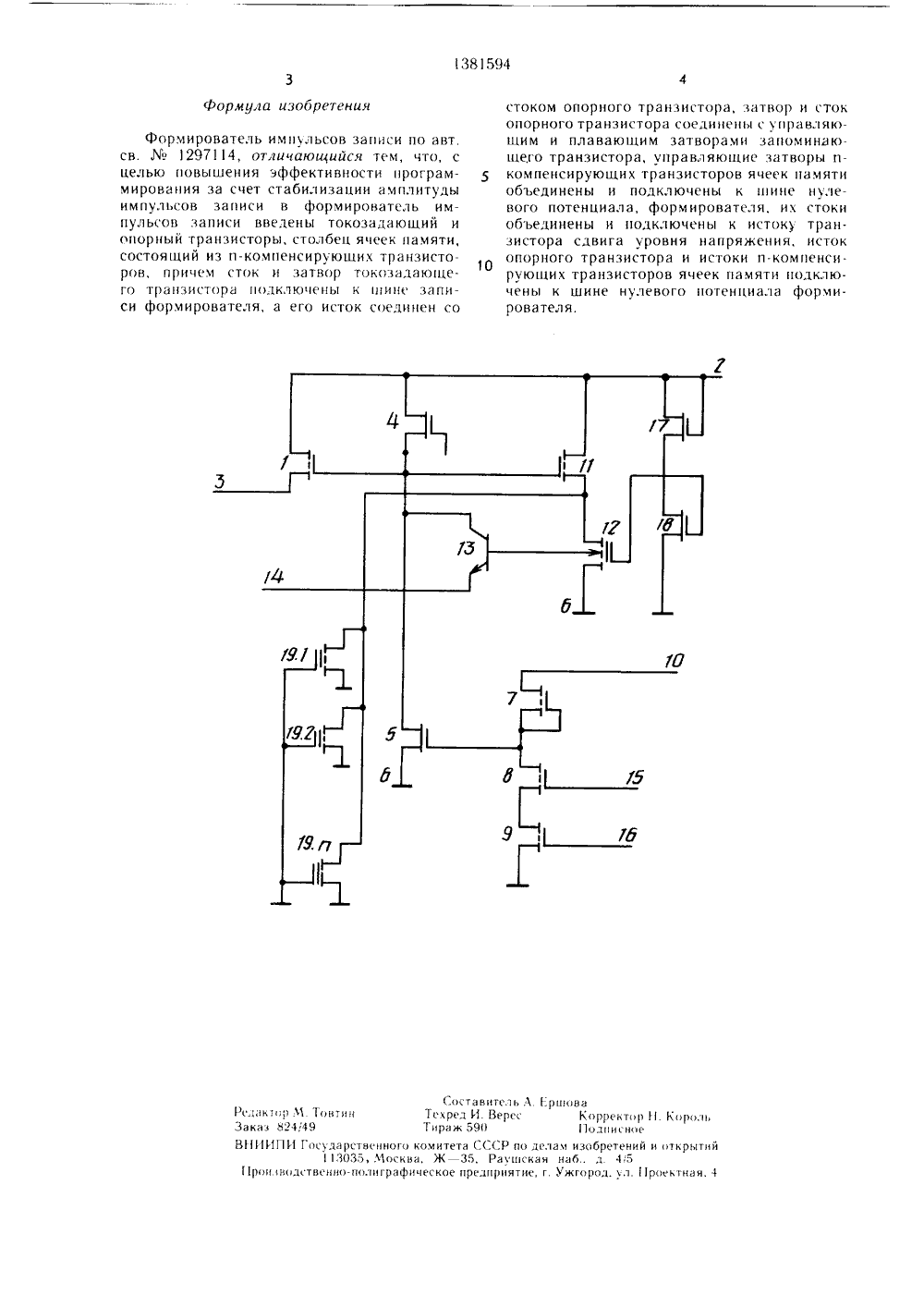

,лВ, ,,ВУ анов СССР985.МПУЛЪСО области электики и испольа поминающих ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ АВТОРСКОМУ СВИДЕТ(57) Изобретение относится кронной н вычислительной технзуется в программируемых з устройствах, использующих инжекцию горячих носителей для записи информации в ячейки памяти накопителя, и является усовершенствованием изобретения по авт, св.1297114. Цель изобретения - повышение эффективности программирования за счет стабилизации амплитуды импульса записи. Поставленная цель достигается тем, что в формирователь импульсов записи введены токозадающий и опорный транзисторы, а также ячейки памяти, в которые записывается идентичный уровень записи, что исключает разброс электрических характеристик ЗУ в режиме считывания информации, 1 ил.50 55 Изобретение относится к электронной технике, предназначено для использования в электрически программируемых запоминающих устройствах, использующих инжекцию горячих носителей для записи информации в ячейки памяти накопителя и является усовершенствованием изобретения по ант. св. М 1297114.Цель изобретенияповышение эффективности программирования путем стабилизации амплитуды импульса записи формирователя.На чертеже представлен формирователь импульсов записи.Устройство содержит транзистор 1 записи, шину 2 записи, информационную входную шину 3, транзистор 4 смещения, пер. ный клк)чевой транзистор 5, шину 6 нулевого потенциала, нагрузочный транзистор 7, транзистор 8 выборки, второй ключевой транзистор 9, шину 10 питания, транзистор 1 сдвига уровня напряжения, запоминающий транзистор 12, третий ключевой транзистор 13 и р и типа, шину 14 отрицательного смещения, уиранляющие входы 15 и 16, токозадающий 17 и опорный 18 транзисторы, и ячеек памяти, выполненных на компенсирующих транзисторах 19.1 - 19.п.Формирователь работает следующим образом. При подаче высоковольтного напряжения (рр) на шину 2 записи, через токо- задающий транзистор 17 протекает ток, обесиечинаю 1 ций падение напряжения на опорном транзисторе 18, которое эквивалентно величине напряжения на плавающем затворе запоминающего транзистора 12 в записанном состоянии. Предлагаемое включение токозадающего 17 и опорного 18 транзисторов обеспечивают слабую зависимость величины выходного напряжения (сток транзистора 18) в достаточно широком диапазоне изменения напряжения записи, а также от величины порогового напряжения данных транзисторов. Напряжение с опорного транзистора 18 подается на управляющий и плавающий затворы запоминающего транзистора 12 и таким образом в структуре запоминающего транзистора 12 создаются условия, идентичные условиям, имеющим место в реальном запоминающем транзисторе, находящемся в записанном состоянии, которое характеризуется минимальной величиной наряе лавинного пробоя (Хлл чин) Есчи на управляющие входы 15, 16 подаются напряжения высокого уровня, примерно равные величинам напряжения питания на шине 10, транзистор 8 выборки и второй ключевой Транзистор 9 переходят в открытое состояние, таким образом затвор ключевого транзистора 5 подключается к шине 6 нулевого потенциала через последовательно включенные транзисторы 8 и 9. При этом перный ключевой транзистор 5 закрыт и на за 5 1 О 15 20 25 30 35 40 45 творе транзисторов 1 и 11 через транзистор 4 тока смещения передается напряжение записи с шины 2. Транзистор 11 открывается, и на стоковую область запоминающего транзистора 12 передается напряжение,примерно равное разности напряжения записи на шине 2 и порогового напряжения транзистора 11. В случае, когда данное напряжение превышает величину напряжения лавинного пробоя стокового перехода, происходит лавинный пробой и возникает снижение носителей в подложку, которая приводит к положительному смещению области подложки вблизи запоминающего транзистора 12, а следовательно и базы биполярного транзистора 13. В результате протекания тока в цепи транзистора 13, напряжение на затворе транзистора сдвига уровня 11 напряжения ограничивается на уровне, обеспечивающем передачу НаИРЯЖЕНИЯ РНВНОГО Ч лл млл На СТОК ТРдН- зистора 12, а следовательно, и на общую числовую шину 3. Через транзистор 1 записи передается напряжение Ълл .лл. Таким образом, н пределах длительности импульса записи его амплитуда остается неизменной, так как напряжение на плавающем затворе запоминающего транзистора 12 в процессе программирования остается постоянным, а следовательно, отсутствует модуляция напряжения лавинного пробоя.В случае значительных токов утечки ио столбцу накопителя н режиме программирования, компенсация их влияния на амплитуду формируемых импульсов записи достигается следующим образом. Так утечки через ячейки памяти 19.1 19.и, равные току утечки через ячейки памяти столбца накопителя, понижают величину напряжения на стоке запоминающего транзистора 12, что приводит к уменьшению тока инжекции в подложку запоминающе о устройства, а следовательно, уменьшается и напряжение смещения на базе биполярного транзистора 13. В результате чего, напряжение на затворе транзистора сднига уровня 11 напряжения увеличивается, и на стоке запоминающего транзистора устанавливается на- ПряЖЕНИЕ 1 ллл члл, а На ВЫХОДЕ у СТрОЙСТ- ва исток транзистора 1 записи, обеспечивается постоянная амплитуда импульса записи.Для обеспечения максимальной компенсации влияния токов утечки ячейки памяти 19.1 19.и конструктивно должны быть выполнены идентично столбцу накопителя ЗУ.Преимушество данного формирователя импульсов записи состоит в том, что повышается эффективность программирования и во все ячейки памяти накопителя записывается идентичный уровень записи, что исключает разброс электрических характеристик ЗУ в режиме считывания информации.1381594 Формула изобретения ставител ь Л.д И. Верес59 Па СССР по д;ргповаКоррПоделаи изобрея наб д,г. Ужгород ГдТехреТираж Редактор М 1 онтинЗаказ 82449ВНИИПИ Госхдарс1130311 рои нодственно-п ектор 11. Короли1 сноетений и открытий45л. Проектная, 4 асиного комитез, Москва, Ж ли графическое 35, Раугиск предприятие Формирователь импульсов записи по авт. св. Хв 1297114, отличающийся тем, что, с целью повышения эффективности программирования за счет стабилизации амплитуды импульсов записи в формирователь импульсов записи введены токозадающий и опорный транзисторы, столбец ячеек памяти, состоящий из и-компенсирующих транзисторов, гричем сток и затвор токозадающего транзистора подключены к шине записи формирователя, а его исток соединен со стоком опорного транзистора, затвор и сток опорного транзистора соединены с управляющим и плавающим затворами запоминающего транзистора, управляющие затворы и компенсирующих транзисторов ячеек памятиобъединены и подключены к шине нулевого потенциала, формирователя, их стоки объединены и подключены к истоку транзистора сдвига уровня напряжения, исток опорного транзистора и истоки и-компенсирующих транзисторов ячеек памяти подключены к шине нулевого потенциала формирователя.

СмотретьЗаявка

4104879, 15.08.1986

ПРЕДПРИЯТИЕ ПЯ Х-5737

СИДОРЕНКО ВЛАДИМИР ПАВЛОВИЧ, ГРУДАНОВ НИКОЛАЙ БОРИСОВИЧ, ХОРУЖИЙ АНАТОЛИЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G11C 16/06

Метки: записи, импульсов, формирователь

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/3-1381594-formirovatel-impulsov-zapisi.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов записи</a>

Предыдущий патент: Устройство для записи информации в программируемое постоянное запоминающее устройство

Следующий патент: Устройство для контроля магнитных интегральных схем памяти

Случайный патент: Концентрационная установка