Сумматор по модулю 2 -1

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1156063

Автор: Карпухин

Текст

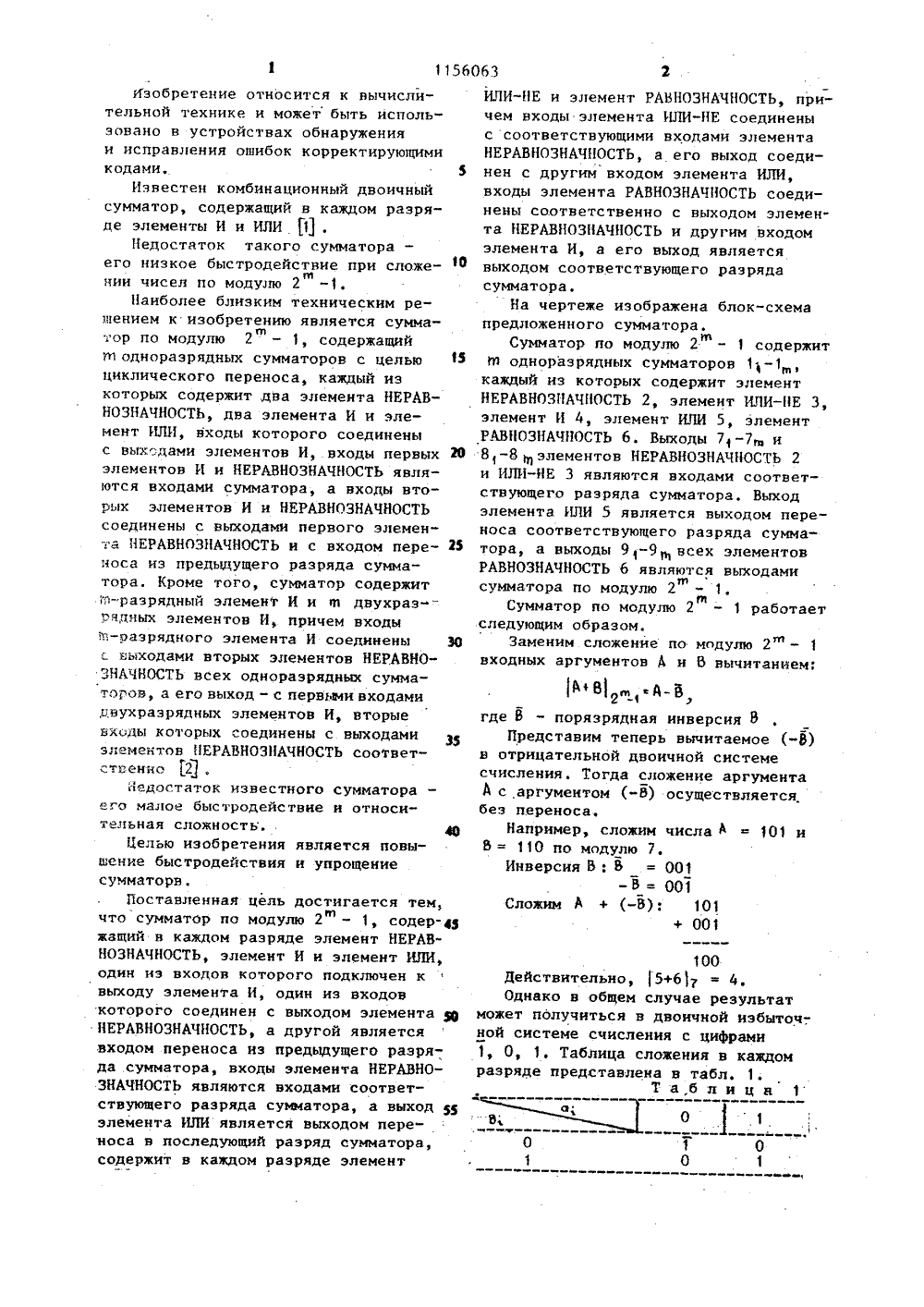

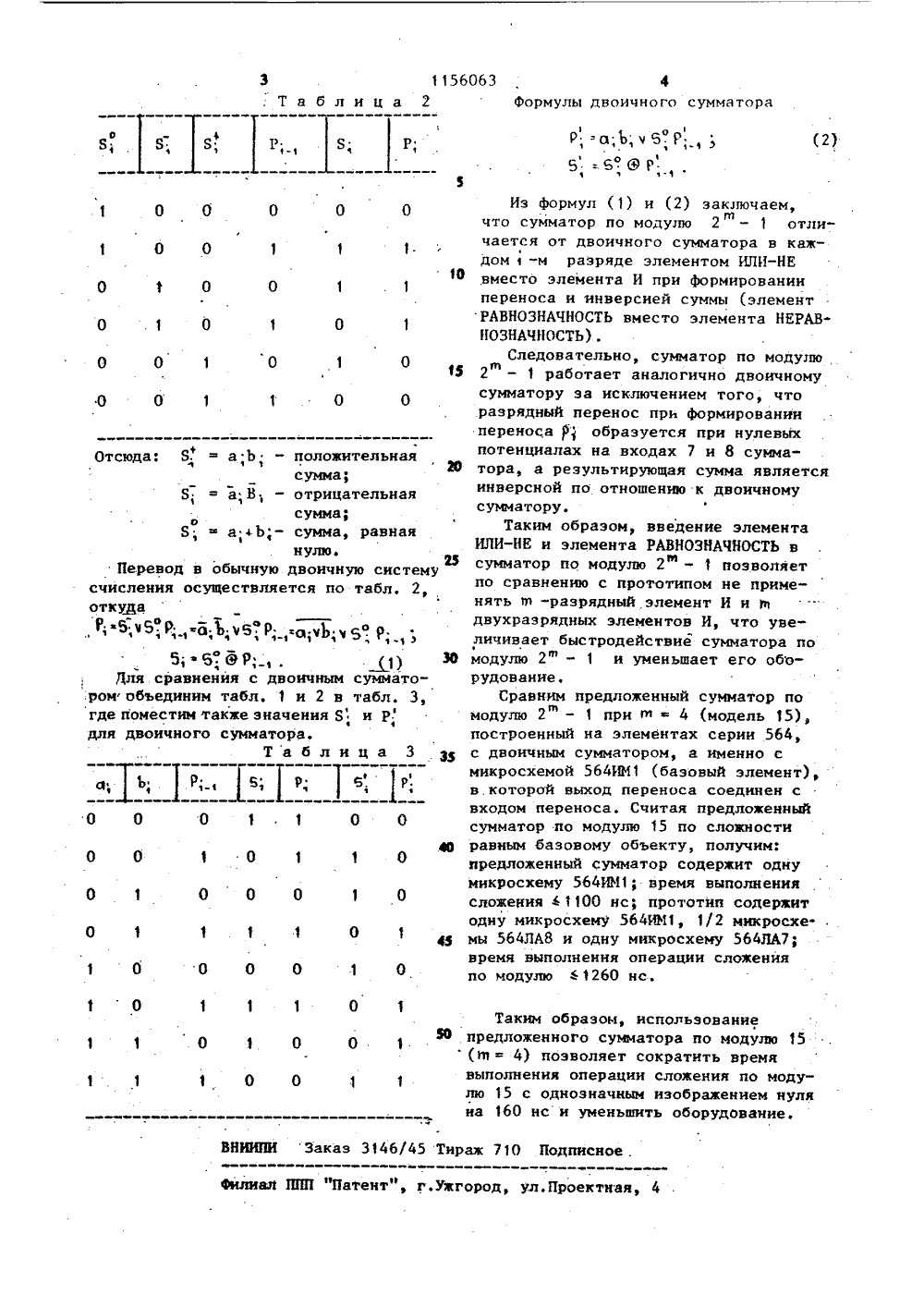

/50 5 цС 0 ОПИСАНИЕ ИЗОБРЕТЕН к ТВУ 18 СССР етельство /50, 1981.ифметическне фровых автома"т 1980 ь с. 12 2 - 1, элемент и зле- орого И, один с выхооса из ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ВТОРСНОМУ СВИДЕТЕЛ(56) 1. Авторское свидВ 800992, кл. С 06 Р 72, Савельев А.Я. Ари логические основы цитов. М., Высшая школа(54)(57) СУММАТОР 110 МОДУЛЮ содержащий в.каждом разряде НЕРАВНОЗНАЧНОСТЬ, элемент И мент ИЛИ, один из входов ко подключен к выходу элемента иэ входов которого соединен дом элемента НЕРАВНОЗНАЧНОС другой является входом пере 801156063 А предыдущего разряда сумматора,входы элемента НЕРАВНОЗНАЧНОСТЬ являются входами соответствующегоразряда сумматора, а выход элементаИЛИ является выходом переноса в последующий разряд сумматора, о т л ич а ю щ и й с я тем, что, с цельюповьпиения быстродействия и упрощениясумматора, он содержит в каждом разряде элемент КПИ-НЕ и элемент РАВНОЗНАЧНОСТЬ, причем входы элементаИЛИ-НЕ соединены с соответствующимивходами элемента НЕРАВНОЗНАЧНОСТЬ;его выход соединен с другим входомэлемента ИЛИ, входы элемента РАВНОЗНАЧНОСТЬ соединены соответственнос выходом элемента НЕРАВНОЗНАЧНОСТЬи другим входом элемента И, а еговыход является выходом соответствующего разряда сумматора.11560 Изобретение относится к вычислительной технике и может быть использовано в устройствах обнаруженияи исправления ошибок корректирующимикодами. %Известен комбинационный двоичныйсумматор, содержащий в каждом разряде элементы И и ИЛИ 1 .Недостаток такого сумматора -его низкое быстродействие при сложе фнии чисел по модулю 2 -1.Наиболее близким техническим решением к изобретению является сумматор по модулю 2 - 1, содержащийщ одноразрядных сумматоров с цельюциклического переноса, каждый изкоторых содержит два элемента НЕРАВНОЗНАЧНОСТЬ, два элемента И и элемент ИЛИ, входы которого соединеныс выходами элементов И,.входы первых 20элементов И и НЕРАВНОЗНАЧНОСТЬ являются входами сумматора, а входы вторых элементов И и НЕРАВНОЗНАЧНОСТЬсоединены с выходами первого элемента НЕРАВНОЗНАЧНОСТЬ и с входом переноса из предыдущего разряда сумматора. Кроме того, сумматор содержитв-разрядный элемент И и а двухраэ рядных элементов И, причем входыВ-разрядного элемента И соединены 30выходами вторых элементов НЕРАВНО"ЗНАЧНОСТЬ всех одноразрядных сумматоров, а его выход - с первыми входамидвухразрядных элементов И, вторыевходы которых соединены с выходамиэлементов НЕРАВНОЗНАЧНОСТЬ соответственно 2 .Недостаток известного сумматора -его малое быстродействие и относительная сложность. 46Целью изобретения является повывенке быстродействия и упрощениесумматорв,Поставленная цель достигается тем,чтосумматор по модулю 2 - 1, содер-,цжащий в каждом разряде элемент НЕРАВНОЗНАЧНОСТЬ, элемент И и элемент ИЛИ,один из входов которого подключен квыходу элемента И, один из входовкоторого соединен с выходом элемента щНЕРАВНОЗНАЧНОСТЬ, а другой являетсявходом переноса кз предыдущего разряда сумматора, входы элемента НЕРАВНОЗНАЧНОСТЬ являются входами соответствующего разряда суьакатора, а выход уэлемента ИЛИ является выходом переноса в последующий разряд сумматора,содержит в каждом разряде элемент 63 2ИЛИ-НЕ и элемент РАВНОЗНАЧНОСТЬ, причем входы элемента ИЛИ-НЕ соединеныс соответствующими входами элементаНЕРАВНОЗНАЧНОСТЬ, а его выход соединен с другим входом элемента ИЛИ,входы элемента РАВНОЗНАЧНОСТЬ соединены соответственно с выходом элемента НЕРАВНОЗНАЧНОСТЬ и другим входомэлемента И, а его выход являетсявыходом соответствующего разрядасумматора.На чертеже изображена блок-схемапредложенного сумматора.Сумматор по модулю 2 - 1 содержитЮ одноразрядных сумматоровкаждый из которых содержит элементНЕРАВНОЗНАЧНОСТЬ 2, элемент ИЛИ-Е Э,элемент И 4, элемент ИЛИ 5, элементРАВНОЗНАЧНОСТЬ 6. Выходы 71-7 и8-8элементов НЕРАВНОЗНАЧНОСТЬ 2и ИЛИ-НЕ 3 являются входами соответствующего разряда сумматора. Выходэлемента ИЛИ 5 является выходом переноса соответствующего разряда сумматора, а выходы 9 1-9 всех элементовРАВНОЗНАЧНОСТЬ 6 являются выходамисумматора по модулю 2 - 1,Сумматор по модулю 2 - 1 работаетследующим образом.Заменим сложение по модулю 2 - 1входных аргументов А и б вычитанием:ьв 1 я-ь,где 8 - порязрядная инверсия 8Представим теперь вычитаемое (-6)в отрицательной двоичной системесчисления. Тогда сложение аргументаА с аргументом (-о) осуществляется.без переноса.Например, сложим числа А101 иВ = 110 по модулю 7,Инверсия В: В = 001- В= 001Сложим А + (-В): 101+ 001 100Действительно, 5+6 у = 4.Однако в общем случае результатможет получиться в двоичной избыточ-,ной системе счисления с цифрами1, О, 1. Таблица сложения в каждомразряде представлена в табл. 1.Таблица 1(2) 0 0 1 0 0 1 0 0 0 1 О О . 1 О О О 0 0 1 1.101 О О 0 О О О Отсюда: 8.а Ь - положительнаяч 1 1 26сумма;Б,а;В, - отрицательнаясумма;о8; щ а;4 Ъ; - сумма, равнаянулю.Перевод в обычную двоичную систему счисления осуществляется по табл, 2, откудаР;б;чЬ;Р, о;Ъ,б Р =о-ч 1) з 5 Р-15;-б. ЭР,. (1) бДля сравнения с двоичным сумматором объединим табл. 1 и 2 в табл. 3, где поместим также значения Я и Р4 для двоичного сумматора.Таблица 3Р;, Б; Р; 6 Р 11 0 О О 1 1 1 О О О 1 О О 1 О 1 1 0 1О 1 О 1 1 1 О 1 Таким образом, использование Зб предложенного сумматора по модулю 15(Ф4) позволяет сократить время выполнения операции сложения по модулю 15 с однозначным изображением нуля на 160 нс и уменьшить оборудование,0 1 О 1 О О 1 1 1 1 ВНИИПИ Заказ 3146/45 Тираж 710 Подписное . Филиал ППП пПатент", г.ужгород, ул,Проектная, 4 0 О 0 1 1 О О 0 0О 1 1 О фФормулы двоичного сумматора Из формул (1) и (2) заключаем,что сумматор по модулю 2 - 1 отличается от двоичного сумматора в каждом-м разряде элементом ИЛИ-НЕвместо элемента И при формированиипереноса и инверсией суммы (элементРАВНОЗНАЧНОСТЬ вместо элемента НЕРАВ"НОЗНАЧНОСТЬ).Следовательно, сумматор по модулю2 - 1 работает аналогично двоичномусумматору за исключением того, чторазрядный перенос при формированиипереносаобразуется при нулевьгхпотенциалах на входах 7 и 8 сумматора, а результирующая сумма являетсяинверсной по отношению к двоичномусумматору,Таким образом, введение элементаИЛИ-НК и элемента РАВНОЗНАЧНОСТЬ всумматор по модулю 2 - 1 позволяетпо сравнению с прототипом не применять Ф -разрядный элемент И и Вдвухразрядных элементов И, что увеличивает быстродействие сумматора помодулю 2 - 1 и уменьшает его оборудование.Сравним предложенный сумматор помодулю 2 - 1 при пф 4 (модель 15),построенный на элементах серии 564,с двоичным сумматором, а именно смикросхемой 564 ИМ 1 (базовый элемент)в.которой выход переноса соединен свходом переноса. Считая предложенныйсумматор по модулю 15 по слокностиравным базовому объекту, получим:предложенный сумматор содержит однумикросхему 564 ИМ 1; время выполнениясложения 4 1100 нс; прототип содержитодну микросхему 564 ИИ 1, 1/2 микросхемы 564 ЛА 8 и одну микросхему 564 ЛА 7;время выполнения операции сложенияпо модулю1260 нс.

СмотретьЗаявка

3692438, 19.01.1984

ОРГАНИЗАЦИЯ ПЯ В-8466

КАРПУХИН АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/50

Опубликовано: 15.05.1985

Код ссылки

<a href="https://patents.su/3-1156063-summator-po-modulyu-2-1.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю 2 -1</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Устройство для умножения

Случайный патент: Способ изготовления бумаги, преимущественно для самопишущих приборов