Устройство для обнаружения и коррекции одиночных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

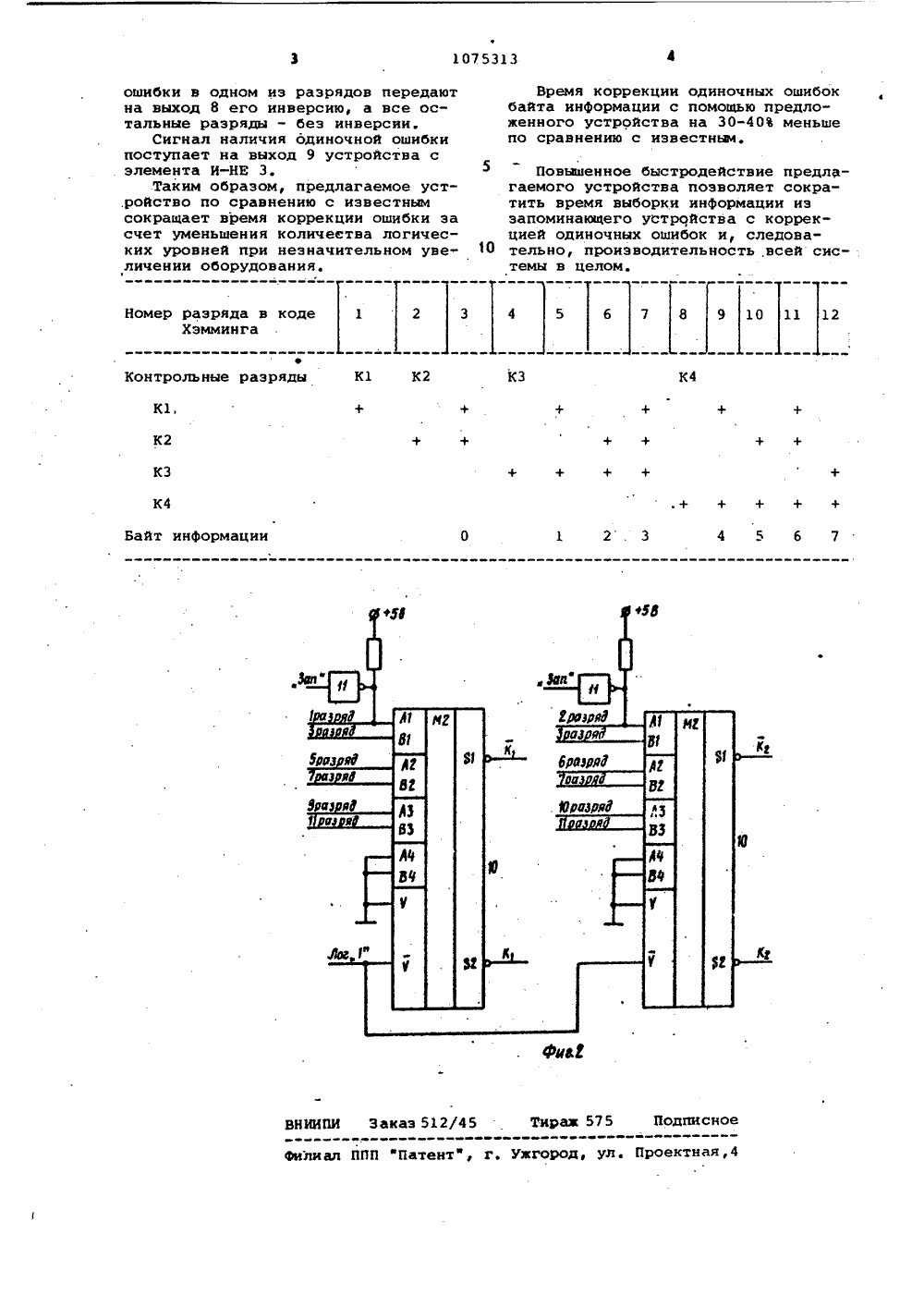

(19) (11 11 С 29/О 315 ЗОБРЕ ЕТЕЛЬСТВУ НОМУ А СССО,УЖЕН одгоил иью СУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ(54)(57) УСТРОЙСТВО ДЛЯ ОБНАРИ КОРРЕКЦИИ ОДИНОЧНЫХ ОШИБОК,жащее блок формирования контросигналов, одни из входов которявляются информационными входаустройства, и элементы НЕ, о тч а ю щ е е с я тем, что, с це НИЯ Й повышения быстродействия устройства,в него введены элемент И-НЕ и коммутаторы, адресные входы которых подключены к одним иэ выходов блока формирования контрольных сигналов, первые информационные входы коммутаторов соединены с информационнымивходами устройства, вторые информационные входы - с выходами элементовНЕ, входы которых подключены к информационным входам устФойства, а выходы коммутаторов являются информа,ционными выходами устройства, контрольным входом которого является выход элемента И-НЕ, входы которогоподключены к другим выходам блокаформирования контрольных сигналов,Недостатком известного устройства является также невысокое быстродействие, связанное с многоступенчатой схемой коррекции,Целью изобретения является повы" шение быстродействия устройства при обнаружении и коррекции одиночной ошибки байта информации в коде Хэмминга. 40 45 Указанная цель достигается тем, что в устройство для обнаружения и коррекции одиночных ошибок, содержащее блок Формирования контрольных сигналов, одни из входов которого являются информационными входами устройства, и элементы НЕ, введены элемент И-ЙЕ и коммутаторы, адресные входы которых подключены к одним из выходов блока формирования контрольнйх сигналов, первые информационные входы коммутаторов соединены с инФормационными, входами устройства, вторые информационные входы - с выходами элементов НЕ, входы которых подключены к информационным входам 60 устройства, а выходы коммутаторов являются информационными выходами устройства, контрольным выходом которого является выход элемента И-НЕ, входы которого подключены к другим 65 Изобретение относится к вычислительной технике, в частности к запоминающим устройствам,Известны устройства для обнаружения и коррекции одиночных ошибок,содержащие входной регистр, селектор, блок коррекции входной информации, генератор кода Хэмминга, регистр контрольного кода, регистркода Хэмминга, блок коррекции контрольного кода, блок сравнения пари Отета записываемой информации, блок.сравиения кода Хэмминга, блок обнаружения неисправностей, дешифраторошибок, контрольный .блок. сравнения,выходной регйстр Ц (2). 15Недостатками этого устройства являются низкое быстродействие, вызванное многоуровневой схемой коррек.ции, и большие аппаратурные затраты.Йаиболее близким техническим реше нием к изобретению является устройство для .обнаружения и коррекции ошибок в памяти, содержащее логическийблок для формирования контрольныхбитов кода Хэмминга и битов синдрома, дешифраторы, входы которых подключены к выходам логического блока,а выходы - к первым входам логических элементов, реализующих функциюИСКЛЮЧАЮЩЕЕ ИЛИ, на вторые входыкоторых поступает информация.из памяти, а с выходов элементов ИСКЛЮЧАКМЦЕЕ ИЛИ информация через инверторыпередается на выходную магистральданных (2).выходам блока формирования контрольных сигналов,На Фиг. 1 изображена структурнаясхема устройства для обнаружения икоррекции одиночных ошибок; нафиг. 2 - возможный вариант выполненияФормирователя контрольных сигналовдля двух разрядов.Устройство (фиг, 1) содержит блок1 формирования контрольных сигналов,служащий для формирования разрядовсиндрома.и контрольных разрядов кодаХэмминга, элементы НЕ 2, элементИ-НЕ 3 и коммутаторы 4, Устройствоимеет входы 5 и 6 и выходы 7-9,Блок 1 ,(фиг, 2) представляет собой четыре схемы 10 четности, формирующие контрольные разряды по .принципу построения кода Хэмминга, а также четыре элемента НЕ 11. При записи в память дляФормирования, например контрольного разряда К 1, схема 10 четности (фиг. 2) должна проверять разряды 3,5,7,9 и 11; для-формирования контрольного разрядаК 2 - разряды 3,6,7,10 и 11 и т.д.в соответствии с таблицей.Элементы НЕ 11 при записи информации в память обнуляют входы схем10 четности., на которые в режимечтения поступают контрольные разряды код Хэмминга,При чтении для формирования разряда К 1 синдрома схема 10 четности дол:жнэа проверять разряды 1,3,5,7,9 и 11;для формирования разряда К 2 - разряды 2,3,6,7,10 и 11 и т,д. в соответствии с таблицей,Блок 1 может быть выполнен намикросхемах типа К 1 55 (133) ИП 2 иК 155 (133) ЛНЗ, Коммутаторы 4 могутбыть выполнены на микросхемах К 155(133) КП 1,Устройство работает следующимобразом,Перед записью в память (не по"казана) со входа 5 устройства в блок1 параллельно поступает байт информации. Б блоке 1 происходит формирование четырех контрольных разрядовК 1-К 4 кода Хэмминга для байта информации. Сформированные разряды поступают на выход 7 устройства для записи в память. При чтении на входы .5 и 6 параллельно нз памяти поступает информация в контрольные разряды кода Хэмминга. При этом блок 1 формирует разряды К 1 - К 4 синдрома, которые поступают на адресные входы коммутаторов 4. Информация со входа 5 поступает также на входы элементов НЕ 2 и первые информационные входы коммутаторов 4. На вторые информационные входы коммутаторов 4 поступает информация с выходов элементов НЕ 2. Коммутаторы 4 при наличии107. 531 3 ошибки в одном иэ разрядов передают на выход 8 его инверсию, а все остальные разряды - без инверсии,Сигнал наличия одиночной ошибки поступает на выход 9 устройства с элемента И-НЕ 3.Таким образом, предлагаемое уст,ройство по сравнению с известным сокращает время коррекции ошибки за счет уменьшения количества логических уровней при незначительном увеличении оборудования. 2 3 4 5 6 7 8 9 10 11 12 Контрольные разряды КЗ К 1 К 2 К 4 К 1,+ ++ + + + + 4 5 6 7 1 2. 3 Байт информации фаай ВНИИПИ Заказ 512/45 Тираж 575 филиал ППП фПатентф, г. ужгород, ул дписн Проектная, 4 Номер разряда в коде 1 Хэмминга Время коррекции одиночных ошибок байта информации с помощью предложенного устройства на 30-40 меньше по сравнению с известныи. Повышенное быстродействие предлагаемого устройства позволяет сократить время выборки информации иэзапоминающего устройства с коррекцией одиночных ошибок и, следова- О тельно, производительность,всей системы в целом.

СмотретьЗаявка

3532143, 30.12.1982

ПРЕДПРИЯТИЕ ПЯ М-5912

АБРАМОВ АЛЕКСАНДР ВЛАДИМИРОВИЧ, КИСЕЛЕВ СЕРГЕЙ КОНСТАНТИНОВИЧ, ЛЯПИНСКИЙ ВАЛЕРИЙ ВАСИЛЬЕВИЧ, РОДИН ВАЛЕРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: коррекции, обнаружения, одиночных, ошибок

Опубликовано: 23.02.1984

Код ссылки

<a href="https://patents.su/3-1075313-ustrojjstvo-dlya-obnaruzheniya-i-korrekcii-odinochnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и коррекции одиночных ошибок</a>

Предыдущий патент: Запоминающее устройство с коррекцией ошибок

Следующий патент: Высоковольтный резистор

Случайный патент: Композиция ингредиентов для игристого вина "браво