Микропрограммное устройство для анализа программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

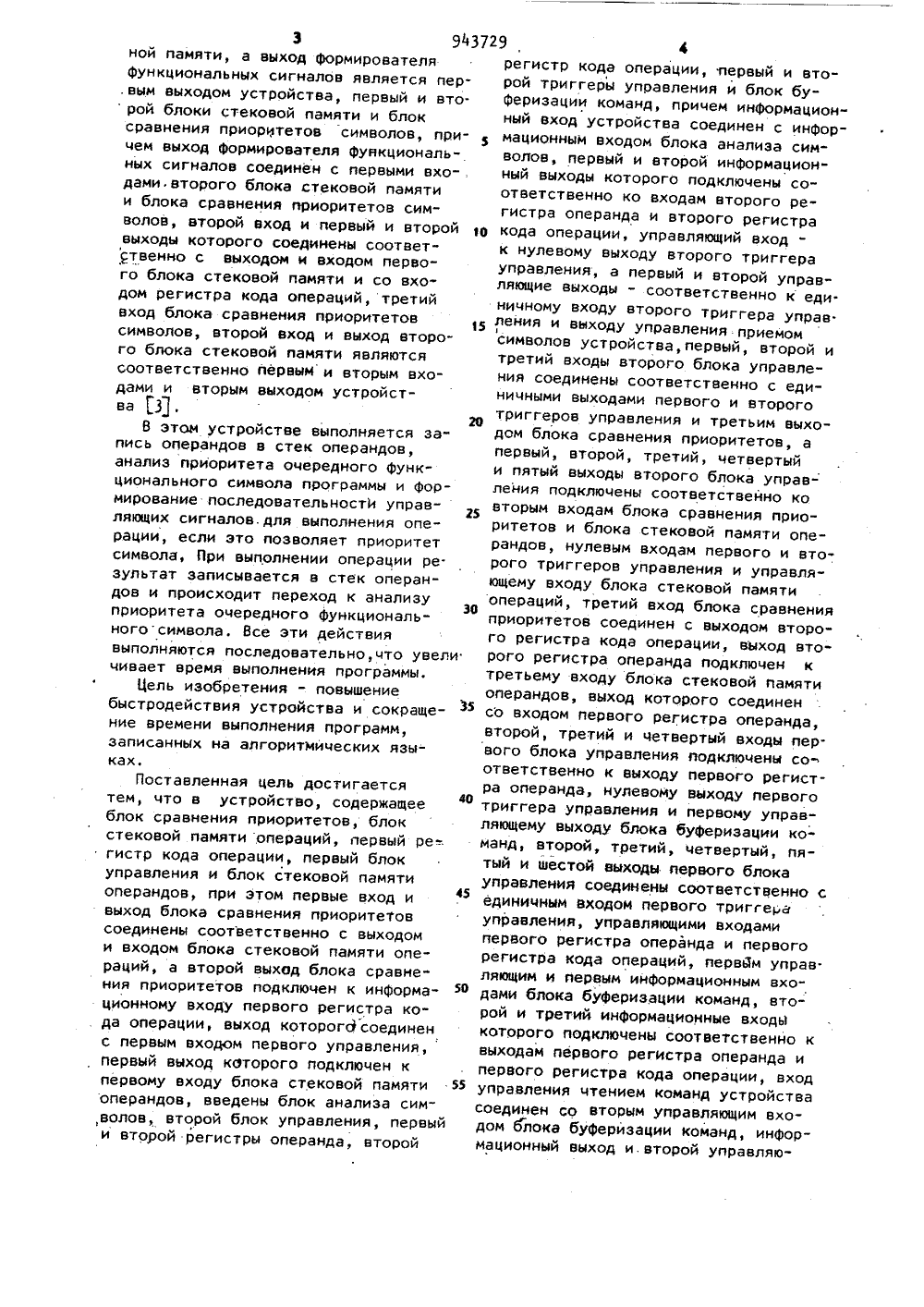

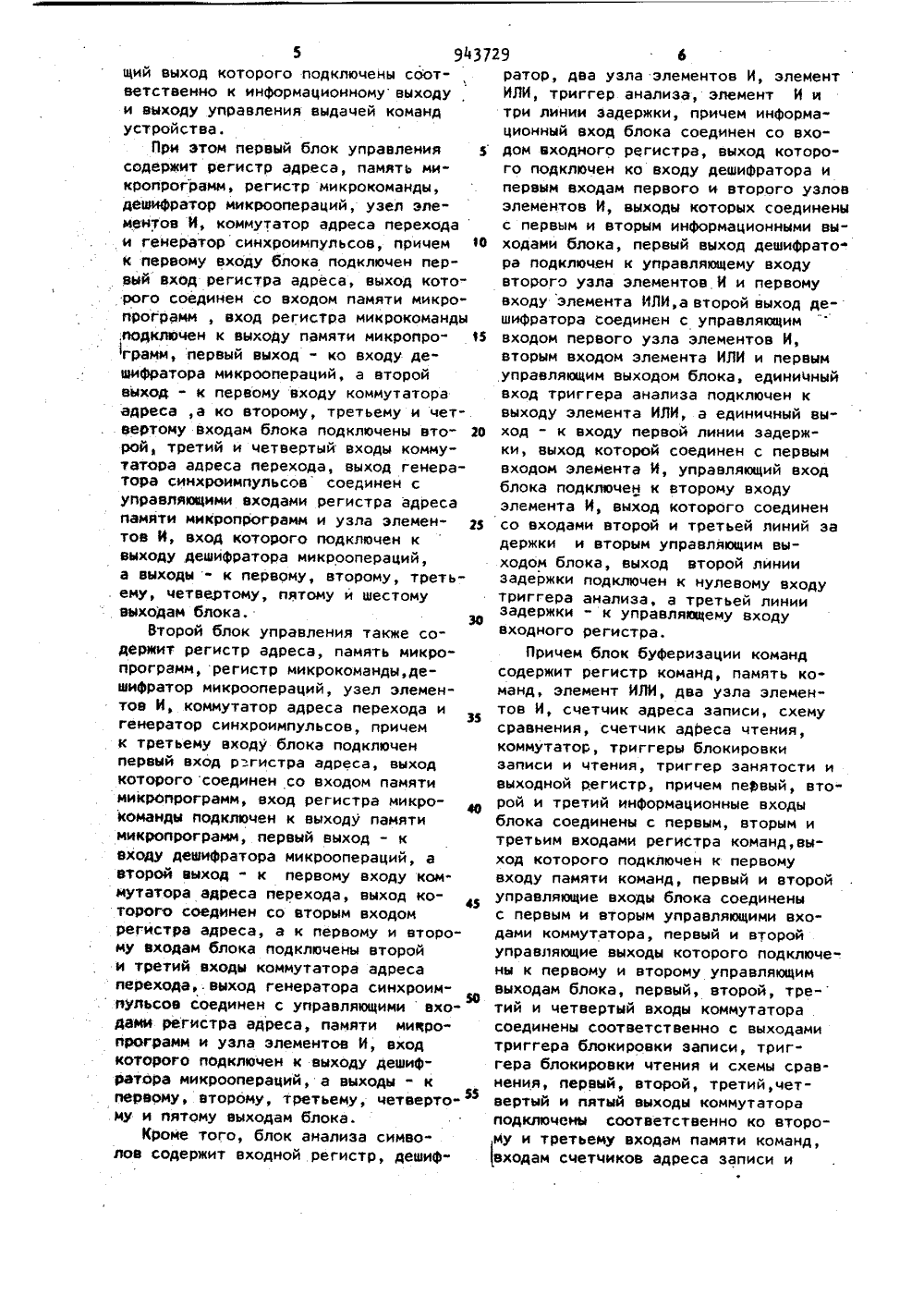

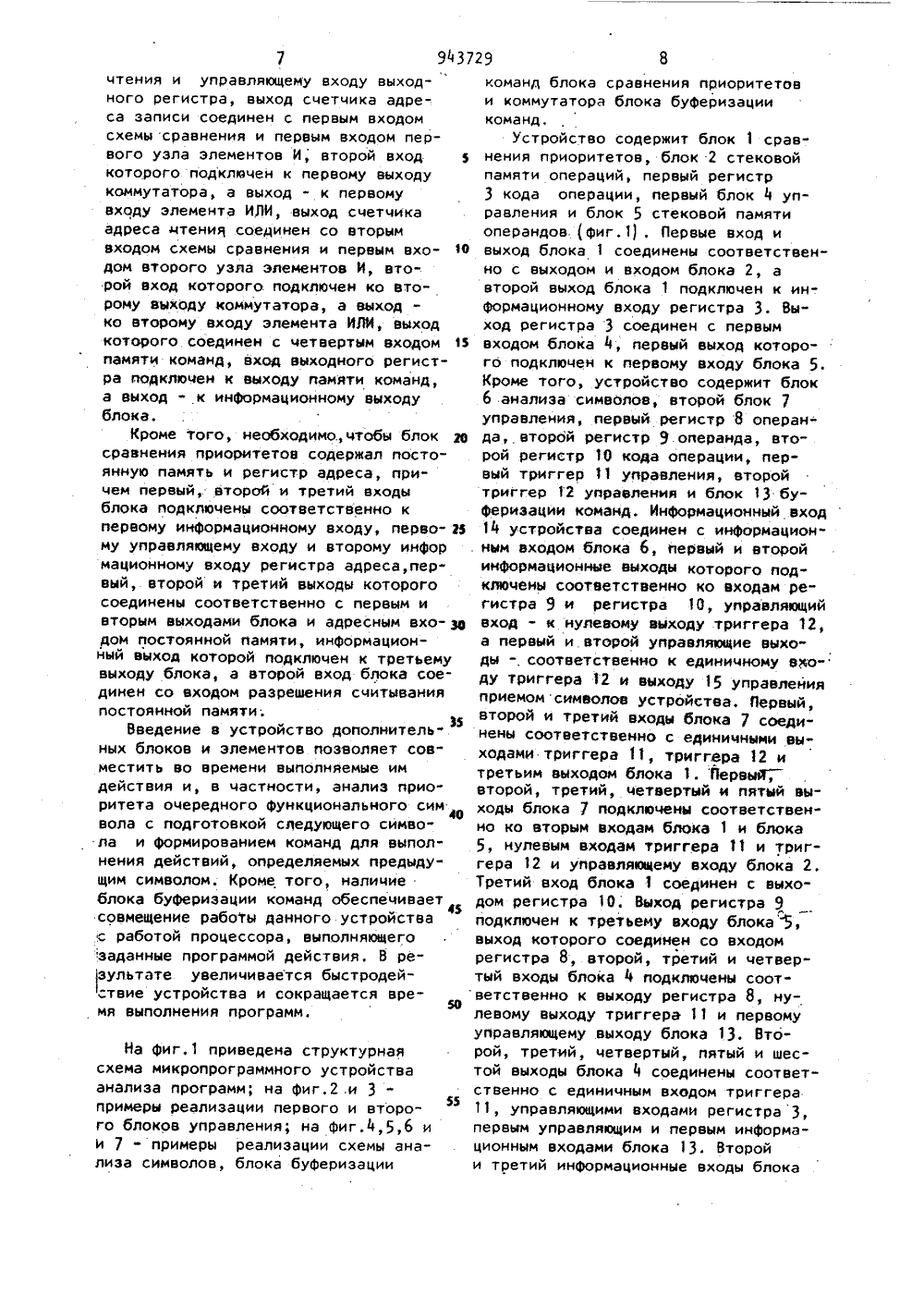

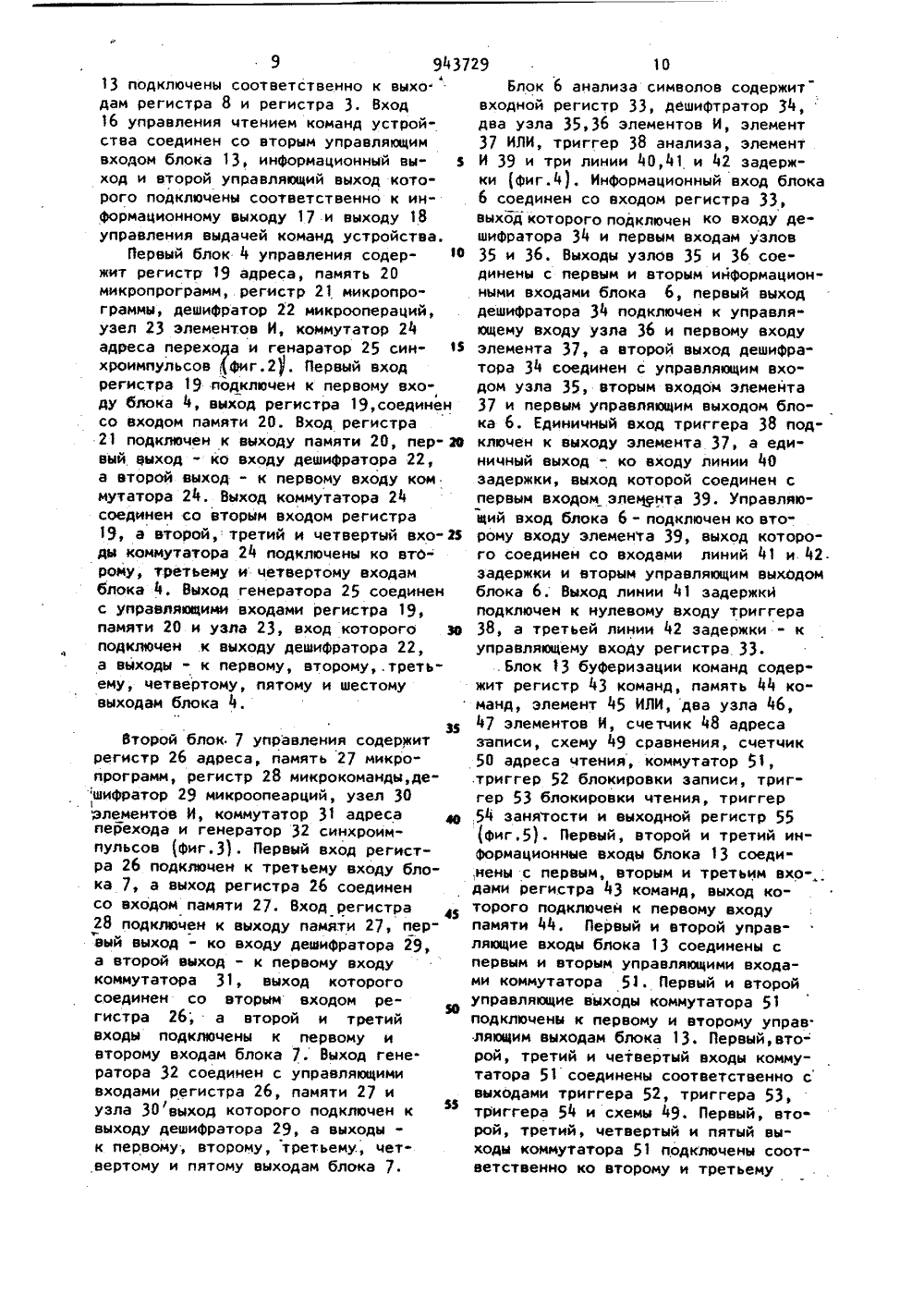

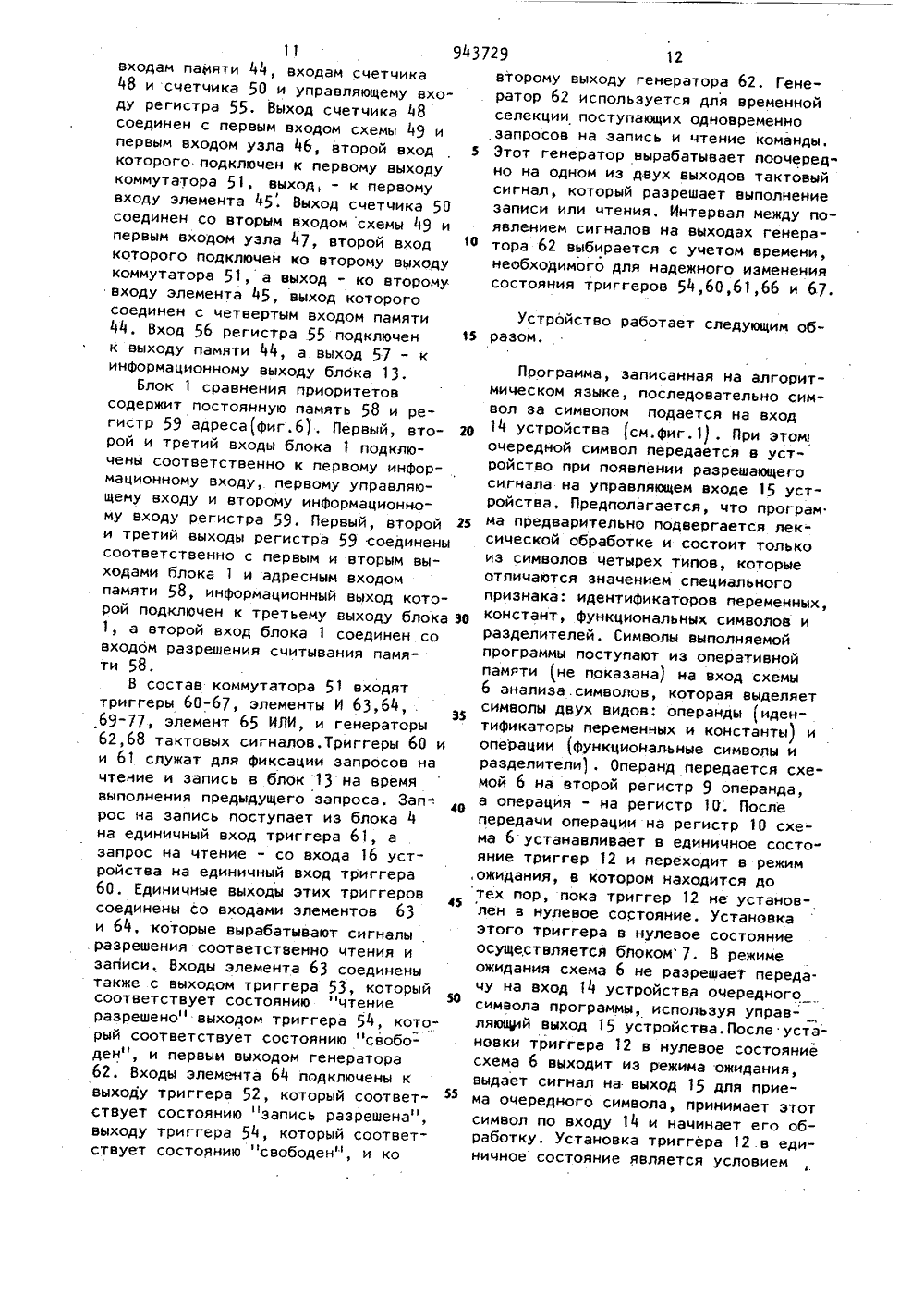

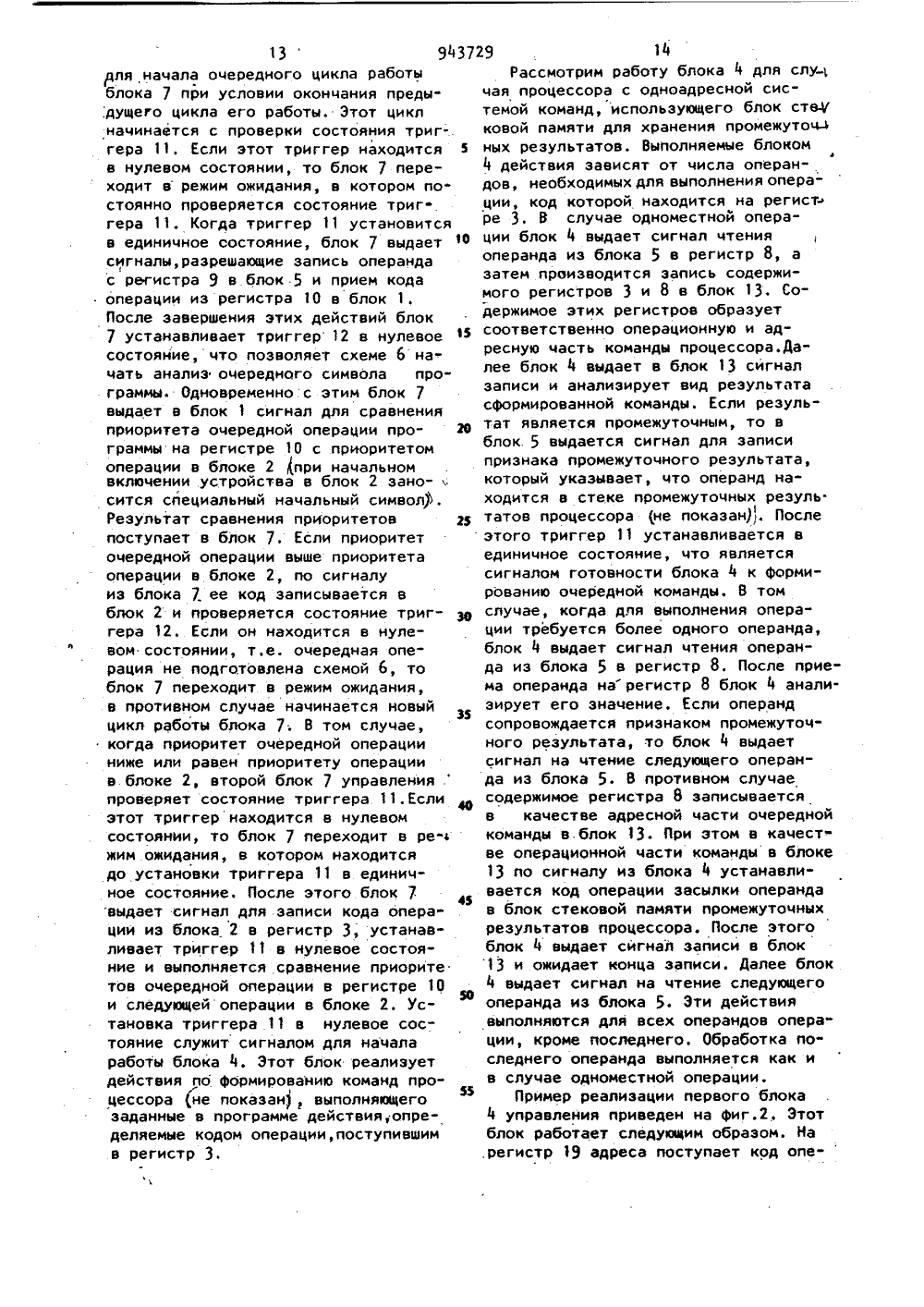

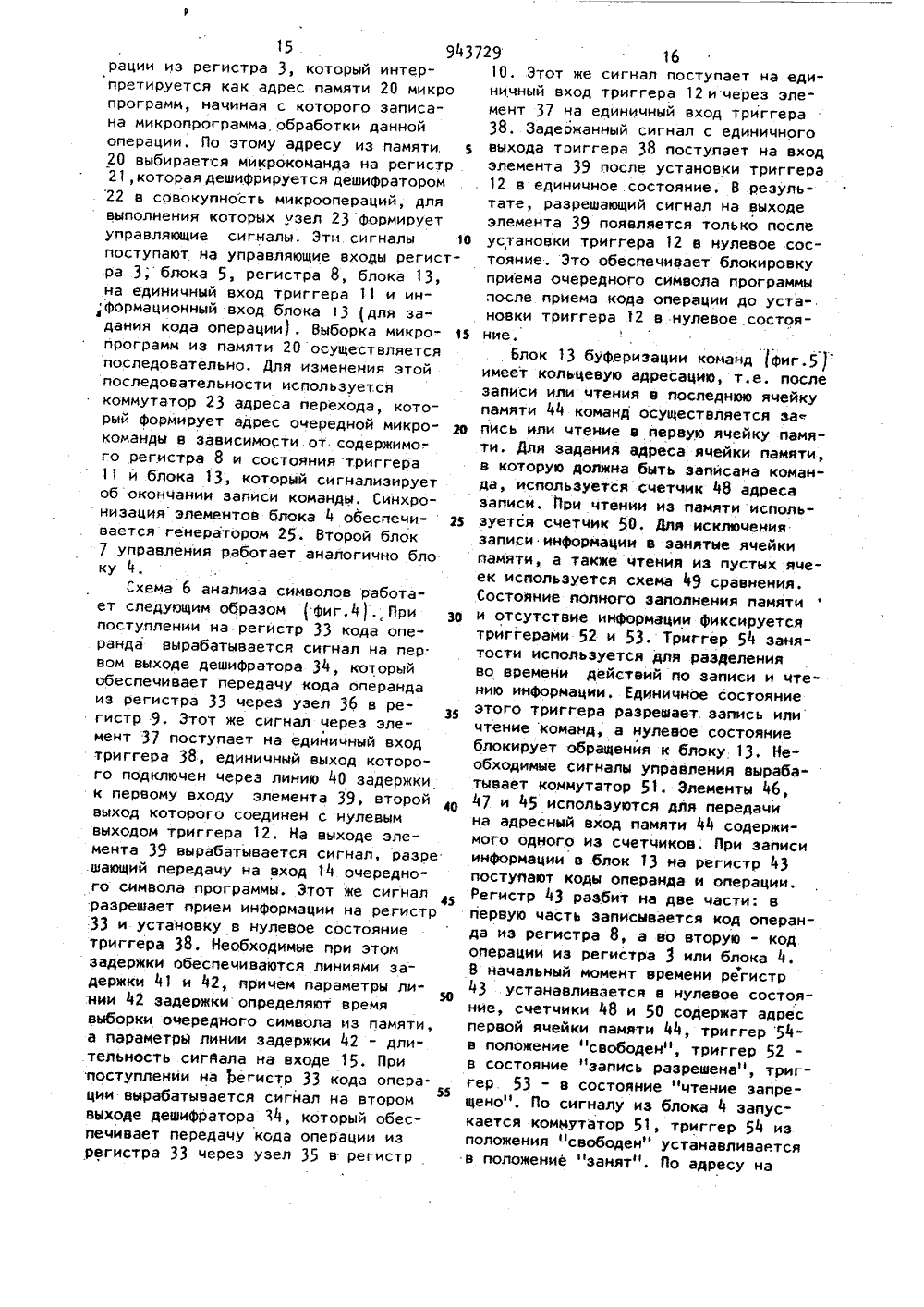

(71) Заявя ИИКРОПРОГРАИИНОЕ УСТРОЙСТПРОГРАИИ Я АНАЛИЗА 1Изобретение относится к вычислительной технике и может применяться в вычислительных машинах, ориентиро ванных на выполнение программ на алгоритмических языках, в качестве устройства преобразования программ.Программы, записанные на алгоритмических языках например АЛГОЛ или фОРТРАН 1, характеризуются сложными взаимосвязями, определяющими порядок выполнения входящих в них операций, который в большинстве случаев не совпадает с порядком записи этих опе раций в программе. Непосредственное выполнение программ,. записанных на алгоритмических языках, требует пере упорядочивания операций, записанных в программе, в соответствии с последовательностью их выполнения.Известны устройства, которые основаны на использовании стека операций, схемы сравнения приоритетов опе раций, стека операндов и ряда управляющих схем и регистров 1 и 1.21. Недостатком данных устройств явяяется низкая скорость выполнения программ на алгоритмических языках.Наиболее близким по техническойсущности к изобретению является устройство микропрограммного управления,содержащее блок постоянной памяти,выход которого соединен с регистроммикрокоманды, дешифратор микроопера",ций, выход которого соединен с первым входом формирователя функциональных сигналов, регистр кода операции,выход которого соединен с первымвходом регистра адреса, блок синхрогнизации, выход которого соединен со 15вторыми входами формирователя функциональных сигналов и регистра адре"са, с первым входом блока постояннойпамяти, причем первый, второй выходы 20 регистра микрокоманды соединены соответственно со входом дешифраторамикроопераций и с третьим входомрегистра адреса, выход которого соединен со вторым входом блока постоян"943729 20программ формирует следующую после- и довательность команд Засылка А пе регистр Запись: = во второйрегистр. 10 кодаоперации 2 Установка, второготриггера 12 управлев единичное состояПроверка состояния первого триг гера 11 управле- ния 19этого блок 1 готов к приему очередного кода операции из регистра 10, Еслприоритет очередной операции ниже илиравен приоритету операции в блоке 2,находящейся в младших разрядах регистра 59, блок 7 после проверки необходимых условий разрешает передачукода операции из блока 2 в регистр3. Для этого код младших разрядоврегистра 59 передается на вход ре вгистра 3, а в младшие разряды регистра 59 записывается очереднойкод из блока 2, После этого блок 1готов к сравнению приоритетов очередной пары операций. Действия по 1 Зприему и выдаче информации произво-дится по сигналам блока 7,Для пояснения работы устройстварассмотрим пример обработки оператора А:8 х С + Е; Предположим,что перед обработкой этого оператора триггер 11 находится в единичном состоянии, а триггер 12 " в нулевом состоянии. Последовательность действий,выполняемых под управлением схемы 6 Ианализа символов, второго блока 7управления и первого блока ч. управления при обработке оператора, приведена в таблице. В таблице принятыследующие обозначения: 1. содержи- зомое вершины блока 2 стековой памятиперед обработкой оператора, ПрПРпризнак промежуточного результата.8 результате обработки оператораА:= В х С + Е; устройство анализа Приведенный пример показывает,что предлагаемое микропрограммноеустройство анализа программ по сравнению с известными устройствами обеспечивает: совмещение подготовки информации кодов операнда и операции)для с 1 череднай операции с обработкойпредыдущей операции; совмещение записи информации в блок 5 и в блок сравнения приоритетов; совмещение сравнения приоритетов очередной операции и второй операции из вершиныблока 2 стековой памяти операций сформированием команды для первойоперации иэ вершины блока 2, а также запись в блок 2 очередной операции; совмещение подготовки очередныхкоманд с выполнением предыдущих команд процессором.Анализ работы предложенного устройства при обработке реальных программ на языке высокого уровня показывает, что его применение сокращает время выполнения программ вполтора. раза по сравнению с известными устройствами,943729 21 Проверка состояния первого триггера 11управления 10 14 Запись + на второй регистр 10 кода операции 7 Запись В во второй регистр 9 операнда 8 Запись х во второй регистр 10 кода операции 9 Установка второготриггера 12 управления в единичноесостояние 13 Запись С на второй регистр 9 операнда 15 Установка второго триггера 12 управления в единичное состояние Запись А в блок 5и ;= в блок 1 сравнения приоритетов Установка второготриггера 12 управления в нулевое состояние Сравнение приоритетов:= и в блоке 1сравнения приоритетов Запись := в блок 2 Проверка состояния второго триггера 12 управления Запись В в блоки х в блок 1 сравне ния приоритетов1Установка второготриггера 12 управления в.нулевоесостояние . Сравнение приоритетов х и := в блоке 1сравнения приоритетов Запись х в блок 2 Проверка состояниявторого триггера 12управления 22Продолжение таблицы943729 23 18 19 Запись Е на второй Сравнение приоритетоврегистр 9 операнда + и х в блоке 1 сравнения приоритетов 20 Запись на второй Проверка состояния перрегистр 10 кода вого триггера 11 управ- операции ления 21 23 Анализ числа в первомрегистре 8 операнда Запись + в блок 2 Установка второготриггера 12 управления в единичное состояниеПроверка состояния первого триггера 11 управления Запись С в блок 5 и+ в блок 1 сравненияприоритетов Установка второго триггера 12 управления в нулевое состояние Запись х из блока 2 впервый регистр 3 кодаоперации Установка первого триггера 11 управления внулевое состояние Сравнение приоритетов+ и := в блоке 1 сравнения приоритетов Проверка состояния второго триггера .12 управления Проверка состояния первого триггера 11 управ- ления 24Продолжение таблицы Чтение С из блока5 в первый регистр8 операнда Запись С из первогорегистра 8 операндаи кода операций "Засылка" в блок 13 Чтение В из блока 5в первый регистр 8операнда943729 27 28 3 б 39 Запись Е в блок 5 ив блок 1 сравненияприоритетов Установка второготриггера 12 управленияв нулевое состояние Сравнение приоритетов; и + в блоке 1 сравнения приоритетов Проверка состоянияпераого триггера 11управления1Запись + из блока 2в регистр 3 нодаоперации Установка первоготриггера 11 управленияв нулевое состояниеСравнение приоритетов;и:; - в блоке 1 сравнения приоритетов Проверка состояния первого триггера 11 управления 26Продолжение таблицы Запись В иэ первогорегистра 8 операндаи х из первого регистра3 кода операции вблок 13 Анализ результата операции Запись ПрПр в блок 5 Установка первого триггера 11 управления вединичное состояние Чтение ПрПр иэ блока5 в первый регистр8 операнда Анализ значения в пер-вом регистре 8 операнда Чтение Е из блока 5943729 27е ю 40 50 Запись : из блока2 в первый регистр3 кода операции Установка первоготриггера 11 управления в нулевоесостояние 28 Продолжение таблицы 1 тЗапись Е из первогорегистра 8 операндаи + из первого регистра3 кода операции вблок 13 Анализ результата операции Запись ПрПр в блок 5 Установка первого триггера 11 управления вединичное состояние Чтение ПрПр из блока5 в первый регистр 8операнда Анализ числа в первомрегистре 8 операнда Чтение А из блока 5в первый регистр 8операнда Запись А из первогорегистра 8 операндаи:= из первого регистра 3 кода операции вблок 13 Анализ результатаоперации Установка первого триггера 11 управления вединичное состояние943729 3 аход которого соединен с входом первого регистра операнда, второй, третий10 1. Иикропрограммное устройство для анализа программ, содержащее блок сравнения приоритетов, блок 5 стековой памяти операций, первый регистр кода операции, первый блок управления и блок стековой памяти операндов, при этом первые вход и выход блока сравнения приоритетов соединены соответственно с выходом и входом блока стековой памяти операций, а второй выход блока сравнения приоритетов подключен к информационному входу первого регистра кодаБ операции, выход которого соединен с первым входом первого блока управления, первый, выход которого подключен к первому входу. блока стековой памяти операндов, о т л и ч а ю щ е е с я тем, что,с целью увеличения быстродействия устройства, он содержит блок анализа символов, второйблок, управления, первый и второй регистры операнда, второй регистр кода операции, первый и второй триггеры управления и блок буферизации команд, причем информационный вход устройства соединен с информационным входом блока анализа символов, зе первый .и второй информационные выходы которого подключены соответственно к входам второго, регистра операнда и второго регистра кода операции, управляющий вход - к нулевому выходу второго триггера управления, а первый и второй управляющие выходы - соотзетственно к единичному входу второго триггера управления и выходу управления приемом символов 4 Е устройства, переый, второй и третий входы второго блока управления сое- динены соответственно с единичными выходами первого и второго триггеров управления и третьим выходом блока сравнения приоритетов, а первый,второй, третий, четвертый и пятый выходы .второго блока управления подключены соответственно к вторым входам блока сравнения приоритетов и блока стекоеой памяти операндов, нулевым входам первого и второго триггеров управления и управляющему входу блока стековой памяти операций, третий вход блока сравнения приоритетов сое 55 динен с выходом второго регистра кода операции, выход второго регистра операнда подключен к третьему входу блока стекоеой памяти операндов, выи четвертый входы первого блока управления подключены соответственно к выходу первого регистра операнда, нулевому выходу первого триггера управления и первому управляоцему выходу блока буферизации команд, второй, третий, четвертый, пятый и шестой выходы первого блока управлениясоединены соответственно с. единичнымвходом первого триггера управления, управляющими входами первого регистра операнда и первого регистра кодаоперации, первым управляоцим и первыминформационным входами блока буферизации команд, второй и третий инфор" мационные входы которого подключены соответственно к выходам первого регистра операнда и первого регистра кода операции, вход управления чтением команд устройства соединен с вторым управляющим входом блока буферизации команд, информационный выход и второй управляющий выход которого подключены соответственно к информационному выходу и выходу управления выдачей команд устройс 1 ва2 Устройство по п.1, о .т л и ч аю щ е е с я тем, что, первый блок управления содержит регистр адреса, память микропрограмм, регистр микро- команды, дешифратор микроопераций, узел элементов И, коммутатор адреса перехода и генератор синхроимпульсов, причем к первому входу блока подключен первый вход регистра адреса, выход которого соединен с входом памяти микропрограмм, вход регистра микрокоманды подключен к выходу памяти микропрограмм, первый выход - ко входу дешифратора микроопераций, а второй выход - к первому входу коммутатора адреса. перехода, выход которого соединен с вторым входом регистра адреса, а к второму, третьему и четвертому входам блока подключены второй, третий и четвертый входыкоммутатора адреса перехода, выход генератора синхроимпульсов соединен с управляющими входами регистра адреса, памяти микропрограмм и узла элементов И, вход которого подключен к выходу дешифратора микроопераций, а выходы - к первому, второму, третьему, четвертому, пятому и шестому выходам блока.3. Устройство по п.1, о т л и ч а 1 ю щ е е с я тем, что второй блок9"3729 31управления содержит регистр адресапамять микропрограмм, регистр микро,команды, дешифратор микроопераций,узел элементов И, коммутатор адресаперехода и генератор синхроимпуль"сов, причем к третьему входу блокаподключен первый вход регистра адреса , выход которого соединен с вхоом памяти микропрограмм, вход регистра микрокоманды подключен к вы фходу памяти микропрограмм, первыйвыход - к входу коммутатора адресаперехода, выход которого соединен свторым входом регистра адреса, а кпервому и второму входам блока подключены второй и третий входы коммутатора адреса перехода, выход генератора синхроимпульсов соединен суправляющими входами регистра адреса, памяти микропрограмм и узлаэлементов И, вход которого подключенк выходу дещифратора микроопераций,а выходы - к первому, второму, третьему, четвертому и пятому выходамблока.25Устройство по п.1, о т л и ч аю щ е е с я тем, что блок анализасимволов содержит входной регистр,дешифратор, два узла элементов И,элемент ИЛИ, триггер анализа, элемент И и три линии задержки, причеминформационный вход блока соединенс входом входного регистра, выходкоторого подключен к входу дещифратора и первым входам первого и второгоЗ 5узлов элементов И, выходы которыхсоединены с первым и вторым информационными выходами блока, первый выход дешифратора подключен к управляющему входу второго узла элементовИ и первому входу элемента ИЛИ, авторой выход дещифратора соединенс управляющим входом первого узлаэлементов И,. вторым входом элемента ИЛИ и первым управляющим выходом 45блока, единичный вход триггера анализа подключен к выходу элемента ИЛИ,а . единичный выход - к входу первойлинии задержки, выход которой соединен с первым входом элемента И, управляющий вход блока подключен квторому входу элемента И, выход которого соединен с входами второй итретьей линий задержки и вторымуправляющим выходом блока, выход вто55рой линии задержки подключен к нулевому входу триггера анализа, а третьей линии задержки - к управляющемувходу входного регистра,325. Устройство по п.1, о т л и ч а,ю щ е е с я тем, что блок буферизации команд содержит регистр команд,па- мять команд, элемент ИЛИ,два узла элементов И, счетчик адреса записи, схему сравнения, счетчик адреса чтения, коммутатор, триггеры блокировки записи и чтения, триггер занятости и выходной регистр, причем первый, второй и третий информационные входы блока соединены с первым, вторым и третьим входами регистра команд, выход которого подключен к первому входу памяти команд, первый и второй управ-: ляющие входы блока соединены с первым и вторым управляющими входами коммутатора, первый и второй управляющие,выходы которого подключены к первому и второму управляющим выходам блока, первый, второй, третий и четвертый входы коммутатора соединены соответственно с выходами триг" гера блокировки записи, триггера блокировки чтения, триггера занятости и схемы сравнения, первый, второй, третий, четвертый и пятый выходы коммутатора подключены соответственно к второму и третьему входам памяти команд, входам счетчиков адреса за" писи и чтения и управляющему входу выходного регистра, выход счетчика адреса записи соединен с первым вхо- дом схемы сравнения и первым входом первого узла элементов И, второй вход которого подключен к первому выходу коммутатора, а выход - к первому входу элемента ИЛИ, выход счетчика адреса чтения соединен с вторым входом схемы сравнения и первым входом второго узла элементов И, второй вход которого подключен к второму выходу коммутатора, а выход - к второму входу элемента ИЛИ, выход которого сое 1 динен с четвертым входом памяти команд, вход выходного регистра подклю 1 чен к выходу памяти команд, а выходк информационному выходу блока.6. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок сравнения . приоритетов содержит постоянную память и регистр адреса, причем первый, второй и третий входы, блока подключены соответственно первому информаци" онному входу перйому управляющему входу и второму информационному входу регистра адреса, первый, второй и третий выходы которого соединены соответственно с первым и вторым выходами блока и адресным входом постоянной памяти, информационный выход ко943729 торой подключен к третьему выходублока, а второй вход блока соединенс входом разрешения считывания постоянной памяти. Источники информации,принятые во внимание при экспертизе34 1. Авторское свидетельство СССР И 209040, кл. 6 06 Г 9/00, 1968. 2. Авторское свидетельство СССР й 519715, кл. 6 06 Г 15/04, 1976. 3 3. Авторское свидетельство СССР М 583435, кл. С 06 Г 9/16, 19773 94372ной памяти, а выход формирователяфункциональных сигналов является пер.вым выходом устройства, первый и вто.рой блоки стековой памяти и блоксравнения приоритетов символов, причем выход формирователя функциональных сигналов соединен с первыми входами. второго блока стековой памятии блока сравнения приоритетов символов, второй вход и первый и второй цвыходы которого соединены соответственно с выходом и входом первого блока стековой памяти и со входом регистра кода операций, третийвход блока сравнения приоритетовсимволов, второй вход и выход второго блока стековой памяти являютсясоответственно первым и вторым входами и вторым выходом устройства 3.В этом устройстве выполняется запись операндов в стек операндов,анализ приоритета очередного функционального символа программы и Формирование последовательности управляющих сигналов.для выполнения операции, если это позволяет приоритетсимвола, При выполнении операции ре.зультат записывается в стек операндов и происходит переход к анализуприоритета очередного Функционального символа. Все эти действиявыполняются последовательно,что увеличивает время выполнения программы.Цель изобретения - повышениебыстродействия устройства и сокращение времени выполнения программ,записанных на алгоритмических языках,Поставленная цель достигаетсятем что в устройство, содержащееблок сравнения приоритетов, блокстековой памяти операций, первый ре-.гистр кода операции, первый блокуправления и блок стековой памятиоперандов, при этом первые вход и45выход блока сравнения приоритетовсоединены соответственно с выходоми входом блока стековой памяти операций, а второй выход блока сравнения приоритетов подключен к информа Вционному входу первого регистра ко. да операции, выход которогд соединенс первым входом первого управления,, первый выход которого подключен кпервому входу блока стековой памяти 55операндов, введены блок анализа сим,волов, второй блок управления, первыйи второй регистры операнда, второй 9, Срегистр кода операции, первый и второй триггеры упоавления и блок буферизации команд, причем информационный вход устройства соединен с информационным входом блока анализа символов, первый и второй информационный выходы которого подключены соответственно ко входам второго регистра операнда и второго регистракода операции, управляющий вход -к нулевому выходу второго триггерауправления, а первый и второй управляющие выходы - соответственно к единичному входу второго триггера управ.пения и выходу управления приемомсимволов устройства первый второй итретий входы второго блока управления соединены соответственно с единичными выходами первого и второготриггеров управления и третьим выходом блока сравнения приоритетов, апервый, второй, третий, четвертыйи пятый выходы второго блока управления подключены соответственно ковторым входам блока сравнения приоритетов и блока стековой памяти операндов, нулевым входам первого и второго триггеров управления и управляющему входу блока стековой памятиопераций, третий вход блока сравненияприоритетов соединен с выходом второго регистра кода операции, выход второго регистра операнда подключен ктретьему входу блока стековой памятиоперандов, выход которого соединенсо входом первого регистра операнда,второй, третий и четвертый входы пер.ваго блока управления подключены соответственно к выходу первого регистра операнда, нулевому выходу первоготриггера управления и первому управляющему выходу блока буферизации команд, второй, третий, четвертый, пятый и шестой выходы первого блокауправления соединены соответственно сединичным входом первого триггерауправления, управляющими входамипервого регистра операнда и первогорегистра кода операций, первйм управ.ляющим и первым информационным входами блока буферизации команд, второй и третий информационные входыкоторого подключены соответственно квыходам первого регистра операнда ипервого регистра кода операции, входуправления чтением команд устройствасоединен со вторым управляющим входом блока буферизации команд, информационный выход и.второй управляю 9437295 9437 щий выход которого подключены соответственно к информационному выходу и выходу управления выдачей команд УстРойства.При этом первый блок управления з содержит регистр адреса, память микропрограмм, регистр микрокоманды, дешифратор микроопераций, узел элементов И, коммутатор адреса перехода и генератор синхроимпульсов, причем 0 к первому входу блока подключен первый вход регистра адреса, выход которого соединен со входом памяти микропрограмм , вход регистра микрокоманды ,подключен к выходу памяти микропро грамм, первый выход - ко входу дешифратора микроопераций, а второй выход - к первому входу коммутатора адреса ,а ко второму, третьему и четвертому входам блока подключены вто рой третий и четвертый входы коммутатора адреса перехода, выход генератора синхроимпульсов соединен с управляющими входами регистра адреса памяти микропрограмм и узла элемен тов И, вход которого подключен к выходу дешифратора микроопераций, а выходы " к первому, второму, третьему, четвертому, пятому и шестому выходам блока.Второй блок управления также содержит регистр адреса, память микропрограмм, регистр микрокоманды,дешифратор микроопераций, узел элементов И, коммутатор адреса перехода и35 генератор синхроимпульсов, причем к третьему входу блока подключен первый вход Р=гистра адреса, выход которого соединен со входом памяти микропрограмм, вход регистра микро 40 команды подключен к выходу памяти микропрограмм, первый выход - к входу дешифратора микроопераций, а второй выход " к первому входу коммутатора адреса перехода выход коФ 4 торого соединен со вторым входом регистра адреса, а к первому и второму входам блока подключены второй и третий входы коммутатора адреса перехода,. выход генератора синхроимпульсов соединен с управляющими вхоЮ дами регистра адреса, памяти микропрограмм и узла элементов И, вход которого подключен к выходу дешифратора микроопераций, а выходы - к первому, второму, третьему, четверто- фф му и пятому выходам блока.Кроме того, блок анализа символов содержит входной регистр, дешиф 29 6ратор, два узла элементов И, элементИЛИ, триггер анализа, элемент И и три линии задержки, причем информационный вход блока соединен со входом входного регистра, выход которого подключен ко входу дешифратора и первым входам первого и второго узлов элементов И, выходы которых соединены с первым и вторым информационными выходами блока, первый выход дешифратора подключен к управляющему входу второго узла элементов.И и первому входу элемента ИЛИ,а второй выход дешифратора соединен с управляоцим входом первого узла элементов И, вторым входом элемента ИЛИ и первым управляющим выходом блока, единичный вход триггера анализа подключен к выходу элемента ИЛИ, а единичный выход - к входу первой линии задержки, выход которой соединен с первым входом элемента И, управляющий вход блока подключен к второму входу элемента И, выход которого соединен со входами второй и третьей линий за держки и вторым управляющим выходом блока, выход второй линии задержки подключен к нулевому входу триггера анализа, а третьей линиизадержки - к управляющему входувходного регистра.Причем блок буФеризации команд содержит регистр команд, память команд, элемент ИЛИ, два узла элементов И, счетчик адреса записи, схему сравнения, счетчик адреса чтения, коммутатор, триггеры блокировки записи и чтения, триггер занятости и выходной регистр, причем певый, вто" рой и третий информационные входы блока соединены с первым, вторым и третьим входами регистра команд,выход которого подключен к первому входу памяти команд, первый и второй управляющие входы блока соединены с первым и вторым управляющими входами коммутатора, первый и второй управляющие выходы которого подключены к первому и второму управляющим выходам блока, первый, второй, тре- тий и четвертый входы коммутатора . соединены соответственно с выходами триггера блокировки записи, триггера блокировки чтения и схемы сравнения, первый, второй, третий,четвертый и пятый выходы коммутатора подключены соответственно ко второ му и третьему входам памяти команд,входам счетчиков адреса записи и9437 чтения и управляющему входу выходного регистра, выход счетчика адреса записи соединен с первым входомсхемы сравнения и первым входом первого узла элементов И; второй вход 5которого подключен к первому выходукоммутатора, а выход - к первомувходу элемента ИЛИ, выход счетчикаадреса чтения соединен со вторымвходом схемы сравнения и первым вхо вдом второго узла элементов И, второй вход которого. подключен ко второму выходу коммутатора, а выходко второму входу элемента ИЛИ, выходкоторого соединен с четвертым входом 15памяти команд, вход выходного регистра подключен к выходу памяти команд,а выход - к информационному выходублока.Кроме того, необходимо.,чтобы блок увсравнения приоритетов содержал постоянную память и регистр адреса, причем первый,: второй и третий входыблока подключены соответственно кпервому информационному входу, перво- Иму управляющему входу и второму информационному входу регистра адреса,первый, второй и третий выходы которогосоединены соответственно с первым ивторым выходами блока и адресным вхо- зфдом постоянной памяти, информационный выход которой подключен к третьемувыходу блока, а второй вход блока соединен со входом разрешения считыванияпостоянной памяти.55Введение в устройство дополнитель".ных блоков и элементов позволяет совместить во времени выполняемые имдействия и, в частности, анализ прио"ритета очередного функционального символа с подготовкой следующего символа и формированием команд для выполнения действий, определяемых предыдущим символом. Кроме того, наличиеблока буферизации команд обеспечиваетсовмещение рабоТы данного устройствас работой процессора, выполняющегозаданные программой действия. В ре зультате увеличивается быстродей 50ствие устройства и сокращается время выполнения программ,На фиг.1 приведена структурная схема микропрограммного устройства анализа программ; на фиг,2 .и 3- примеры реализации первого и второго блоков управления; на фиг.4,5,6 и и 7 - примеры реализации схемы анализа символов, блока буферизации 29 8команд блока сравнения приоритетови коммутатора блока буферизациикоманд,Устройство содержит блоксравнения приоритетов, блок 2 стековойпамяти операций, первый регистр3 кода операции, первый блок 4 управления и блок 5 стековой памятиоперандов ( фиг.1) . Первые вход ивыход блока 1 соединены соответственно с выходом и входом блока 2, авторой выход блока 1 подключен к информационному входу регистра 3. Выход регистра 3 соединен с первымвходом блока 4, первый выход которого подключен к первому входу блока 5.Кроме того, устройство содержит блок6 анализа символов, второй блок 7управления, первый регистр 8 операнда, второй регистр 9.операнда, второй регистр 10 кода операции, первый триггер 11 управления, второйтриггер 12 управления и блох 13 буферизации команд. Информационный вход14 устройства соединен с информационным входом блока 6, первый и второйинформационные выходы которого подключены соответственно ко входам регистра 9 и регистра 10, управляющийвход - к нулевому выходу триггера 12,а первый и,второй управляющие выхо"ды -, соответственно к единичному входу триггера 12 и выходу 15 управленияприемомсимволов устройства, Первый,второй и третий входы блока 7 соединены соответственно с единичными выходами триггера 11, триггера 12 итретьим выходом блока 1. ПервыФ;второй, третий, четвертый и пятый выходы блока 7 подключены соответственно ко вторым входам блока 1 и блока5, нулевым входам триггера 11 и триггера 12 и управляющему входу блока 2.Третий вход блока 1 соединен с выходом регистра 10, Выход регистра 9подключен к третьему входу блока 5выход которого соединен со входомрегистра 8, второй, третий и четвертый входы блока 4 подключены соответственно к выходу регистра 8, нулевому выходу триггера 11 и первомууправляющему выходу блока 13. Второй, третий, четвертый, пятый и шестой выходы блока 4 соединены соответственно с единичным входом триггера11, управляющими входами регистра 3,первым управляющим и первым информационным входами блока 13. Второйи третий информационные входы блока9 9437 13 подключены соответственно к выхо дам регистра 8 и регистра 3. Вход 16 управления чтением команд устройства соединен со вторым управляющим входом блока 13, информационный вы- % ход и второй управляющий выход которого подключены соответственно к инФормационному выходу 17 и выходу 18 управления выдачей команд устройства.Первый блок 4 управления содержит регистр 19 адреса, память 20 микропрограмм, регистр 21 микропрограммы, дешифратор 22 микроопераций, узел 23 элементов И, коммутатор 24 адреса перехода и генаратор 25 син-хроимпульсов (Фиг,2, Первый вход регистра 19 подключен к первому входу блока 4, выход регистра 19,соединен со входом памяти 20. Вход регистра 21 подключен к выходу памяти 20, пер вый выход - ко входу дешифратора 22, а второй выход - к первому входу ком мутатора 24. Выход коммутатора 24 соединен со вторым входом регистра 19, а второй,: третий и четвертый вхо-И ды коммутатора 24 подключены ко второму, третьему и четвертому входам блока 4, Выход генератора 25 соединен с управляющими входами регистра 19, памяти 20 и узла 23, вход которого зе подключен .к выходу дешифратора 22, а выходы - к первому, второму,.третьему, четвертому, пятому и шестому выходам блока 4.3Второй блок 7 управления содержит регистр 26 адреса, память 27 микропрограмм, регистр 28 микрокоманды,дешифратор 29 микроопеарций, узел 30 1элементов И, коммутатор 31 адреса перехода и генератор 32 синхроимпульсов (фиг.3). Первый вход регистра 26 подключен к третьему входу блока 7, а выход регистра 26 соединен со входом памяти 27. Вход регистра45 28 подключен к выходу памяти 27, первый выход - ко входу дешифратора 29, а второй выход - к первому входу коммутатора 31, выход которого соединен со вторым входом регистра 26; а второй и третийЮ входы подключены к первому и второму входам блока 7. Выход гене. ратора 32 соединен с управляющими входами регистра 26, памяти 27 и узла 30 выход которого подключен к выходу дешифратора 29, а выходык первому, второму, третьему, четвертому и пятому выходам блока 7. 29 10Блок 6 анализа символов содержит входной регистр 33, дешифтратор 34, два узла 35,36 элементов И, элемент 37 ИЛИ, триггер 38 анализа, элемент И 39 и три линии 40,41 и 42 задержки (фиг.4). Информационный вход блока 6 соединен со входом регистра 33, выход которого подключен ко входу дешифратора 34 и первым входам узлов 35 и 36. Выходы узлов 35 и 36 соединены с первым и вторым информационными входами блока б, первый выход дешифратора 34 подключен к управляющему входу узла 36 и первому входу элемента 37, а второй выход дешифратора 34 соединен с управляющим входом узла 35, вторым входом элемента 37 и первым управляющим выходом блока 6. Единичный вход триггера 38 под" ключен к выходу элемента 37, а единичный выход - ко входу линии 40 задержки, выход которой соединен с первым входом элемента 39. Управляющий вход блока 6- подключен ко второму входу элемента 39, выход которого соединен со входами линий 41 и. 42- задержки и вторым управляющим выходом блока 6. Выход линии 41 задержкй подключен к нулевому входу триггера 38, а третьей линии 42 задержки - к управляющему входу регистра 33..Блок 13 буферизации команд содержит регистр 43 команд, память 44 ко" манд, элемент 45 ИЛИ, два узла 46, 47 элементов И, счетчик 48 адреса записи, схему 49 сравнения, счетчик 50 адреса чтения, коммутатор 51, триггер 52 блокировки записи, триггер 53 блокировки чтения, триггер ,54 занятости и выходной регистр 55 (фиг,5) Первый, второй и третий информационные входы блока 13 соеди.нены с первым, вторым и третьим вхо- дами регистра 43 команд, выход которого подключен к первому входу памяти 44. Первый и второй управляющие входы блока 13 соединены с первым и вторым управляющими входами коммутатора 51. Первый и второй управляющие выходы коммутатора 51 подключены к первому и второму управ. ляющим выходам блока 13. Первый,второй, третий и четвертый входы коммутатора 51 соединены соответственно с выходами триггера 52, триггера 53, триггера 54 и схемы 49. Первый, вто" рой, третий, четвертый и пятый выходы коммутатора 51 подключены соответственно ко второму и третьему9437 11входам паМяти 44, входам счетчика 48 и счетчика 50 и управляющему входу регистра 55 Выход счетчика 48 соединен с первым входом схемы 49 и первым входом узла 46, второй вход , 5 которого подключен к первому выходу коммутатора 51, выход, - к первому входу элемента 45, Выход счетчика 50 соединен со вторым входом схемы 49 и первым входом узла 47, второй вход 10 которого подключен ко второму выходу коммутатора 51, а выход - ко второму входу элемента 45, выход которого соединен с четвертым входом памяти 44, Вход 56 регистра 55 подключен к выходу памяти 44, а выход 57 - к информационному выходу блока 13Блок 1 сравнения приоритетов содержит постоянную память 58 и регистр 59 адреса(фиг.61, Первый, вто рой и третий входы блока 1 подключены соответственно к первому информационному входу,. первому управляющему входу и второму информационному входу регистра 59. Первый, второй 2 з и третий выходы регистра 59 соединены соответственно с первым и вторым выходами блока 1 и адресным входом памяти 58, информационный выход которой подключен к третьему выходу блока 30 1, а второй вход блока 1 соединен со входом разрешения считывания памяти 58.В состав коммутатора 51 входят триггеры 60-67, элементы И 63,64, 69-77, элемент 65 ИЛИ, и генераторы 62,68 тактовых сигналов. Триггеры 60 и и 61 служат для Фиксации запросов на чтение и запись в блок 13 на время выполнения предыдущего запроса. Запрос на запись поступает из блока 4 на единичный вход триггера 61, а запрос на чтение - со входа 16 устройства на единичный вход триггера 60. Единичные выходы этих триггеров соединены со входами элементов 63 и 64, которые вырабатывают сигналы разрешения соответственно чтения и записи. Входы элемента 63 соединены также с выходом триггера 53, который соответствует состоянию "чтение разрешено" выходом триггера 54, который соответствует состоянию "свободен", и первым выходом генератора 62. Входы элемента 64 подключены к выходу триггера 52, который соответствует состоянию "запись разрешена", выходу триггера 54, который соответствует состоянию "свободен", и ко 29 12второму выходу генератора 62, Генератор 62 используется для временнойселекции поступающих одновременно,запросов на запись и чтение команды.Этот генератор вырабатывает поочеред"но на одном из двух выходов тактовыйсигнал, который разрешает выполнениезаписи или чтения, Интервал между появлением сигналов на выходах генератора 62 выбирается с учетом времени,необходимого для надежного изменениясостояния триггеров 54,60,61,66 и 67. Устройство работает следующим образом,Программа, записанная на алгоритмическом языке, последовательно символ за символом подается на вход 14 устройства 1 см.фиг.1 . При этом 1 очередной символ передается в уст" ройство при появлении разрешающего сигнала на управляющем входе 15 устройства, Предполагается, что програм ма предварительно подвергается лексической обработке и состоит только из символов четырех типов, которые отличаются значением специального признака: идентификаторов переменных, констант, Функциональных символов и разделителей. Символы выполняемой программы поступают из оперативной памяти не показана) на вход схемы 6 анализа. символов, которая выделяет символы двух видов; операнды (идентификаторы переменных и константы) и операции (Функциональные символы и разделители) . Операнд передается схемой 6 на второй регистр 9 операнда, а операция - на регистр 10. После передачи операции на регистр 10 схема 6 устанавливает в единичное состо" яние триггер 12 и переходит в режим ожидания, в котором находится до тех пор, пока триггер 12 не установлен в нулевое состояние. Установка этого триггера в нулевое состояние осуществляется блоком 7. В режиме ожидания схема 6 не разрешает передачу на вход 14 устройства очередного символа программы, используя управляющий выход 15 устройства. После уста- новки триггера 12 в нулевое состояние схема 6 выходит из режима ожидания, выдает сигнал на выход 15 для приема очередного символа, принимает этот символ по входу 14 и начинает его обработку. Установка триггера 12 .в единичное состояние является условием139437 рпя начала очередного цикла работы блока 7 при условии окончания преды" ;дущего цикла его работы. Этот цикл начинается с проверки состояния триггера 11, Если этот триггер находитсяв нулевом состоянии, то блок 7 переходит в режим ожидания, в котором по" стоянно проверяется состояние триг-. гера 11, Когда триггер 11 установится в единичное состояние, блок 7 выдает 10 сигналы, разрешающие запись операнда с регистра 9 в блок 5 и прием кода операции из регистра 10 в блок 1, После завершения этих действий блок 7 устанавливает триггер 12 в нулевое состояние, что позволяет схеме 6 начать анализ очередного символа программы. Одновременно с этим блок 7 выдает в блок 1 сигнал дпя сравнения приоритета очередной операции про граммы на регистре 10 с приоритетом операции в блоке 2 (при начальном включении устройства в блок 2 зано- : сится специальный начальный симвосф . Результат сравнения приоритетов 2 з поступает в блок 7. Если приоритет очередной операции выше приоритета операции в блоке 2, по сигналуиз блока 7. ее код записывается в блок 2 и проверяется состояние триг- зв гера 12. Если он находится в нулевом состоянии, т.е. очередная операция не подготовлена схемой 6, то блок 7 переходит в режим ожидания, в противном случае начинается новый цикл работы блока 7; В том случае, когда приоритет очередной операции ниже или равен приоритету операции в блоке 2, второй блок 7 управления проверяет состояние триггера 11.Если этот триггер находится в нулевом состоянии, то блок 7 переходит в ре" жим ожидания, в котором находится до установки триггера 11 в единичное состояние, После этого блок 7 выдает сигнал для записи кода операции из блока 2 в регистр 3; устанавливает триггер 11 в нулевое состояние и выполняется сравнение приорите тов очередной операции в регистре 10 и следующей операции в блоке 2. Установка триггера 11 в нулевое состояние служит сигналом для начала работы блока 4. Этот блок реализует действия по формированию команд проИ цессора 1,не показан), выполняющего заданные в программе действия;определяемые кодом операции, поступившим в регистр 3. 29 14Рассмотрим работу блока 4 для слу 1 чая процессора с одноадресной системой команд, использующего блок ств( ковой памяти для хранения промежуточных результатов. Выполняемые блокомдействия зависят от числа операндов, необходимых для выполнения операции, код которой находится на регист ре 3. В случае одноместной операции блок 4 выдает сигнал чтения операнда из блока 5 в регистр 8, а затем производится запись содержимого регистров 3 и 8 в блок 13. Содержимое этих регистров образует соответственно операционную и адресную часть команды процессора.Да" лее блок 4 выдает в блок 13 сигнал записи и анализирует вид результата сформированной команды. Если результат является промежуточным, то в блок. 5 выдается сигнал для записи признака промежуточного результата, который указывает, что операнд находится в стеке промежуточных резуль. татов процессора (не показан) После этого триггер 11 устанавливается в единичное состояние, что является сигналом готовности блока 4 к формированию очередной команды. В том случае, когда для выполнения операции требуется более одного операнда, блок 4 выдает сигнал чтения операнда иэ блока 5 в регистр 8. После прие" ма операнда на регистр 8 блок 4 анализирует его значение, Если операнд сопровождается признаком промежуточного результата, то блок 4 выдает сигнал на чтение следующего операнда из блока 5. В противном случае содержимое регистра 8 записывается в качестве адресной части очередной команды в блок 13При этом в качест" ве операционной части команды в блоке 13 по сигналу из блока 4 устанавливается код операции засылки операнда в блок стековой памяти промежуточных результатов процессора, После этого блок 4 выдает сигнал записи в блок 13 и ожидает конца записи. Далее блок 4 выдает сигнал на чтение следующего операнда из блока 5, Эти действия выполняются для всех операндов опера" ции, кроме последнего. Обработка по" следнего операнда выполняется как и в случае одноместной операции.Пример реализации первого блока 4 управления приведен на фиг.2, Этот блок работает следующим образом. На регистр 19 адреса поступает код опе-9437 рации из регистра 3, который интерпретируется как адрес памяти 20 микро программ, начиная с которого записана микропрограмма, обработки данной операции. По этому адресу из памяти. 5 20 выбирается микрокоманда на регистр .21, которая дешифрируется дешифратором 22 в совокупность микроопераций, для выполнения которых узел 23 формирует управляющие сигналы, Эти сигналы 1 О поступают на управляющие входы регистра 3; блока 5, регистра 8, блока 13, на единичный вход триггера 11 и ин,формационный вход блока 13 ( для задания кода операции), Выборка микро программ из памяти 20 осуществляется последовательно, Для изменения этой последовательности используется коммутатор 23 адреса перехода, который формирует адрес очередной микро- щ команды в зависимости от содержимо-, го регистра 8 и состояния триггера 11 и блока 13, который сигнализирует об окончании записи команды. Синхронизация элементов блока 4 обеспечи вается генератором 25. Второй блок 7 управления работает аналогично бло ку 4.Схема б анализа символов работает следующим образом ( фиг,41, При 30 поступлении на регистр 33 кода операнда вырабатывается сигнал на пер. вом выходе дешифратора 34, который обеспечивает передачу кода операнда из регистра 33 через узел 36 в регистр 9 Этот же сигнал через элемент 37 поступает на единичный вход триггера 38, единичный выход которого подключен через линию 40 задержки к первому входу элемента 39, второй выход которого соединен с нулевым выходом триггера 12, На выходе элемента 39 вырабатывается сигнал, разре шающий передачу на вход 14 очередного символа программы. Этот же сигнал 45 разрешает прием информации на регистр 33 и установку в нулевое состояние триггера 38. Необходимые при этом задержки обеспечиваются линиями задержки 41 и 42, причем параметры ли" нии 42 задержки определяют время выборки очередного символа из памяти, а параметры линии задержки 42 - длительность сигяала на входе 15. При поступлении на регистр 33 кода опера 55 ции вырабатывается сигнал на втором выходе деаифратора М, который обеспечивает передачу кода операции из регистра 33 через узел 35 в регистр 29 1610. Этот же сигнал поступает на единичный вход триггера 12 и через элемент 37 на единичный вход триггера 38. Задержанный сигнал с единичного выхода триггера 38 поступает на входэлемента 39 после установки триггера12 в единичное состояние. В результате, разрешающий сигнал на выходе элемента 39 появляется только после установки триггера 12 в нулевое состояние. Это обеспечивает блокировку приема очередного символа программы после приема кода операции до уста-. новки триггера 12 в нулевое состояние,блок 13 буферизации команд 1 Фиг.Цимеет кольцевую адресацию, т.е. послезаписи или чтения в последнюю ячейкупамяти 44 команд осуществляется за пись или чтение в первую ячейку памяти. Для задания адреса ячейки памяти,в которую должна быть записана команда, используется счетчик 48 адреса записи. Йри чтении из памяти используется счетчик 50, Для исключения записи информации в занятые ячейки памяти, а также чтения из пустых ячеек используется схема 49 сравнения. Состояние полного заполнения памяти и отсутствие информации фиксируется триггерами 52 и 53. Триггер 54 занятости используется для разделенияво времени действий по записи и чтению информации. Единичное состояние этого триггера разрешает. запись или чтение команд, а нулевое состояние блокирует обращения к блоку 13, Необходимые сигналы управления вырабатывает коммутатор 51. Элементы 46, 47 и 45 используются для передачи на адресный вход памяти 44 содержимого одного иэ счетчиков. При записиинформации в блок 13 на регистр 43поступают коды операнда и операции.Регистр 43 разбит на две части: впервую часть записывается код операнда из регистра 8, а во вторую - код операции из регистра 3 или блока 4. В начальный момент времени регистр43 устанавливается в нулевое состояние, счетчики 48 и 50 содержат адреспервой ячеики памяти 44, триггер 54- в положение "свободен", триггер 52 в состояние "запись разрешена", триггер 53 - в состояние "чтение запрещено". По сигналу из блока 4 запускается коммутатор 51, триггер 54 изположения "свободен" устанавливается в положение "занят", По адресу на17 9437счетчике 48 производится записьсодержимого регистра 43 в память44. Триггер 53 устанавливается вположение "чтение разрешено", содер,жимое счетчика 49 увеличивается на зединицу, сигнал "Конец записи" коммутатора 51 передается в блок 4, триггер 54 переводится в состояние "свободен",Зались последующих команд производится по сигналу из блока 4 при наличии в памяти 44 свободной ячейки.В противном случае выполнение записиоткладывается до изменения состояния триггера 52, которое имеет мес- нто при чтении команды. Если в памятиимеется свободная ячейка, то следующим шагом является проверка занятости блока 13. В том случае, когда этотблок не занят выполнением чтения, звтриггер 54 устанавливается в состояние "занят", цто блокирует обращение по чтению. Если блок 13 выполняет чтение команды, то запись задерживается до завершения чтения. Последующая запись производится в память ло адресу, который указан всчетчике 48. Одновременно с записьюв память триггер 53 устанавливаетсяв состояние "чтение разрешено" и разрешается чтение из блока 13, затемсодержимое счетчика 48 увелицивается на единицу Если после этого значтение счетчика 48 совпадает со.значением счетчика 50, такое совпадение35фиксируется схемой 49 и свидетельствует о полном заполнении 44, приэтом триггер 52 устанавливается всостояние "запись запрещена", блоки.руя дальнейшую запись в блок 13.Послеэтого, а также если в памяти 4 имеется свободное место, триггер 54 устанавливается в состояние "свободен",а блок 4 получает сигнал окончаниязаписи. Чтение команды из блока 13осуществляется по сигналу из процес.сора, поступающему на вход 16, и возможно только при наличии команд впамяти 44. Если триггер 53 находится в состоянии "чтение запрещено", тозввыполнение чтения задерживается доизменения состояния триггера 53, которое происходит в результате записи в блок 13 очередной команды. Если в памяти 44 имеются команды, то,как и в случае записи, в начале проверяется состояние триггера 54 иблокируются обращения по записипутем установки этого триггера в сос 29 18тояние "занят",После этого осуществляется чтение из памяти 44 по адресу, укаэанном счетчиком 50. Одновременно с чтением из памяти триггер 52 устанавливается в состояние "запись разрешена", т.е. допускается запись в блок 13. Содержимое счетчика 50 увеличивается на единицу. Если после этого значение счетчика 50 совпадает со значением счетчика 48, что означает отсутствие информации в памяти 44, то триггер 53 устанавливается в состояние "чтение запрещено", блокируя последующие считывания из блока 13. После этого, а также, если в памяти 44 имеются команды, триггер 54 устанавливается в состояние "свободно". В процессор с выхода 18 выдается сигнал конца чтения. Считанная из памяти 44 команда поступает на регистр 55, а ,затем с выхода 17 -в процессор.блок 1 сравнения приоритетов содержит постоянную память 58 и регистр 59 адреса (Фиг.6) . Постоянная память содержит информацию о взаимном приоритете всех возможных пар операций. Для этого каждой паре операций языка в памяти 58 поставлено в соответствие слово длиной в одинбит, в котором указано соотношение приоритетов данных операций. Адрес слова в памяти 58 задается регистром 59. В старшие разряды регистра 59 записывается код очеред" ной операции из регистра 10, а младшие -. код операции из блока 2, После записи кодов операции в регистр 59 содержимое. этого регистра выдается на адресный вход памяти 58, на управляющий вход которой поступает сигнал разрешения чтения из блока 7. Считанный код, определяющий соотно" аение приоритетов операций, передается с информационного выхода памяти 5 о в блок 7. В том случае, когда приоритет очередной операции выше приоритета операции в блоке 2, второй блок 7 управления разрешает за-пись кода очередной операции в блок 2, Для этого код младших разрядоврегистра 59 передается в блок 2,акод старших разрядов регистра 59записывается в его младшие разряды. Иладшие разряды регистра59 играют в данном случае роль вершины Ьлока 2 стековой памяти опе": .раций, в которой находится последний записанный в стек код операции. После

СмотретьЗаявка

3221601, 15.10.1980

ПРЕДПРИЯТИЕ ПЯ Г-4677

КОШЕЛЕВ ВЛАДИМИР ПАВЛОВИЧ, СИДОРОВ ЮРИЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: анализа, микропрограммное, программ

Опубликовано: 15.07.1982

Код ссылки

<a href="https://patents.su/21-943729-mikroprogrammnoe-ustrojjstvo-dlya-analiza-programm.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство для анализа программ</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Оснастка для формования корпуса судна из стеклопластика