Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

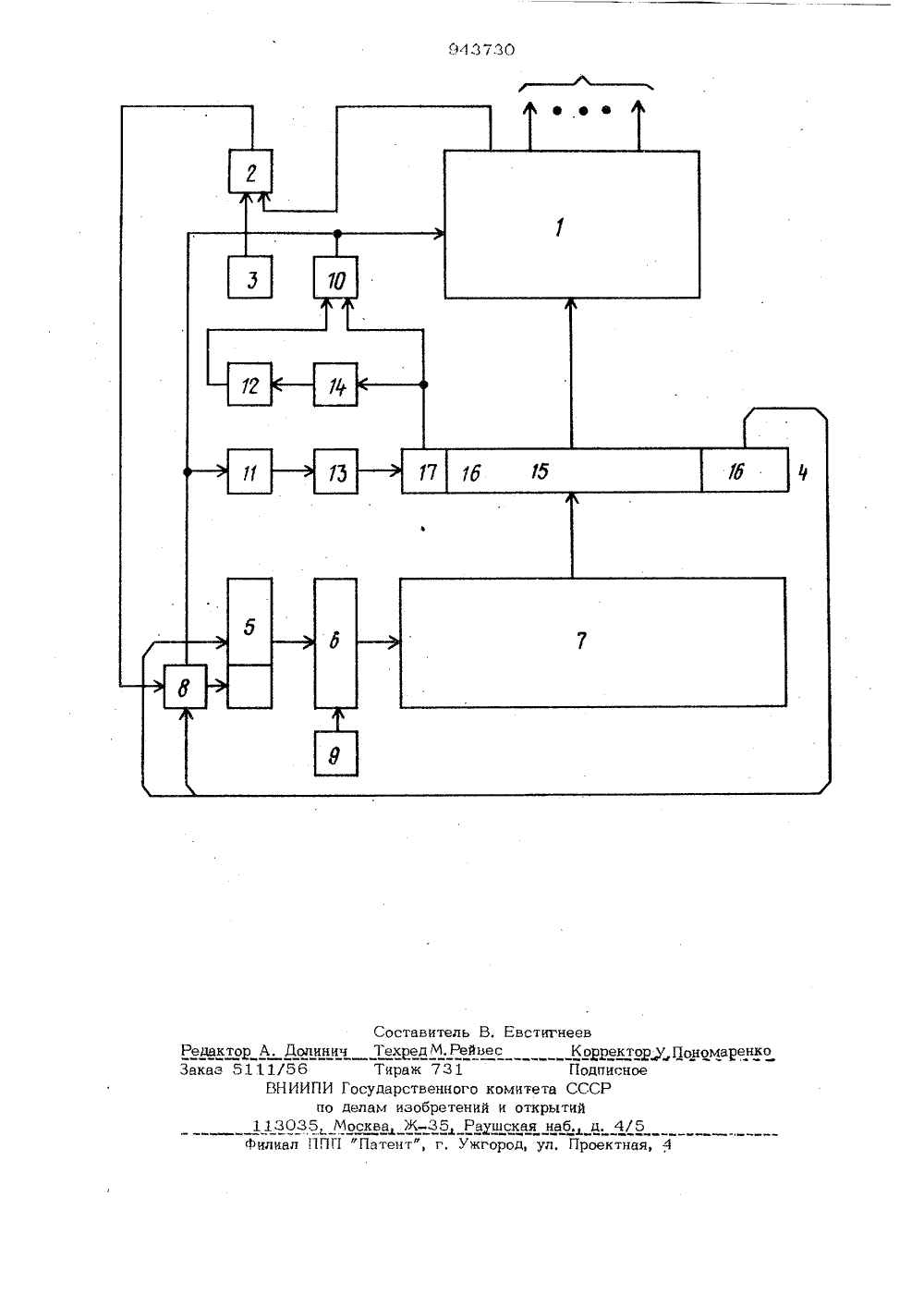

Сеез СоветскмкСфцмапмстмческмкреспублик ОП ИСАНИЕИЗОВРЕТЕН Ия(51)М. Кл,ц 06 Р 9/46 теаударстаснный квмнтет СССР ае ваам нзобратеннй и аткрытнВОрдена Ленина институт кибернетикиАН Украинской ССР(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ 1Изобретение относится к вычислительной технике, в частности к устройстваммикропрограммного управления,Известно микропрограммное устройствоуправления, содержащее дешифратор мик 5рокоманд, регистр микрокоманд, блок памяти микрокоманд, регистр адреса,дешифратор адреса, элементы И, НЕ,схемы задержки, генератор тактовыхимпульсов 1.Однако данное устройство обладаетнедостаточным быстродействием,Наиболее близким к данному изобретению является микропрограммное устройство управления, содержащее дешифратормикрокоманд, выходы которого являютсявыходами устройства, элемент И условийперехода, группу триггеров переходов,регистр микрокоманд, регистр адреса,дешифратор адреса, блок памяти микрокоманд, формирователь адреса перехода,генератор тактовых импульсов, выходомподключенный к управляющему входу дешифратора адреса, выход которого подключен к адресному входу блока памяти микрокоманд, информационным выходом соединенного с информационным входом регистра микрокоманд, первый информационный выход которого соединен с информационным входом дешифратора микро- команд, второй информационный выход регистра микрокоманд соединен с первыми входами формирователя адреса перехода и регистра адреса, выходом соединенного с адресным входом дешифратора адреса, выход формирователя адреса перехода соединен со вторым входом регистра адреса, второй вход формирователя адреса перехода соединен с выходом элемента И условий перехода, первый вход которого соединен с одним из выходов дешифратора микрокоманд, а второй - с выходами группы триггеров переходов 2 .Недостатком этого устройства являются малые функциональные возможности, оПределяемые различной разрядностью информационных и управляющих слов.3 9437Бель изобретения - расширение функциональных воэможностей эе счет унификации длины информационных и управляющих слов.Поставленная цель достигается тем,что устройство содержит элемент И бдокировки, первый и второй элементы НЕ,первый ивторой элементы задержки,выход элемента И блокировки соединен суправляющим входом дешифратора микрокоманд, с третьим входом формирователяадреса перехода и со входом первой схемы задержки, выход которой через первыйэлемент НЕ соединеч с управляющимвходом регистра микрокоменд, третийвыход которого соединен с первым входом.элемента И блокировки и со входом вто-рого элемента задержки, выход которогочерез второй элемент НЕ соединен совторым входом элемента И блокировки,На чертеже представлена блсж-схемаустройстве.Устройство содержит дешифратормикрокоменд 1, элемент И условий.переходе 2, группу триггеров переходов 3,регистр микрокоменд 4, регистр адресе5, дешифратор адреса 6, блок памятимикрокоманд 7, формирователь адресаперехода 8, геиетмтор тактовых импульсов 9, элемент И блокировки 10, первыйэлемент задержки 11, второй элементзадержки 12, первый элемент НЕ 13,второй элемент НЕ 14,Устройство работает следующимобразом,В соответствии с адресом, сформированным нарегистре 5 и сигналом насоответствующем этому адресу выходедешифраторе 6, в моменты времени,определяемыми генератором 9, из блока40памяти макрокоманд 7 считывается очередная микрокоманде не регистр макрокоманд 4. Последний содержит операционные поня 15, адресное поле 16, и спе- .циальный разряд 17, единичное" значение которого указывает микрокоменду45считывания константы из блока 7. Привсех других макрокомандах значение этого разряда равно нулю" и дальнейшаяработа устройства в этом случае заключается в следующем. На выходе ацифре"тора 1 вырабатываются один или несколько элементарных микроопераций в соответствии с кодом микрокоманд, Одновременно с выполнением этих микроопераций с первсе о выхода регистра микроко- Мманд 4 код адреса следующей микрокоманды поступает и запоминается на регистре 5. 30 фУсловные переходы в устройстве осуществляются следующим образом, Если в каком-либо поле регистра 4 записанкод анализа одного ли нескольких триггеров переходов 3, вырабатывающих признаки условий, то сигнал элементарной операции, соответствующий этому коду, анализирует это состояние, поступая на первый вход элемента И 2 условий перех да, на второй вход которого подаются сигнал с выходе анализируемых триггеров 3, Сигнал, вырабатываемый на выходе элемента И 2 при определенномсостоянии указанных выше триггеров, через формирователь адреса перехода 8 меняет состояние определенных разрядов регистра адреса 5.При налички признака микрркоманды считывания констйнты и блока памяти микрокоманд 7, т.е. единицы в специальном разряде 17 регистра 4, микрокоманда отрабатывается в течении двух циклов обращения к блоку 7 (первый цикл - чтение микрокоманды, второй . цикл - чтение константы.В первом цикле после чтения микрокомащщ происходит блокирование дешифретора 1 и. формирование адреса константы. Выходы дешифраторе 1 блокируются путем подачи на его управляющий вход сигнала блокировки с выхода элемента И 10. Через задержки 11 и элемент НЕ 13 к концу первого цикла на управляющий вход регистра микрокоманд 4 подается сигнал блокировки. для формирования адреса константы единичный код третьего выхода регистре микрокоманд через элемент. И 10 вместе с кодом со второго выходе регистра адреса 4 подается на формирователь адреса перехода 8, а затем сформированный адрес запоминается на регистре 5.Адрес константы при этом можетформироваться путем дизьюнкции сигналов первого выхода регистра адреса 4 с сигналов третьего выхода регистра аЪресе.4.Во втором цикле происходит чтение константы и отработка принятой в первом цикле микрокоманды. Для этого в начале второго цикла сигнал с третьего выходе регистра адреса 4 через схему задержки 14 и элемент НЕ 12 поступает на вход элемента И 10, сигнал с выхода которого разблокирует дешифратор 1и задерживается схемой задержки 11 навремя, необходимое для чтения константы.С блока памяти считывается константа.Спустя время задержки на схеме задерж5 0437 ки 11 снимается блокировка со входа регистра 4 и схема 11 готова к приему следующей микрокоманды. На регистре 5 при этом формируется адрес по коду, соответствующему второму выходу регист-Ф ра 4 элемента И 10, так как на выходе, а следовательно, на входе формирователя. адреса перехода 8 устанавливается потек циал нуля .Суммарные затраты времени на микро-й команды считывания констант, определяемое тем, что они выполняются за два цикла блока памяти макрокоманд незначвтельны, так как их количество в реальных микропрограммах, как правило, невелико. 1 Э Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР М 331387, кл. Ь 06 Г 9/16, 1972. 2. Авторское свидетельство СССР,Формула изобретения Микропрограммное устройство управления, содержащее дешифратор микрокоманд, фй выход которого являются выходами устройства, элемент И условий перехода, группу триггеров. переходов, рет истр микрокоманд, регистр адреса, дешифратор адреса, баж памяти макрокоманд, формирователь адре-са перехода, генератор тактовых импульсов, выходом подключенный к управляющем му входу дешифратора адреса, вьисод которого поасиючен к адресному входу блока памяти мнкрокомаа, информационным вы-Зй ходом соединенного с информационнымодом регистра микрокоманд, первый информационный высод которого соединен с инФормациащым входом дешифратора. микрокоманд, второй информационный вы- Н ход регистра микрокоманд соединен с первыми входами формирователя адреса пере 30 Ьхода и регистра адреса, выходом сое.пияенным с адресным входом дешнфратора.мреса, выход формирователя адресйперехода соединен с вторым входомрегистра адреса, второй вход формирователя адреса перехода соединен свыходом элемента И условий перехода,первый вход которого соединен с однимиз высодов дешифратора микрокоманд, авторой - с выходами группы триггеровпереходов, о т л и ч а ю щ е е с я тем,что с целью расширения функциональныхвозможностей за счет унификации длиныинформаонжных и управляющих слов, устройство содержит элемент И блокировки,первый и второй элементы НЕ, первый ивторой элементы задержки, выход элемента И блокировки соединен с управляющимвходом дешифратора микрокоманд, с третьим входом формирователя адреса иереходв и с входом первого элемента зайвржки, выход которого через первый элементНЕ соедвюен с ущевияющим входом регистра микрокоманд, третий выход которого соединен с первым входом элементаИ блокировки и с входом второго элемента задержки, выход которого через второйэлемент НЕ соединен с вторым входомэлемента И блокировки.Составитель В, ЕвстигнеевРедактор А, Долинич ТехцедМ,Рейвес К орректор," ПономаренкоЗаказ 5111/56 Тираж 731 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035 Москва ЖРаушская наб. д, 4/5Филиал ППП фПатент", г, Ужгород, ул. Проектная, 4

СмотретьЗаявка

2124918, 14.04.1975

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР

ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, СИВАЧЕНКО ПЕТР МИХАЙЛОВИЧ, СЫРОВ ВИКТОР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 9/46

Метки: микропрограммное

Опубликовано: 15.07.1982

Код ссылки

<a href="https://patents.su/4-943730-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство для анализа программ

Следующий патент: Устройство для анализа последовательных кодов

Случайный патент: Устройство для подачи воздуха в движущуюся кабину