Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

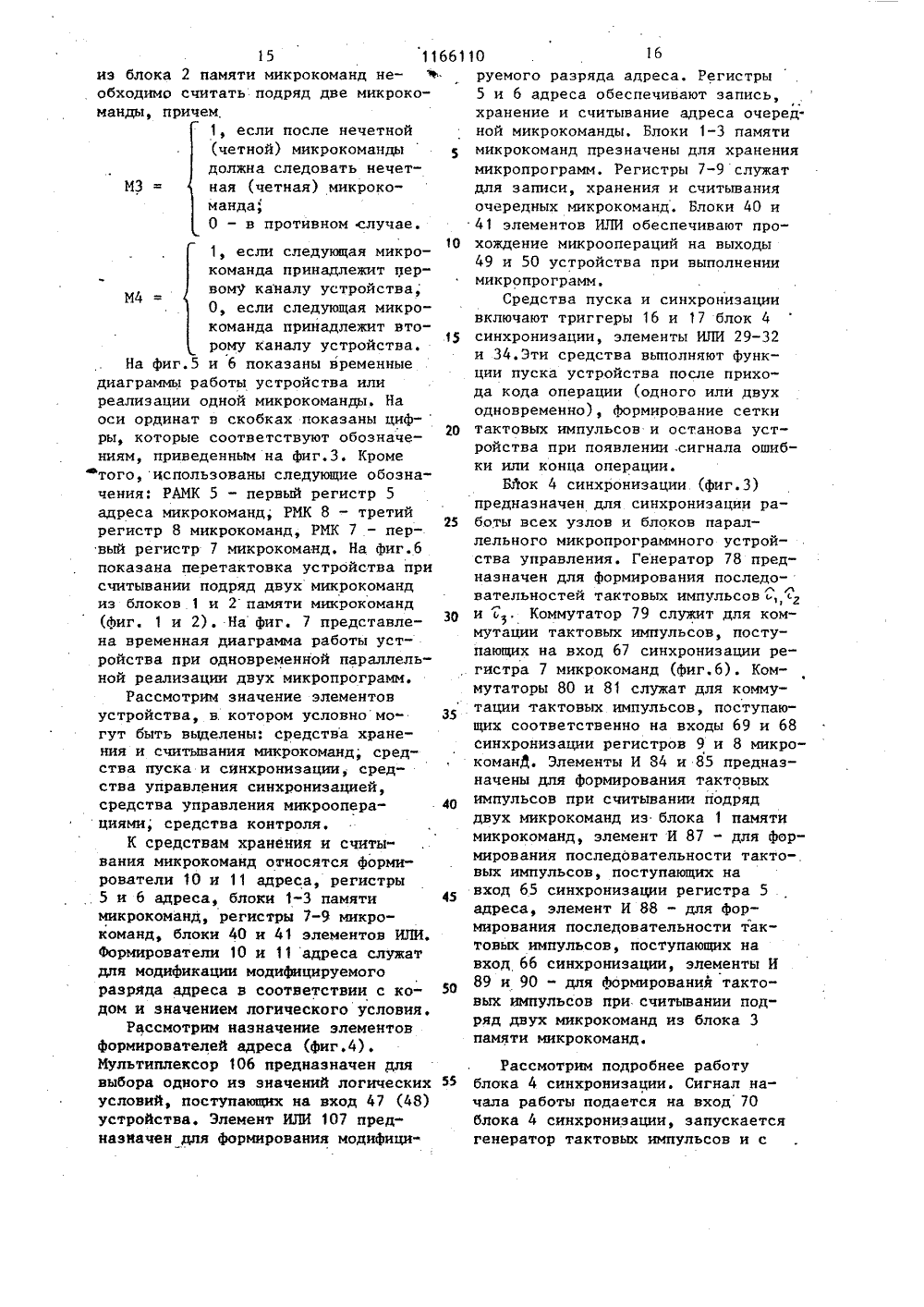

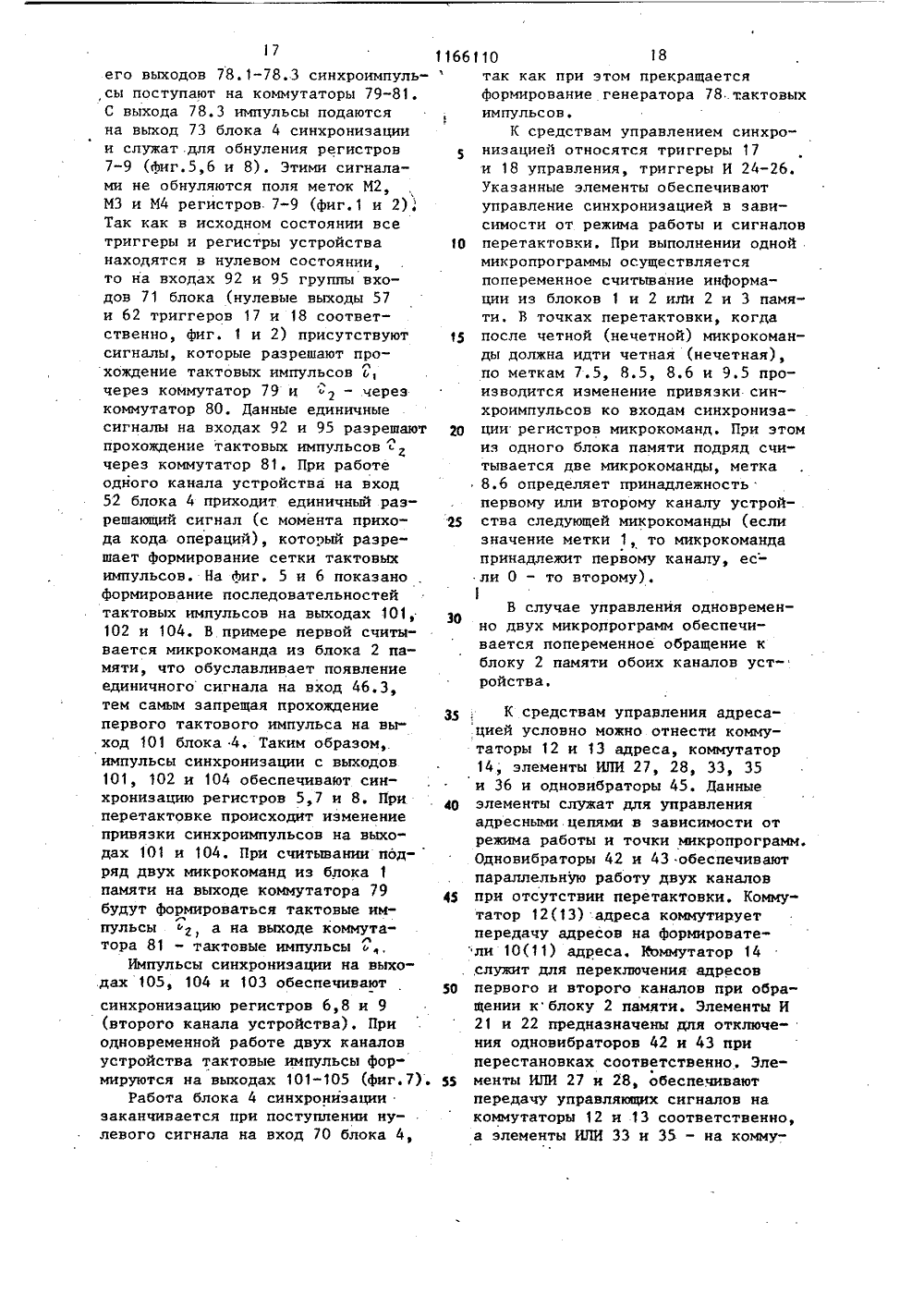

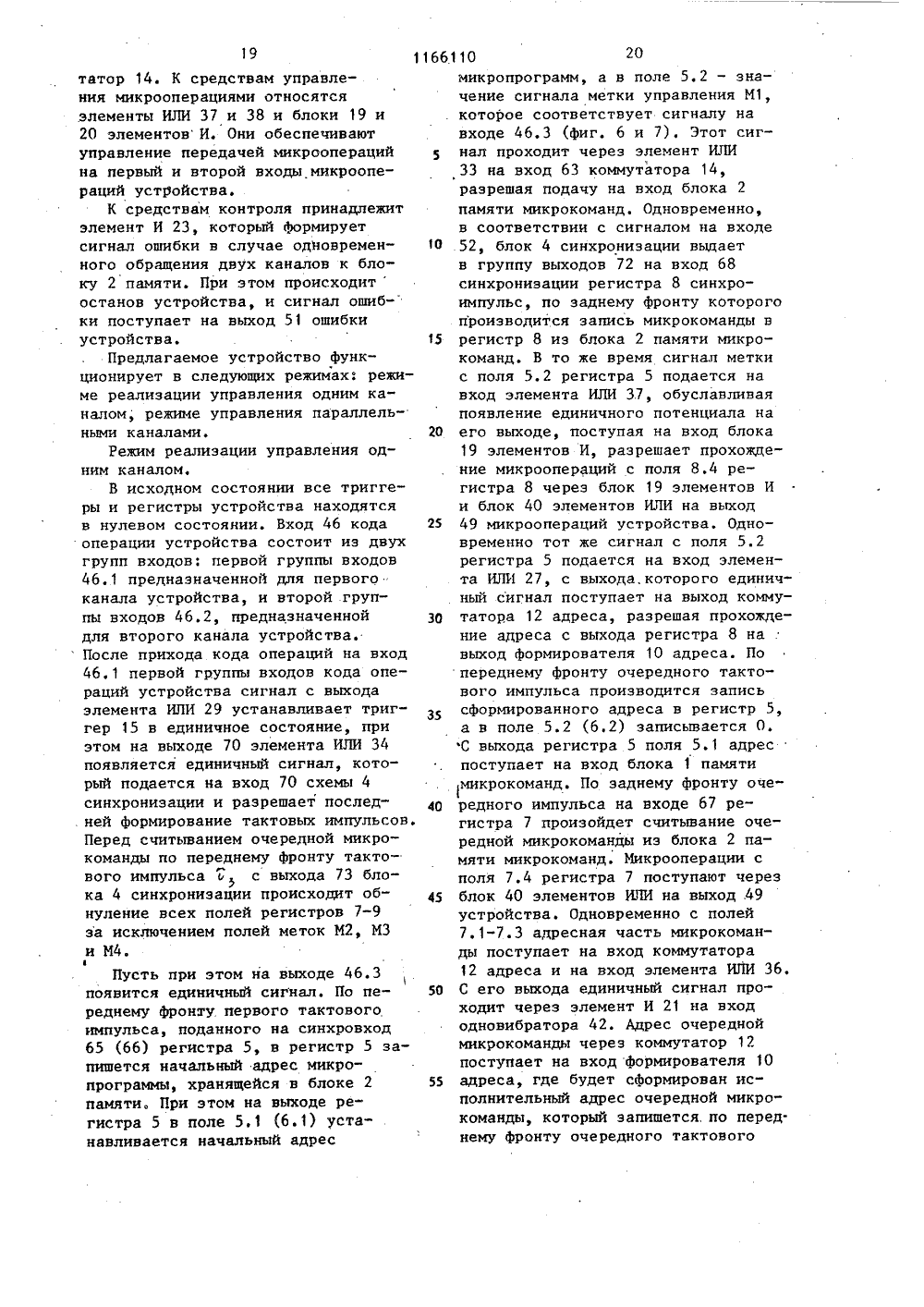

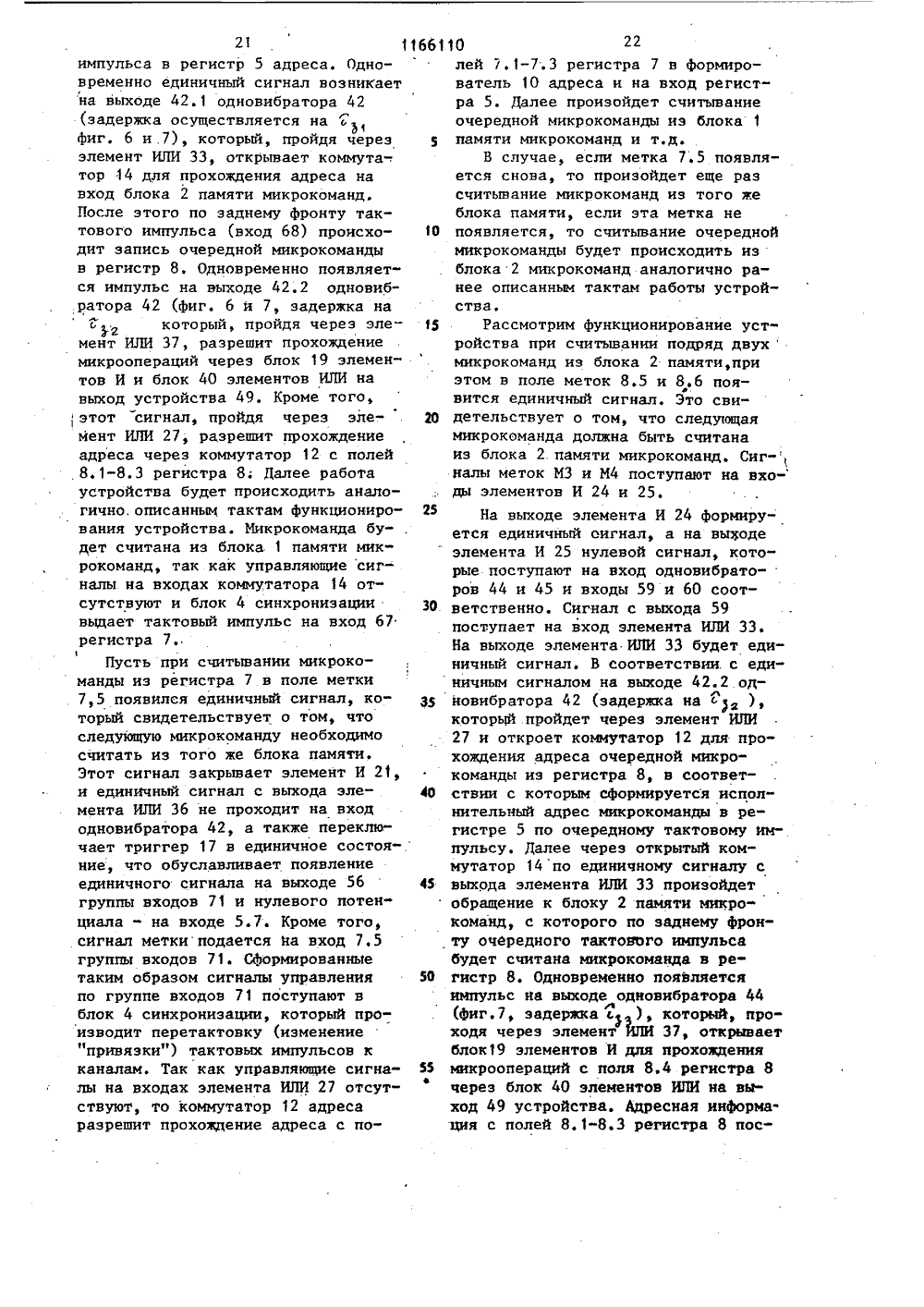

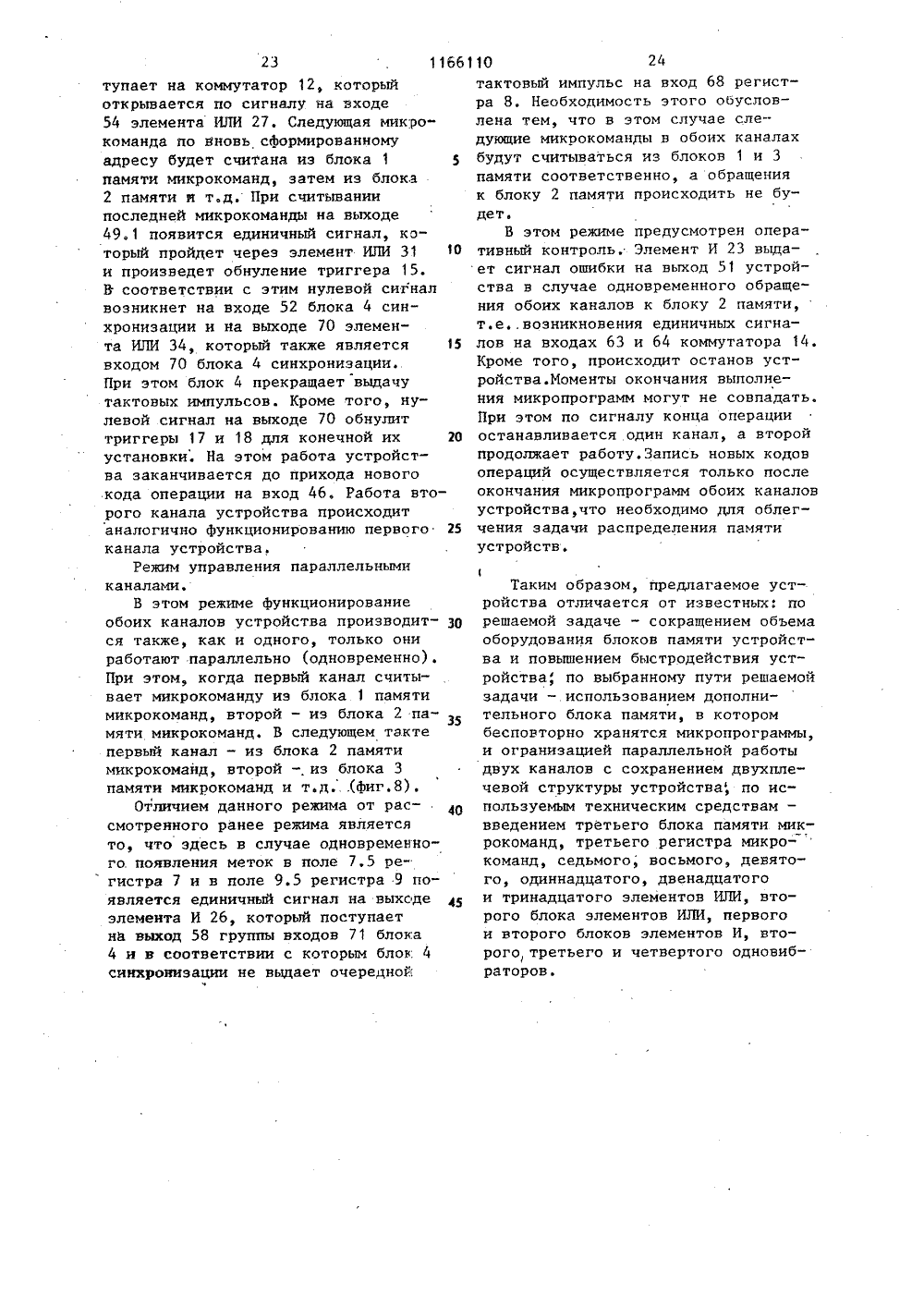

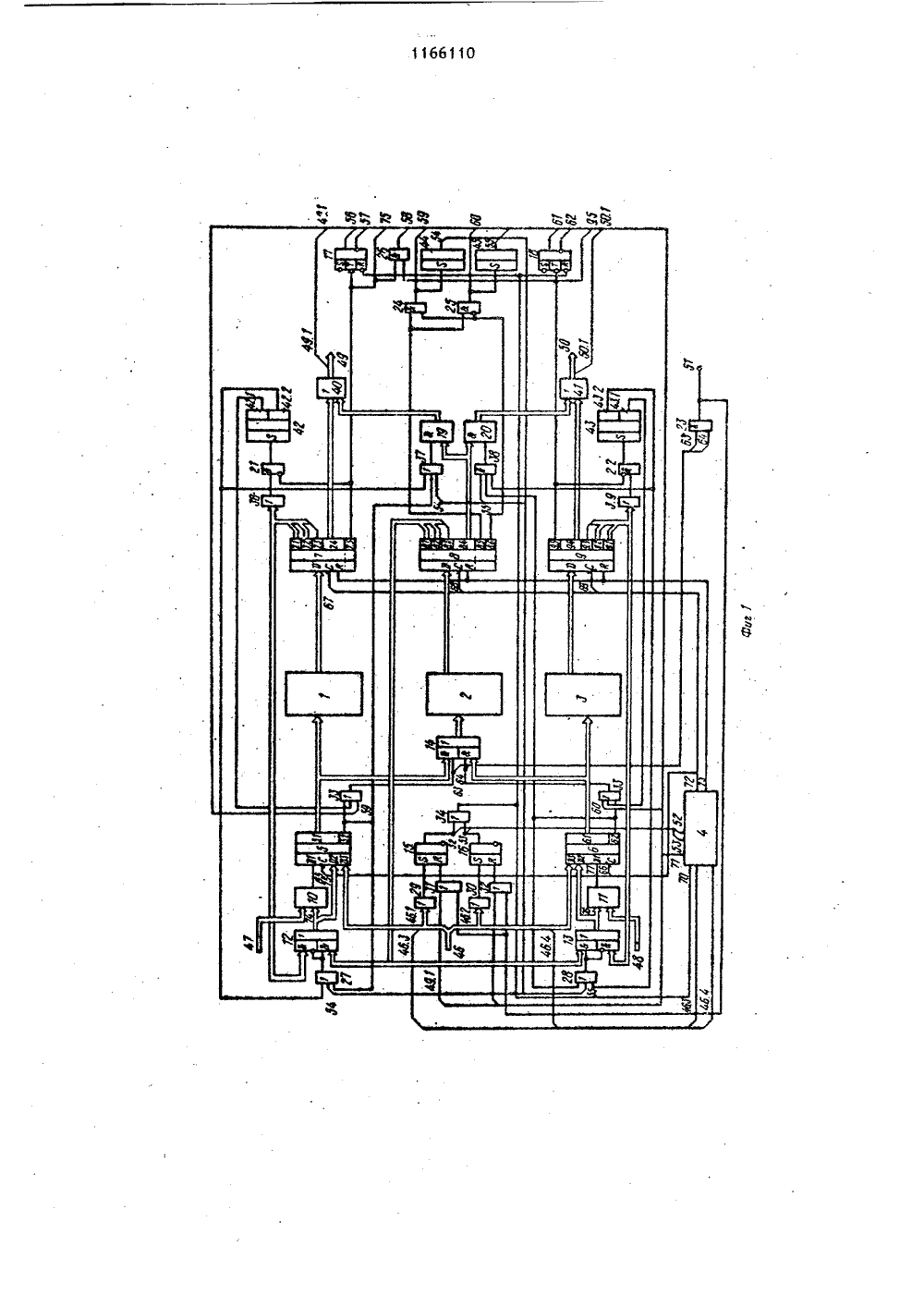

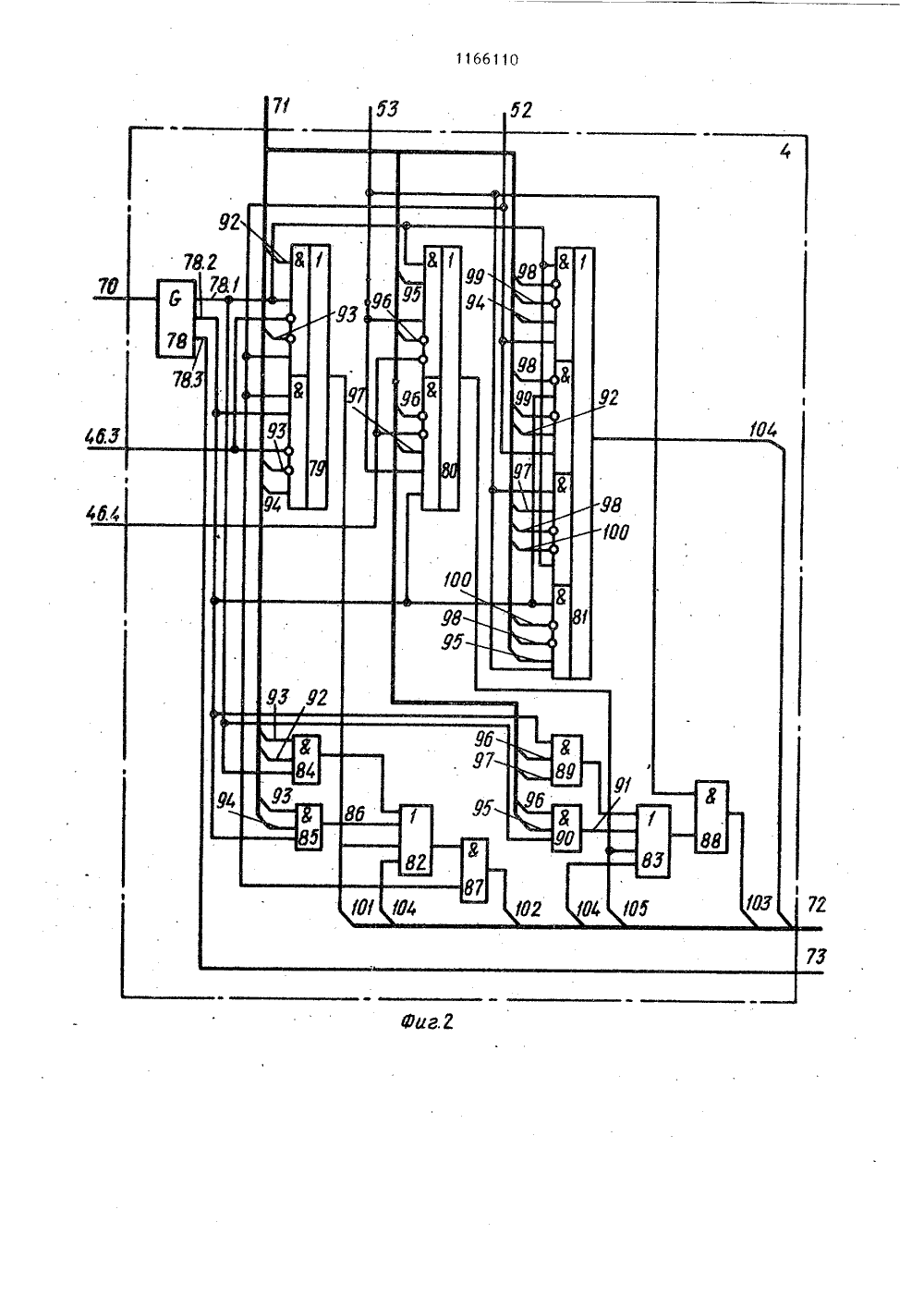

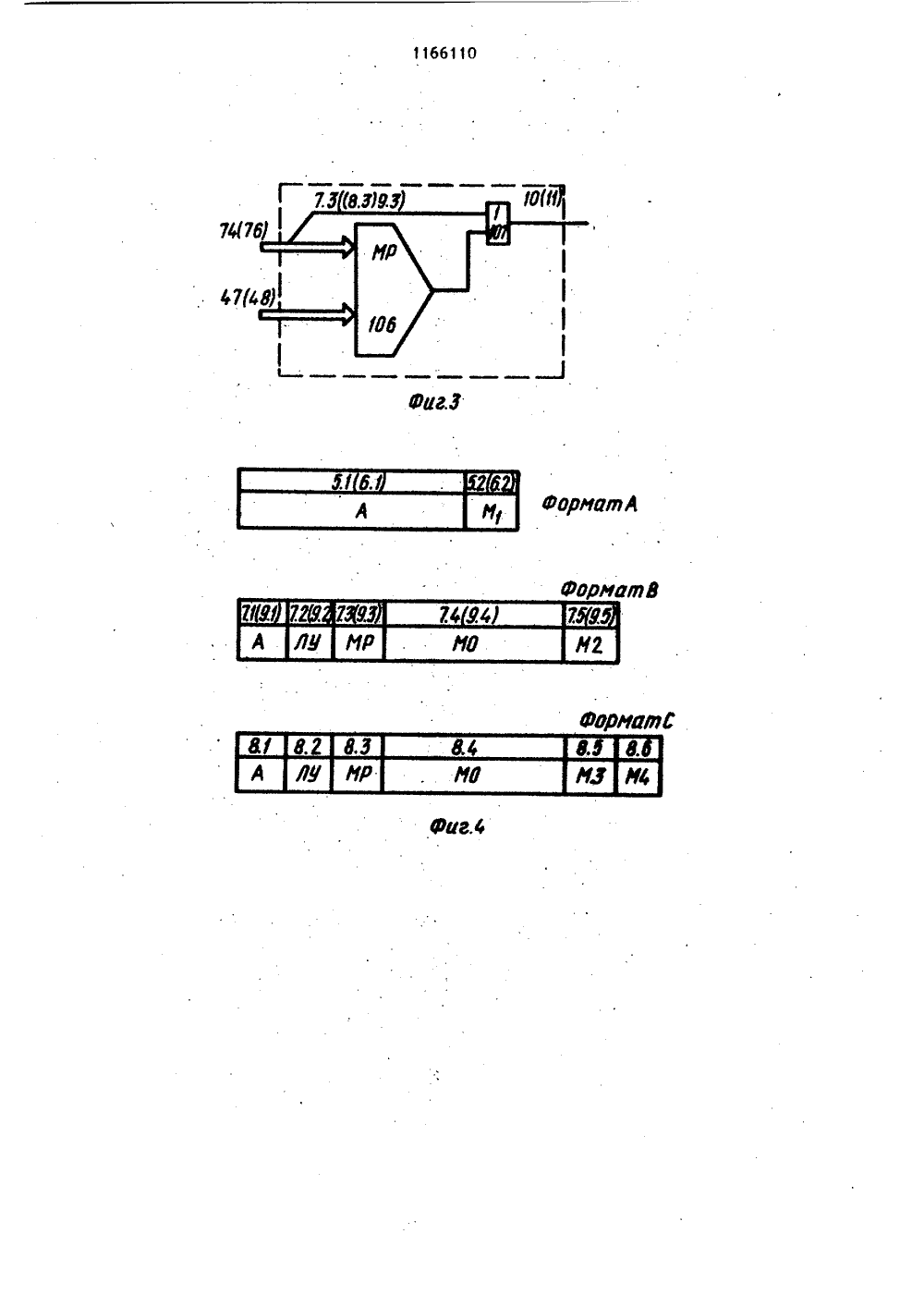

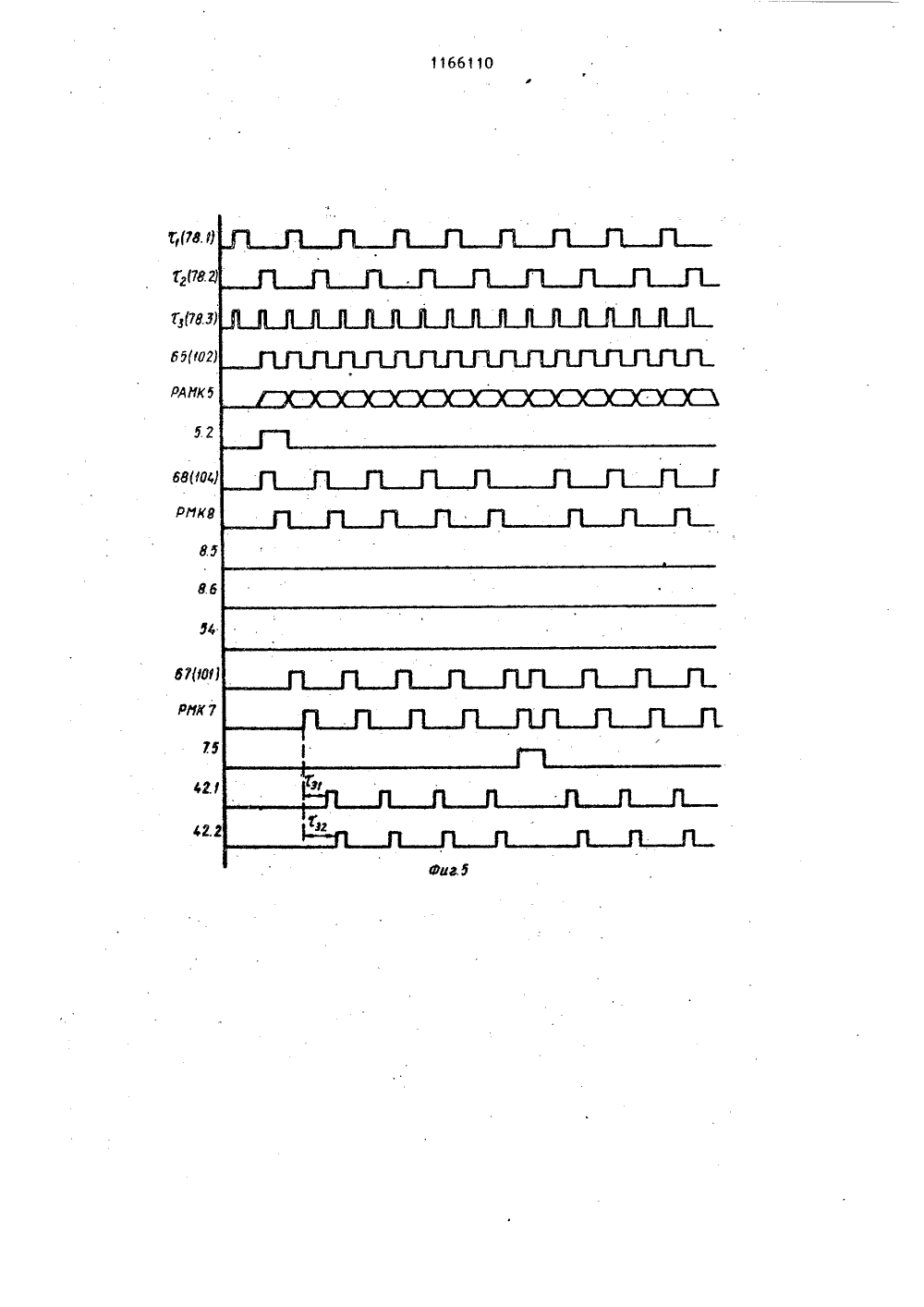

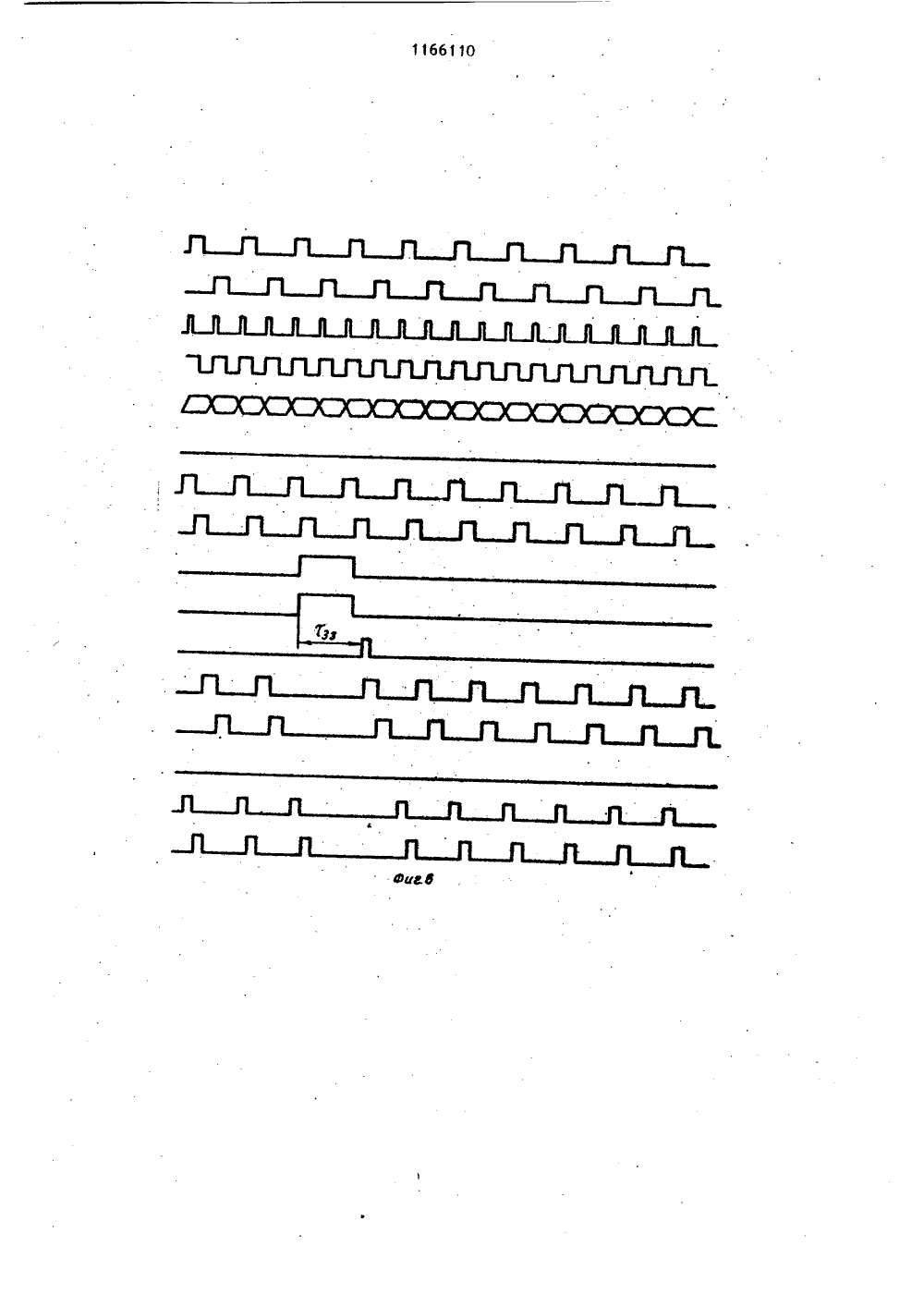

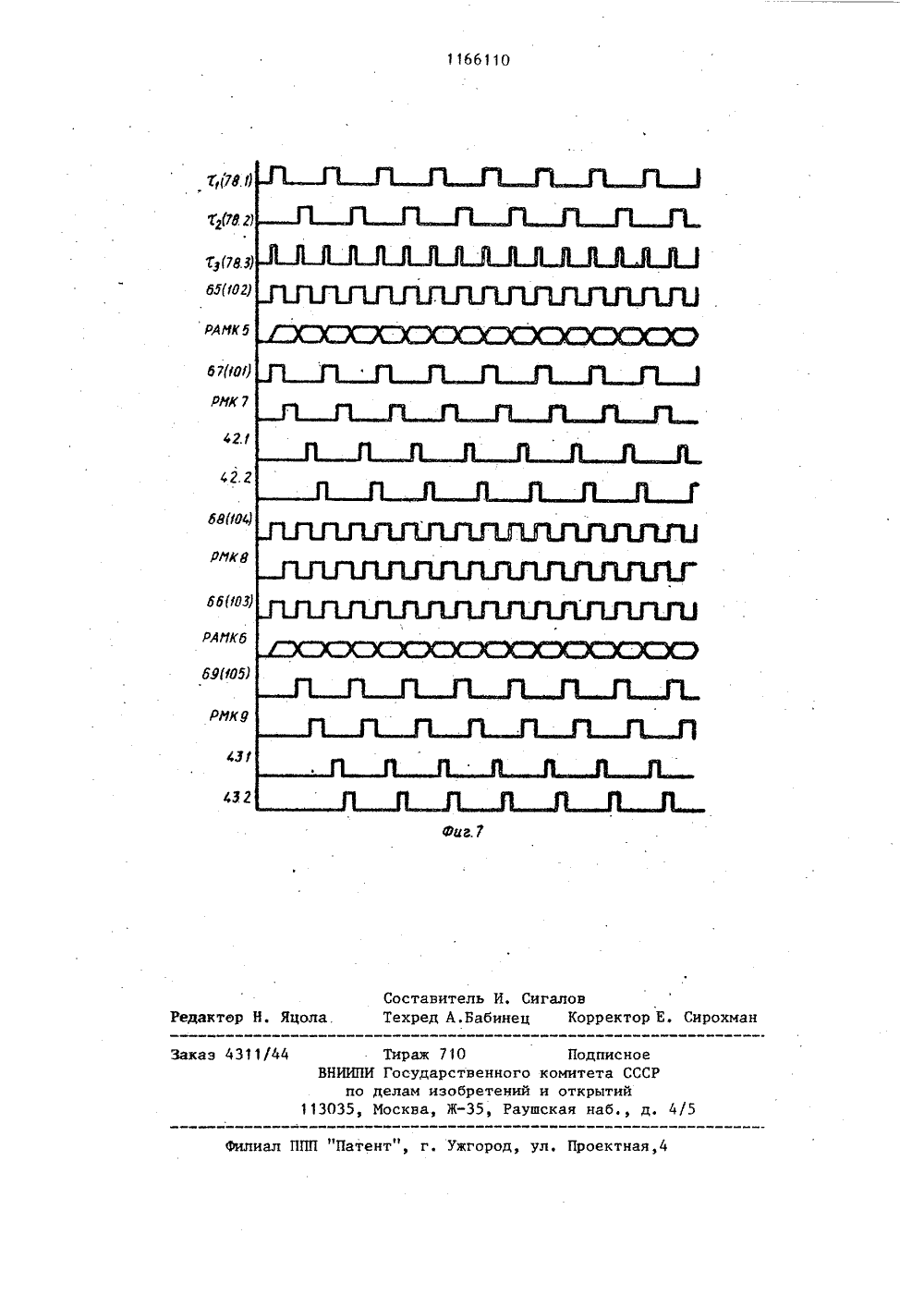

(46) 07.07.85. Б2 В С Ха чен Тимонькиньский,рин опе- вым и ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ОПИСАНИЕ ИЗО юл. У 25(56) 1. Авторское свидетельство СССРк 437072, кл. С 06 Р 9/22, 1974.2. Авторское свидетельство СССРР 451080, кл. С 06 Г 9/22, 1974.3. Авторское свидетельство СССРВ 830383, кл, С 06 Р 9/22; 1981,4. Авторское свидетельство СССР9.1020825, кл. С 06 Р 1/00, 1983(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, первыйи второй регистры адреса, первый ивторой регистры микрокоманд, первыйи второй формирователи адреса, первый и второй коммутаторы адреса,коммутатор, первый одновибратор,первый и второй триггеры пуска,1первый и второй триггеры управления,блок синхронизации, первый, второй,третий, четвертый, пятый, шестойэлементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой элементы И, первый блок элементов ИЛИпервая группа входов кода операцииустройства соединена с первым информационным входом первого регистраадреса и с входом первого элемента ИЛИ, выход которого соединен сединичным входом первого триггерапуска, выход второго элемента ИЛИсоединен с нулевым входом первоготриггера пуска, единичный выход которого соединен с первым входо пуска блока синхронизации, выход третьего элемента ИЛИ соединен с единичным входом второго триггер пуска, вторая группа входов кода рации устройства соединена с пер информационным входом второго регистра адреса, первый вход логических условий устройства соединен с первым входом первого формирователя адреса, выход которого соединен с вторым информационным входом первого регистра адреса, выход четвертого элемента ИЛИ соединен с прямым инверсным управляющими входами пер" вого коммутатора адреса, выходы ко- Я да логических условий и немодифицируемых разрядов адреса которого. соединены соответственно с вторым входом первого формирователя адреса и третьим информационным входом первого регистра адреса, выход второго формирователя адреса соединен с вторыминформационным входом второго регистра адреса, выход пятого элемента ИЛИ соединен с прямым и инверсным управляющими входами второго коммутатора адреса, выходы кода логических условий и немодифи" цируемых разрядов котОрого соединены соответственно с первым входом второго формирователя адреса, и третьим информационным входом второго дюрмирователя адреса, выходы полей адреса ф первого и второго регистров адреса соединены соответственно с входами первого и второго блоков памяти милрокоманд , выходы которых соединены соответственно с информационными входами первого и второго регистров микрокоманд, выход поля микроопера15 11661 из блока 2 памяти микрокоманд необходимо считать подряд две микрокоманды, причем,1, если после нечетной(четной) микрокомандыдолжна следовать нечетная (четная) микрокоманда0 - в противном случае. МЗ = 40 10 1, если следующая микро- команда принадлежит первому каналу устройства, М 4 О, если следующая микро- команда принадлежит вто 15рому каналу устройства.На Фиг.5 и 6 показаны временные диаграммы работы устройства или реализации одной микрокоманды. На оси ординат в скобках показаны циф-ры, которые соответствуют обозначе 20ниям, приведенным на фиг.З. Кроме того, использованы следующие обозначения: РАМК 5 - первый регистр 5 адреса микрокоманд, РМК 8 - третий25 регистр 8 микрокоманд, РМК 7 - первый регистр 7 микрокоманд. На Фиг.6 показана перетактовка устройства при считывании подряд двух микрокоманд из блоков 1 и 2 памяти микрокоманд (Фиг. 1 и 2). На Фиг. 7 представле- З 0 на временная диаграмма работы устройства при одновременной параллельной реализации двух микропрограмм.Рассмотрим значение элементов устройства, в. котором условномо гут быть выделены: средства хранения и считывания микрокоманд, средства пуска и синхронизации, средства управления синхронизацией, средства управления микрооперациями, средства контроля.К средствам хранения и считывания микрокоманд относятся формирователи 10 и 11 адреса, регистры 5 и 6 адреса, блоки 1-3 памяти 45 микрокоманд, регистры 7-9 микро- команд, блоки 40 и 41 элементов ИЛИ, Формирователи 10 и 11 адреса служат для модификации модифицируемого разряда адреса в соответствии с ко дом и значением логического условия,Рассмотрим назначение элементов формирователей адреса (фиг.4), Мультиплексор 106 предназначен для выбора одного иэ значений логических 55 условий, поступающих на вход 47 (48) устройства. Элемент ИЛИ 107 преднаэйачен для формирования модифици 10 16руемого разряда адреса. Регистры 5 и 6 адреса обеспечивают запись, хранение и считывание адреса очередной микрокоманды. Блоки 1-3 памяти микрокоманд презначены для хранения микропрограмм. Регистры 7-9 служат для записи, хранения и считывания очередных микрокоманд. Блоки 40 и 41 элементов ИЛИ обеспечивают прохождение микроопераций на выходы 49 и 50 устройства при выполнении микропрограмм.Средства пуска и синхронизации включают триггеры 16 и 17 блок 4 синхронизации, элементы ИЛИ 29-32 и 34.Эти средства выполняют функции пуска устройства после прихода кода операции (одного или двух одновременно), Формирование сетки тактовых импульсов и останова устройства при появлении, сигнала ошибки или конца операции.БЛок 4 синхронизации (фиг.З) предназначен для синхронизации работы всех узлов и блоков параллельного микропрограммного устройства управления. Генератор 78 предназначен для формирования последов л вательностей тактовых импульсови 7 . Коммутатор 79 служит для ком 5.мутации тактовых импульсов, поступающих на вход 67 синхронизации регистра 7 микрокоманд (Фиг.6). Коммутаторы 80 и 81 служат для коммутации тактовых импульсов, поступающих соответственно на входы 69 и 68 синхронизации регистров 9 и 8 микро- команД. Элементы И 84 и 85 предназначены для формирования тактовых импульсов при считывании йодряд двух микрокоманд иэ блока 1 памяти микрокоманд, элемент И 87 - для формирования последовательности такто-. вых импульсов, поступающих на вход 65 синхронизации регистра 5 адреса, элемент И 88 - для формирования последовательности тактовых импульсов, поступающих на вход 66 синхронизации, элементы И 89 и 90 - для Формирования тактовых импульсов при считывании подряд двух микрокоманд из блока 3памяти микрокоманд.Рассмотрим подробнее работу блока 4 синхронизации. Сигнал начала работы подается на вход 70 блока 4 синхронизации, запускается генератор тактовых импульсов и с1166 10 20 его выходов 78.1-78.3 синхроимпуль сы поступают на коммутаторы 79-81.С выхода 78.3 импульсы подаютсяна выход 73 блока 4 синхронизациии служат.для обнуления регистров7-9 (фиг.5,6 и 8). Этими сигналами не обнуляются поля меток М 2,МЗ и М 4 регистров 7-9 (фиг.1 и 2),Так как в исходном состоянии всетриггеры и регистры устройстванаходятся в нулевом состоянии,то на входах 92 и 95 группы входов 71 блока (нулевые выходы 57и 62 триггеров 17 и 18 соответственно, фиг. 1 и 2) присутствуютсигналы, которые разрешают прохождение тактовых импульсов ь,через коммутатор 79 и- черезкоммутатор 80. Данные единичные сигналы на входах 92 и 95 разрешают прохождение тактовых импульсовчерез коммутатор 81. При работеодного канала устройства на вход 52 блока 4 приходит единичный разрешающий сигнал (с момента прихода кода операций), который разрешает формирование сетки тактовых импульсов. На фиг. 5 и 6 показаноформирование последовательностей 110 18так как при этом прекращается формирование генератора 78.тактовых импульсов.К средствам управлением синхронизацией относятся триггеры 17 и 18 управления, триггеры И 24-26. Указанные элементы обеспечивают управление синхронизацией в зависимости от режима работы и сигналов перетактовки. При выполнении одной микропрограммы осуществляется попеременное считывание информации из блоков 1 и 2 или 2 и 3 памяти. В точках перетактовки, когда после четной (нечетной) микрокоманды должна идти четная (нечетная), по меткам 7.5, 8.5, 8.6 и 9.5 производится изменение привязки синхроимпульсов ко входам синхронизации регистров микрокоманд, При этом из одного блока памяти подряд считывается две микрокоманды, метка 8.6 определяет принадлежность . первому или второму каналу устройства следующей микрокоманды (если значение метки 1, то микрокоманда принадлежит первому каналу, ес- ли 0 - то второму).тактовых импульсов на выходах 101, 50 102 и 104. В примере первой считывается микрокоманда из блока 2 памяти, что обуславливает появление единичного сигнала на вход 46.3, тем самым запрещая прохождение первого тактового импульса на выход 101 блока 4. Таким образом,. импульсы синхронизации с выходов 101, 102 и 104 обеспечивают синхронизацию регистров 5,7 и 8, При перетактовке происходит изменение привязки синхроимпульсов на выходах 101 и 104. При считывании подряд двух микрокоманд из блока 1 памяти на выходе коммутатора 79 будут формироваться тактовые имЪпульсыа на выходе коммута"1л тора 81 - тактовые импульсыИмпульсы синхронизации на выхо.дах 105, 104 и 103 обеспечивают синхронизацию регистров 6,8 и 9 (второго канала устройства). При одновременной работе двух каналов устройства тактовые импульсы формируются на выходах 101-105 (фиг.7)Работа блока 4 синхронизации заканчивается при поступлении нулевого сигнала на вход 70 блока 4,35 40 45 5055 В случае управления одновременно двух микропрограмм обеспечивается попеременное обращение к блоку 2 памяти обоих каналов устройства.К средствам управления адресацией условно можно отнести коммутаторы 12 и 13 адреса, коммутатор 14, элементы ИЛИ 27, 28, 33, 35 и 36 и одновибраторы 45. Данные элементы служат для управления адресными. цепями в зависимости от режима работы и точки микропрограмм, Одновибраторы 42 и 43 -обеспечивают параллельную работу двух каналов при отсутствии перетактовки. Коммутатор 12(13) адреса коммутирует передачу адресов на формирователи 10(11) адреса, Коммутатор 14 ,служит для переключения адресов первого и второго каналов при обращении кблоку 2 памяти. Элементы И 21 и 22 предназначены для отключения одновибраторов 42 и 43 при перестановках соответственно. Элементы ИЛИ 27 и 28, обеспечивают передачу управляющих сигналов на коммутаторы 12 и 13 соответственно, а элементы ИЛИ 33 и 35 - на комму 1166.11020татор 14. К средствам управления микрооперациями относятся элементы ИЛИ 37 и 38 и блоки 19 и 20 элементов И. Они обеспечивают управление передачей микроопераций на первый и второй входы микроопераций устройства.К средствам контроля принадлежит элемент И 23, который формирует сигнал ошибки в случае одиовременного обращения двух каналов к блоку 2 памяти. При этом происходитостанов устройства, и сигнал ошиб- ки поступает на выход 51 ошибки устройства,Предлагаемое устройство функционирует в следующих режимах: режиме реализации управления одним каналом, режиме управления параллельными каналами.Режим реализации управления одним каналом.В исходном состоянии все триггеры и регистры устройства находятся в нулевом состоянии. Вход 46 кода операции устройства состоит из двух групп входов: первой группы входов 46.1 предназначенной для первого канала устройства, и второй группы входов 46,2, предназначенной для второго канала устройства.После прихода кода операций на вход 46.1 первой группы входов кода операций устройства сигнал с выхода элемента ИЛИ 29 устанавливает триг" гер 15 в единичное состояние, при этом на выходе 70 элемента ИЛИ 34 появляется единичный сигнал, который подается на вход 70 схемы 4 синхронизации и разрешает последней формирование тактовых импульсов. Перед считыванием очередной микро- команды по переднему фронту тактового импульса ь с выхода 73 блока 4 синхронизации происходит обнуление всех полей регистров 7-9 за исключением полей меток М 2, МЗи М 4.1Пусть при этом на выходе 46.3 появится единичный сигнал. По переднему фронту первого тактового импульса, поданного на синхровход 65 (бб) регистра 5, в регистр 5 запишется начальный адрес микропрограммы, хранящейся в блоке 2 памяти. При этом на выходе регистра 5 в поле 5.1 (6.1) устанавливается начальный адрес 1 О 15 20 25 30 35 40 45 50 55 микропрограмм, а в поле 5,2 - значение сигнала метки управления М 1,которое соответствует сигналу навходе 46.3 (фиг. 6 и 7), Этот сигнал проходит через элемент ИЛИ33 на вход 63 коммутатора 14,разрешая подачу на вход блока 2памяти микрокоманд, Одновременно,в соответствии с сигналом на входе52, блок 4 синхронизации выдаетв группу выходов 72 на вход 68синхронизации регистра 8 синхроимпульс, по заднему фронту которогопроизводится запись микрокоманды врегистр 8 из блока 2 памяти микрокоманд, В то же время сигнал меткис поля 5.2 регистра 5 подается навход элемента ИЛИ 37, обуславливаяпоявление единичного потенциала наего выходе, поступая на вход блока19 элементов И, разрешает прохождение микроопераций с поля 8.4 регистра 8 через блок 19 элементов Ии блок 40 элементов ИЛИ на выход49 микроопераций устройства. Одновременно тот же сигнал с поля 5.2регистра 5 подается на вход элемента ИЛИ 27, с выхода. которого единичный сигнал поступает на выход коммутатора 12 адреса, разрешая прохождение адреса с выхода регистра 8 на .выход формирователя 10 адреса. Попереднему фронту очередного тактового импульса производится записьсформированного адреса в регистр 5,а в поле 5.2 (6,2) записывается О,С выхода регистра 5 поля 5.1 адреспоступает на вход блока 1 памяти1микрокоманд. По заднему фронту очередного импульса на входе 67 регистра 7 произойдет считывание очередной микрокоманды иэ блока 2 памяти микрокоманд. Иикрооперации споля .4 регистра 7 поступают черезблок 40 элементов ИЛИ на выход .49устройства. Одновременно с полей7.1-7.3 адресная часть микрокоманды поступает на вход коммутатора12 адреса и на вход элемента ИЛИ 36.С его выхода единичный сигнал проходит через элемент И 21 на входодновибратора 42. Адрес очередноймикрокоманды через коммутатор 12поступает на вход формирователя 10адреса, где будет сформирован исполнительный адрес очередной микрокоманды, который запишется. по перед.нему фронту очередного тактового21 1 импульса в регистр 5 адреса. Одно" временно единичный сигнал возникает на выходе 42.1 одновибратора 42(задержка осуществляется на о1 фиг. 6 и .7), который, пройдя через элемент ИЛИ 33, открьвает коммута-. тор 14 для прохождения адреса на вход блока 2 памяти микрокоманд. После этого по заднему фронту тактового импульса (вход 68) происходит запись очередной микрокоманды в регистр 8. Одновременно появляется импульс на выходе 42.2 одновибратора 42 (фиг. 6 и 7, задержка накоторый, пройдя через элемент ИЛИ 37, разрешит прохождение микроопераций через блок 19 элементов И и блок 40 элементов ИЛИ на выход устройства 49. Кроме того, этот сигнал, пройдя через элемент ИЛИ 27, разрешит прохождение адреса через коммутатор 12 с полей 8.1-8,3 регистра 8; Далее работа устройства будет происходить аналогично. описанным тактам функционирования устройства. Микрокоманда будет считана из блока 1 памяти микрокоманд, так как управляющие сигналы на входах коммутатора 14 от" сутствуют и блок 4 синхронизации выдает тактовый импульс на вход 67 регистра 7,.1Пусть при считывании микрокоманды из регистра 7 в поле метки 7,5 появилея единичный сигнал, который свидетельствует о том, что следующую микрокоманду необходимо считать иэ того же блока памяти, Этот сигнал закрьвает элемент И 21, и единичный сигнал с выхода элемента ИЛИ 36 не проходит на вход одновибратора 42, а также переключает триггер 17 в единичное состояние, что обуславливает появление единичного сигнала на выходе 56 группы входов 71 и нулевого потенциала - на входе 5.7. Кроме того, сигнал метки подается иа вход 7.5 группы входов 71. Сформированные таким образом сигналы управления по группе входов 71 поступают в блок 4 синхронизации, который производит перетактовку (изменение "привязки") тактовых импульсов к каналам. Так как управляющие сигналы на входах элемента ИЛИ 27 отсутствуют, то коммутатор 12 адреса разрешит прохождение адреса с по"166110 22 5 10 15 20 25 30 35 40 45 50 55 лей 7.1-7.3 регистра 7 в формирователь 1 О адреса и на вход регистра 5. Далее произойдет считывание очередной микрокоманды иэ блока 1 памяти микрокоманд и т.д.В случае, если метка 7.5 появляется снова, то произойдет еще раз считывание микрокоманд из того же блока памяти, если эта метка не появляется, то считывание очередной микрокоманды будет происходить из блока 2 микрокоманд аналогично ранее описанным тактам работы устройства.Рассмотрим функционирование уст" ройства при считьвании подряд двухмикрокоманд из блока 2 памяти,при этом в поле меток 8.5 и 8.6 пояф вится единичный сигнал. Это свидетельствует о том, что следующая микрокоманда должна быть считана из блока 2 памяти микрокоманд. Сиг-, налы меток МЗ и М 4 поступают на вхо- ды элементов И 24 и 25.На выходе элемента И 24 формируется единичный оигнал, а на выходе элемента И 25 нулевой сигнал, которые поступают на вход одновибраторов 44 и 45 и входы 59 и 60 соответственно. Сигнал с выхода 59 поступает на вход элемента ИЛИ 33. На выходе элемента ИПИ 33 будет единичный сигнал. В соответствии. с единичным сигналом на выходе 42.2 одновибратора 42 (задержка на), которь 1 й пройдет через элемент ЙЛИ 27 и откроет коммутатор 12 для прохождения адреса очередной микро- команды иэ регистра 8, в соответствии с которым сформируется исполнительный адрес микрокоманды в регистре 5 по очередному тактовому импульсу. Далее через открытый коммутатор 14 по единичному сигналу с выхода элемента ИЛИ 33 произойдет обращение к блоку 2 памяти микро- команд, с которого по заднему фронту очередного тактооого импульса будет считана микрокоманда в регистр 8. Одновременно появляется импульс на выходе одновибратора 44 (фиг.7, задержка ь ), который, проходя через элемент ЬЙ 37, открывает блок 19 элементов И для прохождения микроопераций с поля 8.4 регистра 8 через блок 40 элементов ИЛИ на выход 49 устройства. Адресная информация с полей 8. 1-8.3 регистра 8 пос 23тупает на коммутатор 12, который открывается по сигналу на входе 54 элемента ИЛИ 27. Следующая микро- команда по вновь сФормированному адресу будет считана из блока 1 5 памяти микрокоманд, затем из блока 2 памяти к т.д. При считывании последней микрокоманды на выходе 49.1 появится единичный сигнал, который пройдет через элемент ИЛИ 31 10 и произведет обнуление триггера 15. В соответствии с этим нулевой сигнал возникнет на входе 52 блока 4 синхронизации и на выходе 70 элемента ИЛИ 34, который также является 15 входом 70 блока 4 синхронизации При этом блок 4 прекращает выдачу тактовых импульсов. Кроме того, нулевой сигнал на выходе 70 обнулит триггеры 17 и 18 для конечной их 20 установки. На этом работа устройства заканчивается до прихода нового кода операции на вход 46. Работа второго канала устройства происходит аналогично Функционированию первого 25 канала устройства.Режим управления параллельными каналами.В этом режиме Функционирование обоих каналов устройства производит- З 0 ся также, как и одного, только они работают параллельно (одновременно). При этом, когда первый канал считывает микрокоманду из блока 1 памяти микрокоманд, второй - из блока 2 памяти микрокоманд. В следующем такте первый канал - из блока 2 памяти микрокоманд, второй в ,из блока 3 памяти микрокоманд и т.д, .(Фиг.8).Отличием данного режима от рас смотренного ранее режима является то, что здесь в случае одновременного. появления меток в поле 7,5 регистра 7 и в поле 9.5 регистра 9 появляется единичный сигнал на выхсде элемента И 26, который поступает на выход 58 группы входов 71 блока 4 и в соответствии с которым блок 4 синхронизации не выдает очереднойч 110 24тактовый импульс на вход 68 регистра 8 Необходимость этого обусловлена тем, что в этом случае следующие микрокоманды в обоих каналах будут считываться из блоков 1 и 3 памяти соответственно, а обращения к блоку 2 памяти происходить не будет.В этом режиме предусмотрен оперативный контроль. Элемент И 23 выдает сигнал ошибки на выход 51 устройства в случае одновременного обращения обоих каналов к блоку 2 памяти, т.евозникновения единичных сигналов на входах 63 и 64 коммутатора 14. Кроме того, происходит останов устройства.Моменты окончания выполнения микропрограмм могут не совпадать. При этом по сигналу конца операции останавливается один канал, а второй продолжает работу. Запись новых кодов операций осуществляется только после окончания микропрограмм обоих каналов устройства,что необходимо для облегчения задачи распределения памяти устройств.1Таким образом, предлагаемое устройства отличается от известных: порешаемой задаче - сокращением объемаоборудования блоков памяти устройства и повышением быстродействия устройства, по выбранному пути решаемойзадачи - использованием дополнительного блока памяти, в которомбесповторно хранятся микропрограммы,и огранизацией параллельной работыдвух каналов с сохранением двухплечевой структуры устройства, по используемым техническим средствам -введением третьего блока памяти микрокоманд, третьего регистра микрокоманд, седьмого, восьмого, девятого, одиннадцатого, двенадцатогои тринадцатого элементов ИЛИ, второго блока элементов ИЛИ, первогои второго блоков элементов И, второго, третьего и четвертого одновибраторов,474 5 Л 6 1166110 г. Фо мат ормаа ФирююЕ1 ций первого регистра микрокоманд соединен с первым входом первого блока элементов ИЛИ, группа выходов которого является первым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены,с первыми информационными входами соответственно первого и второго коммутаторов адреса, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход второго элемента И соединен с входом первого одновибратора, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, устройство дополнительно содержит третий блок памяти микро- команд, третий регистр микрокоманд, седьмой, восьмой, девятью, десятый, одиннадцатый, двенадцатый и тринадцатый элементы ИЛИ второй блок эле" ментов ИЛИ, первый и второй блоки элементов И, второй, третий и четвертый одновибраторы, причем второй вход логических условий устройства соединен с вторым входом второго формирователя адреса, входы меток. управления синхронизацией первой и второй групп входов кода операции устройства соединены соответственйо с первым и вторым синхронизи-: руемым входом блока синхронизации, выход которого соединен с установочными входами первого, второго и третьего регистров микрокоманд, выход конца работы группы выходов. первого блока элементов ИЛИ соединен с вторым входом второго элемента ИЛИ, выход конца работы группы выходов второго блока элементов ИЛИ. соединен с первым входом шестого элемента ИЛИ, выход которого соединен с нулевым входом второго триггера пуска, выход первого элемента И соединен с вторым входом шестого элемента ИЛИ и является выходом ошибки устройства, втораягруппа входов входа кода операции устройства соединена с входом треть-, его элемента ИЛИ, выходы полей адреса первого и второго регистров .адреса соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен,с входом третьего блока памяти микрокоманд, выход третье" 166110го блока памяти микрокоманд соединен с информационным входом третьего регистра микрокоманд, выходы полей адреса, кода логических условий и модифицируемого разряда адреса которого соединены с вторыми информационными входами первого и второго коммутаторов адреса, выход поля микрооперации третьего регистра микрокоманд соединен с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с вторым входом первого блока элементов ИЛИ и с первым входом второго блока элементов ИЛИ, группа выходов второго блока элементов ИЛИ является вторым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены соответственно с входами седьмого и восьмого элементов. ИЛИ, выходы которых соединены соответственно с прямыми входами второго и третьего элементов И, выход третьего элемента И соединен с входом второго одновибратора, первый выход которого соединен с первым входом девятого элемента ИЛИ, второй выход второго одновибратора соединен с первыми входами пятого и десятого элементов ИЛИ,первый выход первого одновибратора соединен с первым входом одиннадцатого элемента ИЛИ, второй выход первого одновибратора соединен с первыми входами четвертого и двенадцатого элементов ИЛИ, единичный выход перного триггера пуска соединен с первым входом тринадцатого элемента ИЛИ, выход которого соединен с вторым входом пуска блока синхронизации и с нулевыми входами первого и второго триггеров управления, единичный выход второго триггера пуска соединен с вторым входом тринадцато,го элемента ИЛИ, с третьим входом ,пуска блока синхронизации, выход поля метки управления синхронизацией .первого регистра адреса соединен с вторыми входами четвертого, одиннадцатого, двенадцатого элементов ИЛИ, выход поля метки управления синхронизацией второго регистра адреса соединен с вторыми входами пятого, девятого, десятого элементов ИЛИ, выход девятого элемента ИЛИ1166110 Х,17 Е. й РАКК б 7(40) С 2.2 бд бйЩ РИк Составитель И, СигаловТехред А,Бабинец Кор ор Е хм ктер И. Яцол каэ 4311/4 Подписноемитета ССС и открытийская наб., д. 4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная ГдГ 78 8 т,Рвз оо(юо) Тираж ИИПИ Госу по делам 35 Москв.соединен с первым входом первого элемента И и первым управляющим входом коммутатора, выход одиннадцатого элемента ИЛИ соединен с вторым входом первого элемента И и вторым управляющим входом коммутатора, первый и второй выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого и второго регистров адреса, третий,четвертый, пятый выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего регистров микрокоманд, выход поля метки управления синхронизацией первого регистра микрокоманд соединен с инверсным входом второго элемента И, с первым входом четвертого элемента И, со счетным входом первого триггера управления и с первым входом разрешения выработки тактовых импульсов группы входов блока синхронизации, единичный и нулевой выходы первого триггера управления соединены соответственно с вторым и третьим входами группы входов блока синхронизации, выход поля метки управления синхронизацией второго регистра микрокоманд соединен с инверсным входом третьего элемента И, с вторым входом четвертого элемента И, со счетным входом второго триггера управления и с четвертым входом группы входов 110блока синхронизации, единичный и ну" левой выходы второго триггера управления соединены соответственно с пятым и шестым входами группы входов блока синхронизации, выход четверто" го элемента И соединен с седьмым входом группы входов блока синхро- низации, выход поля первой метки управления синхронизацией третьего регистра микрокоманд соединен с пер" вым входом пятого элемента И и с прямым входом шестого элемента И, выход которого соединен с входом третьего одновибратора и с вторым входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход поля второй метки управления синхронизацией третьего регистра микрокоманд соединен с инверсным входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с входом четвертого одновибратора и с третьим входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход третьего одновибратора соединен с третьими входами пятого и десятогоэлементов ИЛИ, выход четвертого одновибратора соединен с третьими входами четвертого и двенадцатого элементов ИЛИ, выходы десятого и двенадцатого элементов ИЛИ соединены соответственно с вторыми входами первого и второго блоков элементов И.Изобретение относится к цифровойвычислительной технике и может быть .использовано при разработке микропрограммных устройств управления параллельных вычислительных и управляю-. щих систем.Известны микропрограммные устройства управления, содержащие первыйи второй блоки памяти микрокоманд,регистры микрокоманд и адреса,формирователи адреса, триггеры, элементы И 1 Д и 2 Д .Недостатками указанных устройствявляются низкая производительность иузкая область применения, обусловлен ные невозможностью управления параллельными процессами.Известно также микропрограммное устройство управления, содержащее первый и второй блоки памяти микро- команд, первый и второй регистры адреса, первый и второй коммутаторы, блок синхронизации, первый и второй триггеры управления, элементы И, ИЛИ З).Недостатками данного устройства являются низкая производительность, обусловленная отсутствием технических средств для управления параллельными процессами и перетактовкой6110 4 з 1 16 устройства при последовательном выполнении двух четных (нечетных) микрокоманд, а также низкая достоверность функционирования.Наиболее близким к изобретению по технической сущности и достигаемому результату является микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй ре гистры адреса, первый и второй регистры микрокоманд, первый и вто" рой коммутаторы, формирователь так. - товых импульсов, первый и второй формирователи адреса, первый и вто рой триггеры управления, первый и второй элементы И, блок элементов ИЛИ, схема сравнения, третий, четвертый и пятый триггеры управления, третий и четвертьп коммутато рытретий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, первый и второй элементы И-НЕ и одновибратор, причем входы логических условий устройства соединены с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первыми вхо . дами соответственно первого и второго регистров адреса, вход кода операции устройства соединен с вторыми информационными входами первого и второго регистров адреса, выходы которых соединены с информационными входами соответственно первого и второго блоков памяти микрокоманд, выходы пер-, вого и второго элементов И соединены с управляющими входами соответст венно первого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно первого и второго регистров микро- команд, первые управляющие выходы 45 первого и второго регистров микро- команд соединены с единичными входами соответственно первого и второго триггеров управления, выходы микро- операций первого и второго регистров 50 микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого является выходом микроопераций устройства, выход адреса первого регистра микро команд соединен с первыми информационными входами первого и второго коммутаторов, выход адреса второго регистра микрокоманд соединен с вторыми информационными входами первогои второго коммутаторов, выходы кото-рых соединены с вторыми информационными входами соответственно первогои второго формирователей адреса,вход кода операции устройства че"рез первьй элемент ИЛИ соединен сединичным входом третьего триггерауправления, единичный выход которогосоединен с входом формирователятактовых импульсов, первый выходформирователя тактовых импульсовсоединен с нулевыми входами триггеров полей микроопераций первого ивторого регистров микрокоманд и спервыми информационными входамитретьего и четвертого коммутаторов,выходы которых соединены с первыми входами соответственно первого ивторого элементов И, второй и третий выходы формирователя тактовых импульсов соединены соответственно с вторыми и третьими информационными входами третьего и четвертого коммута"торов, единичньпЪ выход четвертоготриггера управления соединен с первыми управляющими входами третьего ичетвертого коммутаторов, первымивходами третьего, четвертого и пятого элементов И,первого и второгоэлементов И-НЕ, выходы которых соединены с вторыми входами соответственно первого и второго элементов И,второй управляющий выход первого регистра микрокоманд с 6 единен с первыми входами второго и третьего элементов ИЛИ, выход которого соединенс первым управляющим входом первогокоммутатора, второй управляющий выходвторого, регистра микрокоманд соединен с первым входом четвертого ивторым входом второго элемента ИЛИ,выход которого соединен с Т-входомпятого триггера управления, единичный выход которого соединен с вторыми управляющими входами третьегои четвертого коммутаторов, нулевойвыход пятого триггера соединен с .третьими управляющими входами третьего и четвертого коммутаторов, третьиуправляющие выходы первого и второгорегистров микрокоманд.через йятыйэлемент ИЛИ соединены с единичнымвходом четвертого триггера управления,нулевой выход которого соединен свторым управляющим входом первого5 11 б 61 входом второго коммутатора, нулевйе выходы первого и второго триггеров управления соединены с вторыми входами соответственно третьего и пятого элементов И, выходы которых 5 соединены с вторыми входами соответственно третьего и четвертого элементов ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, третьи управляющие вхо ды первого и второго регистров микро- команд соединены с третьими управляющими входами соответственно первого и второго коммутаторов, единичный выход первого триггера управле ния соединен с вторым входом первого элемента И-НЕ и первым входом шес-. того элемента И, единичный выход второго триггера управления соединен с вторым входом второго элемен- рО та И-НЕ и вторым входом шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И и через одновибратор - с нулевыми входами первого, второго 25 и четвертого триггеров управления, выходы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверсный выходы которой соединены с вторыми входами соответственно седьмого и восьмого элементов И, выход седьмого элемента И соединен с третьими входами третьего и четвертого элементов ИЛИ, выход восьмого35 элемента И соединен с первыми входами шестого и седьмого элементов ИЛИ, выходы которых соединены соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выход конца операции блока элементов ИЛИ соединен с вторыми входами шестого элемента ИЛИ и четвертого элемента И, 45 .выход которого соединен с входом седьмого элемента ИЛИ 4.. Недостатками известного устройства являются большойг объем обору-. дования, вызванный избыточностью 50 блоков памяти, и низкое быстродействие при реализации параллельных микроподпрограмм, обусловленное перестройкой устройства в одноплечевую . структуру. Вольшой объем оборудова ния, вызванный избыточностью блоков памяти устройства, обусловлен двумя причинами: избыточностью блоков па-О 6мяти каждого плеча устройства из-за хранения многократно повторяющихся микроподпрограмм, выполняемых в последовательном и параллельном режимах для управления одним объектом (горизонтальная избыточность) и избыточностью блоков памяти устройства, которая вызвана большим количеством идентичных микроподпрограмм для управления параллельными каналами, хранимых в блоках памяти (вертикальная избыточность). В последовательном режиме функциоиирования устройство представляет собой двух- плечевую структуру в которой обращение к двум блокам памяти производится за счет двух последовательностей тактовых импульсов сдвинутых один относительно другого. Период следования тактовых импульсов устройствав данном режиме равен ,. При переходе в параллельный режим устройство перестраивается в одноплечевую структуру и период следования тактовых импульсов устройства становитсяравным 2 Счто и обуславливает низкое быстродействие.1цель изобретения - повышениебыстродействия устройства,Поставленная цель достигаетсятем, что в параллельное микропрограммное устройство управления, содержащее первый и второй блоки памятимикрокоманд, первый и второй регистры адреса, первый и второй регистры микрокоманд, первый ч второйформирователи адреса, первый и второйрой коммутаторы адреса, коммутатор,первый одновибратор, первый и второй триггеры пуска, первый и второйтриггеры управления, блок синхронизации, первый, второй, третий,четвертый, пятый, шестой элементы ИЛИ, первый, второй,. третий, четвертый, пятый, шестой элементы И,первый блок элементов ИЛИ, причемпервая группа входов кода операцииустройства соединена с первым информационным входом первого регистра адреса и с входом первого элемента ИЛИ, выход которого соединенс единичным входом первого триггера пуска, выход второго элемента ИЛИсоединен с нулевым входом первоготриггера пуска, единичный выходкоторого соединен с первым входомпуска блока синхронизации, выходтретьего элемента ИЛИ соединен с1166 щ7единичным входом второго триггера пуска, вторая группа входов кода операции устройства соединена с первым информационным входом второго, регистра адреса, первый вход логических условий устройства соединен с первым входом первого формирователя адреса, выход которого соединен с вторым информационным входом первого регистра адреса, выход четверто го элемента ИЛИ соединен с прямым н инверсным управляющими входами первого коммутатора адреса, выходы кода логических условий и немодифицируемых разрядов адреса которо го соединены. соответственно с вторым входом первого формирователя адреса и третьим информационным входом первого регистра адреса, выход второго формирователя адреса соединен щ с вторым информационным входом второго регистра адреса, выход пятого элемента ИЛИ соединен с прямым и инверсным управляющими входами второго коммутатора адреса, выходы кода 25 логических условий и немодифицируемых разрядов адреса которого соединены соответственно с первым входом второго формирователя адреса и третьим информационным входом второго формирователя адреса, выходы полей адреса первого и второго регистров адреса соединены соответственно с входами первого и второго блоков памяти микрокоманд, выходы которых соединены соответственно с информационными входами первого и второго регистров микрокоманд,выход поля микроопераций первого регистра микрокоманд соединен с первым входом первого блока элементов ИЛИ, группа выходов которого является первым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены с первыми Эинформационными входами соответственно первого и второго коммутаторов адреса, выход первого элемен та И соединен с первым входом второго элемента ИЛИ, выход второго элемента И соединен с входом первого одновибратора, дополнительно введен третий блок памяти микроко манд, третий регистр микрокоманд, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринад 110 8цатый элементы ИЛИ, второй блок элементов ИЛИ, первый и второй блоки элементов И, второй, третий и четвертый одновибраторы, причем второй вход логических условий устройства соединен с вторым входом второго формирователя адреса, входы меток управления синхронизацией первой и второй групп входов кода операции устройства соединены соответственно с первым и вторым синхронизируемым входом блока синхронизации, выход которого соединен с установочными входами первого, второго и третьего регистров микрокоманд, выход конца работы группы выходов первого блока элементов ИЛИ соединен с вторым входом второго элемента ИЛИ, выход конца работы группы выходов второго. блока элементов ИЛИ соединен с первым входом шестого элемента ИЛИ, выход которого соединен с нулевым входЬм второго триггера пуска, выход первого элемента И соединен с вторым входом шестого элемента ИЛИ и является выходом ошибки устройства, вторая группа входов входа кода операции устройства соединена с входом третьего элемента ИЛИ, выходы полей адреса первого и второго регистров адреса соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен с входом третьего блока памяти микрокоманд, выход третьего блока памяти микро- команд соединен с информационным входом третьего регистра микрокоманд, выходы полей адреса, коды логических условий и модифицируемого разряда адреса которого соединены с вторыми информационными входами первого и второго комму таторов адреса, выход поля микро- операций третьего регистра микро- команд, соединен с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с вторым входом первого блока элементов ИЛИ и с первым входом второго блока элементов ИЛИ, группа выходов второго блока элементов ИЛИ является вторым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены соответственно1166 с входами седьмого и восьмого элементов ИЛИ, выходы которых соединены соответственно с прямыми входами второго и третьего элементов И, выход третьего элемента И соединен с входом второго одновибратора; первый выход которого соединен с первым входом девятого элемента ИЛИ, второй выход второго одновибратора соединен с первыми входами пятого и де О сятого элементов ИЛИ, первый выход первого одновибратора соединен с первым входом одиннадцатого,элемента ИЛИ, второй выход первого одновибратора соединен с первыми входами 15 четвертого и двенадцатого элементов ИЛИ, единичный выход первого триггера пуска соединен с первым входом тринадцатого элемента ИЛИ, выход которого соединен с вторым входом . о пуска блока синхронизации и с нулевым входами первого и второго триггеров управления, единичный выход второго триггера пуска соединен с вторым входом тринадцатого элемен та ИЛИ, с третьим входом пуска блока синхронизации, выход поля метки уп.равления синхронизацией первого регистра адреса соединен с вторыми входами четвертого, одиннадцатого, двенадцатого элементов ИЛИ, выход поля метки управления синхронизацией второго регистра адреса соединен с вторыми входами пятого, девятого, десятого элементов ИЛИ, выход девя 35 того элемента ИЛИ соединен с первым входом первого элемента И и первым управляющим входом коммутатора, выход одиннадцатого элемента ИЛИ соединен с вторым входом первого элемента И н вторым управляющим входом коммутаторапервый и второй выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого и вто рого регистров адреса, третий, четвертый, пятый выходы группы выходов блока синхронизации соединены свходами синхронизации соответственно первого, второго и третьего ре гистров микрокоманд, выход поля метки управления синхронизацией первого регистра микрокоманд соединен синверсным входом второго элемента И, с первым входом четвертого 55 элемента И, со счетным входом первого триггера управления и с первымвходом разрешения выработки тактовых 1 ООимпульсов группы входов блока синхронизации, единичный и нулевой вы ходы первого триггера управления соединены соответственно,с вторым и третьим входами группы входов блока синхронизации, выход поля метки управления синхронизацией второго регистра .микрокоманд соединен с инверсным входом третьего элемента И, с вторым входом четвертого элемента И, со счетным входом второго триггера управления и с четвертым входом группы входов блока синхронизации, единичный и нулевой выходы второго триггера управления соединены соответственно с пятым и шестым входами группы входов блока синхронизации, выход четвертого элемента И соединен с седьмым входом группы входов блока синхронизации, выход поля первой метки управления синхронизацией третьего регистра микрокоманд соединен с первым входом пятого элемента И и с прямым входом шестого элемента И, выход которого соединен с входом третьего одновибратора и с вторым входом разрешения выработки тактовых импульсов группч входов блока синхронизации, выход поля второй метки управления синхронизацией третьего регистра микро- команд соединен с инверсным входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с входом четвертого одновибратора и третьим входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход третьего одновибратора соединен с третьими входами пятого и десятого элементов ИЛИ, выход четвертого одновибратора соединен с третьими входами четвертого и двенадцатого элементов ИЛИ, выходы десятого и двенадцатогс элементов ИЛИ соединены соответственно с вторыми входами первого и второго блоков элементов И.Сущность изобретения состоит в повышении быстродействия устройства за счет введения специального блока памяти,в котором бесповторно хранятся микроподпрограммы и который позволяет сохранить двуплечевую структуру устройства для какдого объекта управления в параллельном вежиме Функционирования.11Введение третьего блока памятимикрокоманд, третьего регистрамикрокоманд, седьмого, восьмого,девятого, одиннадцатого и тринадцатого элементов ИЛИ и обусловленных ими связей позволяет обеспечивать двуплечевую структуру устройства для каждого объекта .управле-ния,Введение десятого и двенадцатого элементов ИЛИ, второго,третьего и четвертого блоков эле-, ментов ИЛИ и обусловленных нмисвязей позволяет обеспечить выдачусигналов микроопераций, считываемыхиз третьего блока памяти микрокоманд, попеременно на два объектауправления.Введение третьего и четвертогоодновибраторов и обусловленных имисвязей позволяет обеспечить считывание подряд двух четных (нечетных)микрокоманд из третьего блока памятимикрокоманд при управлении одним. объектомНа Фиг.1 приведена Функциональная схема микропрограммного устройства управления, на Фиг.2 - Функциональная схема блока синхронизации,на Фиг.3 - функциональная схемаФормирователей адреса, на Фиг.4 Формат микрокоманд, записываемыхв регистры адреса н регистры микрокоманд, на Фиг. 5-7 - временныедиаграммы работы устройства в различных режимах функционирования.Микропрограммное устройствоуправления (Фиг.1) содержит первый блок 1 памяти микрокоманд,третий блок 2 памяти микрокоманд,второй блок 3 памяти микрокоманд,блок 4 синхронизации, первый регистр 5 адреса, содержащий поле 5.1адреса и поле 5.2 метки управлениясинхронизации, второй регистр 6адреса, содержащий поле 6,1 адресаиполе 6.2 метки. управления синхронизации, первый регистр 7 микрокоманд, содержащий поле 7.1 адреса,поле 7.2 кодов логических условий,поле 7.3 модифицируемого разряда,поле 7.4 микроопераций и поле 7.5метки управления синхронизацией,третий регистр 8 микрокоманд, содержащий поле 8.1 адреса, поле 8.2номеров логических условий, поле8.3 модифицируемого разряда, поле8.4 микроопераций, поля первой 8,5 66110 12ивторой 8.6 меток управления синхронизацией, второй регистр 9 микрокоманд, содержащий поле 9. 1 адреса, поле 9,2 номеров логических .условий, поле 9.3 модифицируемогоразряда, поле 9.4 микроопераций иполе 9.5 метки управления синхронизацией, первыйФормирователь 10адреса, второй формирователь 11 1 О адреса, первый коммутатор 12 адреса, второй коммутатор. 13 адреса,коммутатор 14, первый триггер 15пуска, второй триггер 16 пуска,первый триггер 17 управления, вто" 15 рой триггер 18 управления, первыйблок 19 элементов И, второй блок 20элементов И, второй элемент И 21,третий элемент И 22, первый элемент И 23, пятый элемент И 24, о шестой элемент И 25, четвертыйэлемент И 26, четвертый элемент ИЛИ27, пятый элемент ИЛИ 28, первыйэлемент ИЛИ 29, третий элемент ИЛИ30, второй элемент ИЛИ 31, шестой 25 элемент ИЛИ 32, одиннадцатый элемент ИЛИ 33, тринадцатый элемент ИЛИ34, девятый элемент ИЛИ 35, седьмойэлемент ИЛИ 36, двенадцатый элемент ИЛИ 37, десятый элемент ИЛИ 38,восьмой элемент ИЛИ 39, первыйблок 40 элементов ИЛИ, второй блок41 элементов ИЛИ, первый одновибратор 42, содержащий поле 42.1 задержки на , и поле 42.2 задерж, ки на ь, второй одновнбратор 43, 35гсодержащий поле 43.1 задержки на ри поля 43.2 задержки на о д, третий одновибратор 44, четвертый одновибратор 45.40 Кроме того, микропрограммноеустройство содержит вход 46 кодаоперации устройства, первую 46.1(вторая 46.2) группу входов кодаоперации устройства по которым по даются коды операции, реализуемыев первом (втором) канале устройства,метки 46.3 (46.4) управления синхронизацией первого (второго) каналаустройства, вход 47(48) логических 50 условий первого (второго) каналаустройства, первый выход 49 микроопераций устройства и выход 49.1конца работы первого канала устройства, второй выход 50 микроопераций 5 устройства и выход 50.1 конца работы второго канала устройства,выход 51 ошибки устройства, единичныйвыход 52 (53) первого (второго) триг1166 10 30 40 13гера 16 (71) пуска (управляющиевходы блока 4 синхронизации),выход54 третьего (четвертого 55) одновибратора 44 (45), единичный (нулевой) выход 56(57) первого триггера 17 управления, выход 58 элемента И 26, выход 59 элемента И 24,выход 60 элемента. И 25, единичный61 (нулевой 62) выход второготриггера 18 управления, выход 63элемента ИЛИ 33 и выход 64 элемента ИЛИ 35, выход 65 (66) синхронизации первого (второго) регистра5(6) адреса, выходы 67-69 синхронизации первого 7, третьего 8 и второго 9 регистров микрокоманд соответственно, выход 70 элемента ИЛИ 34,группу входов 71 блока 4 синхронизации, группу выходов 72 блока 4синхронизации, выход 73 блока 4 син-. 20хронизации, группу входов 74 кодовлогических условий, которые черезкоммутатор 12 адреса поступают навход формирователя 10 адреса,группу входов 75 немодифицируемых разрядов, адрес которых черезкоммутатор 12 поступает на входрегистра 5, группу входов 76 кодовлогических условий, которые черезблок коммутатор 13 поступают навход формирователя,11 адреса, группу входов 77 немодифицируемых разрядов адреса, которые через коммутатор 13 поступают на вход регистра 6.35Блок 4 синхронизации (фиг,2)содержит генератор 78 тактовых импульсов, выходы 78.1-78.3 генератора импульсов и,. ьэ соответственЛ гно (фиг.5-7), коммутаторы 79-81тактовых импульсов, элементы ИЛИ82 и 83, элементы И 84-90, выход 86элемента И 85, выход 91 элемента И 90, управлякяций вход 92 коммутаторов 79 и 81 (нулевой выход 4557 первого триггера 17 управления110 14ра 18 управления), управляющий вход . 98 коммутатора 81 (выход 58 элемента И 26), управляющий вход 99 коммутатора 81 (выход поля 7.5 метки управления синхронизацией первого регистра 7 микрокоманд), управляющий вход 100 коммутатора 81 (выход поля 9.5 метки управления синхронизацией второго регистра 9 микрокоманд), выход 101 коммутатора 79 (вход 67 синхронизации первого регистра 7 микрокоманд),выход 102 элемента И 87 (вход 65 синхронизации первого регистра 5 адреса), выход 103 элемента И 88 (вход 66 синхронизации второго регистра 6 адреса), выход 104 коммутатора 81 (вход 68 синхронизации третьего регистра 8 микрокоманд), выход 105 коммутатора 80 (вход 69 синхронизации второго регистра 9 микрокоманд).Формирователь 10 (11) адреса (фиг.З) содержит мультиплексор 106 и элемент ИЛИ 107.На фиг,4 показаны форматы микрокоманд, Форма А микрокоманд, записываемых в регистры 5 и 6 адреса, содержит поле адреса А и поле метки М 1, причем 1; если первая микро- команда должна быть считана из блока 2 памяти 2; О, если первая микрокоманда должна быть считана из блока 1 (3) памяти. Формат В микрокоманд, записываемых в регистры 7 и 9 микрокоманд, содержит поле адреса А, поле кодов логических условий Луполе моди 4 ицируемого разряда МР адреса, поле микроопераций МО, поле метки М 2 уп" равления синхронизацией, причем 1, если после нечетной (четной) микрокоманды должна следовать нечетная (четная) микрокоманда, 0 - в противном случае Формат С микрокоманд, записываемых в третий регистр 8 микрокоманд, содержит поле адреса А, поле кодов логических условий ЛУ, поле модифицируемого разряда МР адреса, поле микроопераций МО, поле меток МЗ и М 4. Метки МЗ и М 4 используются при перетактовках устройства, т.е. когда

СмотретьЗаявка

3673339, 03.11.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, НИКОЛЬСКИЙ СЕРГЕЙ БОРИСОВИЧ, КАЛЬЧЕНКО СЕРГЕЙ БОРИСОВИЧ, ЧИГРИН ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 07.07.1985

Код ссылки

<a href="https://patents.su/20-1166110-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное управляющее устройство

Следующий патент: Устройство для подключения источников информации с изменяемыми приоритетами к магистрали

Случайный патент: Устройство для автоматической стабилизации визирной оси нивелира