Преобразователь двоичной последовательности в дуобинарную

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

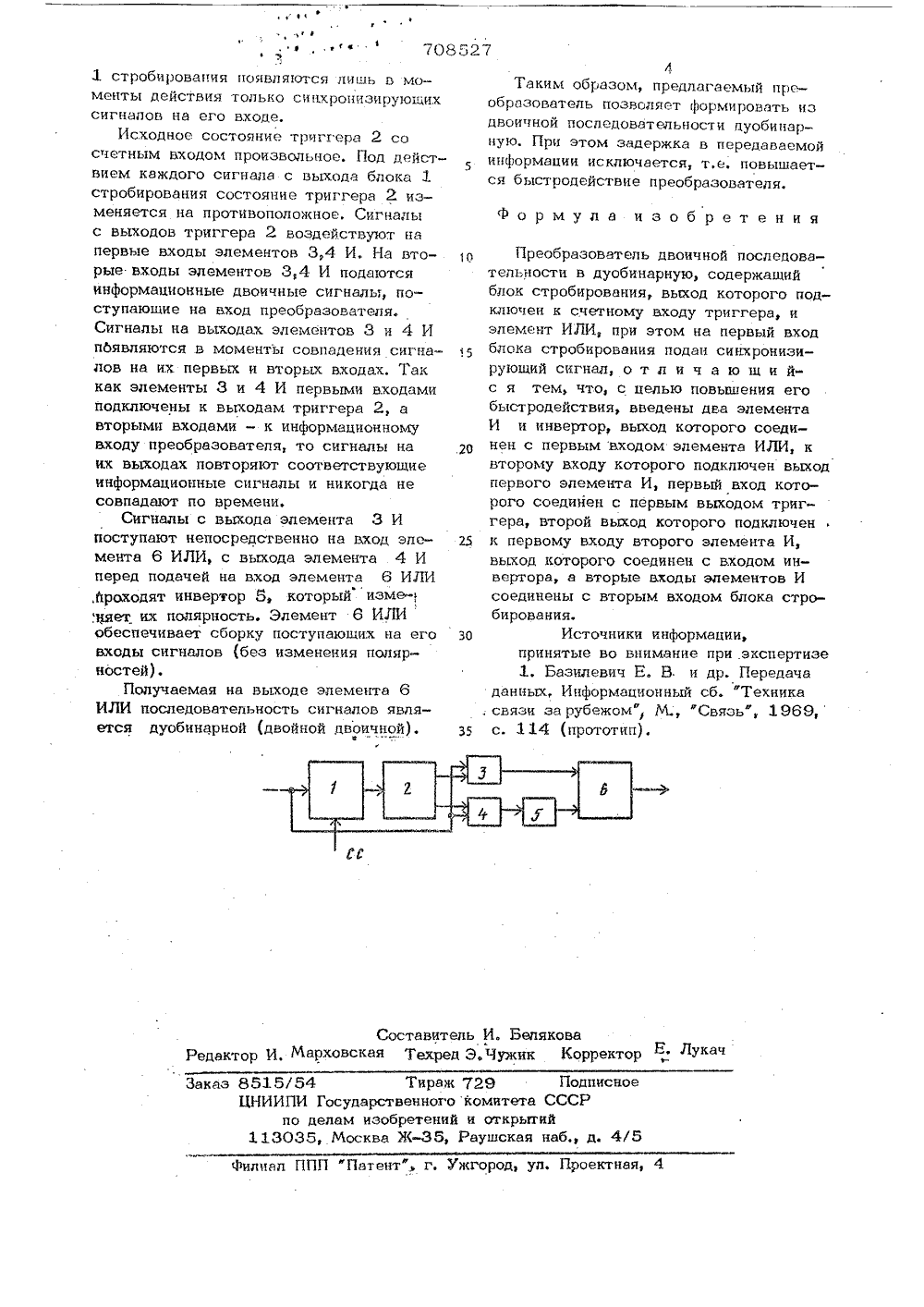

СПИ ИЗОЬ К АВТОРСКО Союз СоветскихСоциалистическихРеспублик и 708527(6) Дополнительное (22) Заявлено 15.06 1)М. Кл. Н 04 Ь 3/02 с присоединением за вудврстввннм 1 комитет СССРПриоритет о делам изобретений бликованоО УДК 621.394(54) ПРЕО ВАТЕЛЬ. ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСВ ДУОБИНАРНУЮ ти 1Изобретение касается передачи данныхи может быть применено в устройствах преобразования сигналов с корреляционными связями между сигналами.Известен преобразователь двоичной последовательности в дуобинарную, содержащий блок стробирования, выход которого подключен к счетному ьходу триггера и элемент ИЛИ, при этом на первый вход блока стробирования подан синхронизируюшпй сигнал, и элемент задержки 11Однако быстродействие этого преобразователя невысоко из-за необходимости обеспечивать задержку последовательносна длительность единичного элемента.Цель изобретения - повышение быстродействия преобразователя.Для этого в преобразователь двоичной последовательности в дуобинарную, содержащий блок стробирования, выход которого подключен к счетному входу триггера, и элемент ИЛИ, при этом на первый вход блока стробироввния подан синхронизируюший сигнал, введены два элемента И и инвертор, выход которого соединен с первым ьходом элемента ИЛИ, к второмувходу которого подключен выход первого элемента И, первый ьход которогосоединен с первым выходом триггера,второй выход которого подключен к первому входу второго элемента И, выходкоторого соединен с входом ицвертора,а вторые ьходы элементов И соединеныс вторым входом блока стробированця.На чертеже приведена структурнаяэлектрическая схема преобразователя.Преобразователь содержит блок 1 стробирования, триггер 2 со счтцым входомэлементы 3,4 И, инвертор 5, элемент6 ИЛИ.Преобразователь работает следующим. образом.На блок 1 стробирования подаютсяинформационные двоичные символы и синхронизпруюшие сигналы. Прнчм информационные символы подаются на запрещаюший вход, синхроцизирующие на разрешающий. Поэтому сигналы на выход блока.г Ю ьу 14В э 708527 ЗБ Составитель И. БеляковаРедактор И, Марховская Техред Э,Чужик Корректор Е Лу Заказ 8515/54 Тираж 729 Подписное ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий 113 О 35, Москва Ж, Раушская наб д. 4/5Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 1 стробировация появляются лишь в моменты действия только синхронизируюнихсигналов на его входе.Исходное состояние триггера 2 сосчетным входом произвольное, Под дейст 5вием каждого сигнала с выхода блоке 1стробирования состояние триггера 2 изменяется на противоположное, Сигналыс выходов триггера 2 воздействуют непервые входы элементов 3,4 И, На вто прые входы элементов 3,4 И подаютсяинформационные двоичные сигналы, поступающие не вход преобразователя,Сигналы на выходах элементов 3 ц 4 Ипбявляются в моменты совпадения сигналов на их первых и вторых входах. Таккак элементы 3 и 4 И первыми входамиподключены к выходам триггера 2, авторыми входами - к информационномувходу преобразователя, то сигналы наих выходах повторяют соответствующиеинформационные сигналы и никогда несовпадают по времени,Сигналы с выхода элемента 3 Ипоступают непосредственно на вход элемента 6 ИЛИ, с выхода элемента 4 Иперед подачей на вход элемента 6 ИЛИ,няет их полярность, Элемент 6 ИЛИобеспечивает сборку поступающих ца его ЗОвходы сигналов (без изменения полярностей) .Получаемая на выходе элемента 6ИЛИ последовательность сигналов является дуобинерной (двойной двоичной). Таким образом, предлагаемый преобразователь позволяет формировать цз двоичной последовательности дуобицарцую, При этом задержка в передаваемой информации исключается, т.е, повышается быстродействие преобразователя,Формула изобретения Преобразователь двоичной последовательности в дуобинарную, содержащийблок стробирования, выход которого подключен к счетному входу триггера, иэлемент ИЛИ, при этом не первый входблока стробирования подан сицхронизирующий сигнал, отл ич ающи йс я тем, что, с целью повышения егобыстродействия, введены два элементаИ и инвертор, выход которого соединен с первым входом элемента ИЛИ, квторому входу которого подключен выходпервого элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого подключенк первому входу второго элемента И,выход которого соединен с входом инвертора, а вторые входы элементов Исоединены с вторым входом блока стробирования.Источники информации,принятые во внимание при .экспертизе1. Базилевич Е. В и др. Передачаданных, Информационный сб. "Техникасвязи за рубежом М., Связь"1968,с. 114 (прототип).

СмотретьЗаявка

2628901, 15.06.1978

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

ЦЫБРИН ВЛАДИМИР ГРИГОРЬЕВИЧ, КУРМАЛИЕВ ФАРИТ ГИЗЗАТОВИЧ

МПК / Метки

МПК: H04L 3/02

Метки: двоичной, дуобинарную, последовательности

Опубликовано: 05.01.1980

Код ссылки

<a href="https://patents.su/2-708527-preobrazovatel-dvoichnojj-posledovatelnosti-v-duobinarnuyu.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичной последовательности в дуобинарную</a>

Предыдущий патент: Устройство для формирования испытательных сигналов для многоканальной системы связи с импульсно-кодовой модуляцией и временным разделением каналов

Следующий патент: Устройство для формирования двухполюсных телеграфных сигналов

Случайный патент: Устройство для ввода алюминиевой проволоки в сталеразливочный ковш