Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

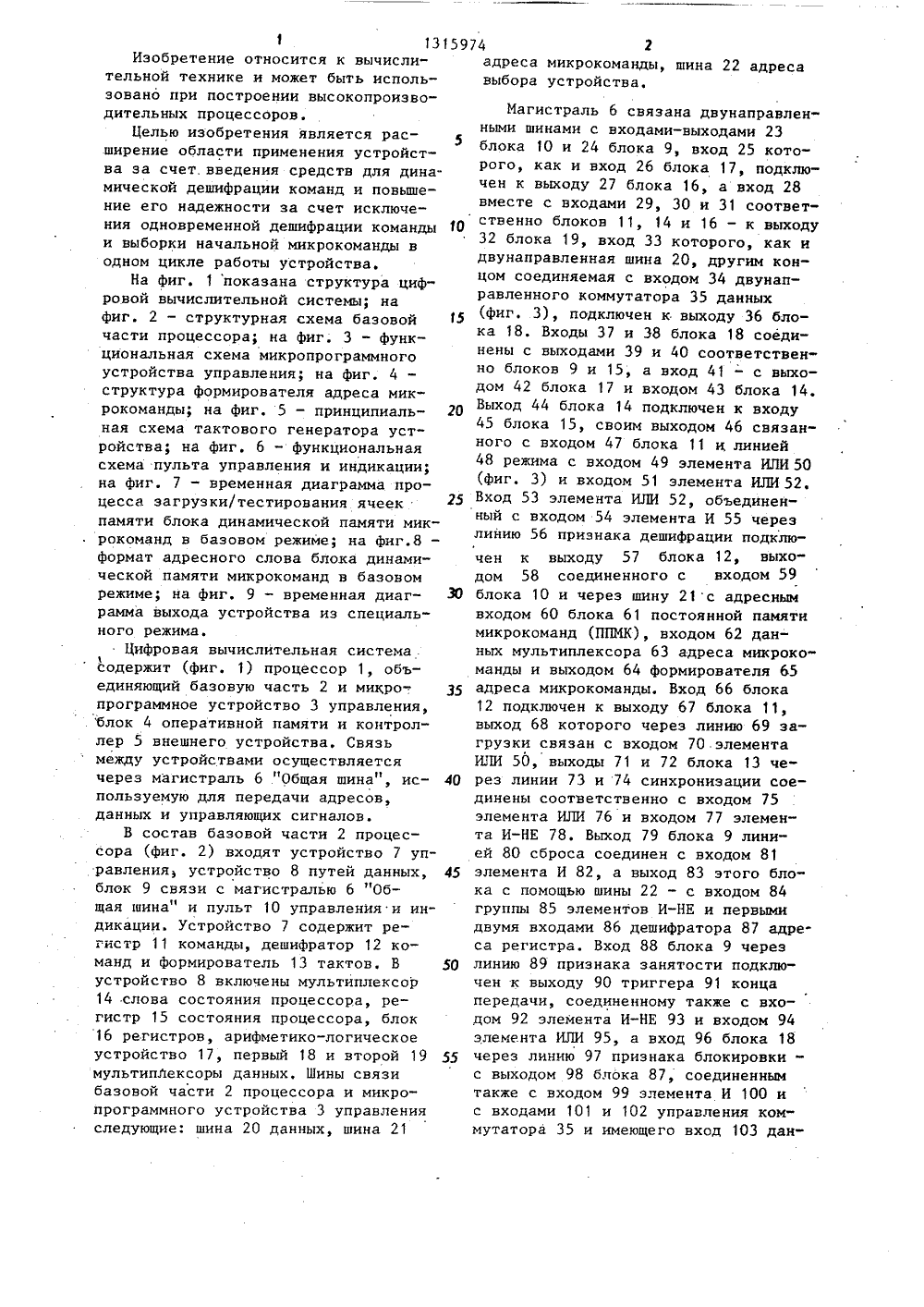

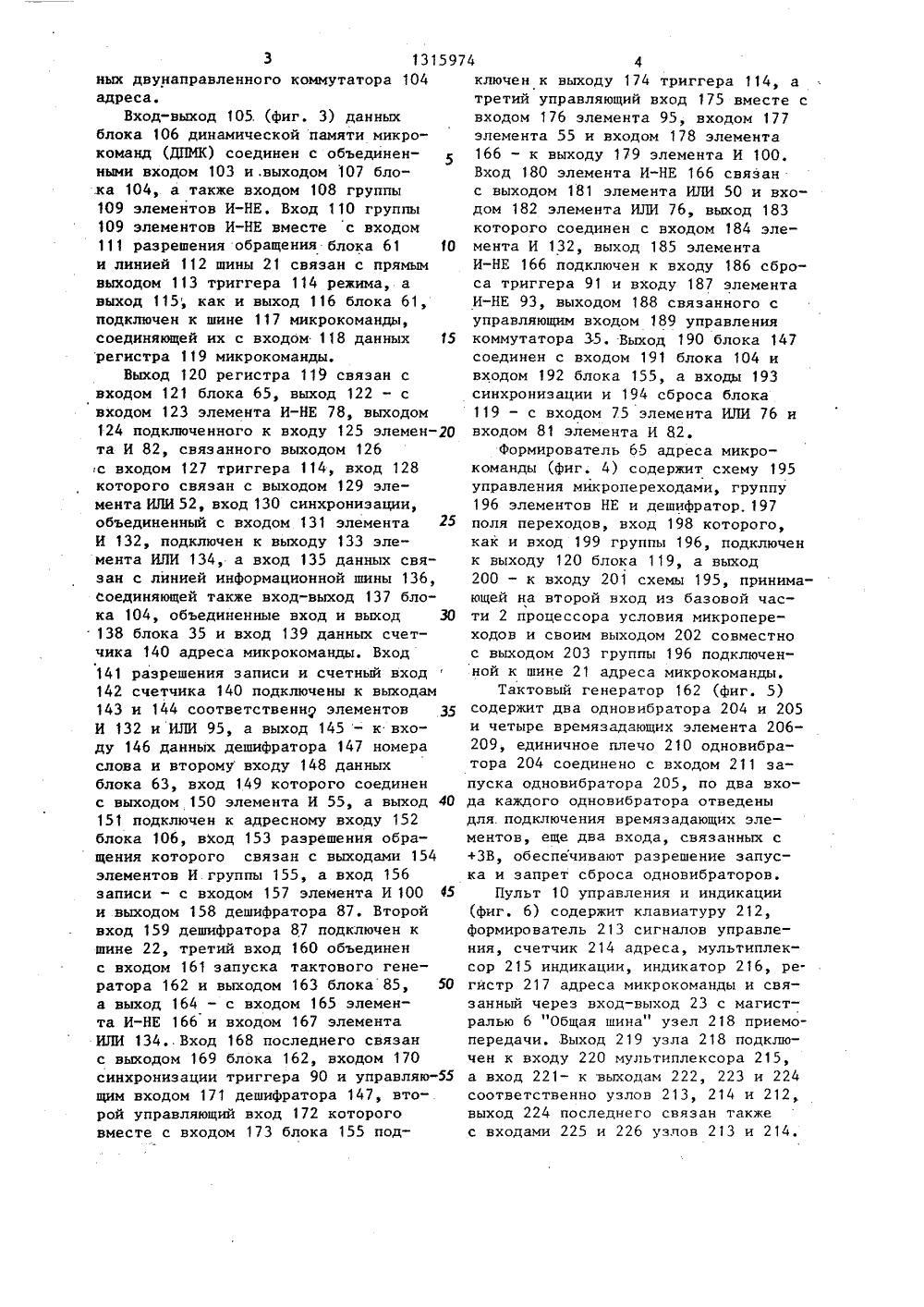

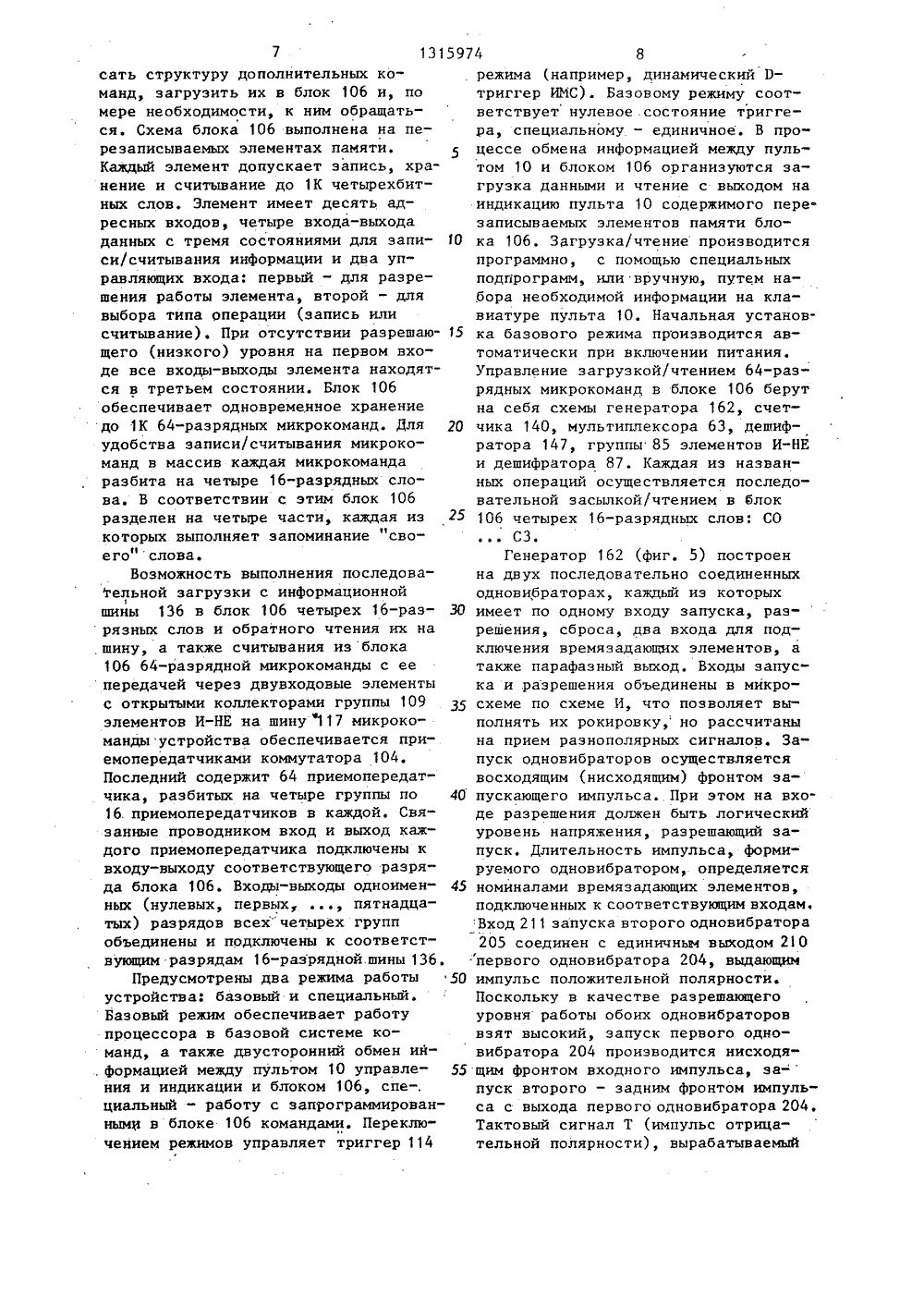

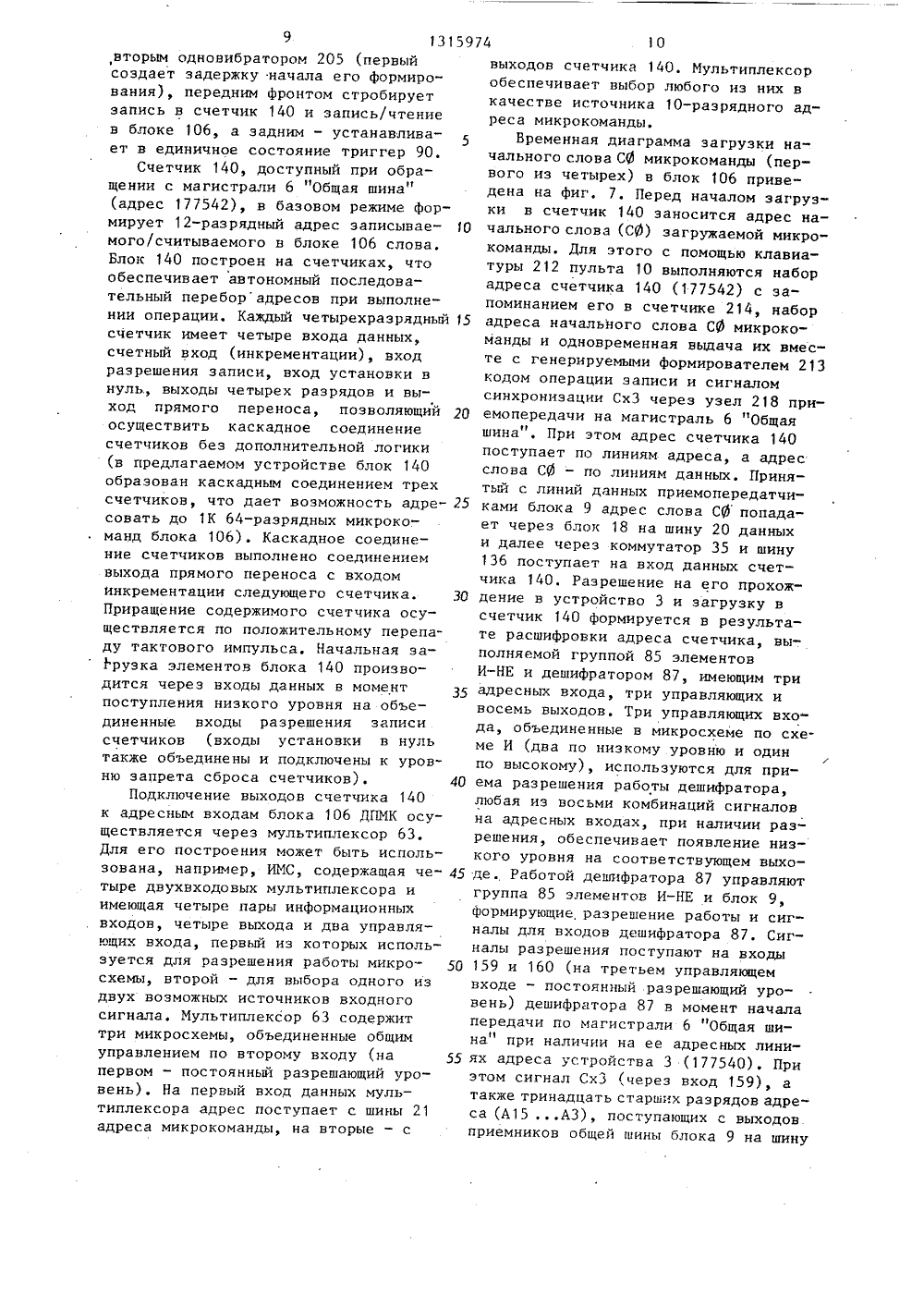

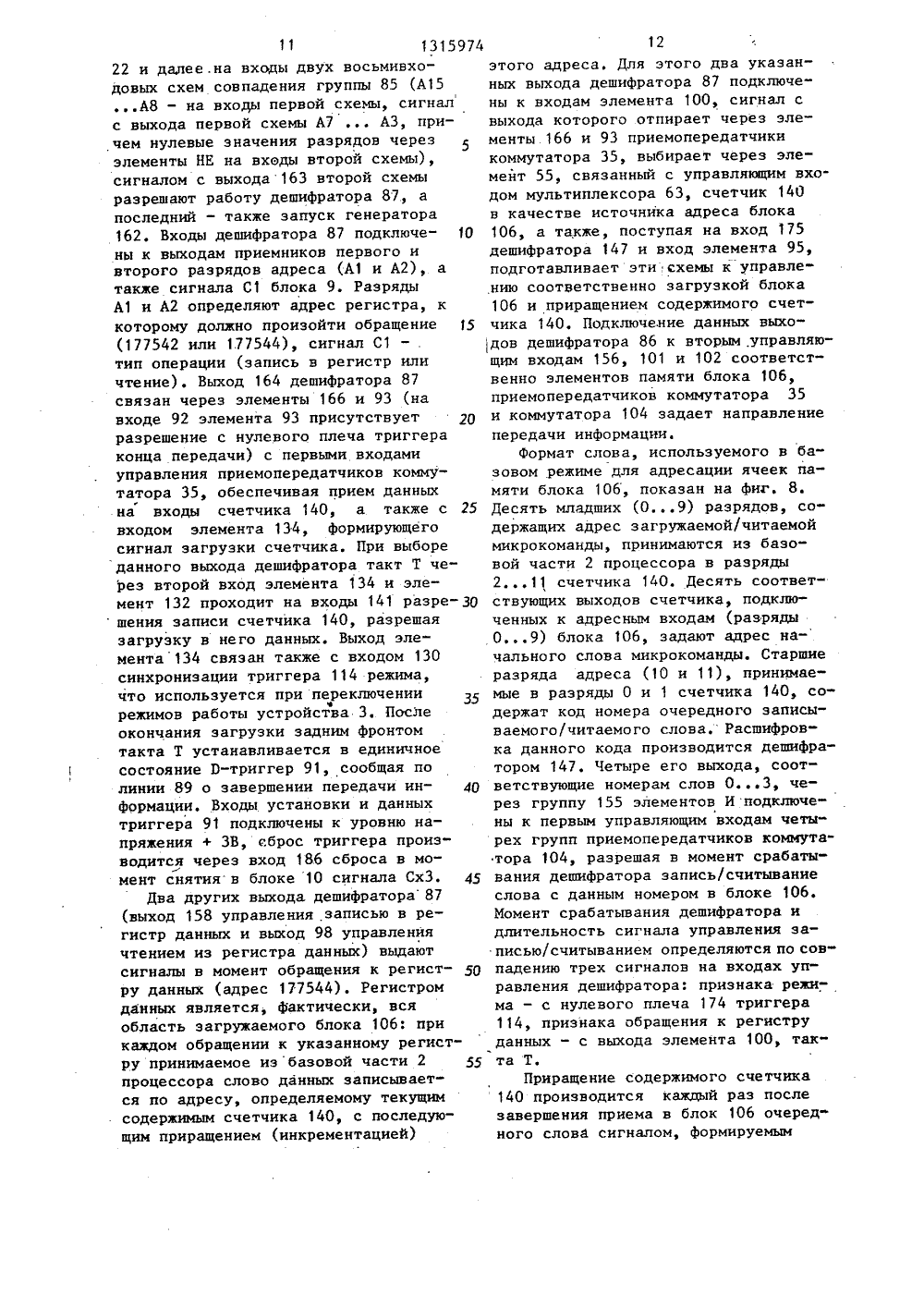

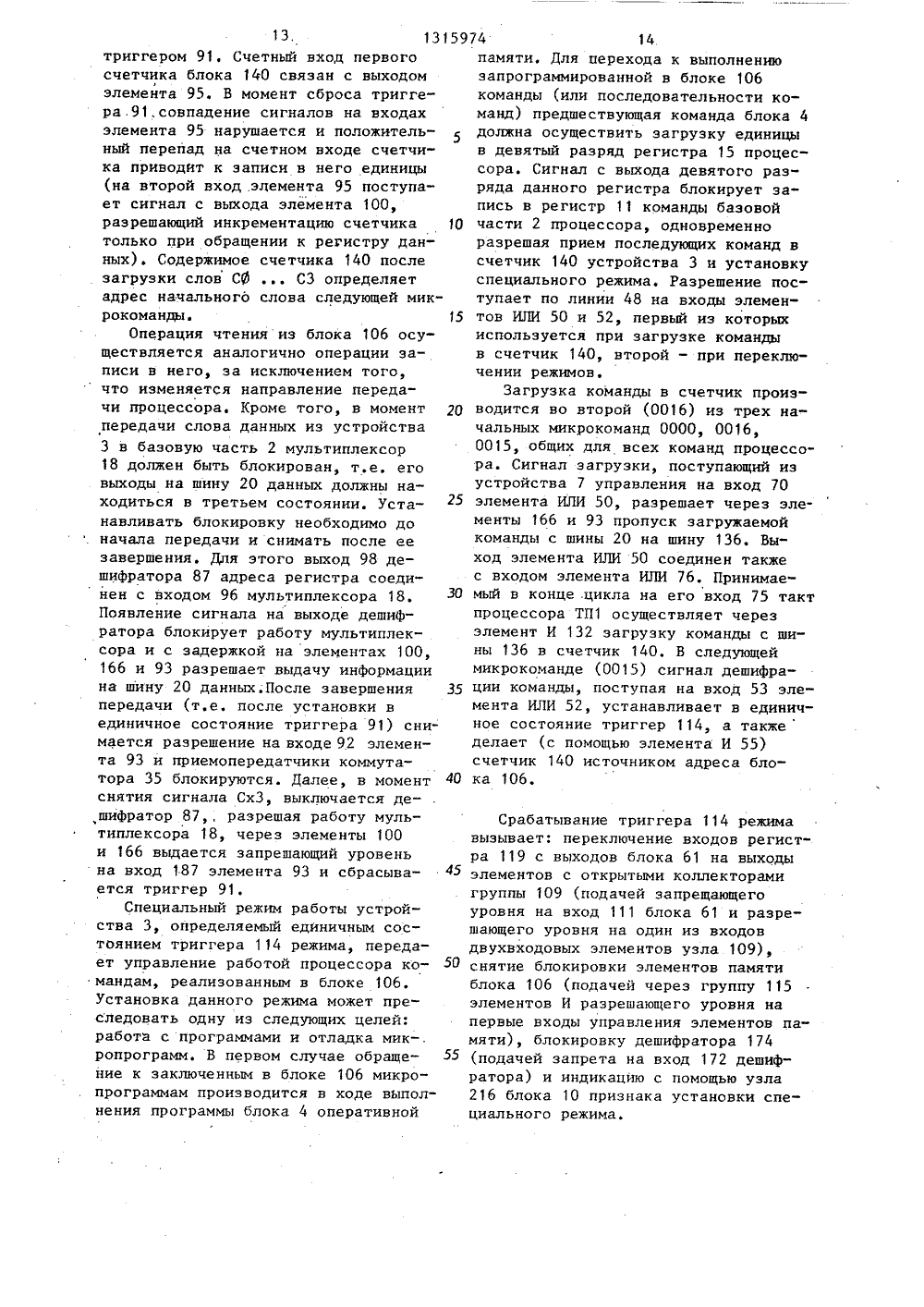

СОЮЗ СОВЕТСКИХСОЦИАЛИСТЮЕСН ИХРЕСПУБЛИК А 1. (19) (И) 51)4 С 06 Р 22 ИЯОПИСАК АВТОРСКОМ РЕТ ЕЛЬСТВ В ство СССР2, 1982.В .20326611980.(57) Изобретениелительной техникепользовано при поизводительных про Е УСТРОЙСТВ тносигся к вычиси может быть истроении высокопроессоров. Целью ОСУДАРСТВЕННЫЙ КОМИТЕТ СС ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ 1) 3952807/24-242) 09,09,856) 07.06.87. Бюл. У 211) Институт электронных управляющи машин,изобретения является расширение области применения устройства за счетвведения средств для динамическойдешифрации команд и повышение егонадежности за счет исключения одновременной дешифрации команды и выборки начальной микрокоманды в одномцикле работы устройства. С этой целью в устройство, содержащее регистрмикрокоманды, блок постоянной памяти микрокоманд, блок динамическойпамятИ микрокоманд, формирователь адреса микрокоманды и мультиплексор адреса микрокоманды, введены дешифратор номера слова, счетчик адреса микрокоманды, тактовый генератор, триггер режима, триггер конца передачи,двунаправленный коммутатор адреса,две группы элементов И, пять элементов ИЛИ, четыре элемента И и три элемента И-НЕ. 9 ил.ва, первый вход третьего элемента ИЛИ подключен к первому входу синхронизации устройства ивходу синхронизации регистра микрокоманды, первый и вто рой входы первого элемента И-НЕ сое 50 55 манды, блок постоянной памяти микрокоманд, блок динамической памятимикрокоманд, формирователь адресамикрокоманды и мультиплексор адреса микрокоманды, причем выход блокапостоянной памяти микрокоманд соединен с входом данных регистра микрокоманды, выход поля адреса очередноймикрокоманды и выход поля микропереходов регистра микрокоманды подключены к управляющему входу формирователя адреса микрокоманды, выход которого соединен с выходом адресамикрокоманды устройства, адреснымвходом блока постоянной памяти микрокоманд.и первым входом данныхмультиплексора адреса микрокоманды,выход которого подключен к адресному входу блока динамической памятимикрокоманд, о т л и ч а ю щ е е с ятем, что, с целью расширения областипримерения устройства за счет введения средств для динамической дешифрации команд и повышения его надежности за счет исключения одновременной дешифрации команды и выборки начальной микрокоманды в одном циклеработы устройства, оно.содержит дешифратор адреса регистра, дешифраторномера слова, счетчика адреса микрокоманды, тактовый генератор, триггер.режима, триггер конца передачи, двунаправленный коммутатор данньхдвунаправленный коммутатор адреса, двегруппы элементов И-НЕ, группу элементов И, пять элементов ИЛИ, четыреэлемента И и три элемента И-НЕ, приэтом первые входы первого и второго элементов ИЛИ соединены соответствен" но с входом загрузки устройства ивходом признака дешифрации устройстдинены соответственно с вторым входом синхронизации устройства и операционным выходом регистра микрокоманды, который подключен также к операционному выходу устройства, первыйвход первого элемента И соединен свходом признака дешифрации устройства, вторые входы первого и второгоэлементов ИЛИ подключены к входу режима устройства, первый и второй входы дешифратора адреса регистра ивходы элементов И-НЕ первой группысоединены с адресным входом устрой 5 10 15 20 25 30 35 ства, вход сброса регистра микрокоманды и первый вход второго элемента И подключены к входу сброса устройства, первый выход дешифратораадреса регистра соединен с первымвходом третьего- элемента И, выходомпризнака блокировки устройства ипервыми управляющими входами двунаправленных коммутаторов данных и адреса, первый вход-выход данных двунаправленного коммутатора данных подключен к входу-выходу данных устройства, вьход триггера конца передачисоединен с первыми входами второгоэлемента И-НЕ и четвертого элементаИЛИ и выходом признака готовностиустройства, выход первого элементаИ-НЕ подключен к второму входу второ"го элемента И, выход которого соединен с входом сброса триггера режима,вход установки которого подключенк выходу второго элемента ИЛИ, прямой выход триггера режима соединен свыходом адреса микрокоманды устройства, вход разрешения обращения блока постоянной памяти микрокоманд ипервыми входами эпементов И-НЕ второй группы, выходы которых подключены к входу данных регистра микрокоманды, вторые входы элементов И-НЕвторой группы соединены с входом-выходом данных блока динамической памяти микрокоманд и первым входомвыходом данных двунаправленного коммутатора адреса, второй вход-выходданных которого подключен к второмувходу-выходу счетчика адреса микрокоманды и триггера режима, выход дешифратора номера слова соединен свторым управляющим входом двунаправленного коммутатора адреса и первымивходами элементов И группы, выходыкоторых подключены к входу разрешения обращения блока динамическойпамяти микрокоманд, инверсный выходтриггера режима соединен с вторымивходами элементов И группы и первымуправляющим входом дешифратора номера слова, второй выход дешифратораадреса регистра подключен к входу Записи блока динамической памяти микро-.команд, второй вход и выход третьегоэлемента И соединены соответственнос вторым вхоцом дешифратора адресарегистра и первым входом третьегоэлемента И-НЕ, который подключен квторому управляющему входу дешифратора номера слова и вторым входомпервого элемента И и четвертого эле20 74 19 13159 мента ИЛИ, выход которого соединен со счетным входом счетчика адреса микрокоманды, выход которого подключен к входу данных дешифратора номера слова и второму входу данных мультиплексора адреса микрокоманды, управляющий вход которого соединен с выходом первого элемента И; третий выход дешифратора адреса регистра подключен к второму входу третьего 10 элемента И-НЕ и первому входу пятого элемента ИЛИ, второй вход которого соединен с выходом тактового генератора, входом синхронизации триггера конца передачи и третьим управ ляющим входом дешифратора номера слова, выход пятого элемента ИЛИ подключен к входу синхронизации триггера режима и первому входу четвертогоэлемента И, второй вход и выход которого соединены соответственно с выходом третьего элемента ИЛИ и входомразрешения записи счетчика адресамикрокоманды, выход первого элементаИЛИ подключен к второму входу третьего элемента ИЛИ и третьему входутретьего элемента И-НЕ, выход которого соединен с вторым входом второгоэлемента И-НЕ и входом сброса триггера конца передачи, выходы элементовИ-НЕ первой группы подключены к третьему входу дешифратора адреса регистраи входу запуска тактового генератора,а выход второго элемента И-НЕ соединен с вторым управляющим входом двунаправленного коммутатора данных.1315974 7 Отбо 758 157УУ 100 119 ид Ввфб тв 97тбб дб тб ВУ 197 1д 75 У тбв И ПУ то 2702 тоу1057 У 1 775711 УОтт 5 192 ит 125 11315974 Адрес ячейки ааиящи блока ДПИК прес качаяьноао слаба кикрокоманды И 70 У д 7 Е б Ф Ю 2 7 0 Разряды счеячика адреса микракоианды фиг. д, сброса режима Триггер режима (единичное плече)Фиг, У Составитель Г. ВиталиевРедактор И. Николайчук Техред М.ХоданичКорректор Л. Патай Заказ 2364/51 Тираж 672 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113 д 35, Москва, И, Раушская наб., д. 4/51 13159Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных процессоров,Целью изобретения является расширение области применения устройства за счет. введения средств для динамической дешифрации команд и повышение его надежности за счет исключения одновременной дешифрации команды 10и выборки начальной микрокоманды водном цикле работы устройства,На фиг. 1 показана структура цифровой вычислительной системы; нафиг. 2 - структурная схема базовой 15части процессора; на фиг. 3 - функциональная схема микропрограммногоустройства управления; на фиг. 4 -структура формирователя адреса микрокоманды; на фиг. 5 - принципиальная схема тактового генератора устройства; на фиг, 6 - функциональнаясхема пульта управления и индикации;на фиг. 7 - временная диаграмма процесса загрузки/тестирования ячеекпамяти блока динамической памяти микрокоманд в базовом режиме; на фиг.8 -Формат адресного слова блока динамической памяти микрокоманд в базовомрежиме; на фиг. 9 - временная диаг- ЗОрамма выхода устройства из специального режима.Цифровая вычислительная системаСодержит (фиг, 1) процессор 1, объединяющий базовую часть 2 и микропрограммное устройство 3 управления,блок 4 оперативной памяти и контроллер 5 внешнего устройства. Связьмежду устройствами осуществляетсячерез магистраль 6 ."Общая шина", используемую для передачи адресов,данных и управляющих сигналов.В состав базовой части 2 процессора (фиг. 2) входят устройство 7 управления, устройство 8 путей данных, 45блок 9 связи с магистралью 6 "Общая шина" и пульт 10 управления и индикации. Устройство 7 содержит регистр 11 команды, дешифратор 12 команд и формирователь 13 тактов. В 50устройство 8 включены мультиплексор14 слова состояния процессора, регистр 15 состояния процессора, блок16 регистров, арифметико-логическоеустройство 17, первый 18 и второй 19 55мультипЛексоры данных. Шины связибазовой части 2 процессора и микропрограммного устройства 3 управленияследующие: шина 20 данных, шина 21 74 2 адреса микрокоманды, шина 22 адреса выбора устройства. Магистраль 6 связана двунаправлен" ными шинами с входами-выходами 23 блока 10 и 24 блока 9, вход 25 которого, как и вход 26 блока 17, подключен к выходу 27 блока 16, а вход 28 вместе с входами 29, 30 и 31 соответственно блоков 11, 14 и 16 - к выходу 32 блока 19, вход 33 которого, как и двунаправленная шина 20, другим концом соединяемая с входом 34 двунаправленного коммутатора 35 данных (Фиг. 3), подключен к выходу 36 блока 18. Входы 37 и 38 блока 18 соеди" иены с выходами 39 и 40 соответственно блоков 9 и 15, а вход 41 - с выходом 42 блока 17 и входом 43 блока 14, Выход 44 блока 14 подключен к входу 45 блока 15, своим выходом 46 связанного с входом 47 блока 11 и линией 48 режима с входом 49 элемента ИЛИ 50 (фиг. 3) и входом 51 элемента ИЛИ 52. Вход 53 элемента ИЛИ 52, объединенный с входом 54 элемента И 55 через линию 56 признака дешифрации подключен к выходу 57 блока 12, выходом 58 соединенного с входом 59 блока 10 и через шину 21 с адресным входом 60 блока 61 постоянной памяти микрокоманд (ППМК), входом 62 данных мультиплексора 63 адреса микрокоманды и выходом 64 формирователя 65 адреса микрокоманды. Вход 66 блока 1 подключен к выходу 67 блока 11, выход 68 которого через линию 69 загрузки связан с входом 70 элемента ИЛИ 50, выходы 71 и 72 блока 13 через линии 73 и 74 синхронизации соединены соответственно с входом 75 элемента ИЛИ 76 и входом 77 элемента И-НЕ 78. Выход 79 блока 9 лини" ей 80 сброса соединен с входом 81 элемента И 82, а выход 83 этого бло" ка с помощью шины 22 - с входом 84 группы 85 элементов И-НЕ и первыми двумя входами 86 дешифратора 87 адреса регистра. Вход 88 блока 9 через линию 89 признака занятости подключен к выходу 90 триггера 91 конца передачи, соединенному также с входом 92 элемента И-НЕ 93 и входом 94 элемента ИЛИ 95, а вход 96 блока 18 через линию 97 признака блокировки " с выходом 98 блока 87, соединенным также с входом 99 элемента И 100 и с входами 101 и 102 управления коммутатора 35 и имеющего вход 103 дан 3 131597 ных двунаправленного коммутатора 104 адреса.Вход-выход 105. (фиг. 3) данных блока 106 динамической памяти микро- команд (ДПМК) соединен с объединен- ньяи входом 103 и .выходом 107 бло.ка 104, а также входом 108 группы 109 элементов И-НЕ, Вход 110 группы 109 элементов И-НЕ вместе с входом 111 разрешения обращения блока 61 10 и линией 112 шины 21 связан с прямым выходом 113 триггера 114 режима, а выход 115, как и выход 116 блока 61, подключен к шине 117 микрокоманды, соединяющей их с входом 118 данных 15 регистра 119 микрокоманды.Выход 120 регистра 119 связан с входом 121 блока 65, выход 122 - с входом 123 элемента И-НЕ 78, выходом 124 подключенного к входу 125 элемента И 82, связанного выходом 126 с входом 127 триггера 114, вход 128 которого связан с выходом 129 элемента ИЛИ 52, вход 130 синхронизации, объединенный с входом 131 элемента 25 И 132, подключен к выходу 133 элемента ИЛИ 134, а вход 135 данных связан с линией информационной шины 136, соединяющей также вход-выход 137 блока 104, объединенные вход и выход 30 138 блока 35 и вход 139 данных счетчика 140 адреса микрокоманды. Вход 141 разрешения записи и счетный вход 142 счетчика 140 подключены к выходам 143 и 144 соответственнр элементов 35 И 132 и ИЛИ 95, а выход 145 - к входу 146 данных дешифратора 147 номера слова и второму входу 148 данных блока 63, вход 149 которого соединен с выходом 150 элемента И 55, а выход 40 151 подключен к адресному входу 152 блока 106, вход 153 разрешения обращения которого связан с выходами 154 элементов И. группы 155, а вход 156 записи - с входом 157 элемента И 100 5 и выходом 158 дешифратора 87. Второй вход 159 дешифратора 87 подключен к шине 22, третий вход 160 объединен с входом 161 запуска тактового генератора 162 и выходом 163 блока 85, 50 а выход 164 - с входом 165 элемента И-НЕ 166 и входом 167 элемента ИЛИ 134,. Вход 168 последнего связан с выходом 169 блока 162, входом 170 синхронизации триггера 90 и управляющим входом 171 дешифратора 147, второй управляющий вход 172 которого вместе с входом 173 блока 155 под 4 4ключен к выходу 174 триггера 114, а третий управляющий вход 175 вместе с входом 176 элемента 95, входом 177 элемента 55 и входом 178 элемента 166 - к выходу 179 элемента И 100. Вход 180 элемента И-НЕ 166 связан с выходом 181 элемента ИЛИ 50 и входом 182 элемента ИЛИ 76, выход 183 которого соединен с входом 184 элемента И 132, выход 185 элемента И-НЕ 166 подключен к входу 186 сброса триггера 91 и входу 187 элемента И-НЕ 93, выходом 188 связанного с управляющим входом 189 управления коммутатора 35. Выход 190 блока 147 соединен с входом 191 блока 104 и входом 192 блока 155, а входы 193 синхронизации и 194 сброса блока 119 - с входом 75 элемента ИЛИ 76 и входом 81 элемента И 82.формирователь 65 адреса микро- команды (фиг, 4) содержит схему 195 управления микропереходами, группу 196 элементов НЕ и дешифратор, 197 поля переходов, вход 198 которого, как и вход 199 группы 196, подключен к выходу 120 блока 119, а выход 200 - к входу 201 схемы 195, принимающей на второй вход из базовой части 2 процессора условия микропереходов и своим выходом 202 совместно с выходом 203 группы 196 подключенной к шине 21 адреса микрокоманды.Тактовый генератор 162 (фиг. 5) содержит два одновибратора 204 и 205 и четыре времязадающих элемента 206- 209, единичное плечо 210 одновибратора 204 соединено с входом 211 запуска одновибратора 205, по два входа каждого одновибратора отведены для.подключения времязадающих элементов, еще два входа, связанных с +ЗВ, обеспечивают разрешение запуска и запрет сброса одновибраторов.Пульт 10 управления и индикации (фиг. 6) содержит клавиатуру 212, формирователь 213 сигналов управления, счетчик 214 адреса, мультиплексор 215 индикации, индикатор 216, ре. гистр 217 адреса микрокоманды и связанный через вход-выход 23 с магистралью 6 "Общая шина" узел 218 приемо- передачи, Выход 219 узла 218 подключен к входу 220 мультиплексора 215, а вход 221- к выходам 222, 223 и 224 соответственно узлов 213, 214 и 212, выход 224 последнего связан также с входами 225 и 226 узлов 213 и 214.Блок 106 предоставляет пользователю воэможность дополнять базовую систему команд процессора командами, ориентированными на выполнение требуемых в данном конкретном случае функций. Для этого пользователь должен на микропрограммном уровне опи 5 131597Вход 227 узла 216 соединен с выходом228 узла 215, входы 229 и 230 которого соответственно напрямую и черезузел 217 подключены к шине 21 адреса микрокоманды. 5Устройство работает следующимобразом.Входящий в состав устройства 364-разрядный регистр 119 принимает свыходов блока 61 или блока 106 (через группу 109 элементов И-НЕ) и втечение одного цикла хранит информацию об исполняемой микрокоманде.Количество разрядов регистра обеспечивает прием и хранение микрокоманд расширенного формата, что способствует повышению эффективностисоздаваемых команд, Для его построения может быть использована интегральная микросхема (ИМС), содержащая 20шесть Э-триггеров, каждый из которыхимеет выход и три входа: данных,синхронизации и сброса. Загрузка микрокоманды в регистр производится вконце текущего цикла задним фронтом 25тактового сигнала ТП процессора, сигналом общего сброса регистр можетбыть очищен. Разряды полей микрокоманды регистра используются при формировании управляющих сигналов процессора,В состав устройства (фиг, 3) входят два блока памяти микрокоманд:блок 61 ППМК и блок 106 ДПМК. Блок61 организовай на прожигаемых элементах памяти емкостью 1 К и используется для хранения микропрограмм базовой системы команд процессора. Каждыйэлемент данного типа имеет восемьадресных входов, два управляющих 40входа и четыре выхода с открытымиколлекторами. На первых управляющихвходах элементов присутствует постоянный разрешающий уровень, вторыеобъединены и подключены к выходу 45триггера 114 режима. Адресация элементов блока 61 происходит через шину 21 сигналами с выходом дешифратора 12 (во время дешифрации командбазовой системы) или формирователя65 (в ходе выполнения микропрограмм),Группа 196 элементов НЕ формирователя 65 (фиг, 4) с открытыми коллекторами обеспечивает возможность подключения к шине 21 выходов разрядовполя адреса очередной микрокомандырегистра 119, а схема 195 - коррекцию этого адреса по результатам расшифровки разрядов поля переходов ре 1315974сать структуру дополнительных команд, загрузить их в блок 106 и, по мере необходимости, к ним обращаться. Схема блока 106 выполнена на перезаписываемых элементах памяти. Каждый элемент допускает запись, хранение и считывание до 1 К четырехбитных слов, Элемент имеет десять адресных входов, четыре входа-выхода данных с тремя состояниями для запи си/считывания информации и два управляющих входа; первый - для разрешения работы элемента, второй - для выбора типа операции (запись или считывание). При отсутствии разрешаю щего (низкого) уровня на первом входе все входы-выходы элемента находятся в третьем состоянии. Блок 1 Об обеспечивает одновременное хранение до 1 К 64-разрядных микрокоманд. Для 20 удобства записи/считывания микрокоманд в массив каждая микрокоманда разбита на четыре 16-разрядных слова. В соответствии с этим блок 106 разделен на четыре части, каждая из 25 которых выполняет запоминание "своего" слова.Возможность выполнения последовательной загрузки с информационнойшины 136 в блок 106 четырех 16-разрязных слов и обратного чтения их на шину, а также считывания из блока 106 64-разрядной микрокоманды с ее передачей через двувходовые элементы с открытыми коллекторами группы 109 элементов И-НЕ на шину 117 микрокоманды устройства обеспечивается приемопередатчиками коммутатора 104, Последний содержит 64 приемопередатчика, разбитых на четыре группы по 40 16 приемапередатчиков в каждой. Связанные проводником вход и выход каждого приемопередатчика подключены к входу-выходу соответствующего разряда блока 106. Входы-выходы одноимен ивах (нулевых, первых , пятнадцатых) разрядов всех" четырех групп объединены и подключены к соответствующим разрядам 16-разрядной, шины 136.Предусмотрены два режима работы 50 устройства: базовый и специальный, Базовый режим обеспечивает работу процессора в базовой системе команд, а также двусторонний обмен ин. формацией между пультом 10 управле ния и индикации и блоком 106, спе-, циальный - работу с запрограммированными в блоке 106 командами. Переключением режимов управляет триггер 114 режима например, динамический Р- триггер ИМС). Базовому режиму соответствует нулевое .состояние триггера, специальному - единичное. В процессе обмена информацией между пультом 10 и блоком 106 организуются загрузка данными и чтение с выходом на индикацию пульта 10 содержимого пере. записываемых элементов памяти блока 106. Загрузка/чтение производится программно, с помощью специальных подпрограмм, или вручную, путем набора необходимой информации на клавиатуре пульта 10. Начальная установ. ка базового режима производится автоматически при включении питания. Управление загрузкой/чтением 64-разрядных микрокоманд в блоке 106 берут на себя схемы генератора 162, счетчика 140, мультиплексора 63, дешифратора 147, группы 85 элементов И-НЕ и дешифратора 87. Каждая из названных операций осуществляется последовательной засылкой/чтением в блок 106 четырех 16-разрядных слов: СОСЗГенератор 1 б 2 (фиг. 5) построен на двух последовательно соединенных одновибраторах, каждый из которых имеет по одному входу запуска, разрешения, сброса, два входа для подключения времязадающнх элементов, а также парафазный выход. Входы запуска и .разрешения объединены в микросхеме по схеме И, что позволяет выполнять их рокировку, но рассчитаны на прием разнополярных сигналов. Запуск одновибраторов осуществляется восходящим (нисходящим) фронтом запускающего импульсаПри этом на входе разрешения должен быть логический уровень напряжения, разрешающий запуск. Длительность импульса, формируемого одновибратором, определяется номиналами времязадающих элементов,подключенных к соответствующим входам. Вход 211 запуска второго одновибратора205 соединен с единичньм выходом 210 первого одновибратора 204, выдающим импульс положительной полярности. Поскольку в качестве разрешающего уровня работы обоих одновибраторов взят высокий, запуск первого одновибратора 204 производится нисходящим фронтом входного импульса, за-пуск второго - задним фронтом импульса с выхода первого одновибратора 204. Тактовый сигнал Т (импульс отрицательной полярности), вырабатываемый40 9 131597 вторым одновибратором 205 (первый создает задержку начала его формирования), передним фронтом стробирует запись в счетчик 140 и запись/чтение в блоке 106, а задним - устанавливает в единичное состояние триггер 90Счетчик 140, доступный при обращении с магистрали 6 "Общая шина" (адрес 177542), в базовом режиме Формирует 12-разрядный адрес записывае мого/считываемого в блоке 106 слова.Блок 140 построен на счетчиках, что обеспечивает автономный последовательный переборадресов при выполнении операции, Каждый четырехразрядный 5 счетчик имеет четыре входа данных, счетный вход (инкрементации), вход разрешения записи, вход установки в нуль выходы четырех разрядов и выход прямого переноса, позволяющий 20 осуществить каскадное соединение счетчиков без дополнительной логики (в предлагаемом устройстве блок 140 образован каскадным соединением трех счетчиков, что дает возможность адре совать до 1 К 64-разрядных микрокоманд блока 106). Каскадное соединение счетчиков выполнено соединением выхода прямого переноса с входом инкрементации следующего счетчика. 30 Приращение содержимого счетчика осуществляется по положительному перепаду тактового импульса. Начальная загрузка элементов блока 140 производится через входы данных в момент поступления низкого уровня на объединенные входы разрешения записи счетчиков (входы установки в нуль также объединены и подключены к уровню запрета сброса счетчиков).Подключение выходов счетчика 140 к адресным входам блока 106 ДПМК осуществляется через мультиплексор 63, Для его построения может быть использована, например, ИМС, содержащая че тыре двухвходовых мультиплексора и имеющая четыре пары информационных входов, четыре выхода и два управляющих входа, первый иэ которых используется для разрешения работы микро схемы, второй - для выбора одного иэ двух возможных источников входного сигнала. Мультиплексор 63 содержит три микросхемы, объединенные общим управлением по второму входу (на 55 первом - постоянный разрешающий уровень). На первый вход данных мультиплексора адрес поступает с шины 21 адреса микрокоманды, на вторые - с 4 10выходов счетчика 140. Мультиплексоробеспечивает выбор любого из них вкачестве источника 10-раэрядного адреса микрокоманды,Временная диаграмма загрузки начального слова СИ микрокоманды (первого из четырех) в блок 106 приве,цена на фиг, 7. Перед началом загрузки в счетчик 140 заносится адрес начального слова (СИ) загружаемой микрокоманды. Для этого с помощью клавиатуры 212 пульта 10 выполняются наборадреса счетчика 140 (177542) с запоминанием его в счетчике 214, наборадреса начального слова СИ микрокоманды и одновременная выдача их вместе с генерируемыми формирователем 213кодом операции записи и сигналомсинхронизации СхЗ через узел 2 18 приемопередачи на магистраль 6 "Общаяшина". При этом адрес счетчика 140поступает по линиям адреса, а адресслова СИ - по линиям данных, Принятый с линий данных приемопередатчиками блока 9 адрес слова С 9 попадает через блок 18 на шину 20 данныхи далее через коммутатор 35 и шину136 поступает на вход данных счетчика 140. Разрешение на его прохождение в устройство 3 и загрузку всчетчик 140 формируется в результате расшифровки адреса счетчика, выполняемой группой 85 элементовИ-НЕ и дешифратором 87, имеющим триадресных входа, три управляющих ивосемь выходов. Три управляющих входа, объединенные в микросхеме по схеме И (два по низкому уровню и одинпо высокому), используются для приема разрешения работы дешифратора,любая иэ восьми комбинаций сигналовна адресных входах, при наличии разрешения, обеспечивает появление низкого уровня на соответствующем выходе. Работой дешифратора 87 управляютгруппа 85 элементов И-НЕ и блок 9,Формирующие, разрешение работы и сигналы для входов дешифратора 87. Сигналы разрешения поступают на входы159 и 160 (на третьем управляющемвходе - постоянный разрешающий уровень) дешифратора 87 в момент началапередачи по магистрали 6 "Общая шина" при наличии на ее адресных линиях адреса устройства 3 (177540). Приэтом сигнал СхЗ (через вход 159), атакже тринадцать старших разрядов адреса (А 15 АЗ), поступающих с выходовприемников общей шины блока 9 на шину11 1315974 22 и далее,на входы двух восьмивходовых схем совпадения группы 85 (А 15 А 8 - на входы первой схемы, сигнал 12 с выхода первой схемы А 7АЗ, причем нулевые значения разрядов через элементы НЕ на входы второй схемы), сигналом с выхода 163 второй схемы разрешают работу дешифратора 87, а последний - также запуск генератора 162, Входы дешифратора 87 подключены к выходам приемников первого и второго разрядов адреса (А 1 и А 2), а также сигнала С 1 блока 9. РазрядыА 1 и А 2 определяют адрес регистра, ккоторому должно произойти обращение(177542 или 1.77544), сигнал С 1тип операции (запись в регистр иличтение). Выход 164 дешифратора 87связан через элементы 166 и 93 (навходе 92 элемента 93 присутствуетразрешение с нулевого плеча триггера конца передачи) с первыми входами управления приемопередатчиков коммутатора 35, обеспечивая прием данных на входы счетчика 140, а также с входом элемента 134, формирующего сигнал загрузки счетчика, При выборе данного выхода дешифратора такт Т через второй вход элемента 134 и элемент 132 проходит на входы 141 разрешения записи счетчика 140, разрешая загрузку в него данных. Выход элемента 134 связан также с входом 130 синхронизации триггера 114 режима, что используется при переключенииМрежимов работы устройства 3 После окончания загрузки задним фронтом такта Т устанавливается в единичное состояние Р-триггер 91, сообщая по линии 89 о завершении передачи информации. Входы установки и данных триггера 91 подключены к уровню напряжения + ЗВ, вброс триггера производится через вход 186 сброса в момент снятия в блоке 10 сигнала СхЗ.Два других выхода дешифратора 87 (выход 158 управления записью в регистр данных и выход 98 управления чтением из регистра данных) выдают сигналы в момент обращения к регистру данных (адрес 177544). Регистром данных является, фактически, вся область загружаемого блока 106: при каждом обращении к указанному регистру принимаемое из базовой части 2процессора слово данных записывается по адресу, определяемому текущимсодержимым счетчика 140, с последующим приращением (инкрементацией) этого адреса. Для этого два указанных выхода дешифратора 87 подключены к входам элемента 100, сигнал свыхода которого отпирает через элементы.166 и 93 приемопередатчикикоммутатора 35, выбирает через элемент 55, связанный с управляющим вхо"дом мультиплексора 63, счетчик 140в качестве источника адреса блока 10 106, а также, поступая на вход 175дешифратора 147 и вход элемента 95,подготавливает эти схемы к управлению соответственно загрузкой блока106 и приращением содержимого счет чика 140, Подключение данных выходов дешифратора 86 к вторым управляющим входам 156, 101 и 102 соответственно элементов памяти блока 106,приемопередатчиков коммутатора 35 20 и коммутатора 104 задает направлениепередачи информации.Формат слова, используемого в базовом режиме для адресации ячеек памяти блока 106, показан на фиг. 8.25 Десять младших (09) разрядов, содержащих адрес загружаемой/читаемоймикрокоманды, принимаются из базовой части 2 процессора в разряды211 счетчика 140. Десять соответ ствующих выходов счетчика, подключенных к адресным входам (разряды09) блока 106, задают адрес на-чального слова микрокоманды. Старшиеразряда адреса (10 и 11), принимаемые в разряды 0 и 1 счетчика 140, содержат код номера очередного записываемого/читаемого слова. Расшифровка данного кода производится дешифратором 147. Четыре его выхода, соот ветствующие номерам слов 03, через группу 155 элементов И нодключены к первым управляющим входам четырех групп приемопередатчиков коммутатора 104, разрешая в момент срабаты вания дешифратора запись/считываниеслова с данным номером в блоке 106.Момент срабатывания дешифратора идлительность сигнала управления записью/считыванием определяются по сов падению трех сигналов на входах управления дешифратора: признака режима - с нулевого плеча 174 триггера114, признака обращения к региструданных - с выхода элемента 100, так та Т.Приращение содержимого счетчика140 производится каждый раз послезавершения приема в блок 106 очередного слова сигналом, формируемым5974 14 5 10 15 20 25 30 35 40 45 50 55 13. 131 триггером 91. Счетный вхоц первого счетчика блока 140 связан с выходом элемента 95. В момент сброса триггера.91,совпадение сигналов на входах элемента 95 нарушается и положительный перепад на счетном входе счетчика приводит к записи в него единицы (на второй вход элемента 95 поступает сигнал с выхода элемента 100, разрешающий инкрементацию счетчика только при обращении к регистру данных). Содержимое счетчика 140 после загрузки слов СИСЗ определяет адрес начального слова следующей мик" рокоманды.Операция чтения из блока 106 осуществляется аналогично операции записи в него, за исключением того,что изменяется направление передачи процессора. Кроме того, в момент передачи слова данных из устройства 3 в базовую часть 2 мультиплексор18 должен быть блокирован, т.е. его выходы на шину 20 данных должны находиться в третьем состоянии. Устанавливать блокировку необходимо до начала передачи и снимать после ее завершения. Для этого выход 98 дешифратора 87 адреса регистра соединен с входом 96 мультиплексора 18. Появление сигнала на выходе дешифратора блокирует работу мультиплексора и с задержкой на элементах 100, 166 и 93 разрешает выдачу информации на шину 20 данных. После завершения передачи (т.е. после установки в единичное состояние триггера 91) снимается разрешение на входе 92 элемента 93 и приемопередатчики коммутатора 35 блокируются. Далее, в момент снятия сигнала СхЗ, выключается дешифратор 87 разрешая работу мультиплексора 18, через элементы 100 и 166 выдается запрешающий уровень на вход 187 элемента 93 и сбрасывается триггер 91.Специальный режим работы устройства 3, определяемый единичным состоянием триггера 114 режима, передает управление работой процессора командам, реализованным в блоке 106. Установка данного режима может преследовать одну из следующих целей: работа с программами и отладка мик-. ропрограмм. В первом случае обращение к заключенным в блоке 106 микропрограммам производится в ходе вшполнения программы блока 4 оперативной памяти. Для перехода к выполнениюзапрограммированной в блоке 106команды (или последовательности команд) предшествующая команда блока 4 должна осуществить загрузку единицыв девятый разряд регистра 15 процессора. Сигнал с выхода девятого разряда данного регистра блокирует запись в регистр 11 команды базовойчасти 2 процессора, одновременноразрешая прием последующих команд всчетчик 140 устройства 3 и установкуспециального режима. Разрешение поступает по линии 48 на входы элементов ИЛИ 50 и 52, первый из которыхиспользуется при загрузке командыв счетчик 140, второй - при переключении режимов.Загрузка команды в счетчик производится во второй (0016) из трех начальных микрокоманд 0000, 0016,0015, общих для всех команд процессора. Сигнал загрузки, поступающий изустройства 7 управления на вход 70элемента ИЛИ 50, разрешает через элементы 166 и 93 пропуск загружаемойкоманды с шины 20 на шину 136. Выход элемента ИЛИ 50 соединен такжес входом элемента ИЛИ 76. Принимаемый в конце .цикла на его вход 75 тактпроцессора ТП 1 осуществляет черезэлемент И 132 загрузку команды с шины 136 в счетчик 140. В следующеймикрокоманде (0015) сигнал дешифрации команды, поступая на вход 53 элемента ИЛИ 52, устанавливает в единичное состояние триггер 114, а такжеделает (с помощью элемента И 55)счетчик 140 источником адреса блока 106,Срабатывание триггера 114 режима вызывает: переключение входов регистра 119 с выходов блока 61 на выходы элементов с открытыми коллекторами группы 109 (подачей запрещающего уровня на вход 111 блока 61 и разрешающего уровня на один из входов двухвходовых элементов узла 109), снятие блокировки элементов памяти блока 106 (подачей через группу 115 элементов И разрешающего уровня на первые входы управления элементов памяти), блокировку дешифратора 174 (подачей запрета на вход 172 дешифратора) и индикацию с помощью узла 216 блока 10 признака установки специального режима.15 13Код принимаемой счетчиком 140 команды несет в себе адрес микропрограммы этой команды. При исполнении микрокоманды 0015, в момент поступления из базовой части 2 процессора сигнала дешифрации команды, этот код беспрепятственно проходит на адресные входы блока 106, определяя ячейку блока с идентичным адресом, содержащую ее начальную микрокоманду, т.еадрес микропрограммы этой команды. Выбранная микропрограмма загружается в конце цикла в регистр 119 и в следующем цикле исполняется. Таким образом, в данном устройстве используется укороченная цепь обработки команды:, регистр команды - память микрокоманд (вместо общепринятой: регистр команды - дешифратор команд - память микрокоманд). Использование укороченной цепи не только экономит оборудование, но и снижает требования к быстродействию используемых в блоке 106 элементов памяти, поскольку исключается необходимость выполнения в одном цикле микрокоманды двух операций, связанных с обращением к относительно медленнодействующим элементам памяти: считывание адреса микропрограммы в дешифраторе команд и начальной микрокоманды в блоке 106, Адрес каждой последующей микро- команды определяется разрядами поля текущей, поступающими с шины 21 адреса микрокоманды через мультиплексор 63 на адресные входы блока 106. Одновременно оба адреса высвечиваются на индикаторах 216 блока 10 (с помощью узлов 215 и 217). Последняя выполняемая микрокоманда каждой микропрограммы блока 106 в поле адреса очередной микрокоманды содержит адрес 0000, а в одном из неиспользуемых в специальном режиме разрядов - разрешение сброса триггера 114. Вход 127 сброса триггера подключен к выходу элемента 82, вход 80 которого принимает сигнал общего сброса процессора, а вход 125 обеспечивает установку триггера в нулевое состояние в случае совпадения на входах элемента И-НЕ 78 указанного разрешения и поступающего из базовой части 2 процессора на вход 77 такта ТП 2, Триггер 114 (фиг. 9) сбрасывается в начале второй половины цикла данной микрокоманды, обеспечивая снятие блокировки блока 61, считывание из него микрокоманды с адресом , 15974 16 5 10 15 20 25 ЗО 35 40 45 50 55 0000 и загрузку ее в конце цикла в регистр 19, Очередная команда из блока 4 во время исполнения микрокоманды 0015 вновь поступает в счетчик 140, поскольку девятый разряд регистра 15 процессора остается по-прежнему в единице и прием в регистр 11 запрещен, после чего процесс повторяется, Для возврата к базовой системе команд процессора девятый разряд регистра 15 должен быть установлен в ноль, что выполняется специальной запрограммированной в блоке 106 командой.Второй способ перехода к специальному режиму работы устройства 3 используется при отладке микропрограмм с помощью блока 10 в режиме работы процессора по микрошагам. Для установки специального режима и обращения к произвольной микропрограмме блока 106 в 15-и разряде загружаемого в счетчик 140 слова адреса начальной микрокоманды этой микропрограммы выставляют единицу. Пятнадцатый разряд шины 136 подключен непосредственно к входу данных триггера 114В момент загрузки адреса в регистр .сигнал с выхода элемента 134 устанавливает триггер в единичное состояние с описанными последствиями (смена источника информации регистра 119, снятие блокировки элементов памяти блока 106, блокировка дешифратора 147, индикация признака режима управления). Далее, следуя по микро- шагам, вйполняются микрокоманды 0000, 0016 (при этом содержимое счетчика 140 не меняется ввиду отсутствия единицы в девятом разряде ре.гистра 15) и 0015. Поступление сигнала дешифрации команды в цикле выполнения микрокоманды 0015 вызывает .обращение к блоку 106 по записанному в счетчике 140 адресу и прием регистром 119 определяемой этим адресом микрокоманды. Выборка и исполнение последующих микрокоманд происходят до конца микропрограммы как и в первом варианте перехода к специальному режиму (только в режиме работы процессора по микрошагам). Для обращения к новой микропрограмме необходимо снова заслать в счетчик 140 соответствующий адрес с единицей в пятнадцатом разряде.Формула изобретенияМикропрограммное устройство управления, содержащее регистр микроко

СмотретьЗаявка

3952807, 09.09.1985

ИНСТИТУТ ЭЛЕКТРОННЫХ УПРАВЛЯЮЩИХ МАШИН

ЛИТВИНОВ ВИКТОР ВАСИЛЬЕВИЧ, ШВЕИН АЛЕКСЕЙ АНАТОЛЬЕВИЧ, ШУМЕЙ АЛЕКСАНДР СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.06.1987

Код ссылки

<a href="https://patents.su/14-1315974-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Преобразователь временного интервала в двоичный код

Следующий патент: Многоканальное устройство для управления обслуживанием запросов

Случайный патент: Устройство для управления электромагнитным тормозом