Устройство для обработки выражений языков программирования

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

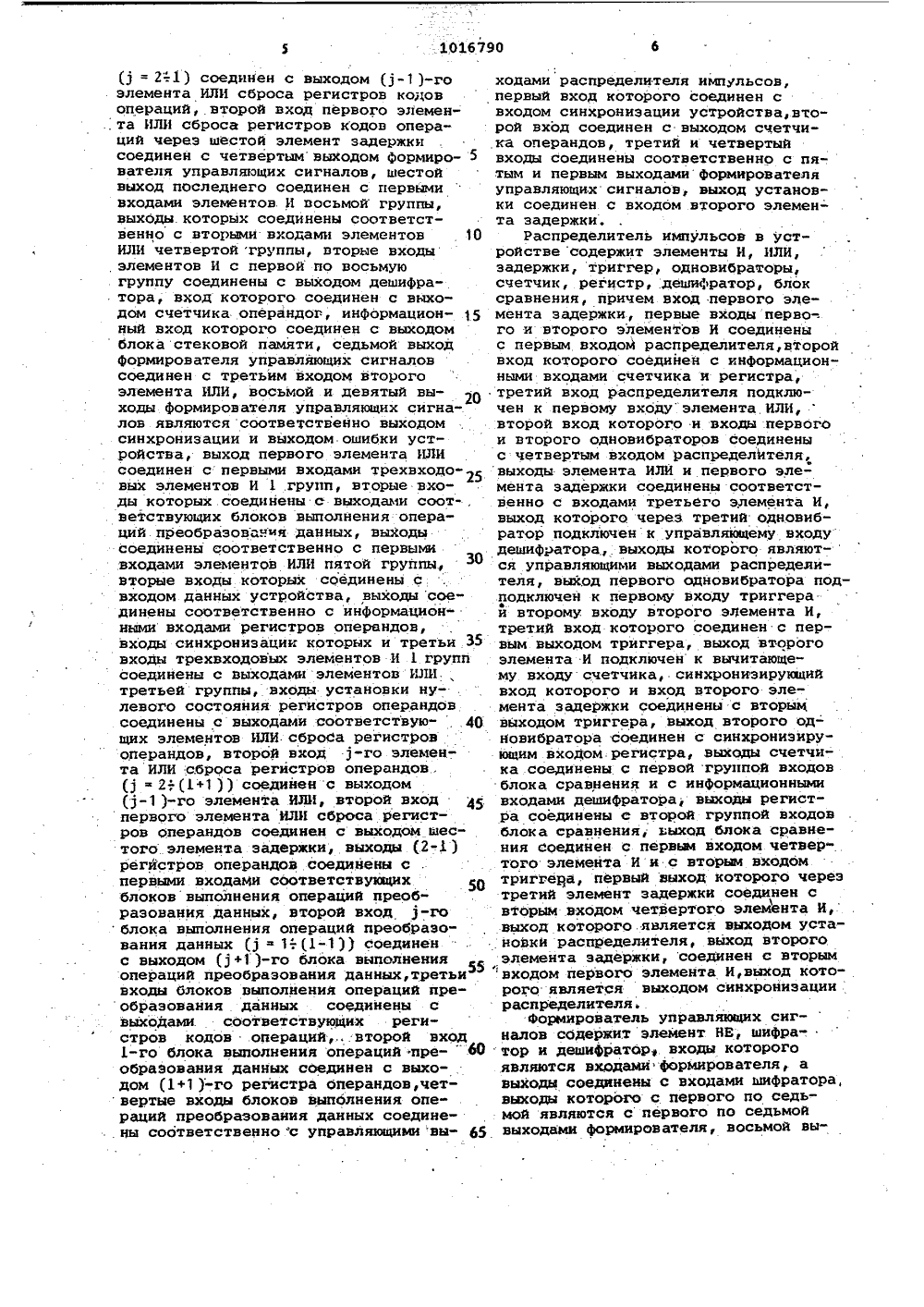

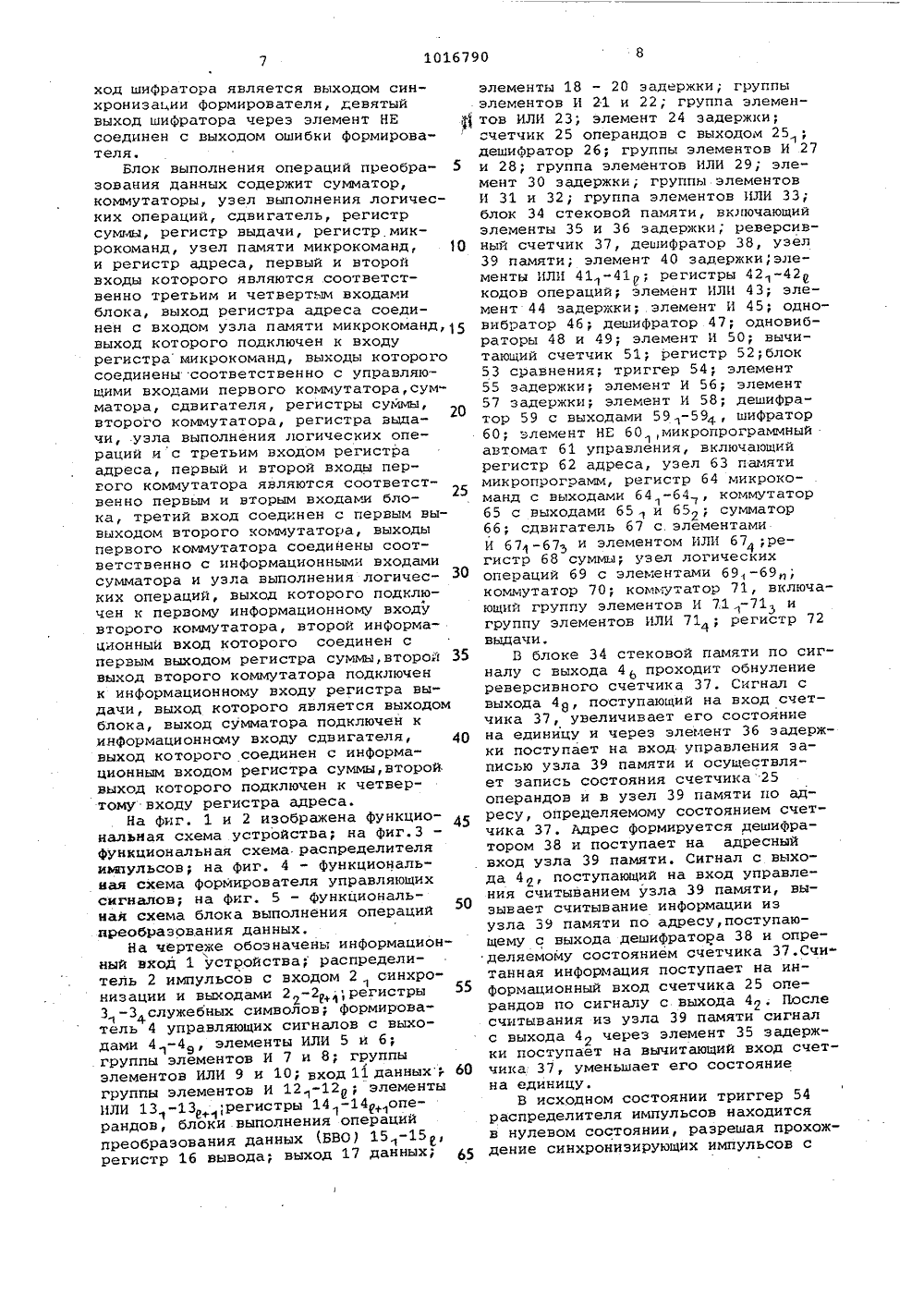

СНИХ ПВ (И) 6 06 ГОСУДАРСТВЕННЫЙ НОМИЧЕТПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ПИСАНИЕ ИЗОБРЕТЕНИЯ В 3 Ж; 1 У СВИДЕТЕЛЬСТВУ АВ 21 ) 33383(72) Б,И, Си М,А, Кур153 ) 681.3С 56) 1. АвВ 583440,2.АвторР 446882,3. АвторМ. 51971, клпрототип ) 83. Бюл. 9 1ергеев, А.П. Посов5,22(088.8 )орское свндетелл, С 06 Г 15/2ское свидетельл, 6 06 Р 15/2ское свидетельС 06 Р 15/04 ре ее ьство СС 1976. тво СССР 1972. тво СССРвходы пермвблов под-жщу уст- регистиеи с ин)-го рес 1-мнищих сигорого союди 1-3 ) ОБРА ОВАН 54 )(57 ) 1 УСТРОЙСТВО ДЛЯ БОТКИВЫРАЖЕНИЙ ЯЗЫКОВ ПРОГРАИИИР ИЯсодержащее первый и второй регистрыоперандов, Формирователь управляющих сигналов, первый выход которогосоединен с входом управления считыванием блока стековой памяти, входомсинхронизации счетчика операндов,счетный вход которого соединен с втсрым выходом формирователя управляющих сигналов, третий выход которогосоединен с входом управления записьюблока стековой памяти, информационный вход которого соединен с выходомсчетчика операндов, вход установкинулевого состояния которого и входсинхронизации регистра вывода,под:,ключены к четвертому выходу.формиро"вателя управляющих сигналов, выходпервого регистра операндов подключенк первому входу первого блока выполиения операций преобразования данных, выход которого соединен с инфор.мационным входом регистра вывода,(Ъ) регистров операндов,регистров кодов операндов, (8-1 ) блоковвыполнения операций преобразованияданных.1+1 ) элементов ИЛИ сброса регистров операндов, ь элементовИЛИ сброса регистров кодов операций,распределитель импульсов и четырегистра служебных символов, входысинхронизации которых соединены свыходом еинхроиизации распределителяимпульсов, информационныевого регистра служебйых сиклвченц к информационномузройства, выход 1-го (1ра служебных символов соедиФормационными входами 3.+1гистра служебных символов ивходом формирователя управлналов, четвертый вход котнен с выходом четвертого регистраслужебных символов, первый выходФормирователя управляющих сигналовчерез первый элемент задержки соединен с первыми входами первого и второго элементов ИЛИ, выаа второгоэлемента задержки соединен с первымивходами элементов И первой н второйгрупп, выходы которых соединенысоответственно с первыми входамиэлементов ИЛИ первой и второй групп,вторые входы элементов ИЛИ первойгруппы соединены с выходами элементов И третьей .группы, а выходы соедииены с первыми входами (1+1) элементов ИЛИ сброса регистров операндов,второй выход Формирователя управляющих сигналов через третий элементзадержки соединен с вторым входомвторого элемента ИЛИ, выход которогосоединен с первыми. входами элементовИ четвертой группы, выходы которыхсоединены соответственно с первымивходами элементов ИЛИ третьейгруппы, вторые входы йоследних соединены соответственно с выходамиэлементов И пятой группы, первыевходы которых, второй вход первогоэлемента ИЛИ и вход четвертого элемента задержки соединены с пятымвыходом Формирователя управляющихсигналов, выход четвертого элемента45 Ст- состояние счетчика операндов25, 1= Ст; Ч 3 - код на выходе блока стековой памяти 34; УЗ 4 - состояние указателя стека; Е - код операции.Соответствие комбинаций управляющих сигналов на выходах 4-4 9 формирователя 4 управляющих символов представлено в табл. 2. С -комбинации, не соответствующие разрешеннымкомбинациям 1,41 Операнды, соответ ствующие служебным символам, заносятся в блок памяти операндов (не показан ).Коды служебных символов из внешней памяти поступают на вход 1 уст ройства.Сигнал синхронизации, поступающий на вход 2 устройства и далее на входы синхронизации регистров 3-34 с выхода распределителя 2, вызывает сдвиг кодов служебных символов в регистрах служебных символов 31-3 в результате чего состояние регйстра 32 перезаписывается в регистр 3, состояние регистРа 3 переписывается в регистр Зз и код служебного символа с входа 1 записывается в регистр 31.На входы Формирователя управляющих сигналов 4 поступает комбинация четырех кодов служебных символов с выходов регистров 3 - 34, При этом на одном из выходов 4 - 4 э Форми рователя 4 управляющих сигналов появляется единичный сигнал.Сигнал с выхода 46 приводит к 35 обнулению счетчиков 25 и 37, приему инФормациирезультатов вычислений предшествуюцей записи ) с выхода блока 151 в регистр 16, а через элемент задержки 40 вызывает обнуление 40 регистров 14 -14 1 операндов и регистров 42 -42 кодов операций (осуществляется подготовка схемы к началу обработки новой элементарной записи ).Сигнал с выхода 4является синхронизирующим сигйалом, по которому внешние схемы Фиксируют прием резуль" тата вычисляемой элементарнои записи.Сигнал с выхода 4 З через элемент ИЛИ б разрешает прохождение сигнала с выхода .деыиФратора 26 через группу элементов И 7, группу элементов ИЛИ 9 на вход синхронизации регистра 14 операндов, вызывая прием операнда с входа 11 данных через группу элементов ИЛИ 10.Сигнал с выхода 4 1 вызывает увеличение состояния счетчика 25 на единицу и, следовательно, изменение кода на выходе дешиФратора 26, далее 60 через элемент 24 задержки, элемент ИЛИ 6 разрешает прохождение сигнала о одного из выходов деыиФратора 26 через группу элементов И 7, группу элементов ИЛИ 9 на вход .синхрониза ции регистра 14 операндов, разреыая прием операнда с входа 11 данных через группу элементов ПЛИ 10.. Сигнал с выхода 4 резрешаст прохождение сигнала с одного из выходов дешиФратора 26 через группу элементов И 32 и группу элементов ИЛИ 33 на вход синхронизации соответствующего регистра 42; кодов операций , вызывая прием кода операции с входа 1.Сигнал с выхода 4 вызывает запись кода состояния с выхода 25 1 счетчика 25 в блок 34 стековой памяти.Под воздействием сигнала 4 распределитель 2 импульсов Формирует сигнал запуска 1-го блока 15 на выполнение операции. Номер блока определяется состоянием счетчика 25 (кодом на выходе 25.,), Прохождение импульсов синхронизации на входы синхронизации регистров 3-3+ не блокируется. Одновременно сигнал с ьыхода 4 через элемент 11 ЛИ 5 поступает на вход групп элементов И 12-12, а также разрешает прохождение сигнала с 1-го выхода деыиФратора 26 через группу элементов И 8, группу элементов ИЛИ 9 на вход группы элементов И 12; вход синхронизации регистра 14; операндов это достигается монтажным сдвигом выходных сигналов деыиФратора 26 на один разряд при передаче их через группу элементов И 8 на вход группы элементов ИЛИ 9 ), разрешая прохождение кода промежуточного результата с выхода блока 15;,через группу элементов И 12; , группу элементов ИЛИ 10. На йнФормационные входы регистра 14; операндов, далее после выполнения операции, сигнал с выхода 4 через элемент 20 задержки разрешает прохождение сигнала с -го выхода дешиФратора 26 через группу элементов И 21, группу элементов ИЛИ 23, элемент ИЛИ 13 на вход установки в "0" регистра 14 операндов, и далее распределение его через элементы ИЛИ 13 -13,на асинхронные входы уста 11новки в фО" регистров 14 -14 Доперан 1+ +т дов осуществляется выборочное обнуление регистров 14;,-14+операндов ), а также данный сигйал разрешает про" хождение сигнала с 1-го выхода деииФ- ратора 26 через группы элементов И 28, элементов ИЛИ 29, через элемент ИЛИ 41; это достигается монтажным сдвигом подобно описанному выше) на вход установки в "0" регистра 42; 1 кодов операций и далее распространение его через соответствуюцие элементы ИЛИ 41;"41 р на входы установки в "Оф регистров 42;-42 кодов операций (осуществляется выборочное обнуление регистров кодов операций 42; 1-42) , далее сигнал с выхода 4 через элемент 30 задерж 1ки разрешает прохождение сигнала с1-го выхода дешифратора 26 через группы элементов И 31, элементов ИЛИ 33 на вход синхрЬнизации регистра 42; кодов операций (это дос тигается монтажным сдвигом сигнала с 1-го выхода дешифратора 26 на один 5 разряд при прохождении через группу элементов И 31 на вход группы элементов ИЛИ 33), вызывая установку в регистре 42 кодов операций кода операции с входа 1 устройства.10Поступая на вход распределителя импульсов, сигнал 42 блокирует прием служебных символов и вызывает формирование серии последовательных сигналов, поочередно запускающих 15 блоки 15 , где- код, считываемый по этому сигналу с блока 34 стековой памяти в счетчик 25, После выдачи этих импульсов на выходе распределителя.импульсов. формируется сигнал и разрешается прохождение .последующих илаульсов с входа 2 на выход синхронизации.Одновременно сигнал с выхода 4 вызывает считывание кода из вершины блока 34 стековой памяти и занесение его в счетчик 25 операндов, далее через элемент 13 задержки, элемент ИЛИ 6 разрешает прохождение сигнала с выхода дешифратора 26 через группы элемейтов И 7,. элементов ИЛИ 9 на30 вход синхронизации регистра 14; операндов и одновременно на вход группы элементов И 12-12, разрешая прохождение кода йромежуточного результата с выхода блока 15;,через группыЗ 5 элементов И 12 и элементов ИЛИ 10 , на информационные входы регистра 14 операндов. Далее (после завершения операций и записи результата ) сигнал с выхода распределителя импуль сов через элемент 19 задержки разрешает прохождение сигнала с 1-го выхода дешифратора 26 через группы элементов И 22 и элементов ИЛИ 23 через элемент ИЛИ 13; (это достига ется монтажным сдвигом сигнала с 1-го выхода дешифратора 26 на один разряд,при прохождении через группы элементов И 22 на вход группы элементов ИЛИ 23) на вход установки в "0" регистра 14 операндов и да 1+Ялее распространение его через элементы ИЛИ 13 -13 Е+на входы установки в "0" регистров 14. -14 операндов (осуществляется виЪорочное обнуление регистров 14 -14, операндов),55 а также данный сигнал разрешает прохождение сигнала с 1-го выхода дешифратора 26 через группы элементов И 27 и элементов ИЛИ 29, элемент ИЛИ 41 на вход установки в "Оф 60 регистра 42; кодов операций и далее распространение его через элементы ИЛИ 41 -41 Е на входы установки в фОф регистров 42 -42 Е кодов операиИций (осуществляется выборочное обну ление регистров 42 -42 кодов опеераций ).Сигнал с выхода 49 является символом семантической ошибки во входном выражении.Работу устройства будем рассматривать по циклам. При этом под циклом будем понимать последовательность действий, выполненных междупоследовательными приемами кодов служебных символов.При приеме кодов служебных сим-волов, вызьваюцих формирование сигна. -лов на выходах 4,4 - 4 9 цикл содер- .жит один такт (длительность тактарассчитана на длительность выполнения самой длинной операции). Еслипринятый служебный символ вызываетФормирование сигнала на выходе 42,под воздействием которого распределитель 2 импульсов блокирует приемкодов служебных символов на времявыполнения операций двумя соседними блоками; то цикл содержит дватакта.Рассмотрим работу устройства наследующем примере,Пусть на вход 1 устройства поступает элементарная записьк.3 +7 кУ)-я +ЯМ +Я -я )кя Л -Я ) хф +Л )Общим в процессе функционирования является то, что в начале каждого цикла на вход синхронизации регистров служебных символов поступает единичный сигнал с выхода распределите" ля 2 импульсов, а на информационные входы данных регистров поступает код служебногосимвола, в результата чего в регистрах служебных символов осуществляется сдвиг кодов о код нового служебного символа заносится в первый регистр, Далее формирователь управляющих сигйалов Формирует единичный сигнал на одном из своих выходов. При рассмотрении примера будем опускать этот начальный этан каждого цикла и начинать с момента появления единичного сигнала на ойном из выходов формирователя управляющих сигналов.Первый цикл. о сигналу с выхода 4 происходит обнуление счетчика операндов 25, реверсивного счетчика 37 и прием результата вычисления предыдущего выражения в регистр 16 (это значение сохраняется в нем до момента получения результата данного выражения и прихода следующего ); обнуление регистров 14-144 операндов и,. регистров 42 -42 кодов операций.3Второй цикл. Формируется сигнал на выходе 4 , по которому внешними схемами (на фиг. 1 не показаны) фикЮсируется приемник результата вычисляемого выражения.Двадцать пятый цикл, По сигналУс выхода 4 э происходит прием в регистр 14 операндов операнда мз, по" 45 ступившего на вход 11.Двадцать шестой цикл. По сигналус выхода 4. происходит вычислениеи прием в регистр 14 операндов ре"зультата промежуточных вычислений1(1 = о х Л х Т 1 з ); выборочныйсброс в фОф регистров 14 З и 14+ операндов регистров 422 и 423 кодовопераций; прием в регистр 422 кодовопераций кода операции "-ф.Двадцать седьмой цикл. По сигналус выхода 4 происходит прием в реЭгистр 14 З операндов операнда 1 дпоступивйего на вход 11,Двадцать восьмой цикл. По сигналу с выхода 42 происходит запись 60 в счетчик 25 кода нз вершины блока34 стековой памяти, вычисление иприем в регистр 14 2 операндов ре. зультата промежуточных вычисленийР(Р = 1 - Т 10) выборочный сброс в 5 фОф регистров 14и 144, операндов Третий цикл. По сигналу с выхода4 э осуществляется прием в регистр 14операнда л , поступившего на вход 111 фЧетвертый цикл. По сигналу с выхода 4 происходит прием в регистр42 кодов операций кода операции "+".Пятый цикл. По сигналу с выхода4 в производится запись в блок 34стековой памяти кода состояния счетчика 25.Шестой цикл. По сигналу с выхода44 происходит увеличение состояниясчетчика 25 на единицу; прием в ре"гистр 14 2 операндов операнда йпоступившего на вход 11.Седьмой цикл. По сигналу с выхода4 1 происходит прием в регистр 422кодов операций кода операции "х".Восьмой цикл. По сигналу с выхода44 происходит увеличение состояниясчетчика 25 на единицу, прием в регистр 14 операндов операнда 71 З, поступившего на вход 11.Девятый цикл. По сигналу с выхода4 происходит запись в счетчик 25кода иэ вершины блока 34 стековойпамяти; вычисление и прием в регистр14 1 операндов результата промежуточных вычислений ( с. Х, ф 1%хзЬ;после выполнения. укаэанных операцийвыборочный сбросв "О" регистров142-144. операндов, регистров 42-42 Зкодов операций.Десятый цикл. По сигналу с выхода 44 происходит прием в регистр42 1 кодов операций кода операцииОдиннадцатый цикл. По сигналус выхода 44 происходит увеличениесостояния счетчика 25 на единицу;прием в регистр 142 операндов операнда У,Двенадцатый цикл, По сигналу свыхода 4.1 происходит вычисление иприем в регистр 14 операндов результата промежуточных вычисленийЬ(Ь = Ы - л,); выборочный сбросв "О" регистров 142-144 операндов,регистр 42-423 кодов операций;прием в регистр 42 кодов операцийкода операцииТринадцатый цикл. По сигналу свыхода 4 8 происходит запись в блок34 стековой памяти кода состояниясчетчика 25.Четырнадцатый и пятнадцатый циклыаналогичны циклу 13,Шестнадцатый цикл. По сигналу свыхода 44 происходит увеличениесостояния счетчика 25 на единицу;прием в регистр 14 З .операндов опе"ранда 71, поступившего на вход 11Семнадцатый цикл. По сигналу свыхода 4 происходит прием в регистр 428 кодов операций кодаоперации "+".Восемнадцатый цикл. По сигналу, с выхода 44 происходит увеличениесчетчика 25 на единицу; прием в ре 5 10 15 20 25 30 35 40 гистр 14 операндов операнда 71поступившего на вход 11,Девятнадцатый цикл. По.сигналус выхода 4происходит вычисление и прием в регистр 14 операн 3дов результата промежуточных вычислений с(с = Г + 3 Т ); выборочныйсброс в "Оф регистра 144 операндов,регистра 42 З кодов операций; приемв регистр 42 зкодов операций кодаоперацииДвадцатый цикл. По сигналу свыхода 4 з происходит прием в регистр14 операндов операнда Л , поступившего на вход 11.Двадцать первый цикл. 11 о сигналус выхода 4 2 происходит запись всчетчик 25 кода иэ вершины блока 34стековой памяти, вычисление и приемв регистр 142 операндов результатапромежуточных вычислений Й(Й = с- Ц);выборочный сброс в "О" регистров 14144, операндов регистров 422,423кодов операций.Двадцать второй цикл. По сигналус выхода 47 происходит прием в регистр 422 кодов операций кода операции "х".Двадцать третий цикл. По сигналус выхода 4+ происходит увеличениесостояния счетчика 25 на единицу;прием в реГистр 143 операндов операнда У 8, поступившего на вход 11 данных.Двадцать четвертый цикл. По сиг"налу с выхода 4 происходит вычисление и прием в регистр 14 операн 2дов результата промежуточных вычислений й хна , прием в регистр 144операндов операнда У ; прием в регистр 422 кодов операций кода операции "х".регистров 42 н 42 кодов опера чнслений у(у=Ь+ь ) исходного выраженияций,2 Эв выходной регистр 16; обнуление реДвадцать девятый цикл. По сигна- гистров 14 -14+ операций, регистровлу с выхода 4 -,. происходит прием в. 42 -42 кодов операций.регистр 42 кодов операций кода опе- Таким образом, предлагаемое устрации фхтр. ройство для обработки языков програмТридцатый цикл. Происходит за- мирования обладает способностью адаппись в блок 34 стековойпамяти кода тации к виду выражений и их пошагосостояния счетчика 25. . вой интерпретации беэ преобраэоваТридцать первый цикл, По сигналуния к виду польской записи, что увес выхода 4+ происходит увеличеиие . 10 .лнчивает скорость обработки,состояния счетчика 25 на единицу Синтаксический анализ каждого симприем в регистр 14 операндов операн- вола выражения с учетом предшествуюда У щих символов требует только одного1 фТридцать второй цикл. Происхо- цикла работы устройства, что способдит прием в регистр 42 З кодов опе ствует повышению скорости .обработкираций кода операции "+". выражений,Тридцать третий цикл, По сигналу Пошаговая интерпретация выраженийс выхода 4 происходит увеличение позволяет в процессе интерпретациисостояния счетчика 25 на единицу проводить выполнение операций и на+прием в регистр 14 операндов опе- ;р копление промежуточных результатовбесскобочных выражений.Тридцать четвертый цикл. По сиг- Структурные отображения скобочналу с выхода 4 .происходит запись ных выражений устройством путем инв счетчик 25 кода из вершины блока дивидуальной последовательностт.и34 стековой памяти, вычисление и . 25 настройки блоков 15 и шин передачиприем в регистр 14 операндов резуль- промежуточных результатов, нарядутатов промежуточных вычислений . . с вычислением подскобочиых выражений,сС = р ( У+; выбороч- . ,позволяет. в одном цикле, соответстный сброс в "0 регистров .14 з и 144.вуюцем закрывающейся скобке выраоперандов регистров 422 и 42 кодов ЗО жения; сворачивать одно -подскобочное выражение, что позывает скоростьоперацийТ идцать пятый цикл. По сигналу обработки скобочных форм ырв ажений.Рс выхода 42 происходит запись в счет- Структурное отображение выражечик 25 кода иэ вершин блока 34 сте- ний (адаптация устройства к видуковой памяти, вычисление и прием в выражения осуществляется установ 14е авда результата про- З пением соответствия между операциямив ажениймежуточных вычных вычислений в данном.слу- и операндами подскобочных выражен1 15 ихчае перезапись промежуточного резуль- . с одной стороны и блокаютата в регистр 14операндов); выбо-. регистрами кодов операций и регистрочный сброс в ф 0" регистров 14 и рами операндов с другой стороны, а14 операндов регистров 42 и 42 40 также между выходами результатов,ф оий. и регистрами операндов (для передачикодов операций.Тридцать шестой цикл. По сигналу и хранения промежуточных реэуэ льтатовс выхода 4 происходят. обнуление . что уменьшает потери времени на высчетчика 25 операндов, реверсивного эов промежуточных результатов, иссчетчика 37 и прием результата вы пользуемых в качестве операндов.1016790 Составитель Л. Хереноведактор А. Фролова 1 ехред С,Мигунова корректор Е. Рошк Зака тент", г. ужгород, ул. Проектная,илиал ПП 387/48 Тираж 706 ВНИИПИ Государственног по делам изобретений 113035, Москва, )."-35, РаПодписноекомитета СССРи открытийшская наб., д. 4/5% задержки соединен с первыми входамиэлементов И третьей и шестой групп,выход четвертого элемента задержкичерез пятый элемент задержки соединен с первыми входами элементов Иседьмой группы, выходы которых соединены соответственно с первыми входами элементов ИЛИ четвертой группы,выходы последних соединены соответ ственно с входами синхронизации регистров" кодов операций, информационные входы которых подключены к информационному входу устройства,входустановки нулевого состояния каждогорегистра. кодов операций соединен свыходом соответствующего элементаИЛИ сброса регистров кодов операций,первый вход которого соединен с выходом элементов ИЛИ второй группы,вторые входы которых соединены соответственно с выходами элементов Ишестой группы, второй вход -го элемента сброса регистров кодов операций (2-1) соединен с выходом( -1)-го. элемента ИЛИ сброса регистров кодов операций, второй вход первого элемента ИЛИ сброса регистровкодов операций через шестой элементзадержки соединен с четвертым выходом Формирователя управляющих сигналов, шестой выход последнего соединен с первыми входами элементов Ивосьмой группы, выходы которых соединены соответственно с вторыми входами элементов ИЛИ четвертой группы, вторые входы элементов И с первой по восьмую групп соединены с выходом дешифратора, вход которого соединен с выходом счетчика операндов, информационный вход которого соединен с выходом блока стековой памяти, седь" мой выход формирователя управляющих сигналов соединен с третьим входом второго элемента ИЛИ, восьмой и девятый выходы Формирователя управляющих сигналов являются соответственно выходом синхронизации и выходом ошибки устройства, выход первого элемента ИЛИ соединен с первыми входами трехвходовых элементов И 1 групп вторые входы которых соединены с выходами соответствующих блоков выполнения операций преобразования данных, выходы соединены соответственно с первыми входами элементов ИЛИ пятой группы, вторые входы которых соединены с входом данных устройст.ва, выходы соединены соответственно с информационными входми,регистров операндов, входы синхронизации.кото- рых и третьи, входы трехвходовых эле ментов И 1 групп соединены с выходами элементов ИЛИ третьей группы, вхо ды установки нулевого состояния регистров операндов соединены а выходами соответствующих элементов ИЛИ сброса регистров операндов, второй вход -го элемента ИЛИ сброса регист-. ров операндов (1= 2-1+1 соединенс выходом (1-1)-го элемента ИЛИ,второй вход первого элемента ИЛИсброса регистров операндов соединенс выходом шестого элемента задержки,выходы (2-1 ) регистров операндовсоединены с первыми входами соответствующих блоков выполнения операцийпреобразования данных, второй вход 1-го блока выполнения операций преобразования данных (1= 1(1-1) соединен с выходом+1 )-го блока выполнения операций преобразования данных,третьи входы блоков выполнения операций преобразования данных соединены с выходами соответствующих регистров кодов операций, второй вход 1-го блока выполнения операций преобразования данных соединен с выходом (1 +1 )-го регистра операндов, четвертые входы блоков выполнения операций преобразования данных соединенысоответственно с управляющими выходами распределителя импульсов, первый вход которого соединен с входом синхронизации устройства, второй вход соединен с выходом счетчика операндов, третий и четвертый входы соединены соответственно с пятым и первым выходами формирователя управляющих сигналов, выход установки соединен с входом второго элемента задержки.2. Устройство по п.1, о т л н ч а ю щ е е с я тем, что распределитель импульсов содержит элементы И, ИЛИ, задержки, триггер, одновибраторы, счетчик, регистр, дешифратор, блок сравнения, причем вход первого элемента задержки, первые входы первого и второго элементов И соединены с первым входом распределителя, второй вход которого соединенс информационными входами счетчика и регистра, третий вход распределителя подключен к первому входу элемента ИЛИ, второй вход которого и входы первого и второго одновибраторов соединены с четвертым входом распределителя, выходы элемента ИЛИ и первого элемента задержки соединены соответственно с входами третьего элемента И,выход которого через третий одиовибратор подключен к управляющему входу дешифратора, выходы которого являются управляющими выходами распределителя, выход первого одновибратора подключен к первому входу триггера и второму входу второгоэлемента И, третий вход которого соединен с первым выходом триггера,выход второго,элемента И подключен квычитающему входу счетчика, синхронизирующий вход которого и вход второго элемента задержки соединены свторым выходом триггера, выход второго одновибратора соединен с синхронизирующим входом регистра, выходы счетчика соединены с первой группой1016790 входов блока сравнения и с информационными входами дешифратора, выходы регистра соединены с второй группой входов блока сравнения, выход блока. сравнения соединен с первым входом четвертого элемента И и с вторым вхЬ" дом триггера, первый выход которого через третий элемент задержки соединен с вторым входом четвертого эле-. мента И, выход которого является выходом установки распределителя, выход второго элемента задержки соединен с вторым входом первого элемента И, выход которого является выходом синхронизации распределителя.3. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что формирователь управляющих сигналов содержит элемент НЕ, шифратор и дешифратор, входы которого являются входами формирователя, а выходы соединены с входами шифратора, выходы которого с первого по седьмой являются с первого по седьмой выходами Формирователя, восьмой выход шифратора является выходом синхронизации формирователя, девятый выход шифратора через элемент НЕ соединен с выходом ошибки формирователя.4. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок выполнения операций преобразования данных содержит сумматор, коммута. - торы, узел выполнения логических операций, сдвигатель, регистр суммы, регистр выдачи, регистр микрокоманд,1Изобретение относится к вычйслительной технике и может бытьиспользовано в быстродействующихоперационных системах обработки инФормации, в частности в системах с. К недостаткам процессора относятая значительнь 1 е затрата времени натрансляцйю: с языков высокрго: уровня,на внутренний язык, пре)вйсвуощую.вычислениям,Известен интерпретатор алгоритмического языка, содержащий регистркодов служебных символов, регистрданньЖ, регистр операций, счетчик,дешифратор, Формирователь управлявузел памяти микрокоманд и регистрадреса, первый и второй входы которого являются соответственно третьими четвертым входами блока, выходрегистра адреса соедин н с входомузла памяти микрокоманд, выход которого подключен к входу регистра микрокоманд, выходы которого соединены.соответственно с управляющими входами первого коммутатора, сумматора,сдвигателя, регистра сумчы, второгокоммутатора, регистра выдачи, узлавыполнения логических операций, стретьим входом регистра адреса, первый я второй "входы первого коммута-.тора Ййжявтсясоответственно первыми вторым входами блока, третий входсоединен с первым выходом второгокоммутатора, выходы первого коммутатора соединены соответственно с информационными входами суюетора иузла выполнения логических операций,выход которого подключен к первомуинформационному входу второго коммутатора, второй информационный вход,которого соединен с первым выходойрегистра суммы, второй выход второго.коммутатора подключенк информационному входу регистра выдачи, выходкоторого является выходом блока, выход сумматора подключен кинформационному входу сдвигателя, выход которого соединен с информационным входом регистра,суммы, второй выход которого подключен к четвертому входу .регистра адреса,2щих символов, арифметико-логический.блок, блок памяти 2.Недостатком указанного интерпретатора является большая сложность 5 процесса .интерпретации, а также низкое быстродействие устройства.Наиболее близким по техническойсущности к предла.гаемому являетсяустройство для обработки выражений 10О языков программирования, содержащеевход кодов служебных символов, входсинхронизации, вход данных, первыйи второй регистры операндов, Формирователь управляющих, сигналов, первый выход которого соединен.с входомуправления считыванием блока стековойпамяти, входом синхронизации счетчика операндов, счетный вход которого.соединей с вторьва.выходом формирователя управляющих сигналов, третий ф выход которого соединен с входомуправления записью блока стековойпамяти, инФормационный вход которогосоединен с выходом счетчика операн5 10 5 0 25 регистра вывода подключены к четвертому выходу формирователя управляющихсигналов, выход первого регистра операндов подключен к первому входу первого блока выпблнения и операЦий преобразования данных, выход которогосоединен с информационным входом регистра вывода, выход которого соединен с выходом устройства, введены элеэлементы задержки, элементы ИЛИ И,дешифратор, (1-1) регистров операндов, 1 регистров кодов операндов, . 60(1-1) блоков выполнения операцийпреобразования данных, (1+1 ) элементов ИЛИ сброса регистров операндов,1 элементов ИЛИ сброса регистровкодов операций, распределитель им дов, вход установки нулевого состояния которого с входом установки нулевого состояния указателя блокастековой памяти и входом синхронизации выходного регистра подключены кчетвертому выходу формирователя управляющих сигналову выход первого регистра операндов подключен к первомувходу арифметико-логического блока,выход которого соединен с информационными входами выходного регистра,выход которого соединен с выходомданных 3.Недостатком известного устройстваявляется низкая скорость обработкиарифметико-логических выражений, поскольку в нем выражения предварительно преобразуются в польскую инверснуюзапись (ПОЛИЗ) и только после этоговычисляются. Система имеет низкуюскорость трансляции программ, таккак основные ее элементы и связи между ними выполнены программно в видеинструкций. Трансляция осуществляется методом ПОЛИЗа, основанного напрямом просмотре формулы исходноготекста программы, вычислений промежуточных результатов, загрузки формулы в стек в инверсном ее представлении с последующей выгрузкой формулы из стека и вычислении результата.По этому методу в стек загружается.что в устройство, содержащее первыйи второй регистры операндов, формирователь управляющих сигналов, первый выход которого соединен с входомуправления считыванием блока стековойпамяти, входом синхронизации счетчика оперантов, счетный вход которогосоединен с вторым выходом формирователя управляющих сигналов, третийвыход которого соединен с входомуправления записью блока стековой 45памяти, информационный вход которогосоединен с выходом счетчика операндов, вход установки нулевого состоя.ния которого и вход синхронизации пульсов и четыре регистра служебныхсимволов, входы синхронизации которых соединены с выходом синхронизации распределителя импульсов, информационные входы первого регистра служебных символов подключены к информационному входу устройства, выход1-го (1 = 1-3 ) регистра служебныхсимволов соединен с информационнымивходами (1+1)-го регистра служебныхсимволов и 1-и входом формирователяуправляющих сигналов, четвертыйвход которого соединен с выходомчетвертого регистра служебных символов, первый выход формирователяуправляющих сигналов через первыйэлемент задержки соединен с первымивходами первого и второго элементовИЛИ, выход второго элемента задержки.соединен с первыми входами элементовИ первой и второй групп, выходы которых соединены соответственно спервыми входами элементов ИЛИ первой и второй групп, вторые входыэлементов ИЛИпервой группы соединены с выходами элементов И третьейгруппы, а.выходы соединены с первымивходами (1+1) элементов ИЛИ сбросарегистров операндов, второй выходформирователя управляющих сигналовчерез третий элемент задержки соединен с вторым входом второго элементаИЛИ, выход которого соединен с первыми входами элементов И четвертойгруппы, выходы которых соединенысоответственно с первыми входами элементов ИЛИ третьей группы, вторыевходи последних соединены соответственно с выходами элементов И пятойгруппы, первые входы которых, второйвход первого элемента ИЛИ и входчетвертого элемента задержки соединены с пятым выходом формирователяуправляющих сигналов, выход четвертого элемента задержки соединен спервыми входами элементов И. третьейи шестой групп, выход четвертого элемента задержки через пятый элементзадержки соединен с первыми входамиэлементов И седьмой группы, выходыкоторых соединены соответственно спервыми входами элементов ИЛИ четвертой группы, выходы последних соединены.соответственно с входами синхронизации .регистров кодов операций,информационные входы которых подключены к информационному входу устройства, вход установки нулевого состояния каждого регистра кодов, операцийсоединен с выходом соответствующегоэлемента ИЛИ сброса регистров кодовопераций, первый вход которого соединен с выходом элементовИЛИ вто-:рой группы, вторые входы ко-торых соединены соответственнос выходами элементов И . шестой группы, второй вход -го элементасброса регистров кодов операций( = 21) соединен с выходом (-1)-го элемента ИЛИ сброса регистров кодов операций,.второй вход первого элемен.; та ИЛИ сброса регистров кодов операций через шестой элемент задержки соединен с четвертым выходом формиро вателя управляющих сигналов, шестой выход последнего соединен с первыми входами элементов И восьмой группы, выходы. которых соединены соответственно с вторыми входами элементов 10 ИЛИ четвертой группы, вторые входы элементов И с первои по восьмую группу соединены с выходом дешифра.тора, вход которого соединен с выходом счетчика операндог, информацион ный вход которого соединен с выходом блока стековой памяти, седьмой выход формирователя управляющих сигналов соединен с третьим входом второго элемента ИЛИ, восьмой и девятый выходы формирователя управляющих сигналов являются соответствейно выходом синхронизации и выходом ошибки устройства, выход первого элемента ИЛИ соединен с первыми входами трехвходовых элементов И 1 .групп, вторые входы которых соединены с. выходами соот-, ветствующих блоков выполнения операций преобразования данных, выходы соединены соответственно с первыьж входами элементов ИЛИ пятой группы, вторые входы которых соединены с входом данных устройства, выходы соединены соответственно с информационными входами регистров операндов, входы синхронизации которых и третьи 35 входы трехвходовых элементов И 1 групп соединены с выходами элементов ИЛИ третьей группы, входы установки нулевого состояния регистров операндов соединены с выходами соответствую щих элементов ИЛИ.сброоа регистров операндов, второй вход -го элемента ИЛИ сброса регистров операндов, Ц2-;(1+1соединен с выходом Ц)-го элемента .ИЛИ, второй вход 45. первого элемента ИЛИ сброса регистров операндов соединен с выходом шестого. элемента задержки, выходи 2-1 ) регйстров операндов соединены с первыми входайи соответствующих блоков выполнения операций преобразования данных, второй вход 1-гоблока выполнения операций преобразования данных Ц 1-:(1-1 соединен с выходом Ц +1 )-го блока выполнения операций преобразования данных, третьи входи блоков выполнения операций преобразования данных соединены с выходами. соответствующих регистров кодов операций, :второй вход 1-го блока выполнения операций пре- " бО образования данных соединен с выходом (1+1 )-го регистра операндов,четвертые входи блоков выполнения операций преобразования данных соедине. ны соответственно с управляющими вы ходами распределителя импульсов,первый вход которого соединен свходом синхронизации устройства,второй вход соединен с выходом счетчика операндов, третий и четвертый входы соединены соответственно с пятым и первым выходами формирователя управляющих сигналов, выход установки соединен с входом второго элемен- та задержки.Распределитель импульсов в устройстве содержит элементы И, ИЛИ, задержки, триггер, одновибраторы, счетчик, регистр, .дешифратор, блок сравнения, причем вход первого элемента задержки, первые входы перво-. го и второго элементов И соединеныс первым входоМ распределителя, второйвход которого соединен с информационными входами счетчика и регистра,третий вход распределителя подключен к первому входу элемента ИЛИ,второй вход которого и входы первогои второго одновнбраторов соединеныс четвертым входом распределителя,выходы элемента ИЛИ и первого элемента задержки соединены соответственно с входами третьего элемента И,выход которого через третий одновибратор подключен к управляющему входудешифратора,. выходы которого являются управляющими выходами распределителя, выход первого одновибратора подподключен к первому входу триггерай второму входу второго эЛемента И, третий вход которого соединен с первым выходом триггера, выход второго элемента И подключен к вычитающему входу счетчика, синхронизируниций вход которого и вход второго элемента задержки соединены с вторым, выходом триггера, выход второго од- новибратора соединен с синхронизирующим входом регистра, выходы счетчика соединены с первой группой входов блока сравнения и с информационными входами дешифратора, выходы регистра соединены с второй группой входов блока сравнения, ьыход блока сравнения соедийен с первым входом четвертого элемента И и с вторым входом триггеца, первый выход которого через третий элемент задержки соединен с вторым входом четвертого элемента И, выход которого является выходом установки распределителя, выход второго элемента задержки, соединен с вторым входом первого элемента И,выход которого является выходом синхронизации раснределителя.Формирователь управляющих сигналов сбдержит элемент НЕ, шифра-. тор и дешифратор входи которого являются входамиФормирователя, а выходи соединены с входами шифратора, выходы которого с первого по седьмой являются с первого по седьмой выходамн формирователя, восьмой вы 101679010 ход шифратора является выходом синхронизации формирователя, девятыйвыход шифратора через элемент НЕсоединен с выходом ошибки формирователя.Блок выполнения операций преобразования данных содержит сумматор,коммутаторы, узел выполнения логических операций, сдвигатель, регистрсуммы, регистр выдачи, регистр микрокоманд, узел памяти микрокоманд,и регистр адреса, первый и второйвходы которого являются соответственно третьим и четвертым входамиблока, выход регистра адреса соединен с входом узла памяти микрокоманд,5выход которого подключен к входурегистрамикрокоманд, выходы которогосоединены соответственно с управляющими входами первого коммутатора,сумматора, сдвигателя, регистры суммы,второго коммутатора, регистра выдачи, узла выполнения логических операций и с третьим входом регистраадреса, первый и второй входы первого коммутатора являются соответственно первым и вторым входами блока, третий вход соединен с первым вывыходом второго коммутатора, выходыпервого коммутатора соединены соответственно с информационными входамисумматора и узла выполнения логичес- ЗОких операций, выход которого подключен к первому информационному входувторого коммутатора, второй информационный вход которого соединен спервым выходом регистра суммы, второй 35выход второго коммутатора подключенк информационному входу регистра выдачи, выход которого является выходомблока, выход сумматора подключен кинформационному входу сдвигателя, 4 Овыход которого соединен с информационным входом регистра суммы, второй. выход которого подключен к четвертому входу регистра адреса.На Фиг. 1 и 2 изображена функцио иалъиая схема устройства; на фиг.З - функциональная схема распределителя иытульсов; на фиг. 4 - функциональная схема формирователя управляющих сигналов, на фиг. 5 - Функциональная схема блока выполнения операций преобразования данных.На чертеже обозначены информационный вход 1 устройства; распределитель 2 импульсов с входом 2синхронизации и выходами 2 -2 ,регистры 55 3 -3 служебных символов; формирователь 4 управляющих сигналов с выходами 4. -4 , элементы ИЛИ 5 и б; группы элементов И 7 и 8; группы элементов ИЛИ 9 и 10; вход 11 данных, 60 группы элементов И 12 -12, элементы ИЛИ 13-13 ;регистры 141-14+операндов, блоки выполнения операций преобразования данных БВО) 15-15, регистр 16 вывода; выход 17 данных; 65 элементы 18 - 20 задержки; группы элементов И 21 и 22; группа элементов ИЛИ 23; элемент 24 задержки; счетчик 25 операндов с выходом 25 дешифратор 26; группы элементов И 27 и 28; группа элементов ИЛИ 29; элемент 30 задержки; группы элементов И 31 и 32; группа элементов ИЛИ 33; блок 34 стековой памяти, включающий элементы 35 и 36 задержки; реверсивный счетчик 37, дешифратор 38, узел 39 памяти; элемент 40 задержки,элементы ИЛИ 41 -41, Регистры 421-42 кодов операцйй; элемент ИЛИ 43; элемент 44 задержки; элемент И 45; одно- вибратор 46; дешифратор 47; одновибраторы 48 и 49; элемент И 50; вычитающий счетчик 51; регистр 52;блок 53 сравнения; триггер 54; элемент 55 задержки; элемент И 56; элемент 57 задержки; элемент И 58; дешифратор 59 с выходами 59 -59, шиФратор 60; элемент НЕ 601,микропрограммный автомат 61 управления, включающий регистр 62 адреса, узел 63 памяти микропрограмм, регистр 64 микрокоманд с выходами 64 -64 , коммутатор 65 с выходами 65й 652, сумматор 66; сдвигатель 67 с. элементами И 67 -67 и элементом ИЛИ 674,регистр 68 суммы; узел логических операций 69 с элементами 69-69,; коммутатор 70; коммутатор 71, включающий группу элементов И 71 -71 и группу элементов ИЛИ 71 ; регистр 72 выдачи.В блоке 34 стековой памяти по сигналу с выхода 4 6 проходит обнуление реверсивного счетчика 37. Сигнал с выхода 48, поступающий на вход счетчика 37, увеличивает его состояние на единицу и через элемент 36 задержки поступает на вход управления записью узла 39 памяти и осуществляет запись состояния счетчика 25 операндов и в узел 39 памяти по адресу, определяемому состоянием счетчика 37. Адрес формируется дешифратором 38 и поступает на адресный вход узла 39 памяти. Сигнал с выхода 4, поступающий на вход управления считыванием узла 39 памяти, вызывает считывание информации из узла 39 памяти по адресу, поступающему с выхода дешифратора 38 и определяемому состоянием счетчика 37.Считанная информация поступает на информационный вход счетчика 25 операндов по сигналу с выхода 42, После считывания из узла 39 памяти сигнал с выхода 42 через элемент 35 задержки поступает на вычитающий вход счетчика 37, уменьшает его состояние на единицу.В исходном состоянии триггер 54 распределителя импульсов находится в нулевом состоянии, разрешая прохождение синхронизирующих импульсов с23 Ю 313 ООС ф 24 Л 33 Х25 333126 Ъ 3 Л27 3 ГИ28 КЯ СГ29 Ю ССС30 . САУЛ31 АССЕ32 ЗКС33.: 3 ЕИ34 3 Ж35 ЛГ 3 2 +у У+3 Т 694 ЕЯ5 У 3б 3337 3 В8 .ООФ У9 0 Ф УУ10 ЮУГл11 ЫЕй12 у)ЯКУ13 ХСС Л Запись Ст встек На шиве 45 "1" ЛСт 3 ст +1; 36 2 К ЗЕ 37 3 УЗЭ 14 СЭюЮВ 15 ГССР ст 3:= Ч 4;ВС, ВвцЯС: =Р 6",= 0В входа 2 на выход через элементИ 56. На входах 4 и 4 нулевые сигналы. В счетчик 51 первписываетсясостояние счетчика 25 по связи 25.Запись этого состояния в регистр 52блокирована. При поступлении сигнала на вход 4 и окончании переходных процессов на выходе элемента И 45.появляется положительный перепад напряжения,по 10 которому одновибратор 46 вырабатывает импульс, разрешающий формирование дешифратором 47 импульса запуска блока, номер которого .(номер выхода дешифратора с единичным. сигналом) 5 определяется .состоянием счетчика 51. Состояние счетчика при этом не меняется.При поступлении сигнала на вход 4 аналогично формируется сигнал наодном и выходов дешифратора.47.Одновременно одновибратор 48 выдает импульс, блокирующий изменение состоя" ния счетчика 51 в текущем такте и устанавливающий в единичное состояние триггер 54. Благодаря задержке 55 синхронизирующий импульс с входа 2 полностью поступает на выход через элемент И 56. Затем элемент 49 выдает импульс после считывания кода и записи его в счетчик 25 ), разрешающий запись кода с входа 25., в регистр 52. В каждом последующемтакте состояние счетчика 51 уменьшается на единицу и формируется им 35 Выполняемые операции ЯС= ВВЕ 0; ВС= ВСЪ О ф 34пульс йа соответствующем выходе дешифратора 47. При совпадении состояний счетчика 51 и регистра 52 на выходе блока 53 сравнения появляется единичный сигнал, устанавливающий триггер 54 в нулевое состояние.Это влечет за собой разрешение поступления последующих синхронизирующих импульсов на выход.После Формирования необходимого числа синхронизирующих импульсов по сигналу 42 единичный сигнал с выхода блока 53 сравнения препятствует формированию этого сигнала в момент поступления кода 42, когда в регистр 52 еще не записано состояние счетчика 25, а триггер 54 уже установлен в единичное состояние, Сигнал с выхода синхронизации распределителя 2 импульсов может быть использовай внешними схемами не рассмотрены) для подготовки очередного кода служебного символа после записи очередного кода в регистр 3.1"оды служебных символов с регистров 3-34 служебных символов посту"- пают йа входы дешифратора 59 формирователя 4, на одном из его выходов 59-59 формируется единичный сигнал (уйитарный код), если комбинация кодов служебных символов ва входе соответствует одной из разрешенных табл. 1). Унитарный код, поступая на вход шифратора 60, вызывает формирование унитарного кода на его выходах 4.,-4.8(табл. 2).таблица 1 Служебные Выполняемке операции .символы,2324,25 0,2 26,2 32,3 8,29,30,34 Запись Ст в ст операций, (сложения, вычитания,умножения, деления и др, ),Для реализации сложных арифметиих операций по интерационнымритмам используется сдвигательосуществляющий передачу кода безга с выхода сумматора 66 черезенты 671 и элемент ИЛИ 67+ нарегистра 68 суммы или передачусо сдвигом вправо через элементыИ 672, ИЛИ 67 или со сдвигом влево через элементы И 67, ИЛИ 674под действием соответствующего управляющего кода с выхода 64.Прием промежуточного кода с выхода сдвигателя 67 в регистр 68 суммы.осуществляется под действием управляющего кода с выхода 64+управляющий код с выхода 64управляет коммутатором 71, который ческ алго 67, сдви элем вход 5 Единичный сигнал на выходе 49,формируется в случае запрещенной .комбинации на входах дещифратора 59,в этом случае на выхбдах 591-594нулевой код).При поступлении единичного сйгнала 2; в блоки 15 осуществляется прием кода операции с соответствующегорегистра 42 кода операции в регистр62 адреса и запуск микропрограммногавтомата 61 управления. Микрокоманды, считываемые.из узла 63 врегистр 64 микрокоманд, имеют семьуправляющих полей. Код на выходе64 управляет подачей операндов ипромежуточных результатов на входысумматора 66 и узла 69 логическихопераций,Код 64тора при р Продолжение табл. 11016790 произвоцит передачу окончательного результата с выхода регйстра суммы или узла 69 логических операций на выход или осуществляет передачу кода промежуточного результата арифметических операций с выхода регист ра 68 суммы на вход коммутатора 65.Управляющий код с выхода 646 управляет коммутатором 70, который осуществляет передачу результата логической операции с выходов эле ментов 69-69 коды операндов поступают на все элементы одновременно ) на коммутатор 71.Код адреса следующий микрокоманды с выхода 64 г поступает на вход регистра 62 адреса и управляет ходом выгголнения Микропрограммы операции.Сигналы переполнения, знака и др., поступающие с регистра 68уммы на вход регистра 62 адр используются для проверки логических условий и ветвлений в микропрограммах.После выполнения микропрограммы операции над заданными операндами результат через коммутатор 71 записывается в регистр 72 и микропрограммный автомат 61 управления переходит в режим ожидания до поступления очередного управляющего сигнала на вход.Основой языка программирования предлагаемого устройства являются элементарные записи; которые в определениях языка Бэкуса записываются следующим образом: 35( ( выражение)Х 1(выражение),где у, - признак приемника результата вычисления выражения;Х - операция из множества выполняемых.Скобки предназначены для измене"ния порядка вычислений (выделенияучастков выражения с более высокимуровнем ),При этом под уровнем выраженияпонимается часть арифметико-логического выражения, заключенная между открывающей и соответствующей ей 55закрывающей скобками одной степенивложенности.Под степенью вложенности понимается число, указывающее количествооткрытых скобок в последовательности открывающих и закрывающих скобок. При нулевой степени вложенностискобки отсутствуют.Обработка очередного уровня можетпрерываться появлением старшего по 65 степени вложенного уровня. При этом результат обработки прерванного и незавершенного уровня запоминается в регистре операндов данного уровня, Обеспечивается коммутация цепей для запоминания промежуточных результатов прерывающего 1,старшего ) уровня на регистры операндов старшего уровня. По завершении обработки высшего уровня осуществляется переход на обработку низшего уровня (прерванного ) с соответствующей перецачей результата вычислений высшего уровня в качестве операнда для .низшего уровня и так далее, пока не закончится обработка всего выражения, что определяется поступлением соответствующих кодов служебных символов.Элементарные записи объединяются в последовательность записей:( записьюСимволуказывает на окончание очередной записи и на начало следующей.В результате анализа данного символа устройство подготавливается к началу Обработки очередного выражения.Например, выражения ч:ахль-си+И); у = а+ь-ск(дй);у =мчал(сна(+) ); 3 будут представлены следующим образом: м)г (И ЛЕ 3)юл) у лХ И ЗЫ иК Щу 7 У,УЕ ЛХ ГЕК),Э 5 8 где У - служебный символ, указывающий данные,Е - операция "+" (сложение ариф 1метическое );Е - операция "-". (вычитание);2Х - операция "хф (умножение3арифметическое );- операция "/ф (деление);операция "ч" (сложение логическое-дизъюнкция)- операция "Лф (умножениеЬлогическое-конъюнкция )- вычитание "6" (сложение по7модулю два - ИСКЛЮЧАЮЩЕЕИЛИ);Х - операция пдф (коньюнкция8с предварительной инверсиейвторого операнда);Записанные подобным образом арифметико-логические выражения кодируются поэначно и вжодятся в блок памяти (не показан ).Разрешенные комбинации служебных символов сведены в табл. 1, где

СмотретьЗаявка

3338385, 22.09.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМЕНИ МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

СЕРГЕЕВ БОРИС ИВАНОВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, КУРНОСОВ МИХАИЛ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 17/22, G06F 9/45

Метки: выражений, программирования, языков

Опубликовано: 07.05.1983

Код ссылки

<a href="https://patents.su/17-1016790-ustrojjstvo-dlya-obrabotki-vyrazhenijj-yazykov-programmirovaniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обработки выражений языков программирования</a>

Предыдущий патент: Устройство для анализа сложных сигналов

Следующий патент: Устройство для определения взаимных корреляционных функций

Случайный патент: Внутренний центратор для сборки и сварки кольцевых швов в среде защитного газа