Устройство для сортировки чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

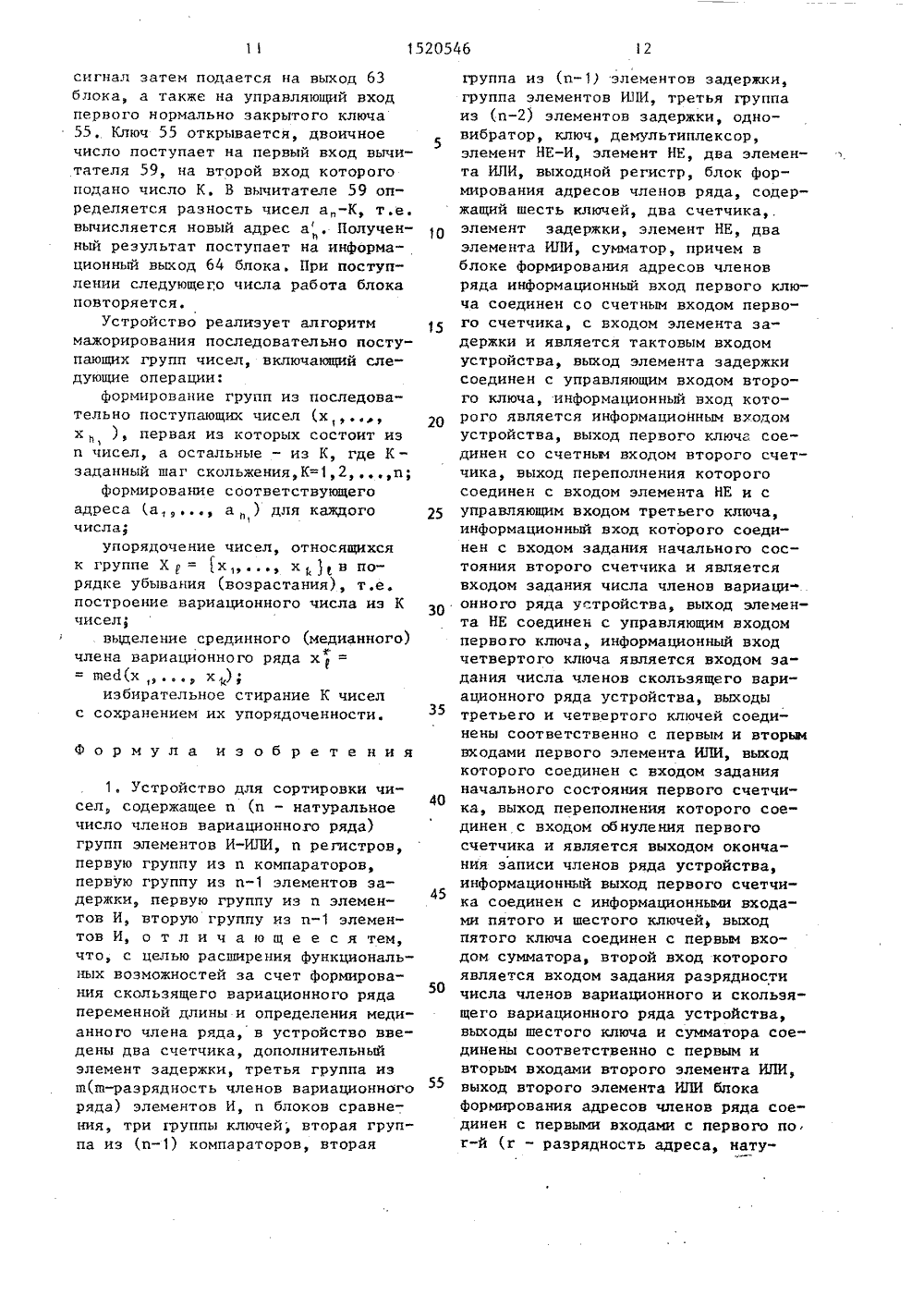

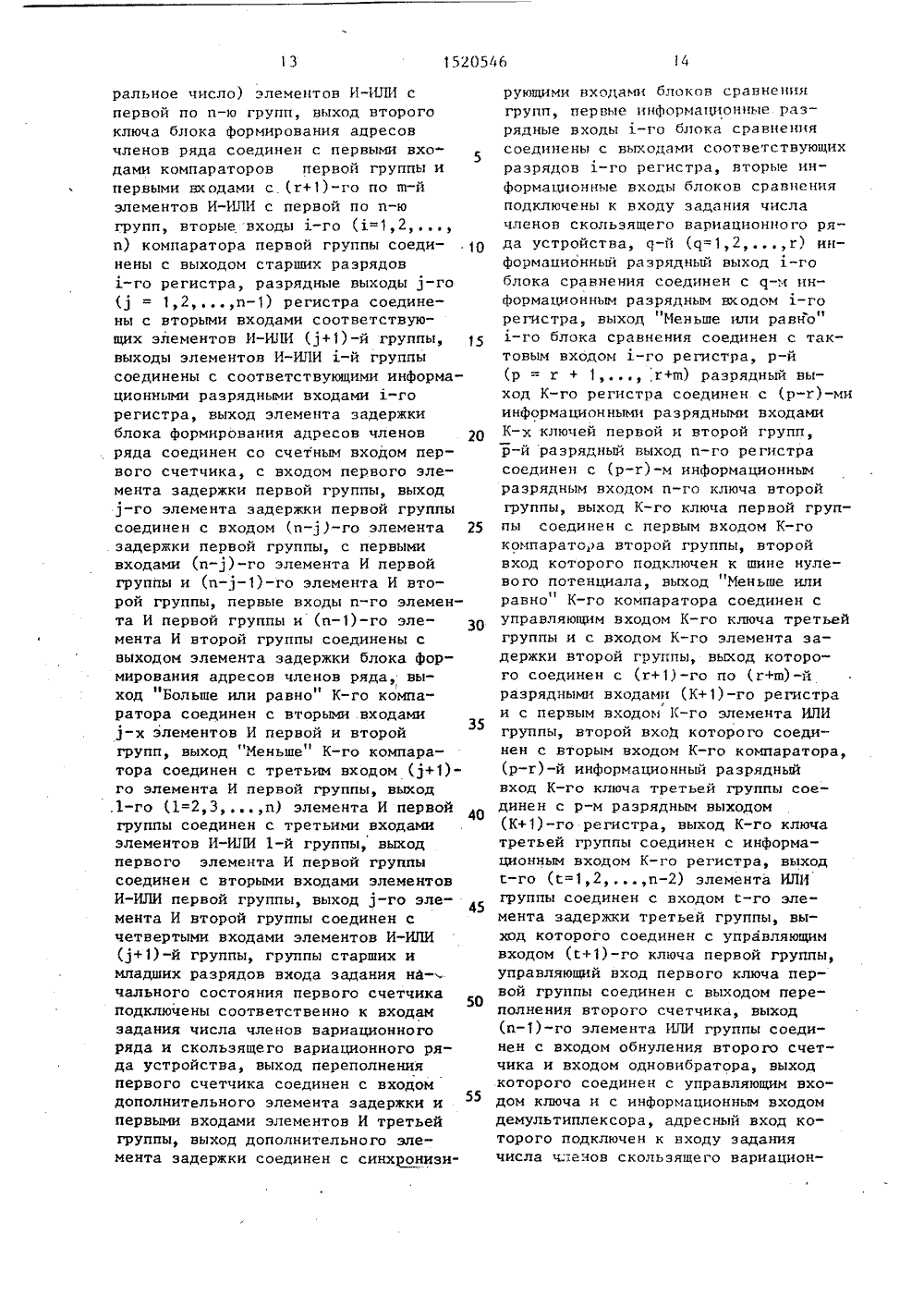

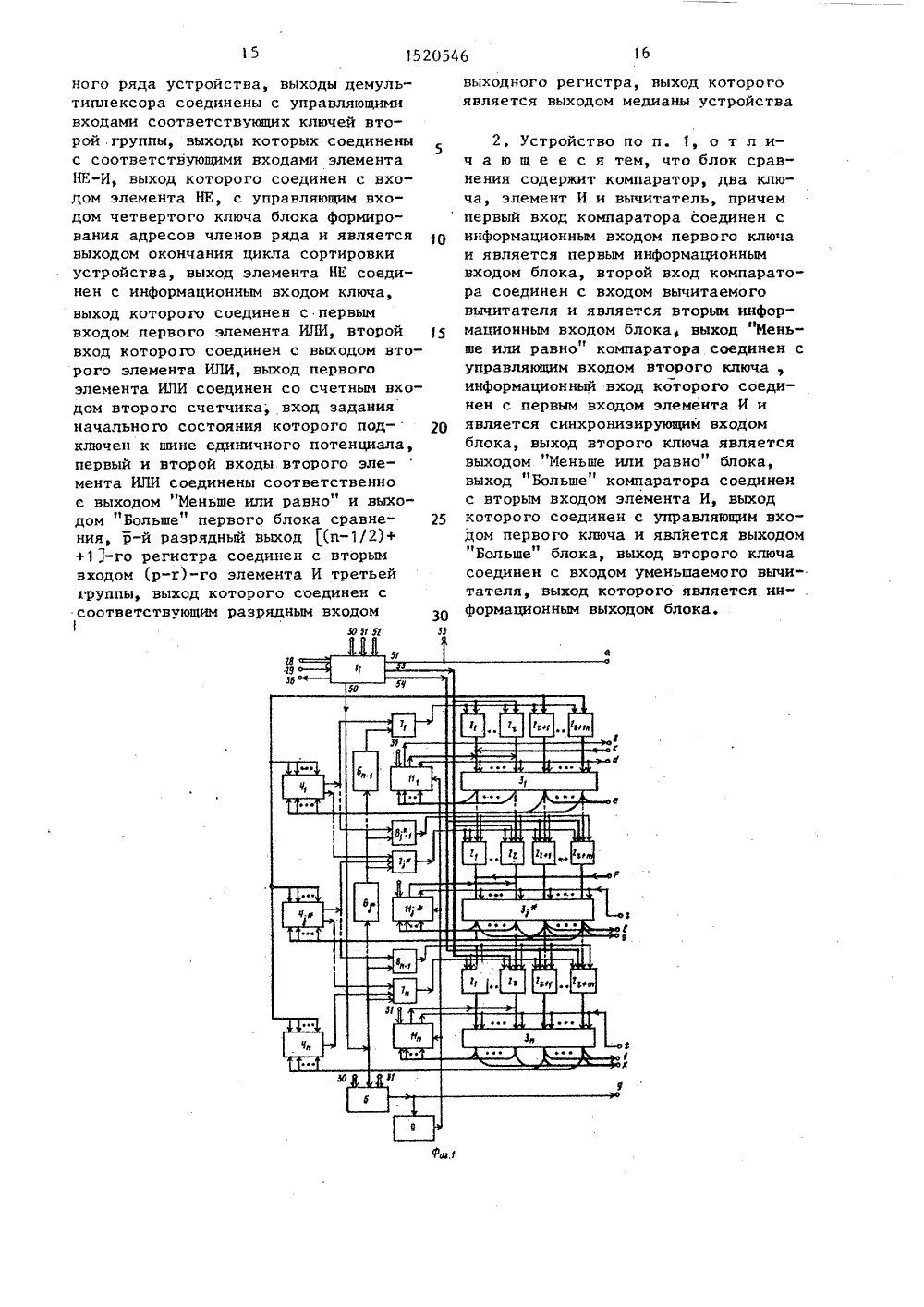

3 сОВетснихЦИАЛИСТИЧЕСН РЕСПУ 6 ЛИН ОПИСАНИЕ ИЗОБРЕТЕНИЯК А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ й инпредставл иг. 3 - с есов член ена схема ема блока устроиства; на фформирования адрна фиг, 4 - схема ряда; авнения.ков ГОСУДАРСТВЕННЫЙ КОМИТЕТпО и 306 Ретениям и ОтнРытиямПРИ ГКНТ СССР(56) Авторское свидетельство СССРУ 1037246, кл. С Об Р 7/06, 1982.54) УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ЧИСЕЛ(57) Изобретение относится к автоматике и вычислительной технике и можетбыть использовано при создании цифровых систем автоматического управления и прогнозирования, Цель изобретения - расширение функциональных.возможностей за счет формированияскользящего вариационного ряда пе- . Изобретеи вычислителбыть испольровых систетоматизировровых систеЦель изофункциональства за счещего вариацидлины и опрна рядаНа фиг ие относится к автомат ьной технике и может овано при создании циф автоматического и авнного управления, цифпередачи данных.ретения - расширение ых возможностей устрой формирования скользяонного ряда переменной деления медианного члеременнои длины и определения медианного члена ряда, Устройство содержитблок формирования адресов членов ряда, группу элементов И-ИЛИ, группурегистров, две группы компараторов,две группы блоков задержки, тригруппы ключей, группу элементов ИЛИ,два счетчика, одновибратор, демультиплексор, выходной регистр, которыеосуществляют формирование скользящих выборок заданного объема с заданным шагом скольжения, обеспечивают помехоустойчивое оцениваниесостояний выходов и входов объектауправления особенно при наличии грубых помех за счет оперативного ма"жорирования цифровых данных в соответствии с алгоритМом скользящей медианы. 1 з.п.ф-лы, 4 ил. ЮУстройство фиг. 1 и 2) содержит (",", блок 1 формирования адресов членов (;Д ря а п групп из ш+г элементов И-ИЛИ 2, и регистров 3, группу из и компараторов 4, счетчик 5, группу из иэлементов 6 задержки, группу из п элементов И 7, группу из иэлементов И 8, элемент 9 задержки, группу из ш элементов И 10, и блоков 11 сравнения, группу ключей 12, группу ключей 13, группу из икомпараторов 14, группу ключей 15, группу иэ иэлементов 16 задержки, иэлемент ИЛИ 17, группу из иэлементов 18 задержки, счетчик 1 9, одновибратор 20, ключ 21, демульти1520546Составитель В. Орлов Редактор В.Петраш Техред Л.Сердюкова Корректор И.Муска Заказ 6760/51 Тираж 668 Подписное ВНИИПИ Государственного комитета по изобретениям и открьгтиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д, 4/5Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 0155 плексор 22, элемент НЕ-И 23, элемент НЕ 24, первый 25 и второй 26 элементы ИЛИ, выходной регистр 27, информационный 28 и тактовый 29 входы, вхоц 30 задания числа членов вариационного ряда, вход 31 задания числа членов скользящего вариационного ряда, шину 32 нулевого потенциала, синхронизирующий выход 33, шину 34 единичного потенциала, информационный выход 35 выход 36 окончания записи членов ряда.Блок 1 (фиг, 3) формирования адресов членов ряда содержит ключ 37, счетчик 38 элемент 39 задержки, ключ 40, счетчик 41, элемент 11 Е 42, ключи 43-46, элемент ИЛИ 47, сумматор 48, элемент ИЛИ 49,тактовый выход 50, управляющий вход 51, вхвд 52 задания разности числа. чпенов вариацианного ряда и скользящего вариационного ряда, первый ионформационный выход 53, второй информационный выход 54.Блок 11 (Фиг. 4) сравнения содер" жит ключ 55, компаратор 56, элемент И 57, ключ 58, вычитатель 59, первый информационный вход 60, синхронизирующий вход 61, выход "Меньше или равно" 62, выход "Больше"63, информационный выход 64.Устройство работает следующим образом.Предварительно на входы 30,31,32 и 34 задаются значения параметров: на вход 30 устройства подается число и, на вход 3 1 - число К; на вход 32 - "0", на вход 34 - "1". В исходном состоянии во всех регистрах 3, а также выходном регистре 27 записаны нули.После пуска устройства двоичные ш"разрядные числа х х х относящиеся к 1-й группе чисел последовательно друг за другом поступают на вхоцную шину 28 устройства. Моменты их поступления синхронизированы с импульсами, подаваемыми на вход 29 устройства. По мере поступления чисел каждому из них в блоке 1 присваивается соответствующий адрес. По первой выходной информационнойшине блока 1 на группы 2,2 элементов И-ИЛИ передается адрес числа, а по второй - на группы 2 2 , само число. При появлении первого числа х, на выходе блока 1 оно передается на первые 10 15 20 25 30 35 40 входы компараторов 4. Поскольку свыходов регистров 3 на вторые входы компараторов 4 поданы нулевые потенциалы, на первых выходах компараторов 4 появляется единичный (разрешающий) потенциал. Одновременно спервым числом х, с тактового выхода блока 1 на счетчик 5, на (и)-йэлемент И 8 и на и-й элемент И 7 поступает управляющий импульсПройдя(и)-й элемент И 8, сигнал поступает на четвертые входы и-й группыэлементов И-ИЛИ 2, осуществляя перезапись из (и)-го регистра в и-йрегистр 3. Перезапись информации из(+1)-й регистр 3 осуществляется аналогично, т,е, подобно работе сдвигового регистра. Элементы 6 задержкислужат для обеспечения устойчивойнадежности работы устройства. Пройдявсе элементы 6 задержки и поступив напервый элемент И 7 , управляющий им"пульс разрешает запись первого числа хи его адреса в первый регистр3. Адрес числа записывается в первыег ячеек регистра 3, а само число -в последние ш ячеек. Счетчик 5 фиксирует первый управляющий импульс.Второе число х(будем считать, например, что х )х,) поступает на вторую выходную шину блока 1 одновременно со своим адресом, поданным напервую выходную шину блока 1. Приэтом на первых выходах компараторов4 появляется единичный сигнал, таккак второе число хбольше чисел,записанных в регистрах 3. Управляющий импульс разрешает перезаписьчисел и их адресов из -го регистрав (.ь+1)-й регистр 3, В результате впервом регистре 3 будет записаночисло хи его адрес, во втором -число х, и его адрес, а во всех остальных - нули. Счетчик 5 фиксируетдва управляющих импульса,При поступлении третьего числа х з(пусть х з = х) на первых выходахкомпараторов 4 также появляется единичный сигнал, так как очередноечисло не меньше чисел, записанныхв регистрах 3. Третий управляющийимпульс осуществляет перезапись информации иэ д-го регистра в (+1)-йрегистр 3. В первый регистр 3 записывается адрес и само число х , Если четвертое число х 1 х х (х =хто на вторых выходах первого и второго компараторов 4 и на первых выходах остальных компараторов 4 появляется единичный сигнал, открывающий третий элемент И 7 и все элементы И 8, кро 5 ме первых двух. Четвертый управляющий импульс переписывает информацию из 1-го регистра 3 в (1+1)-й регистр 3 Ц = 3,4п), а в третий регистр 3 записывается число х и его адрес, В результате в первом регистре будет записано максимальное число, т,е. хс адресом, во втором регистре - равное ему число х и его адрес, в третьем - хд и его адрес, в 15 четвертом - х, и его адрес, а во всех остальных - нули. Далее до заполнения всех регистров 3 устройство работает аналогично, записывая поступающие числа в регистры 3 в порядке 20 убывания.После того, как и двоичных чисел прошли через блок 1, на выходе 36 устройства появляется сигнал. По этому сигналу поступление чисел и 25 синхроимпульсов прекращается до появления сигнала на выходе 33 устройства. Одновременно с поступлением числа хр на выходе счетчика 5 появляется единичный сигнал, который по ступает на первые входы элементов И 10 и на вход элемента 9 задержки. Ба вторые входы элементов И 10 подано медианное число х=тей(хх ,3.х ) из регистра 3 , где 1 = -- +1 - 35и е 2 срединный регистр. При поступлении сигнала от счетчика 5 медианное число запоминается выходнь 1 м регистром 27 и передается на выход 35 устрой О ства. В элементе 9 задержки сигнал задерживается, на время, необходимое для записи медианы х в регистре 27 и поступает на синхронизирующие входы блоков 11. Из первых 2 ячеек ре гистра 3 на первый информационный вход блока 11 подается двоичное число, представляющее собой адрес чис ла, хранящегося в регистре 3. Если адрес числа меньше либо равен заданному шагу скольжения К, то из блока 11 на вход регистра 3 подается импульс сброса, обнуляющий г+ш ячеек регистра, т.е. стирающий число и его адрес, В случае, если адрес числа больше заданного числа К, адрес изменяется и новое его значение поступает в первые г ячеек регистра 3, Управляющий импульс, поступивший с выхода первого блока 11 на элементИЛИ 26, подается далее на элементИЛИ 25. С элемента ИЛИ 25 сигналпоступает на счетный вход счетчика19 с предварительно установленнойна его входе 34 единицей,Счетчик 19 фиксирует первый импульс и формирует на своем выходеединичный сигнал, который подаетсяна нормально закрытый ключ 12, Припоступлении этого сигнала ключ 12открывается и пропускает двоичноечисло иэ последних ш ячеек первогорегистра 31 в компаратор 14. Еслидвоичное число х не равно нулю, сигнал с второго выхода компаратора 14подается на второй вход элементаИЛИ 17, В противном случае (х = 0)с первого выхода компаратора 14,сигнал поступает на нормально закрытый ключ 15 и элемент 16, задержки,Нормально закрытый ключ 15открывается и пропускает двоичное числои его адрес из ячеек второго регист"ра 3 в ячейки первого регистра 3,Элемент 16 задержки задерживает сигнал на время, необходимое для перезаписи числа из (1+1)-го в х-й регистр 3(=1,2и) и подает его напервый вход элемента ИЛИ 17,.и наобнуляющий вход (+1)-го регистра 3.Сигнал поступивший либо на первый,либо на второй вход элемента ИЛИ 17поступает на вход элемента 18, задержки. Задержанный на время обнуления регистра 3 сигнал пропускается на второй нормально закрытый ключ12 и открывает его, Из последних аячеек регистра 3число поступаетна компаратор 14. Если это числоравно нулю, то по сигналу с первоговыхода компаратора 14 на нормальнозакрытый ключ 15 осуществляется перезапись числа из третьего во второйрегистр 3. Этот сигнал задерживаетсяв элементе 16 задержки и обнуляеттретий регистр 3, а также передаетсяна первый вход элемента ИЛИ 17 , Если число, поступившее на компаратор14 не равно нулю, то сигнал с второго выхода компаратора 14поступает на второй вход элемента ИЛИ 17.С элемента ИЛИ 171 сигнал задерживается в элементе 18задержки и подается на следующий нормально закрытыйключ 12. Далее до срабатывания5 1 О 15 20 25 30 35 40 45 50 55 разом осуществляется перезапись чисел из нижних регистров в верхние,После срабатывания (и)-го элемента ИЛИ 17, сигнал с его выходаподается на вход одновибратора 20 ина вход обнуления счетчика 19, Поэтому сигналу счетчик 19 обнуляется.Единичный сигнал с одновибратора 20распределяется демультиплексором 22по нескольким адресам, т.е. подаютсясигналы на управляющие входы К последних нормально закрытых ключей13, Ключи 13 , 13 13открываются, и числа из последних Крегистров 3 поступают на элементНЕ-И 23. Если не все числа равны нулю, то на выходе элемента НЕ-И 23имеется нуль, который подается наэлемент НЕ 24, и преобразуется в единичный сигнал, который, в свою очередь, поступает на информационныйвход нормально закрытого ключа 21,Ключ 2 1 открывается управляющим сигналом с одновибратора 20. Единичный сигнал с выхода ключа поступаетна элемент ИЛИ 25, который срабатывает, пропуская единичный сигнал насчетчик 19. Счетчик 19 фиксируетэтот сигнал и открывает первый нормально закрытый ключ 12. Устройствоснова начинает переписывать числа из1+1)-х в х-е регистры 3, Это повто"ряется до тех пор, пока не обнулятсяпоследние Х регистров 3. В этом случае на выходе элемента НЕ-И 23 появляется единичный сигнал, которыйподается на вход элемента НЕ 24, науправляющий вход блока 1 и выход 33устройства. При поступлении единичного сигнала на вход НЕ 24 на его выходе появляется нуль и ключ 2 1 закрывается, Сигнал, поступивший на выход33 устройства, разрешает подачу тактовых импульсов и К двоичных чисел1 х +.,хна входы 28 и 29устройства до появления сигнала навыходе 36 устройства. Рабочий циклустройства повторяется вновь. Такимобразом, оно срабатывает последовательно поступающие на его вход выборки чисел,Блох 1 формирования адресов членовряда работает следующим образом.Перед началом работы на вход 30устройства предварительно устанавливается двоичное число и, на вход 31устройства - двоичное число К, навход 52 блока - двоичное число, равное и-К, После включения устройства на его информационный вход 28 последовательно подаются двоичные числа 1 хьх,3 ЕОдновременно на вход 29 устройства поступают управляющие импульсы. Управляющий импульс с входа 29 устройства подается на информационный вход первого нормально открытого ключа 37, на счетный вход первого счетчика 38 и на вход элемента 39 задержки, где импульс за" держивается на время срабатывания блоков 41,42 и 47 - 49, т.е, на время формирования адреса поступившего двоичного числа. Ключ 37 пропускает импульс,и второй счетчик 4 1 фиксирует его. Ключ 43 открыт, и двоичное число и с информационного входа ключа 43, соединенного с входом 30 устройства, подается на первый вход первого элемента ИЛИ 47. Элемент ИЛИ 47 срабатывает и передает число п на установочный вход первого счетчика 38.1При поступлении первого импульсапервый счетчик 38 фиксирует его ивыдает соответствующее число на свойинформационный выход. Ключи 44 и 45закрыты, Число с выхода первого счетчика 38 проходит через открытый ключ4 б и подается на вход второго элемента ИЛИ 49. Элемент ИЛИ 49 срабатывает и выдает на первый информационный выход 53 блока адрес "1" числах . Одновременно ключ 40 открывается импульсом из элемента 39 задержки, и число х, выдается на второй инФормационный выход 54 блока. Затем навыход 29 устройства подается второй импульс, а на вход 28 - второе двоичное число х . Ключи 37 и 43 открыты.Счетчики 4 1 и 38 Фиксируют второйимпульс. На информационом выходесчетчика 38 появляется число "2",которое через открытый ключ 4 б,поступает на вход элемента ИЛИ 49. Элемент ИЛИ 49 срабатывает, и на выходе53 блока появляется адрес "2"числа.Второй импульс из элемента задержкипоступает на управляющий вход первого нормально закрытого ключа 40,открывает его и на втором информационном выходе 54 блока одновременнос адресом появляется число х . Припоявлении следующего импульса и следующего двоичного числа работа блокаповторяется до и-го импульса,ч 15В конце рабочего цикла на вход 28 устройства поступает двоичное число х, а на вход 29 -й импульс, который подается на счетньп вход счетчика 38, на вход блока 39 задержки и через открытый ключ 40 на счетный вход счетчика 41, Счетчик 41 фиксирует и-й импульс, и на его выходе переполнения появляется управляющий импульс. Второй нормально открытый ключ 43 закрывается, срабатывает элемент НЕ 42, сигнал с которого закрывает первый нормально открытый ключ 37. Счетчик 38 фиксирует и-й импульс, на его выходе переполнения появляется единичный сигнал, который подается на управляющий выход 36 устройства и обнуляет счетчик 38, Поступление двоичных чисел х и импульсов по этому сигналу прекращается.На информационном выходе счетчика 38 одновременно с управляющим сигналом появляется число, которое через открытый ключ 46 подается на первый вход элемента ИЛИ 49. Элемент ИЛИ 49 срабатывает. На первом информационном выходе 53 блока появляется адрес "и" числа, а на втором информационном выходе 54 блока - само число х После этого блок 1 прекращает работу до появления единичного сигнала на входе 51 блока. По этому сигналу начинается поступление двоичных чисел х х ,и уп.равляющих импульсов в устройство.При появлении сигнала на входе 51 блока открываются нормальнозакрытые ключи 44 и 45, нормально открытый ключ 46 закрывается, Ключи 37 и 43 в это время закрыты. Через .открытый ключ 45 двоичное число К поступает на второй вход элемента ИЛИ 47, который срабатывает и пропускает число на установочный вход счетчика 38. Счетчик 38 фиксирует первый импульс, поступивший с входа 29 устройства, и передает число "1" на свой информационный выход, Число "1" через открытый ключ 44 поступает на первый вход сумматора 48, где складывается с числом и-К, поданным на второй вход сумматора. Полученная сумма (п-К)+1 представляет собой адрес поступившего на вход 28 устройства (и+1)-го числа х , . Первый импульс из блока 39 задержки подается на управляющий вход первого нормально закрытого клю 20546ча 40, открывает его, и число хпередается на выход 54 бпока. Одновременно срабатывает элемент И 1 И 49,на второй вход которого подано число5из сумматора 48. На первьп информационный выход 53 блока выдается адрес числа. При поступлении второгоимпульса срабатывают элементы 38,ч 4,10 48 и 49, формируется адрес следующего числа, Задержанный в блоке 39 задержки импульс вновь открывает ключ40 и на выходе 54 блока появляетсядвоичное число х . При этом рабочий15 цикл блока повторяется.При поступлении К-го импульса науправляющем выходе счетчика 38 появляется сигнал, который обнуляет счетчик 38 и передается на выход 36 уст 20 ройатва, таким образом останавливается поступление двоичных чисел иимпульсов. На информационном выходесчетчика 38 одновременно с управляющим сигналом появляется число К, Че 25 рез открытый ключ 44 оно поступаетна первый вход сумматора ч 8. Результат суммирования (и-К)+К подаетсяна второй вход элемента ИЛИ 49 и далее передается на выход53 блока.Одновременно импуЛьсом из блока 39задержки открывается ключ 40 и навыходе 54 блока появляется двоичноечисло х, . На этом работа блока;прекращается до поступления очеред 35ного сигнала с управляющего входа 51блока,Блок 11 работает следующим образом. Перед началом работы на выходе 31 устройства устанавливаетсядвоичное число К. После пуска устройства адрес ачисла поступает на информационный вход 60 блока. Однорвеменно на синхронизирующий вход 61подается управляющий импульс, кото 4, рый поступает на вторые входы нор 4малько закрытого ключа 58 и элементаИ 57. Адрес ас входа 60 блока поступает на информационный вход нормально закрытого ключа 55 и на первый вход компаратора 56, где оносравнивается с числом К. Если аК,то сигнал с выхода компаратора 56открывает ключ 58 и управляющий импульс подается на выход 62 блока,Этот импульс является сигналом обнуления соответствующего регистра 3.В случае, если а 7 К, то сигнал с вы-хода компаратора 56 поступает наэлемент И 57, который срабатывает, исигнал затем подается на выход 63 блока, а также на управляющий вход первого нормально закрытого ключа 55, Ключ 55 открывается, двоичное число поступает на первый вход вычитателя 59, на второй вход которого подано число К. В вычитателе 59 определяется разность чисел а-К, т.е. вычисляется новый адрес а . Полученный результат поступает на информационный выход 64 блока. При поступлении следующего числа работа блока повторяется.Устройство реализует алгоритм мажорирования последовательно поступающих групп чисел, включающий следующие операции:формирование групп из последовательно поступающих чисел (хр аарон х), первая из которых состоит из и чисел, а остальные - из К, где К - заданный шаг скольжения,К=1,2 п;формирование соответствующего адреса (а, а) для каждогочисла;упорядочение чисел, относящихся к группе Х= х х аа) в порядке убывания (возрастания), т,е. построение вариационного числа из К чисел;выделение срединного (медианного) члена вариационного ряда х=А"= щей(х , х);избирательное стирание К чисел с сохранением их упорядоченности,Формула изобретения1. Устройство для сортировки чисел, содержащее и (п - натуральное число членов вариационного ряда) групп элементов И-ИЛИ, и регистров, первую группу из и компараторов, первую группу из иэлементов задержки, первую группу из и элементов И, вторую группу из пэлементов И, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет формирования скользящего вариационного ряда переменной длины и определения медианного члена ряда, в устройство введены два счетчика, дополнительный элемент задержки, третья группа из ш(ш-разрядность членов вариационного ряда) элементов И, п блоков сравнения, три группы ключей; вторая группа из (и) компараторов, вторая группа из (и) элементов задержки,группа элементов ИЛИ, третья группаиз (п) элементов задержки, одновибратор, ключ, демультиплексор,элемент НЕ-И, элемент НЕ, два элемента ИЛИ, выходной регистр, блок формирования адресов членов ряда, содержащий шесть ключей, два счетчика,.элемент задержки, элемент НЕ, дваэлемента ИЛИ, сумматор, причем вблоке формирования адресов членовряда информационный вход первого ключа соединен со счетным входом первого счетчика, с входом элемента задержки и является тактовым входомустройства, выход элемента задержкисоединен с управляющим входом второго ключа, информационный вход которого является информационным входомустройства, выход первого ключа соединен со счетным входом второго счетчика, выход переполнения которогосоединен с входом элемента НЕ и суправляющим входом третьего ключа,информационный вход которого соединен с входом задания начального состояния второго счетчика и являетсявходом задания числа членов вариационного ряда устройства, выход элемента НЕ соединен с управляющим входомпервого ключа, информационный входчетвертого ключа является входом задания числа членов скользящего вариационного ряда устройства, выходытретьего и четвертого ключей соединены соответственно с первым и вторымвходами первого элемента ИЛИ, выходкоторого соединен с входом заданияначального состояния первого счетчика, выход переполнения которого соединен с входом обнуления первогосчетчика и является выходом окончания записи членов ряда устройства,информационный выход первого счетчика соединен с информационными входами пятого и шестого ключей, выходпятого ключа соединен с первым входом сумматора, второй вход которогоявляется входом задания разрядностичисла членов вариационного и скользящего вариационного ряда устройства,выходы шестого ключа и сумматора соединены соответственно с первым ивторым входами второго элемента ИЛИ,выход второго элемента ИЛИ блокаформирования адресов членов ряда соединен с первыми входами с первого пог-й (г - разрядность адреса, натуральное число) элементов И-ИЛИ с первой ло п-ю грулл, выход второго ключа блока формирования адресов членов ряда соединен с первыми вхо дами компараторов первой группы и первыми входами с.(г+1)-го по пг-й элементов И-ИЛИ с первой ло и-ю групп, вторые входы ь-го (=1,2 и) комларатора первой группы соединены с выходом старших разрядов -го регистра, разрядные выходы )-го (1 = 1,2п) регистра соединены с вторыми входами соответствующих элементов И-ИЛИ (+1)-й группы, 15 выходы элементов И-ИЛИ -й группы соединены с соответствующими информационными разрядными входами -го регистра, выход элемента задержки блока формирования адресов членов 20 ряда соединен со счетным входом первого счетчика, с входом первого элемента задержки первой группы, выход -го элемента задержки первой группы соединен с входом (и)-го элемента 25 задержки первой группы, с первыми входами (и- -го элемента И первой группы и (и-)-1)-го элемента И второй группы, первые входы п-го элемента И первой группы и (п)-го эле- З 0 мента И второй группы соединены с выходом элемента задержки блока формирования адресов членов ряда, вы 11 иход Больше или равно К-го компаратора соединен с вторыми входами 3-х элементов И первой и второй35 групп, выход "Меньше" К-го компаратора соединен с третьим входом (+1)- го элемента И первой группы, выход .1-го (1=2,3,..,и) элемента И первой 40 группы соединен с третьими входами элементов И-ИЛИ 1-й группы, выход первого элемента И первой группы соединен с вторыми входами элементов И-ИЛИ первой группы, выход )-го эле 45 мента И второй группы соединен с четвертыми входами элементов И-ИЛИ Я+ 1)-й группы, группы старших и младших разрядов входа задания на чального состояния первого счетчика50 подключены соответственно к входам задания числа членов вариационного ряда и скользящего вариационнога ряда устройства, выход переполнения первого счетчика соединен с входом дополнительного элемента задержки и первыми входами элементов И третьей группы, выход дополнительного элемента задержки соединен с синхронизирующими входами блоков сравнениягрупп, первые инфорггационные разрядные входы г. - го блока сравнениясоединены с выходами соответствующихразрядов г.-го регистра, вторые информационные входы блоков сравненияподключены к входу задания числачленов скользящего вариационного ряда устройства, с-й (ц= 1,2 .,г) информационный разрядный выход т-гоблока сравнения соединен с ц-и информационным разрядным входом г.-горегистра, выход "Меньше или равно"д-го блока сравнения соединен с тактовым входом г.-го регистра, р-й(р = г + 1 г+тп) разрядный выход К-го регистра соединен с (р-г)-миинформационными разрядными входамиК-х ключей первой и второй групп,р-й разрядный выход и-го регистрасоединен с (р-г)-м информационнымразрядным входом и-го ключа второйгруппы, выход К-го ключа первой группы соединен с первым входом К-гокомпаратаа второй группы, второйвход которого подключен к шине нулевого потенциала, выход "Меньше илиравно" К-го компаратора соединен суправляющим входом К-го ключа третьейгруппы и с входом К-го элемента задержки второй группы, выход которого соединен с (г+1)-го по (г+ш)-йразрядными входами (К+1)-го регистраи с первым входом К-го элемента ИЛИгруппы, второй вход которого соединен с вторым входом К-го компаратора,(р-г) -й информационный разрядныйвход К-го ключа третьей группы соединен с р-м разрядным выходом(К+1)-го регистра, выход К-го ключатретьей группы соединен с информационным входом К-го регистра, выходс-го (с=1,2п) элемента ИЛИгруппы соединен с входом Е-го элемента задержки третьей группы, выход которого соединен с управляющимвходом (с+1)-го ключа первой группы,управляющий вход первого ключа первой группы соединен с выходом переполнения второго счетчика, выход(и)-го элемента ИЛИ группы соединен с входом обнуления второю счетчика и входом одновибратора, выходкоторого соединен с управляющим входом ключа и с информационным входомдемультиплексора, адресньгй вход которого подключен к входу заданиячисла членов скользящего вариацион 151 Ь1520546ного ряда устройства, выходы демультиплексора соединены с управляющими входами соответствующих ключей второй группы, выходы которых соединены с соответствующими входами элемента НЕ-И, выход которого соединен с входом элемента НЕ, с управляющим входом четвертого ключа блока формирования адресов членов ряда и является выходом окончания цикла сортировки устройства, выход элемента НЕ соединен с информационным входом ключа, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ, выход первого элемента ИЛИ соединен со счетным входом второго счетчика; вход задания начального состояния которого подключен к шине единичного потенциала, первый и второй входы второго элемента ИЛИ соединены соответственно е выходом "Меньше или равно" и выходом "Больше" первого блока сравнения, р-й разрядный выход 1(п/2)+ +1 3-го регистра соединен с вторым входом (р-г)-го элемента И третьей группы, выход которого соединен с соответствующим разрядным входомЮОЯ выходного регистра, выход которогоявляется выходом медианы устройства 2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок сравнения содержит компаратор, два ключа, элемент И и вычитатель, причемпервый вход компаратора соединен с 1 О информационным входом первого ключаи является первым информационнымвходом блока, второй вход компаратора соединен с входом вычитаемоговычитателя и является вторым информационным входом блока, выход "Меньше или равно" компаратора соединен суправляющим входом второго ключаинформационный вход которого соединен с первым входом элемента И и 2 О является синхронизирующим входомблока, выход второго ключа являетсявыходом "Меньше или равно" блока,выход "Больше" компаратора соединенс вторым входом элемента И, выходкоторого соединен с управляющим входом первого ключа и является выходом"Больше" блока, выход второго ключасоединен с входом уменьшаемого вычитателя, выход которого является.информационным выходом блока. л

СмотретьЗаявка

4329948, 17.11.1987

СИБИРСКИЙ МЕТАЛЛУРГИЧЕСКИЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

КУЛАКОВ СТАНИСЛАВ МАТВЕЕВИЧ, БЕГИШЕВ ГЕННАДИЙ АЛЕКСАНДРОВИЧ, ГОЛУБЕВА НАТАЛЬЯ ФЕДОРОВНА, ЗИМИНА КЛАРИСА АЛЕКСАНДРОВНА, ЧЕРНЫШ ИГОРЬ ГЕННАДЬЕВИЧ

МПК / Метки

МПК: G06F 17/18, G06F 7/08

Метки: сортировки, чисел

Опубликовано: 07.11.1989

Код ссылки

<a href="https://patents.su/10-1520546-ustrojjstvo-dlya-sortirovki-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сортировки чисел</a>

Предыдущий патент: Устройство для определения закона распределения

Следующий патент: Устройство для поиска информации в памяти

Случайный патент: Устройство для диагностики подшипников качения