Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

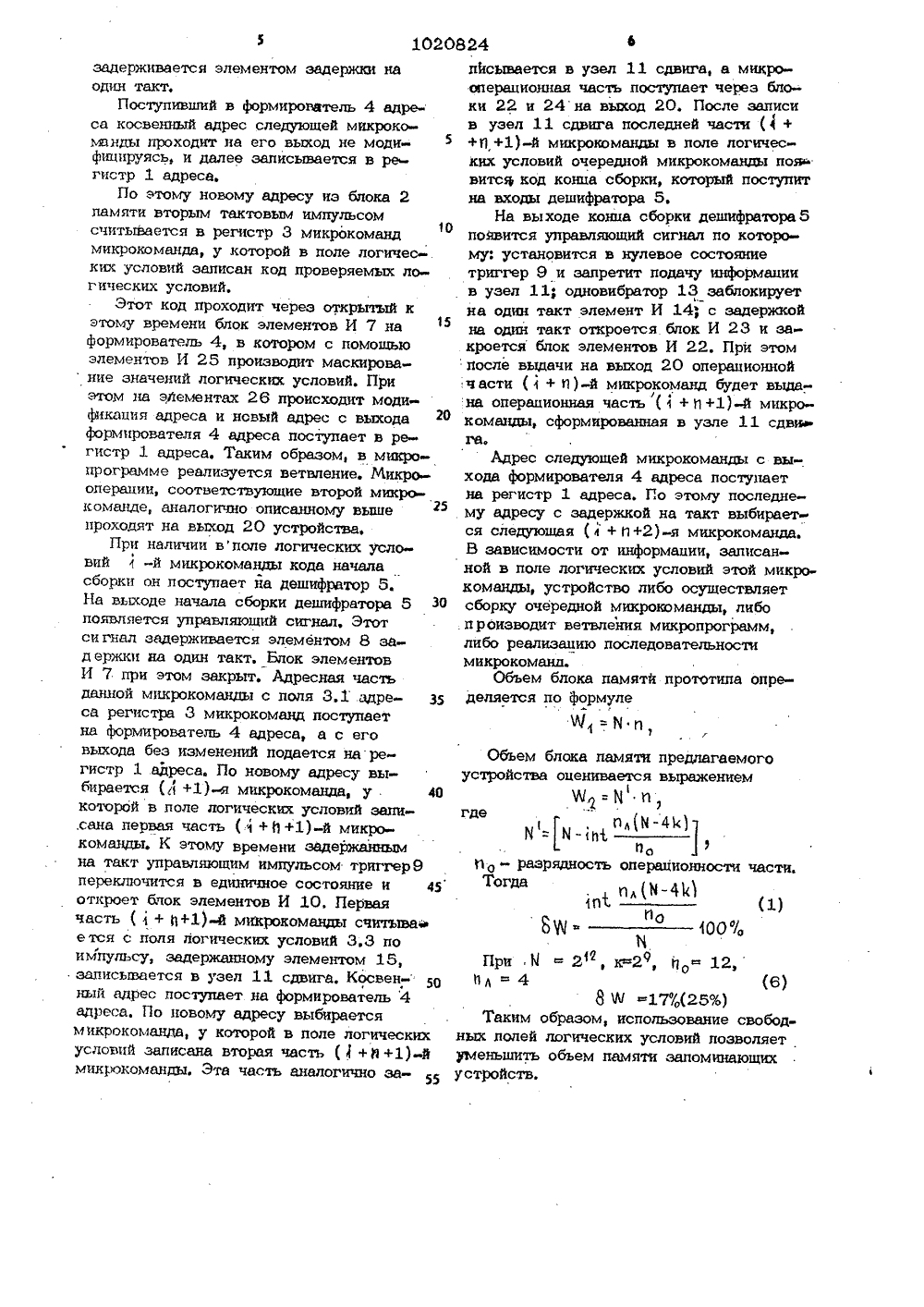

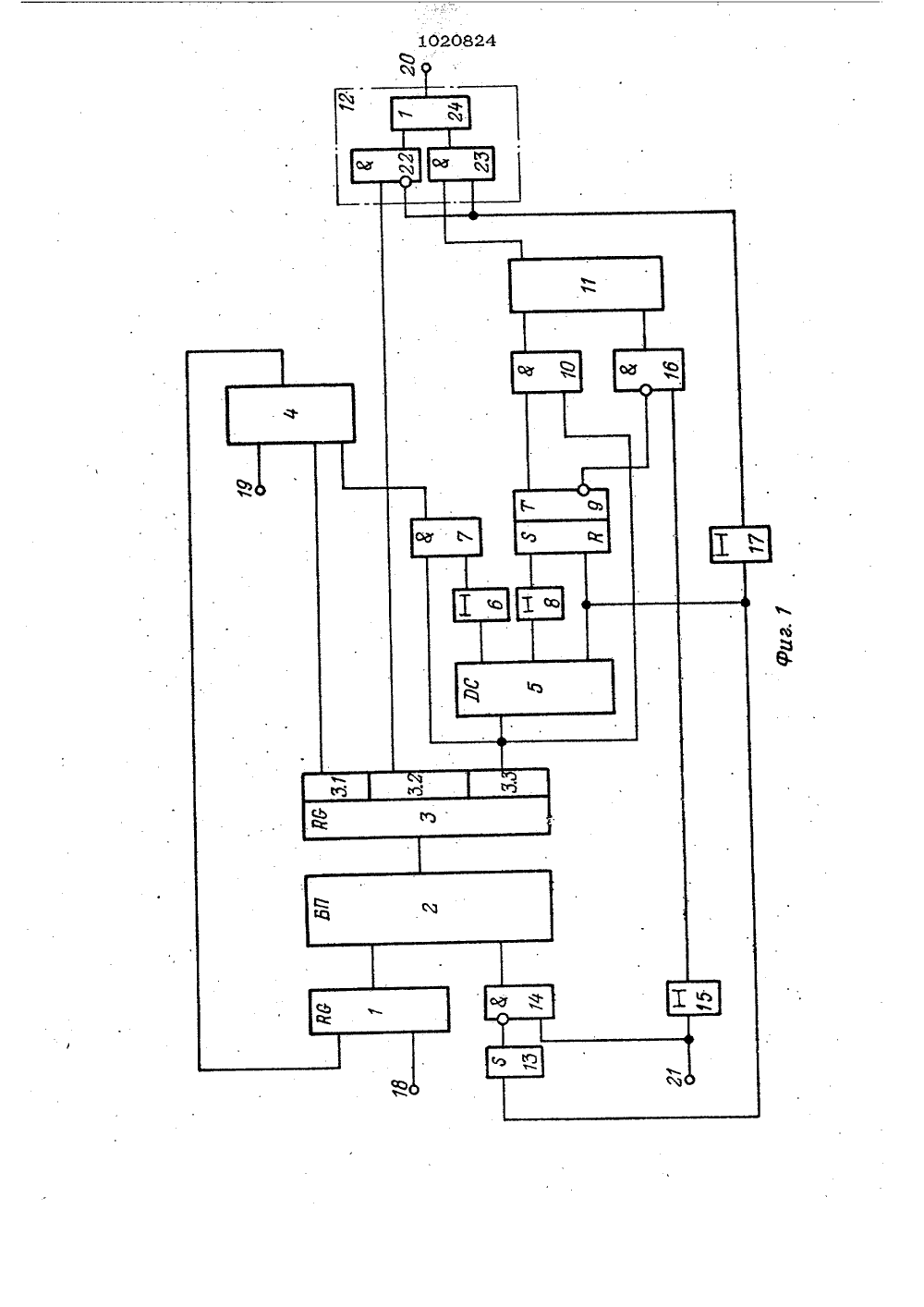

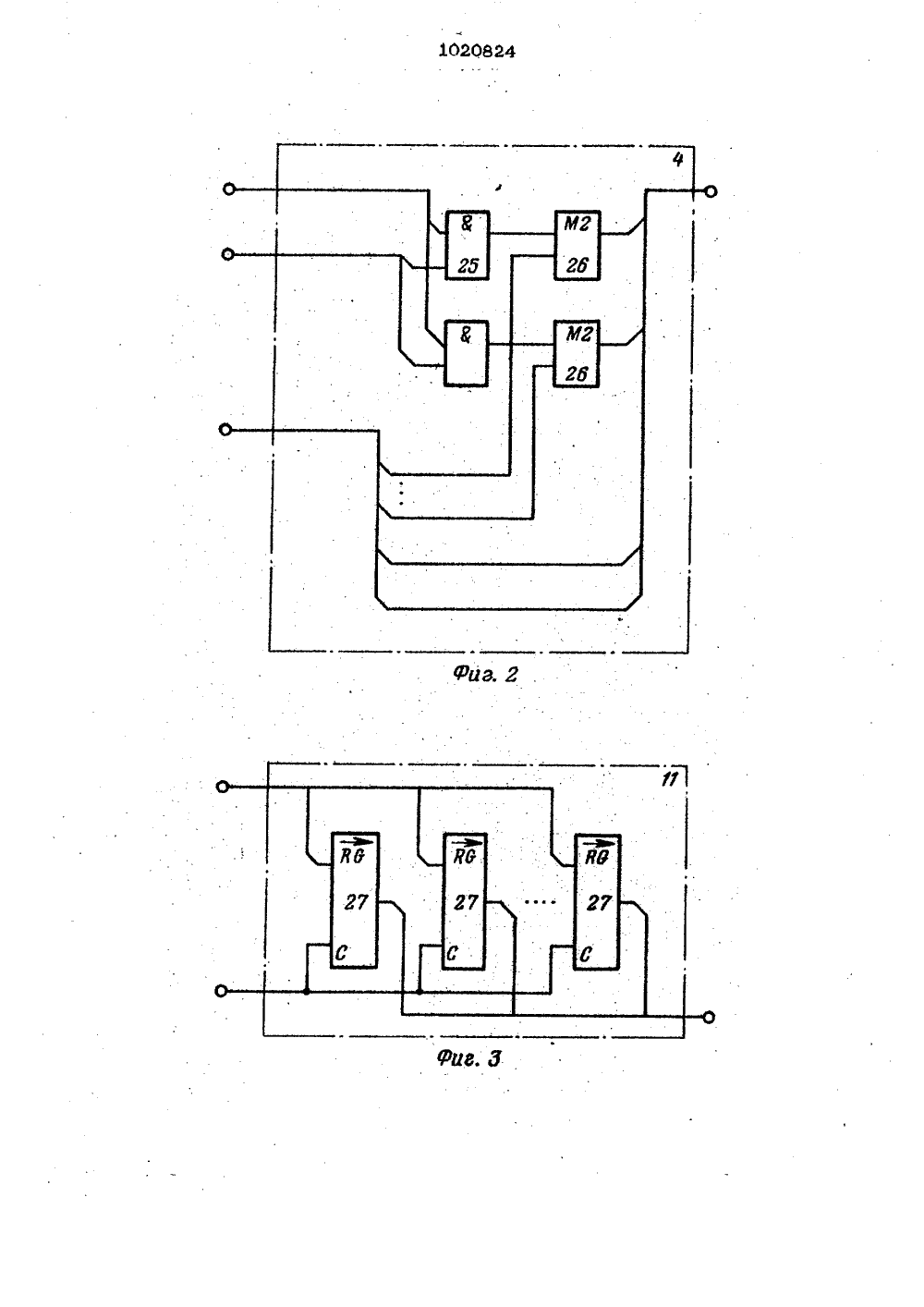

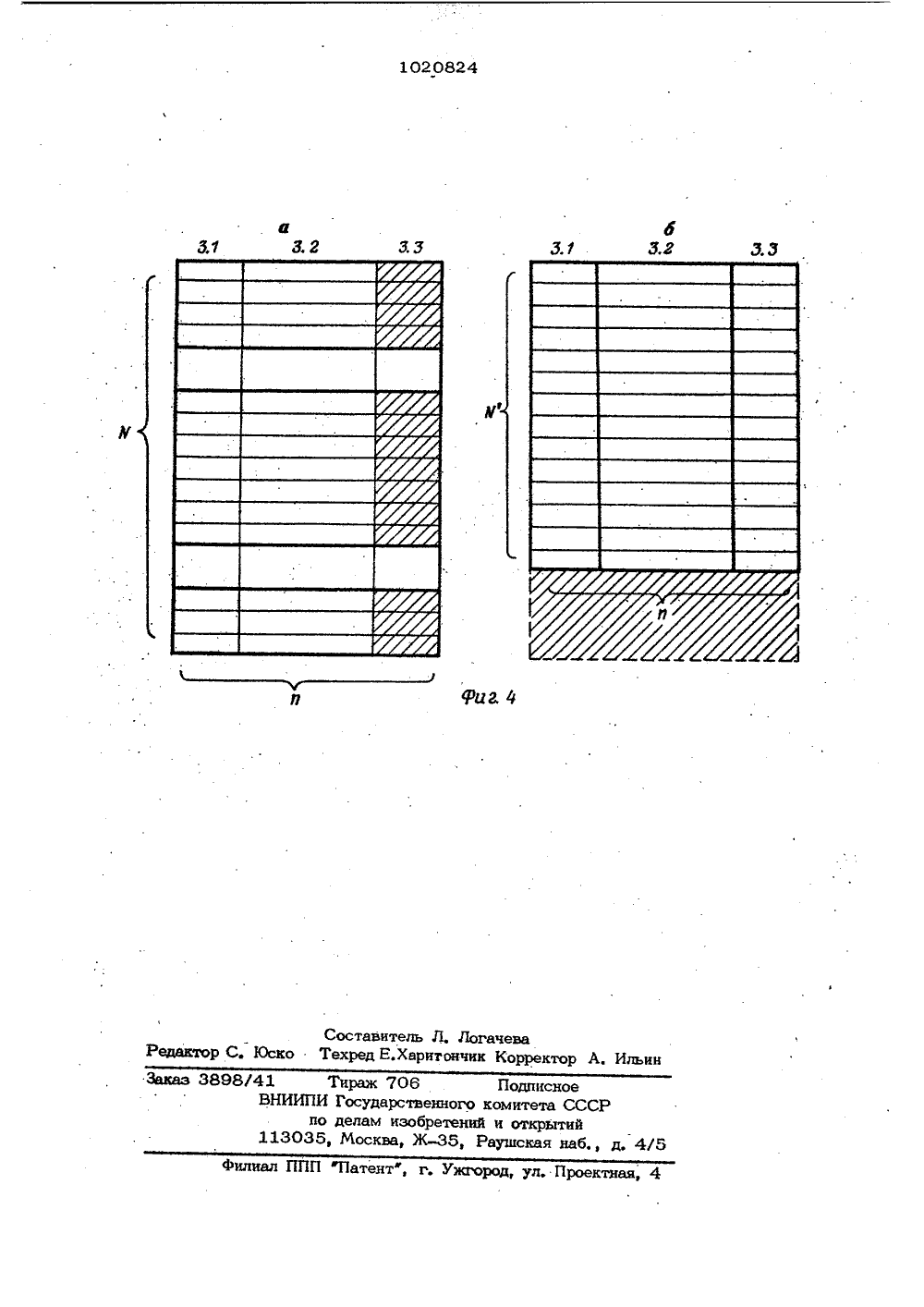

/2 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И.ОТКРЫТИЙ ТЕ ОПИСАНИЕ ИЗОБ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) 09.02.82 выход поля логических условий регистра(46) 30. 05.83. Вюл. М 20 . микрокоманд соединен с первыми входами(72) Г. Н. Тимонькин, В. С. Карпам первого и второго блока элементов И.С. Н. Ткаченко и Ю. И, Матвиенко и с входом дешифратора,выход логйческих7 . условий которого соединен через первый(53) 681. 325(088.8) элемент задержки с вторим входом пер(56) 1. Авторское свидетельство СССР вого блока элементов И, выход которогоМ 857995, кл. С 1 06 Р 8/22, 1981, соединен с вторым входом логических2, Справочник по цифровой вычисли- условий формирователя адреса, выход нательной технике. Под ред, Б. Н. Мали- чала сборки дешифратора через второй . ковского, К., Техникаф 1979, с. 2 Ъ 3 . элемент задержки соединен с единичным(поототип), входом триггера, а. выход конца сборки(54) (57) МИКРОПРОГРАММНОЕ УСТ дешифратора соединен с нулевым входомРСЙСТВО УПРАВЛЕНИЯ, содержащее триггера, через одновибратор - с ииверсРегистр адреса, блок памяти, регистр ным входом первого элемента И а чеф емикрокоманд, формирователь адреса,. при", рез третий элемент задержки - с первычем первый информационный вход регист ми входами третьего и четвертого бло-.ра адреса соединен с входом кода опера- ков элементов И, выходы которых черезции устройства, выход риистра адреса блок элементов ИЛИ соединены с выхосоединен а адресным входом блока памяти,. дом микроопераций устройства, единич- авыход которого соединен с входом регисъ- ный и нулевой выходы триггера соедира микрокоманд, выход поля адреса ко-,нены соответственно с вторым входом . файфторого соединен с адресным входом фор- второго блока элементов И и инверсным 1 мирователя адреса, вход логических ус-; входом второго элементаИ, выходы коловий устройства соединен с первым входом торых соединены соответственно с ийфорлогических условий формирователя адреса, вы-, мационным и управлякпцим входами реход которого соединен с вторым инфор гистр сдвига ввод которого соединен ф мационным входом регистра адреса, о т - с:вторым входом третьего блока элемен-л и ч а ю щ е е с я тем, что, с цельютов И, выход микроопераций регистра. 91 Ьсокращения оборудования, оно дополнитель микрокоманд соединен с.вторым входом но содержит дешифратор, первый второй четвертого блока элементов И, выход так третий и четвертый элементы задержки, товых импульсов устройства соединен с первый, второй, третий и четвертый бщ прямым входом первого элемента И, а ки. элементов И, триггер, блок элемен- через четвертый элемент зад тов ИЛИ, узел сдвига, одновибратор прямым входом второго элем ержки - сента И.1020824 Изобретение относится к вычислительной технике и может быть использовано при построении устройств управлениямикропрограммных электронных вычислительных машин и систем.Известно микропрограммное упр авляюшее устройство, содержащее блок памятимикрокоманд, регистры адреса и микрокоманд и формирователь адреса ЯНедостатком этого устройства являеься большая избыточность блока памяти,которая обусловлена неэффективным испотьзованием свободных полей микрокомандее1Наиболее близким по технической сущности к пуедлагаемому является устройство, содержащее регистр адреса, блок памяти, регистр микрокоманд, формировательадреса, причем первый информационныйвход регистра адреса является входомкода оперции устройства, выход регистраадреса соединен с информационным входомблока памяти, выход которого соединен свходом регистра микрокоманд, выход поля адреса которого соединен с адреснымвходом формирователя адреса; вход логических условий устройства соединен спервым входом логических условий формирователя адреса, выход котброго соединен с вторым информационным входомрегистра адреса 2Недостатком. данного устройства является большой объем блока иамяти, так какзаписанные последовательно микрокоманды содержат в поле логических условий 3полезную информацию только в точкахветвления .микропрограммы. Вследствиеэтого в блоке памяти остается значительное количество свободных ячеек, которыене используются в процессе реализациимикропрограмм, Доля используемогообъема блока памяти оценивается формулои3= - (- - ) юи,07где Ч, т - разрядность поля логических условий и микрокоманды в целом;1(, М - число микрокоманд ветвле;ния и общее числО микрокоманд.При Н= 4, П "- 32, 8 - 136; Поскольку 90-95% объема оборудования микроПРОГРаММНогО УСТРОйСТВа пРИходнтя Наблок памяти, то его избыточность существенно снижает экономичность устрой-Цель изобретения - сокращение оборудования,Поставленная цель достигается тем,что в микропрограммное устройство управления, содержащее регистр адреса,блок памяти, регистр микрокомжщ, фор 5мирователь адреса, причем первый информационный вход регистра адреса соедииен с входом кода операции устройства, выход регистра адреса соединен с 1 О адресным входом блока памяти, выходкоторого соединен с входом регистрамикрокоманд, выход поля адреса которогосоединен с адресным входом формирователя адреса; вход логических условийустРойства соединен с первым входомлогических условий формирователя "адреса, выход которого соединен с вторыминформационным входом регистра адреса,дополнительно введены дешифратор, пер- Овый, второй, третий и четвертый элементы задержки, первый, второй, третий ичетвертый блоки элементов И, триггер,блок элементов ИЛИ, узел сдвига, одновибратор, первый, второй элементы И, . причем выход поля логических условийрегистра микрокоманд соединен с первыми входами первого и второго блоковэлементов И и с входом дешифратора,выход логических условий которого сое-"динен через первый элемент задержки с Овторым входом первого блока элементов И, выход которого соединен с вторым входом логических условий,формирователя адреса, выход начала сборки дешифратора через второй элемент задержки 5 соединен с единичным входом триггера,а выход конца сборки дешифратора соединен с нулевым входом триггера, черезодновибратор - с инверсным входом первого элемента И, а через третий элемент, задержки - с первыми входамитретьего и четвертого блоков элементов И,выходы которых через блок элементовИЛИ соединены с выходом микроопераций устройства, единичный и нулевой вы ходы триггера соединены соответственнос вторым входом второго блока элементов И и инверсным входом второго эле-мента И, выходы которых соединены соответственно с информационным и.управ- О ляющим входами регистра, сдвига, выход которого соединен с вторым входомтретьего блока элементов И выход микр оопераций регистра микрокоманд соеди- . нен с вторым входом четвертого блока 5 элементов И, выход тактовых импульсов устройства соединен с прямым входоМпервого элемента И, а через четвертыйэлемент задержки - с прямым входом второго элемента И.24 . .4Устройство содержит (фиг, 1) регистр 1 адреса, блок 2 памяти, регистр 3 микрокоманд, содержащий поле 3.1 адреса, поле 3.2 микроопераций, поле 3.3 логических условий, формироватеть 4 адреса, дешифратор 5, первый элемент 6 задержки, первый блок элементов И 7, второй элемент 8 задержки, триггер 9, второй бдок элементов И 10, узел 11 сдвига, коммутатор 12, одновибратор 13, первый элемент. И 14, четвертый:эле- мент 15 задержки, второй элемент И 16, третий элемент 17 задержки, вход А 8 кода операции, вход 19 логических усло вий, выход 20 микроопераций, вход 21 тактовых импульсов, Коммутатор содержит блоки элементов И 22 и 23 и блок элементов ИЛИ 24.Формирователь 4 адреса (фиг. 2) со держит блок элементов И 25, блок эле ментов 2 б сумма по модулю два. Узел 11 сдвига (фиг. 3) содержит группу регистр. ров 27 сдвига.На фиг. 4 использованы следующие обозначения; й - разрядность микроко. манд, й ( й) - число линеек в блоке памяти прототипа и предлагаемого устройства. Нумерация полей сожыдает с нумерацией полей на регистре 5В исходном состоянтти в блоке 2 нам яти записаны микропрограммы, регистр 1 адреса, регистр 3 микрокоманд и узел 12 сдвига и триггер 9 находятся в нулевом состоянии.Устройство работает следующим образом.Начальный адрес (код оцерации) .поступает со входа 18 на регистр 1 адреса. В соответствиис этим адресом из .блока 2 памяти выбирается первая микрокоманда и по,тактовому иыпульсу, поступающему со входа 21 через открытый элемент И 14, считьтваетсч в р гистр 3 микрокоманд. 3 10208 свободное поле логических условий пре- . щ.дьтдущих П микрокоманд линейной последовательности.При считывании одной иэ Ь микроко .манд информация иэ полей. логических условий поступает в регистр сдвига 25В(О +1)-ом такте считывается не микрокоманде, записанная в. запоминающем.устройстве следом за .( П -1)-1-й, а микрокоманде, собранная в регистресдвига. В следующем такте считывания . що считывается очередная микрокоманда,записанная в блоке памяти. Такиы образом, при наличии в микропрограмме учась. ков, содержащий число .микрокоманд между микрокомандами ветвления достажч- . ное для записи целой микрокоыанды в полях логических условий, существенно сокращается объем брома памяти.Для идентификации наличия в полях логйческих условий частей микрокоманды используют коды начала и конца сборки.Для эщх код(и используются коды с большим числом единйц, например при .05 Фвами кодами могут быть 01111, .1 О 111, 11011.Коды логических условий не содержат больтцого числа единиц, поэтому можно однозначно, с вероятностью Р 1, выбратьтакие коды начала и конца сборки, которые ие совпацут с кодами логических условий.50 Косвенный адрес следующей ыикрокоманды поступает с выхода поля 3.1 адреса регистра 3 микрокоманд в форми- рователь 4 адреса.Код ыикроопераций считывается с поля.3.2 микроопераций регистра 3 микржоманд и проходит через открытый блок элементов И 22 и блок элементов ИЛИ 24 на вход 20 устройства,Если в поде логических условий этой микрокомандьт записан код идентификатор микрокоманды ветвления, то дешифра тор 5 выдает разрешающий сигнал на выходе логических условий, этот сигнал. На. фиг. 1 представлена функциональнаи схеме микропрограммного управляющего устройства; на фиг. 2 и 3 - функ ционалыпае схемы формирователя адреса 55 к узла сдвига соответственно; на фиг. 4 варианты упаковки блока памяти протожпа (а) и предлагаемого устройства (б). Сущность изобретения состоит в умень шепни объема блока памяти за счет использования свободных полей логических условий в последовательностях микрокоманд стандарптого формата для хранения частей микрокомаиды, т.е, сокращения оборудования.юСтаттдартяый формат микрокомйнды соф стоит из трех полейт ноля адреса, поля логических условий и поля микроопераций. 30 ., В поле логических условий информация записывается только тогда, когда в.мыропрограммв происходит ветвление. В ос тельных слу таях поле логических условий свободно. Это поле в предлагаемом уст-.р ойстве испоньзуется следующим образоме. Каждую микрокоманду разбивают на Пчастей и каждую часть записывают в(1)ЯО ф/ задерживается элементом задержки на один такт.Поступивший в формирователь 4 адреса косвенный адрес следующей макрокоманды проходит на его выход не модифиццруясь, и далее записывается в ре гистр 1 адреса.По этому новому адресу из блока 2 памяти вторым тактовым импульсом считывается в регистр 3 микрокоманд микрокоманда, у которой в поле логичес-. ких условий записан код проверяемых логических условий.Этот код проходит через открытый к этому времени блок элементов И 7 на формирователь 4, в котором с помошью элементов И 25 производит маскирова ние значений логических условий. При этом на элементах 26 происходит модификация адреса и новый адрес с выхода формирователя 4 адреса поступает в регистр 1 адреса. Таким образом, в микропрограмме реализуется ветвление. Микро- операции, соответствующие второй микро. команде, аналогично описанному выше проходят на выход 20 устройства.При наличии вполе логических условий-й микрокоманды кода начала сборки он поступает йа дешифратор 5. На выходе начала сборки дешифратора 5 З 0 появляется управляющий сигнал. Этот си гнал задерживается элементом 8 задержки на один такт. Блок элементов И 7 при этом закрыт. Адресная часть дмшой микрокоманды с поля 3.1 адре сй регистра 3 микрокоманд поступает на формирователь 4 адреса, а с его выхода без изменений подается на регистр 1 адреса. По новому адресу выбирается (д +1)-я микрокоманда, у 40 которой в поле логических условий запи,сана первая часть (1+ И+1)-й микро- команды. К этому времени задержанным на такт управляющим импульсом триггер 9 переключится в единичное состояние и 45 откроет блок элементов И 10, Первая часть ( 1+ п+1)-й микрокоманды считывае ется с поля логических условий З.З по импульсу, задержанному элементом 15, записывается в узел 11 сдвига. Косвенный адрес поступает на формирователь 4 адреса, По новому адресу выбирается микрокоманда, у которой в поле логических условцй записана вторая часть ( 1 +И+1)-й микрокомйнды, Этй часть аналогично зй 824пйсывается в узел 11 сдвига, а микрооперационная часть поступает через бло-ки 22 и 24 на выход 20. После записив узел 11 сдвига последней части (4 ++П +1)-й микрокоманды в поле логических условий очередной микрокоманды поямвится код конца сборки, который поступитна входы дешифратора 5.На выходе конца сборки дешифратора 5появится управляющий сигнал по которому: установится в нулевое состояниетриггер 9 и запретит подачу информациив узел 11; одновибратор 13 заблокируетна один такт элемент И 14) с задержкойна один такт откроется блок И 23 и закроется блок элементов И 22. При этомпосле выдачи на выход 20 операционнойчасти (1+ ц)-й микрокоманд будет вьщана операционная часть (+ п+1)-й микрокоманды, сформированная в узле 11 сдвиггйфАдрес следующей микрокоманды с выхода формирователя 4 адреса поступаетна регистр 1 адреса. Го этому последнему адресу с задержкой на такт выбирается следующая (+ 8+2)-я микрокоманда.В зависимости от информации, записанной в поле логических условий этой микрокоманды, устройство либо осуществляетсборку очередной микрокоманды, либопроизводит ветвления микропрограмм,либо реализацию последовательностимикрокоманп.Объем блока памятй прототипа определяется по формулеЯ=И и,Объем блока памяти предлагаемогоустройства оценивается выражениемф= д,( Г . Ои(В)М =И-МО о - разрядность операционности части,Тогдап 13 юПри й -2, кИ -12Ол =4 (6)8 ф/ ф=17(25%)Таким образом, использование свободных полей логических условий позволяетуменьшить объем памяти запоминающихустройств.1020824 едйкто Ильи филиал ППП фПа Заказ 3898/41 ВН 11Составитель Л. Логачевао Техред Е.Харигоичик Кор Тираж 706 Подписное ИПИ Государственного комитета СССР по делам изобретений и открытый 35, Москва, Ж, Раушская наб.,

СмотретьЗаявка

3393401, 09.02.1982

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, МАТВИЕНКО ЮРИЙ АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.05.1983

Код ссылки

<a href="https://patents.su/7-1020824-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Интегро-дифференциальный вычислитель

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ футеровки изложницы центробежной машины