Интегро-дифференциальный вычислитель

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1020823

Автор: Баранов

Текст

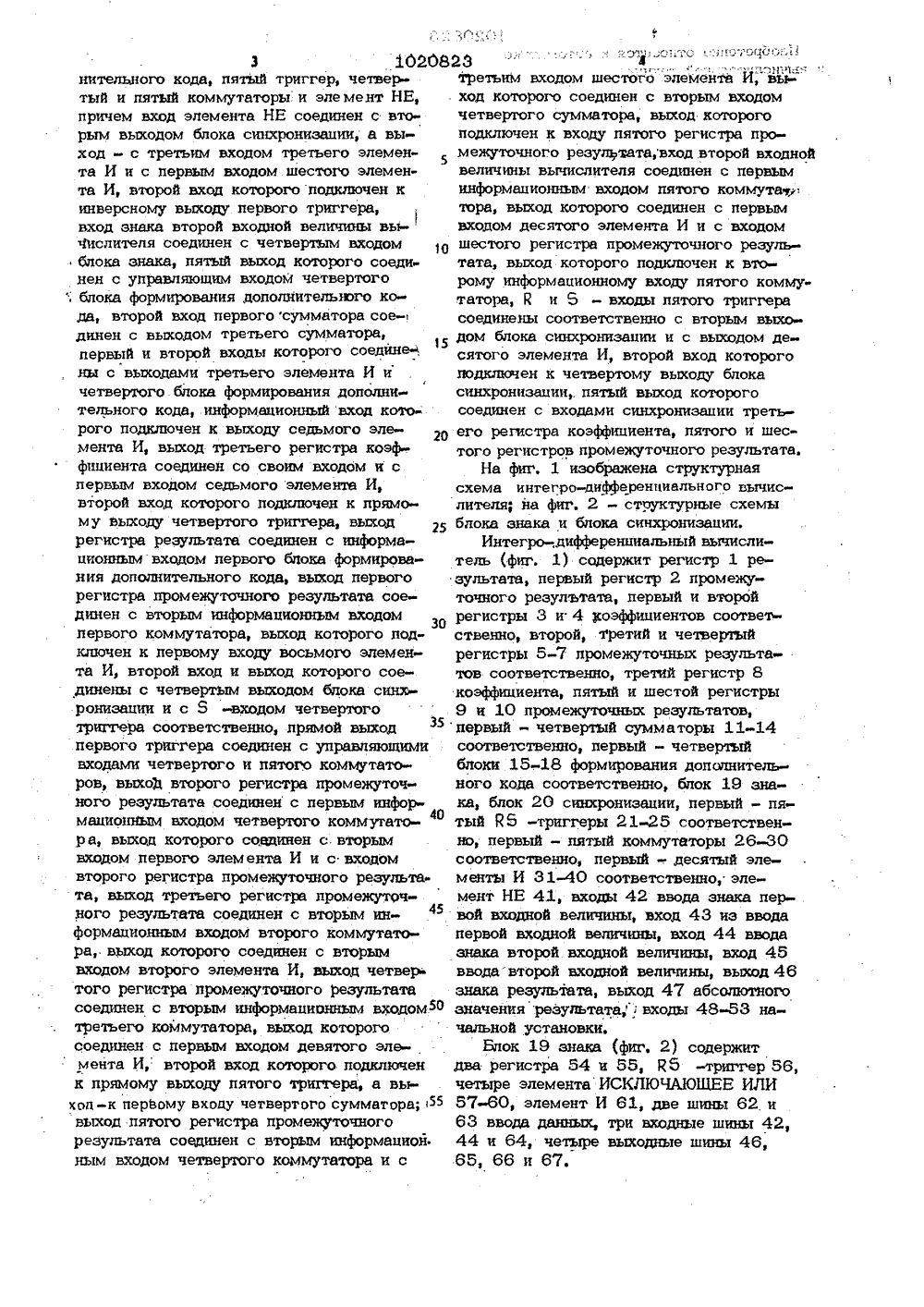

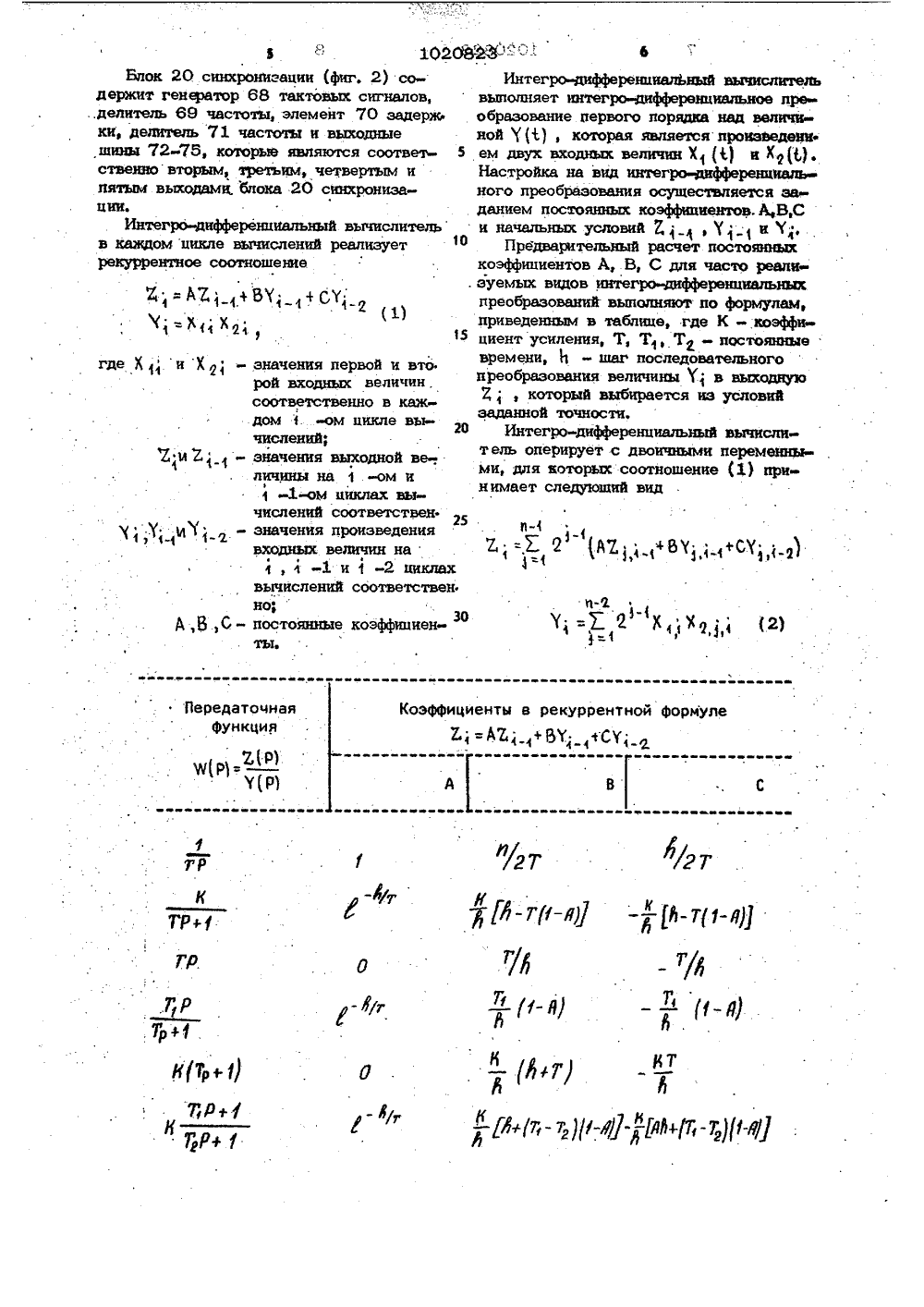

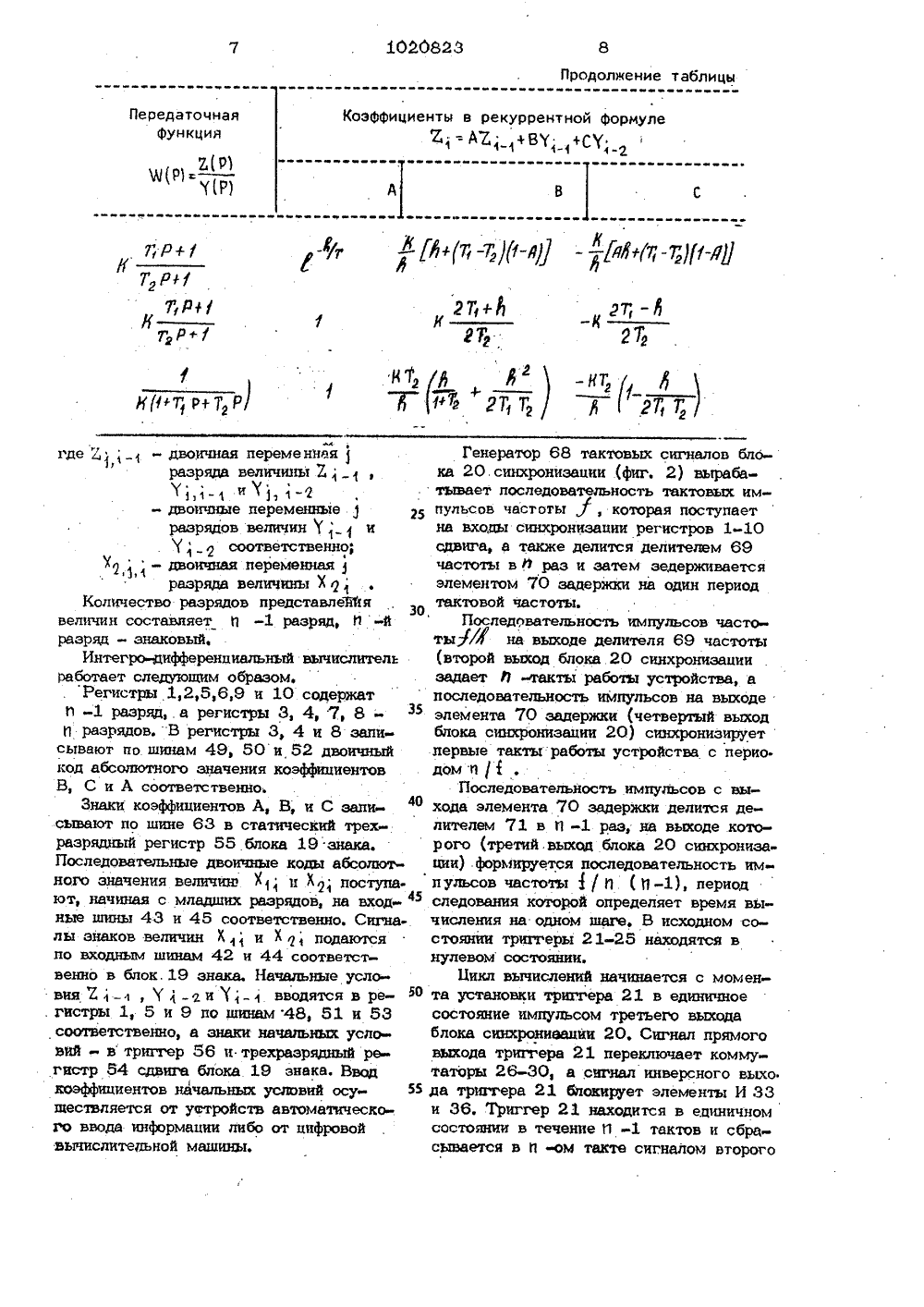

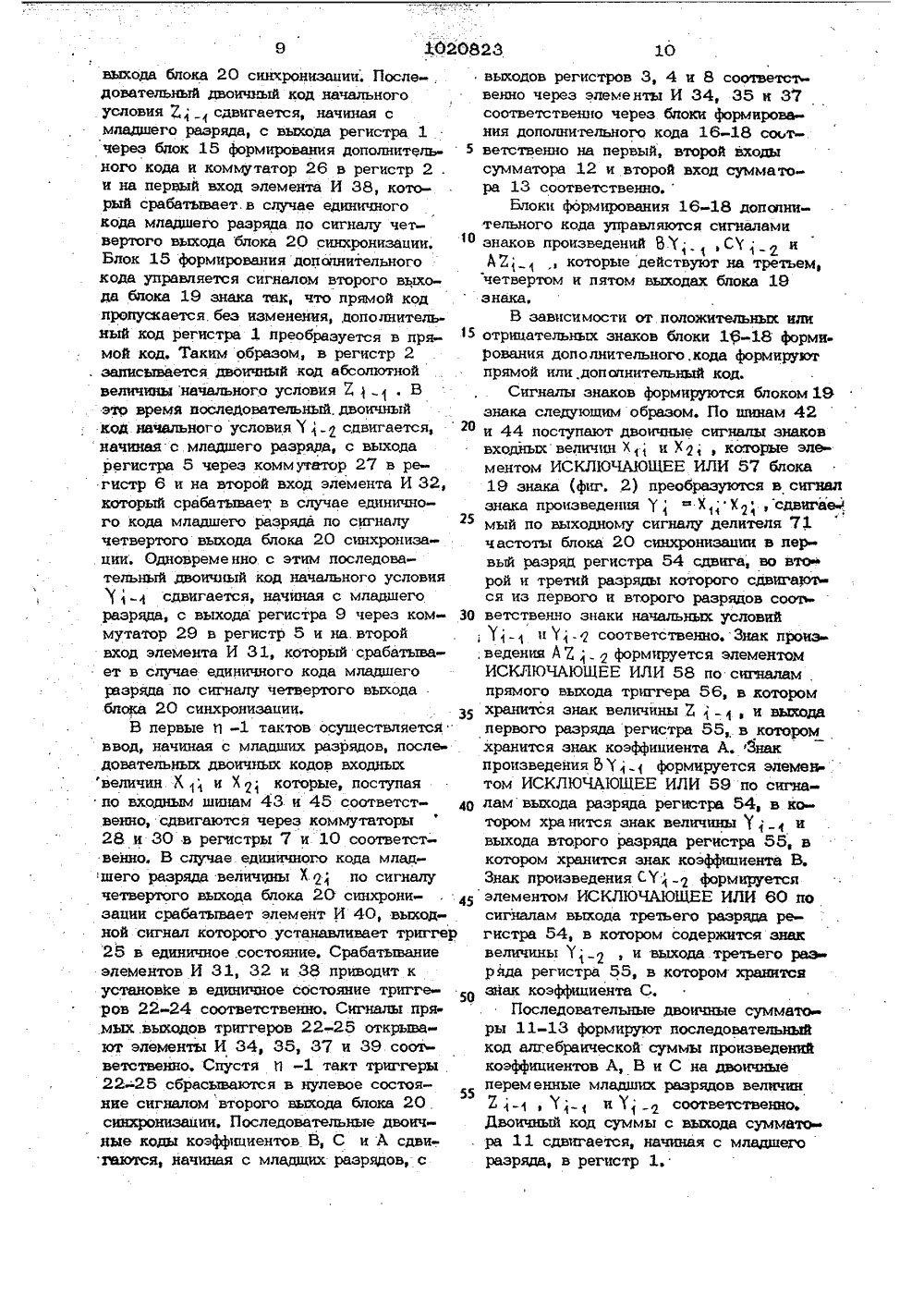

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК ЯО,1020823 1 с 067/64 П Д ИОПИСАНИЕ ИЗОБРЕТЕНИЯ ТОРСКОМУ .СВИДЕТЕЛЬСТВ(71) Институт электродинамики АН Украинской ССР(56) . 1. Вычислительная техника. Справочник под ред, Г, Д, Хаски и Г. А, Кона. Т. 1. М-ЛфЭнергцяф 1964,с. 63-73, табл 2-2-5.2. Неслуховскцй К, С. цифровые диференциальные анализаторы. М., "Машиностроенцеф, 1968, с, 84; рис. 15,3, Авторское свидетельство СССРпо заявке М 2895320/18-24,кл. ( 06 Г 7/64, 18,03.80 (прототип)(54) (57) 1. ИНТЕГРО-ДИффЕРЕНЦИАЛЪНЫЙ ВЪЧИСЛИТЕЛЪ, содержащий регистр результата, два регистракоэффыциента и четыре регистра промежуточных результатов, два сумматора, три блока, формирования дополнительного кода, блок знака, блок синхронизации, четыре триггера, три коммутатора и десять элементов И, причем вход знака первой входной величины вычислителя соединен с первым входом блока знака, первый выход которого соединен с вых одом знака результата вычислителя, выход первого сумматора соединен с входом регистра результата и вторым входом блока знака, второй третий и четвертый выходы которого; соецинены с управляющими входамц первого, второго и третьего блоков формирования дополнительного кода соответственно, первый выход блока синхронизации соедцнен с третьим входом блока знака, второй выход - с Й -входами первого, второго,ОСУДАРСТВЕННЫЙ НОМИТЕТ СССР О ЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬТИ Ъ третьего и четвертого триггеров, третий выход - с 5 -входом первого тригге ра, четвертый выход - с первыми входамц первого и второго лементов И и пятью .выход - с входами синхронизации регистра результата, первого и второго регистра коэффициента и первого, второго, третьего и четвертого регистров р- промежуточных результатов, выход регистра результата соединен с первым входом третьего, элемента И, второй ф- вход которого соединен с инверсным выколем первого триггера прямой выход которого подключен к управляющим входам первого, второго и третьего коммутаторов, выход первого блока формирования дополнительного кода соединен с выходом абсолютного значения результата вычислителя и с первым информационным входом первого коммутатора, выход которого подключен к входу перво го регистра йромежуточного,результата, выходы первого и второго регистров коэффициентов соединены со своиМи входами. Ю и с первыми входами четвертого и пятого . Ь 3 элементов И соответственно, прямые вьют ходы второго и третьего триггеров соеди- рр нены с вторыми входами четвертого и пятого элементов И соответственно, Б входы второго и третьего триггеров соединены с выходами первого и второго элементовИ соответственно, первый вход первого сумматора подключен к выходу второго сумматора, первый и второй входЫ которого соединены с выходами,Вфф второго ц третьего блоков формирования дополнитегп ного кода, цнформаццотпые входы которых подключены к выходам четвертого ц пятого элементов И соответственно, выход второго регистра промежуточного результата соединен с пер1020823 Ри Заказ 38 41 Тираж 706 ВНИИПИ Государственного ком но делам изобретений и 113035, Москва, Ж, РауПоднисноеитета СССРоткрытий ская набд илиал ППП фПатент", г. Ужгород, ул. Проектная,Составитель А. Чеканов едактор С. Юско Техред Т.фанта Корректор А. Дзятковым информационным входом второго коммутатора, выход которого соединен с входом третьего регистра промежуточного результата, вход первой входной величины вычислителя соединен с первым информационным входом третьего коммутатора, выход которого соединен с.входом четвертого регистра промежуточного результата, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем вычисления нелинейных интегро-дифференциальных преобразований, в него введены третий регистр коэффициента, пятый и шестой регистры промежу. точных результатов, третий и четвертый сумматоры, четвертый блок формирования дополнительного кода, пятый триггер, чеъ вертый и пятый коммутаторы и элемент НЕ, причем вход элемента НЕ соединен с вторым выходом блока синхронизации, а выход - с третьим входом третьего элемента И и с пррвьпм входом шестого элемента И, второй вход аоторого подклкь чен к инверсному выходу первого триггера, вход знака второй входной величины вычислителя соединен с четвертью входом блока знака, пятый выход которого соединен с управляющим входом четвертого блока формирования дополнительного кода, второй вход первого сумматора соединен с выходом третьего сумматора, первый и второй входы которого соединены с выхо дами третьего элемента И и .четвертого блока формирования дополнительного кода,информационный вход которого подключен к выходу седьмого элемента И, выход третьего регистра коэффициента соединен со своим входом и с первым входом седь мого элемента И, второй вход которого подключен к прямому выходу четвертого . триггера, выход регистра результата соединенс информационным входом первого блока формирования дополнительного кода, выход первого регистра промежуточного результата соединен с вторым информационным входом первого коммутатора, выход которого подключен к первому входу восьмого элемента И, второй вход 823й выход которого соединены с четверым выходом блока синхронизации и с Ь -вхо дом четвертого триггера соответственно, прямой выход первого триггера соединен с управляющими входами четвертого и пятого коммутаторов, выход второго регистра промежуточного результата соединен с первым информационным входом четвертого комм утатора, выход которого соединен с вторым входом первого элемента И и с входом второго регистра промекуточного результата, выход треть его регистра промекуточного результата соединен с вторым информационным входом второго коммутатора, выход которого соединен с вторым входом второго элемента И, выход четвертого регистра промежуточного результата соединен с вторым информационным входом третьего коммутатора, выход которого соединен с первым входом девятого элемента И, второй вход которого подключен к прямому выходу пятого триггера, а выход - к первому входу четвертого сумматора, выход пятого регистра промекуточного результата соединен с.вторым информационным входом чатвертого коммутатора и с третьим входом шестого элемента И выход которого соединен с вторим входом четвертого сумматора, выход .которого подключен к входу пятого регистра промежуточного результата, вход второй входной величины вычислителя соединен с первым информационным входом и ягого коммутатора, выход которого соединен с первым входом девятого элемента И и с входом шестого регисъра промежуточного результата, выход которого подключен к второму информационному входу пятого коммутатора, Й и5 - входы пятого триггера соединенысоответственно с вторым выходом блокасинхронизации и с выходом десятого элемента И, второй вход которого подключенк четвертому выходу блока синхронизации, питий выход которого соединен с входами синхронизации третьего регистракоэффициента, пятого и шестого регистр.ров промежуточного результата.10208Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано для моделирования и управления динамическими объектами в различных Отраслях промышленности,Известны аналоговые интегро-дифференциальные устройства, содержащие аналоговые интеграторы, сумматоры и масштабные блоки для задания коэффициентов передачи 1 10Недостатком аналоговых интегро-дифференциальных устройств является низкаяточность вычислений выходных сигналовв случае достаточно больших значенийпостоянных времени, характерных для 15многих технологических процессов,Известны цифровые интегро-дифференциальные устройства типа цифровых дифференциальных анализаторов, которыесодержат ряд цифровых интеграторов, 20коммутйруемых между собой согласнозаданному интегро-дифференциальномупреюбрамвгаао 2:. Однако штегро-дифференциальные устройства характеризуются низким быстродействием и сложностью реализации.Наиболее близким по технической супности к предлагаемому является интегродифференциальный вычислитель, содержащий семь регистров, два сумматора,три блока формирования дОНОлнительногокОда, блок знака, блок синхронизации,четыре триггера, двенадцать элементов И,четыре элемента ИЛИ и элемент задержки, с соответствующими связямиЮ,Однако вычислитель Обладает низким35быстродействием и ограниченными функциональными воэможйостями.Мель изобретения - повышение быстродействия и расширение функциональныхвоэможностей путем вычисления нелинейных40интегро-пифференциальныхпреобразований.Поставленная. пель достигается тем,что в интегро-дифференциальный вычисслитель, содержащий регистр результата,два. регистра коэффициента и четыре ре 45гистра промежуточньк результатов, двасумматора, три блока формирования до. Полнительного кОда, блок знака, блОксинхронизации, четыре триггера,: трикоммутатора и десять элементОв И, причем вход знака первой входной величины вычислителя соединен с первым входом блока знака, первый выход которогосоединен с выходом знака результатавычислителя, выход первого сумматорасоединен с входом регистра результатаи вторим входом блока знака, второй,третий и четвертый выходы которого 1 23 ъсоединены с управляющими входами первого, второго и третьего блоков форми рования дополнительного, кода соответственно, первый выход блока синхронизации соединен с третьим входом блОка знака, второй выход - с К -входами первого, второго, третьего и .четвертого триггеров, третий вцход - с 5 -входом первого триггера, четвертый выход - с первыми входами первого и второго элементов И и пятый выход - с входами 1синхронизации регистра результата, первого и второго регистров коэффициента и первого, второго, третьего и четверто го регистров промежуточных результатов, выход регистра результата соединен с первым .входом третьего элемента И, второй вход которого соединен с инверсным выходом первого триггера, прямой выход которого подключен к управляюцщм входам первого, второго и третьего комму таторОв, выход первого блока формирования дополнительного кода соединен с выходом абсолютного значения результата вычислителя и с первым информационным входом первого коммутатора, выход которого подключен к входу первого регистра промежуточного результата, выходы первого и второго регистров коэффициентов сое динены со своими входами и с первьжи входами четвертого и пятого элементов И соответственно, прямые выходы второго и третьего триггеров соединены с вторыми входами четвертого и пятого элементов И соответстэенно, 5 -входы второго и третьего триггеров соединены с выходами первого и второго элементов соответственно, первый вход первого сумматора подключен к выходу второго сумматора, первый и второй входы кото рого соединены с выходами. второго и третьего блоков формирования дополнительного кода, информационные входы которых подключены к выходам четвертого и пятого элементов И соответственно, выход второго регистра промежуточного результата соединен с первым информационным входом второго коммутатора, выход которого соединен с входом третьего регистра промежуточного результата, вход первой входной величины вычислите ля соединен с первым информационным входом третьего коммутатора, выход которого соединен с входом четвертого регистра промещточного результата, ввецены третий регистр коэффициента, пятый и шестой регистры промежуточных результатов, третий и четвертый суммато ры, четвертый блок формирования допол 1020823"ю " ""кительного кода, пятый триггер, четвер- третьим входом шестого элемента И, вы-тый и пятый коммутаторы и элемент НЕ, . ход которого соединен с вторым входомпричем вход элемента НЕ соединен с вто- четвертого сумматора, выход которогорым выходом блока синхронизации, а вы- подключен к входу пятого регистра проход - с третьим входом третьего элемен- межуточного резущлата,вход. второй входнойта И и с первым входом шестого элемен- величины вычислителя соединен с первымта И, второй вход которого подключен к информационным входом пятого коммутауинверсному выходу первого триггера, тора, выход которого соединен с первымвход знака второй входной величины вью- входом десятого элемента И и с входомчислителя соединен с четвертым входом 1 О шестого регистра промежуточного резульбпока знака, пятый выход которого соеди тата, выход которого подключен к втонен с управляющим входом четвертого рому информационному входу пятого комму; блока формирования дополнительного ко татора,и 5 - входы пятого триггерада, второй вход первогосумматора сое- соединены соответственно с вторым выходинен с выходом третьего сУмматора дом блока синхронизации и с выходом депервый и второй входы которого соедине сятого элемента И, второй вход которогоны с выходами третьего элемента И и . подключен к четвертому выходу блокачетвертого блока формирования дополни синхронизации,. пятый выход котороготельного кода, информаионный вход кото- соединен с входами синхронизации третьрого подключен к выходу седьмого эле- о его регистра коэффициента, пятого и шесмента И, выход третьего регистра коэф того регистров промежуточного результата.фициента соединен со своим входом и с На фиг, 1 изображена структурнаяпервым входом седьмого элемента И, схема интегро-дифференциального вычисвторой вход которого подключен к прямо- лителя; на фиг. 2 - структурные схемыму выходу четвертого триггера, выход 5 блока знака и блока синхронизации.регистра результата соединен с информа- Интегро-,дифференциальный вычислиционным входом первого блока формирова- тель (фиг, 1) содержит регистр 1 рения дополнительного кода, выход первого зультата, первый регистр 2 промежурегистра промежуточного результата сое- точного резулътата, первый и второйдинен с вторым информационным входом, регистры 3 и 4 коэффициентов соответпервого коммутатора, выход которого под- отвеяно, второй, третий и четвертыйключен к первому входу восьмого элемен- регистры 5-7 промежуточных результата И, второй вход и выход которого сое- тов соответственно, третий регистр 8динены с четвертым выходом блока синз- коэффициента, пятый и шестой регистрыронизации и с Я -входом четвертого 9 и 10 промежуточных результатов,триггера соответственно, прямой выход 5 первый - четвертый сумматоры 11-1435первого триггера соединен с управляющими соответственно, первый - четвертыйвходами четвертого и пятого коммутато- блоки 15-18 формирования дополнительров, выход второго регистра промежуточ- ного кода соответственно, бпок 19 знаного результата соединен с первым инфор- ка, блок 2 О синхронизации, первый - пямационным входом четвертого коммутато- тый РБ -триггеры 21-25 соответствен 40ра, выход которого соддинен с. вторым но, первый - пятый коммутаторы 26-30входом первого элемента И и с входом соответственно, первый -. десятый элевторого регистра промежуточного резульм- менты И 31-40 соответственно, элета, выход третьего регистра промежуточ- мент НЕ 41, входы 42 ввода знака перного результата соединен с вторым ин вой входной величины, вход 43 из вводаформационным входом второго коммутато- первой входной величины, вход 44 вводара, выход которого соединен с вторым знака второй входной величины, вход 45входом второго элемента И, выход четвер вводавторой входной величины, выход 46того регистра промежуточного результата знака результата, выход 47 абсолютногосоединен с вторым информационным входом 5 О значения результата, входы 48-53 натретьего коммутатора, выход которого чапьной установки,соединен с первым входом девятого эле- Бпок 19 знака (фиг. 2) содержитмента И,: второй вход которого подключен два регистра 54 и 55, Я 5 -триггер 56,к прямому выходу пятого триггера, а вы- четыре элемента ИСКЛЮЧАЮШЕЕ ИЛИход-к первому входу четвертогосумматора; Я 57-60, элемент И 61, две шины 62 ивьиод пятого регистра промежуточного 63 ввода данных, три входные шины 42,результата соединен с вторым информациой 44 и 64, четыре выходные шины 46,ным входом четвертого коммутатора и с 65, 66 и 67.1020823 Продолжение таблицы Коэффициенты в рекуррентной формуле , = А8,СУ;Передаточная функцияТР+КТРф 17 Р /8 -7 Р+ 1 ИфД В,4где- двоичная переменнаяразряда величины Еи,- двоичные переменныеРазрядов величин Уисоответственно;Х- двоичная переменная 4разряда величины Х 2Колнчество разрядов представлеМявеличин составляет О -1 разряд, И -йразряд - знаковый,Интегро-дифференциальный вычислительРаботает следующим образом.Регистры 1,2,5,6,9 и 10 содержатп -1 разряд,. а регистры 3, 4, 7, 8 П разрядов. В регистры 3, 4 и 8 записывают по шинам 49, 80 и 52 двоичныйкод абсолютного значения коэффициентовВ, С и А соответственно.Знаки коэффициентов А, В, и С запи40сывают по шине 63 в статический трехразрядный регистр 55 блока 19 знака.Последовательные двоичные коды абсолютного значения величин 1 Хи Хпоступают, начиная с младших разрядов, на вход 45ные шины 43 и 48 соответственно. Сигна-.лы знаков величин Е 1 и Х у, подаютсяпо входным шинам 42 и 44 соответственно в блок. 19 знака. Начальные условия 2, 1и 1 1 вводятся в ре 50. гистры 1, 5 и 9 по шинам 48, 81 и 83соответственно, а знаки начальных условий - в триггер 56 и трехраэрядный регистр 84 сдвига блока 19 знака. Вводкоэффициентов начальных условий осу 55ществляется от устройств автоматическо-.го ввода информации либо от цифровойвычислительной машины,Генератор 68 тактовых сигналов блока 20.синхронизации (фиг. 2) вырабатывает последовательность тактовых импульсов частоты У, которая поступает на входы синхронизации регистров 1-10 сдвига, а также делится делителем 69 частоты в 1 раз и затем зедерживается элементом 70 задержки на один период тактовой частоты.Последовательность импульсов часто- тыУ на выходе делителя 69 частоты (второй выход блока 20 синхронизации задает 6 -фгакты работы устройства, а последовательность импульсов на выходе элемента 70 задержки (четвертый выход блока синхронизации 20) синхронизирует первые такты работы устройства с перио. дом л (1,Последовательность импульсов с выхода элемента 70 задержки делится де лителем 71 в П -1 раэ, на выходе .которого (третий. выход блока 20 синхронизации) формируется последовательность импульсов частоты 1 / П ( П), период следования которой определяет время вычисления на одном шаге. В исходном состоянии триггеры 21-28 находятся в нулевом состоянии.Цикл вычислений начинается с момента установки триггера 21 в единичное состояние импульсом третьего выхода блока синхрониаацки 20, Сигнал прямого выхода триггера 21 переключает коммутаторы 26-30, а сигнал инверсного выхо да триггера 21 блокирует элементы И 33 и 36. ниггер 21 находится в единичном состоянии в течение 0 -1 тактов и сбра сывается в й -ом такте сигналом второговыхода блока 20 синхронизации. После-, довательный двоичный код начального условиясдвигается, начиная с младшего разряда, с выхода регистра 1 через блок 15 формирования дополнительного кода и коммутатор 26 в регистр 2 . и на первый вход элемента И 38, который срабатывает. в случае единичного кода младшего разряда по сигналу четвертого выхода блока 20 синхронизации,Блок 15 формирования допопнитепьного кода управляется сигналом второго выхода блока 19 знака так, что прямой код пропускается. беэ изменения, дополнительный код регистра 1 преобразуется в прямой код. Таким образом., в регистр 2 , записывается двоичный код абсолютной величины начального условия Е 1. В эю время последовательный, двоичный код начального условия 1сдвигается, начиная с младшего разряда, с выхода регистра 5 через коммутатор 27 в регистр 6 и на второй вход элемента И 32, который срабатывает в случае единичного кода младшего разряда по сигналу четвертого выхода блока 20 синхронизации. Одновременно с этим последовательный двоичный код начального условиясдвигается, начиная с младшего разряда, с выхода регистра 9 через коммутатор 29 в регистр 5 и на. второй вход элемента И 31, который срабатывает в случае единичного кода младшего уезряда по сигналу четвертого выхода блока 20 синхронизации.В первые П -1 тактов осушествляется" ввод, начиная с младших разрядов, последовательных двоичных кодов входных величин Х , и М; которые, поступая по входным шинам 43 и 45 соответственно, сдвигаются через коммутаторы 28 и 30 в регистры 7 и 10 соответственно. В случае единичного кода млад- :щего разряда величины Х 2 по сигналу четвертого выхода блока 20 синхронизации срабатывает элемент И 40, выходной сигнал которого устанавливает триггер 25 в единичное .состояние. Срабатывание элементов И 31, 32 и 38 приводит к установ 1 се в единичное состояние тригге ров 22-24 соответственно. Сигналы пря.мых .выходов триггеров 22-25 открывают элементы И 34, 35, 37 и 39 соответственно. Спустя и -1 такт триггеры 22-25 сбрасываются в нулевое состояние сигналом второго выхода блока 20 синхронизации. Последовательные двоичные коды коэффициентов В, С и А сдвигаются, начиная с младших разрядов, с выходов регистров 3, 4 и 8 соответственно через элементы И 34, 35 и 37соответственно через блоки формирования дополнительного кода 16-18 ссьт5 ветственно на первый, второй входысумматора 12 и второй вход сумматора 13 соответственно.Блоки формирования 16-18 допсднительного кода управляются сигналами1 О знаков произведений 8.;. С 1иА 2 1, которые действуют на третьем,четвертом и пятом выходах блока 19знака.В зависимости от положительных или15 отрицательных знаков блоки 1-18 формирования дополнительного. кода формируютпрямой ипи,допопнительный код.Сигналы знаков формируются блоком 19знака спедуюшим образом. По шинам 42о и 44 поступают двоичные сигналы знаковвходных величин Х,; и Хд;, которые элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 57 блока19 знака (фиг, 2) преобразуются в сигналзнака произведенияХ 1,Х , сдвигае 425 мый по выходному сигналу делителя 71частоты блока 20 синхронизации в первый разряд регистра 54 сдвига, во второй и третий разряды которого сдвигаются из первого и второго разрядов сооть 30 ветственно знаки начальных условийцу соответственно.Знак произ; ведения Аформируется элементомИСКНЮЧАЮЩЕЕ ИЛИ 58 по сигналампрямого выхода триггера 56, в которомЗ 5 хранится знак величины 2; 1 4, и выходапервого разряда регистра 55, в которомхранится знак коэффициента А, фЗнакпроизведения Ь 1формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 59 по сигна 40 лам выхода разряда регистра 54, в котором хранится знак величины У4 ивыхода второго разряда регистра 55, вкотором хранится знак коэффициента В.Знак произведения СУ,формируется45 элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 60 посигналам выхода третьего разряда регистра 54, в котором содержится знаквеличины У;р и выхода третьего разфряда регистра 55, в котором хранитсязнак коэффициента С,Последовательные двоичные сумматоры 11-13 формируют последовательныйкод алгебраической суммы произведенийкоэффициентов А, В и С на двоичныепеременные младших разрядов величин-1, Уи У 1соответственно,Двоичный код суммы с выхода суммато3.020823 Одновременно с этим с выхода сумматора 14 с;двигается начиная с младцн о разряда в регистр 9 последователыпяй двоичный код произведения величины Хна младший разряд величины 1 (который поступает с выходакоммутатора 28 через элемент И 39на первый вход сумматора 14).Поскольку регистры 3 2, 5, 6, 9и 10 содержат 11 -3. разряд, а регистры3, 4, 7 и 8 И разрядов, то спустя итактов двоп пые коды в регистрах 3., 25, 6, 9 и 10 сдвинутся на один разрядпо отношению к,двоичным кодам в регистрах 3, 4, 7 и 8 а также по отношению к сигналам четвертого выхода блока20 синхронизации,Поэтому в И +1-ом также на выходах элементов И 31, 32, 38 и 40 произойдет совпадение сигналов в случаеедцни 1 ных кодов во вторых разрядах величин1, (: 2, 2 -1Х 2 , сдвигаемых с выходов регистров 5, 6, 2 и 1соответственно. Так как триггер. 21 вэто время находится в нулевом состояниито коммутаторы 26-30 подключа 1 от выходы регистров 2, ; 7 5 и 10 соответственно к их входам соответственно,а с элементов И 33 и 36 снимаетсяблокировка от триггера 21. Б этом случае сумматор 13 формирует последовательный двоичный код суммы содержимогорегистра 1, сдвигаемого через элементИ 33, и произведения коэффициента А,сдвигаемого с вьжода регистра 8, навторой разряд величины Е1которыйс выхода регистра 2 через коммутатор 26и элемент И 38 фиксируется в триггере24, Сумматор 12 формрует последова-тельный двоичный код алгебраическойсуммы произведений коэффициентов В и С,сдвигаемых с выходов регистров 3 и 4соответственно, на вторые разряды величин У 1-. и Ч. соответственно, которые фиксируются в триггерах 22 и 23соответственно, Сумма тор 1 1 суммируетвыходные сигналы сумматоров 12 и 13,а результирующая сумма сдвигается врегистр 1. Сигналы суммы с выхода сумматора14 сдвигаются в регистр 9. В каждоми -ом такте сигнал второго выхода блока 20 синхронизации через инвертор 41блокирует элементы И ЗЗ и 36, оттирая этим младшие разряды накапливаемой суммы в регистрах 1 и 9 соответс твенно,10Б дальнейшем устройство функционирует аналогичным образом и через Й(п)тактов в регистре 1 формируется й -1старших разрядов выходной величиныв прямом или дополнительном коде, а врегистре 9 формируется и -1 старших15разрядов произведения У = Х 1,ХЕсли в регистре 1 сформировался дополнительный код, то последпй знаковыйразряд с выхода сумматора 13. поступает через элемент И 61 в триггер 5620 блока 19 знака.Один цикл работы интегро-дифференциального вычислителя или один шаг0 вычислений заканчивается,Последующие шаги вычислений согласно соотношению (2) выполняютсяинтегро-дифференциальным вычислителеманалогичным образом.Знак выходной величины 2форми.руется на прямом выходе триггера 56З 0. блока 19 знака и выходной шине 46.Последовательный двоичный код абсолютного значения величины 2сдвигаетсяс выхода регистра 1 через блок 15 формирования дополнительного кода на выход35 ную шину 47.Технико-экономические .преимушествапредлагаемого интегро-дифференциальноговычислителя заключаются в повышениибыстродействия и в расширении функцио 40 нальных воэможностей,По сравнению с прототипом, в которомодин шаг вычислений выполняется за2 И ( Л -1) тактов, быстродействие.предлагаемого интегро-дифференциального45 вычислителя вдвое выше, так как у негоодин шаг вычислений занимает толькоП ( 11 -1) тактов. 50 55 Б это время сумматор 14 суммирует содержимое регистра 9, которое сдвигаеь ся через элемент И 36, с произведением величщы,сдвигаемой с выхода регистра 7 через коммутатор 28 и элемент И 39, на второй разряд величины Х который с выхода регистра 10 через коммутатор 30 и элемент И 40 поступает в триггер 25. Функциональные возможности интегродифференциального вычислителя позволяют кроме линейных интегро-дифференци,альных преобразований первого порядка выполнять также нелинейные интегродифференциальные преобразования, например интегро-дифференциальные преобразования первого порядка с переменнымкоэффициентом усиления значение которого изменяется в зависимости от одногоиз входных сигналов иитегро-дифференциального вычислителя, Последовательное соединение ряда однотипных интегро-дифференциальных вычислителей, при котором выходные шины одного вычислителя подключаются к входным шинам другого вычислителя, позволяет реализовать сложныенелинейные интегро-дифференциальныепреобразования высокого порядка, например, с переменными коэффициентами усиления,

СмотретьЗаявка

3334474, 07.09.1981

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УССР

БАРАНОВ ГЕОРГИЙ ЛЕОНИДОВИЧ, БАРАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/64

Метки: вычислитель, интегро-дифференциальный

Опубликовано: 30.05.1983

Код ссылки

<a href="https://patents.su/10-1020823-integro-differencialnyjj-vychislitel.html" target="_blank" rel="follow" title="База патентов СССР">Интегро-дифференциальный вычислитель</a>

Предыдущий патент: Генератор псевдослучайных узкополосных сигналов

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ транспортного освоения лесосырьевых баз