Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1015384

Авторы: Благодарный, Скорик, Тимонькин, Ткаченко, Харченко

Текст

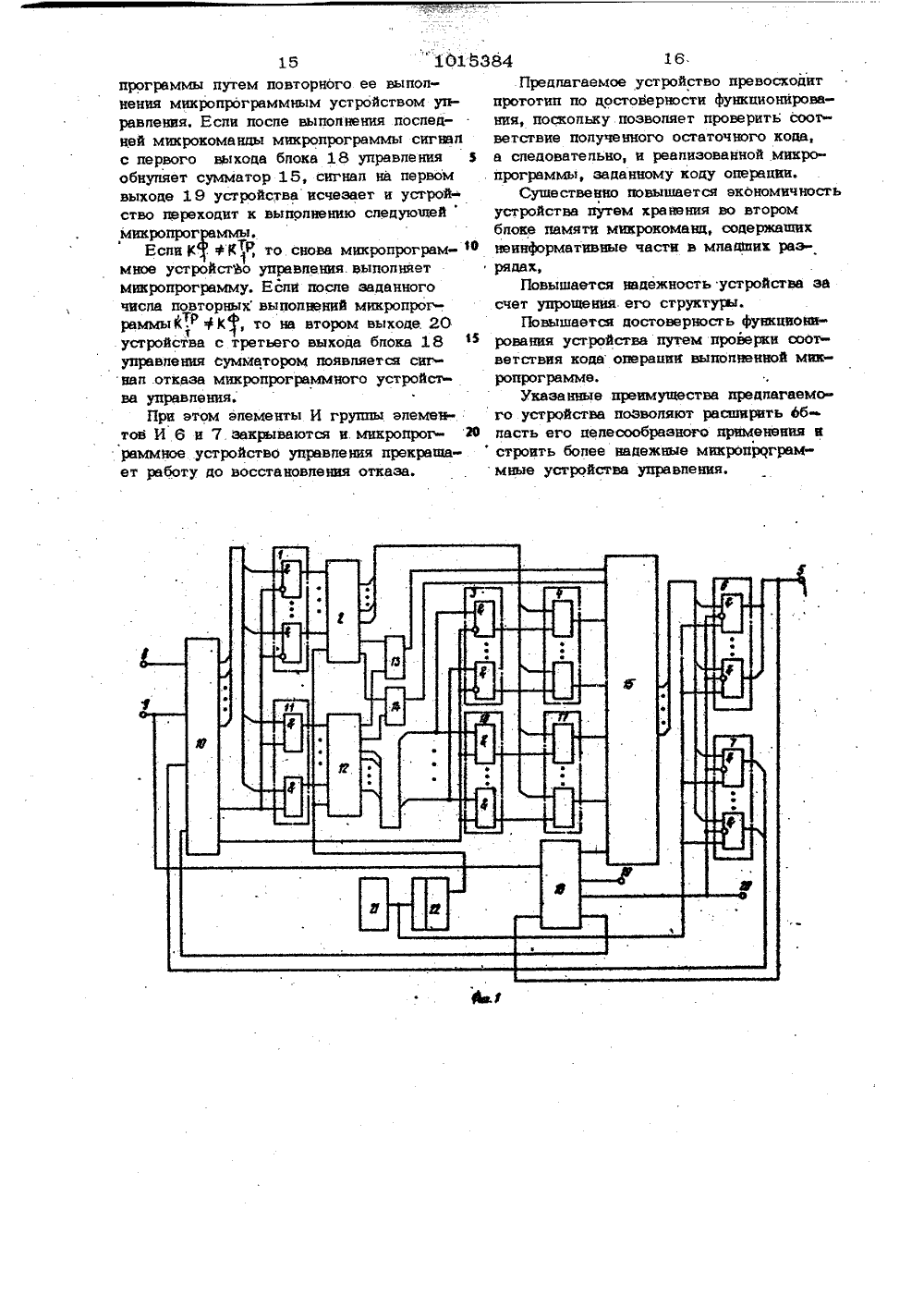

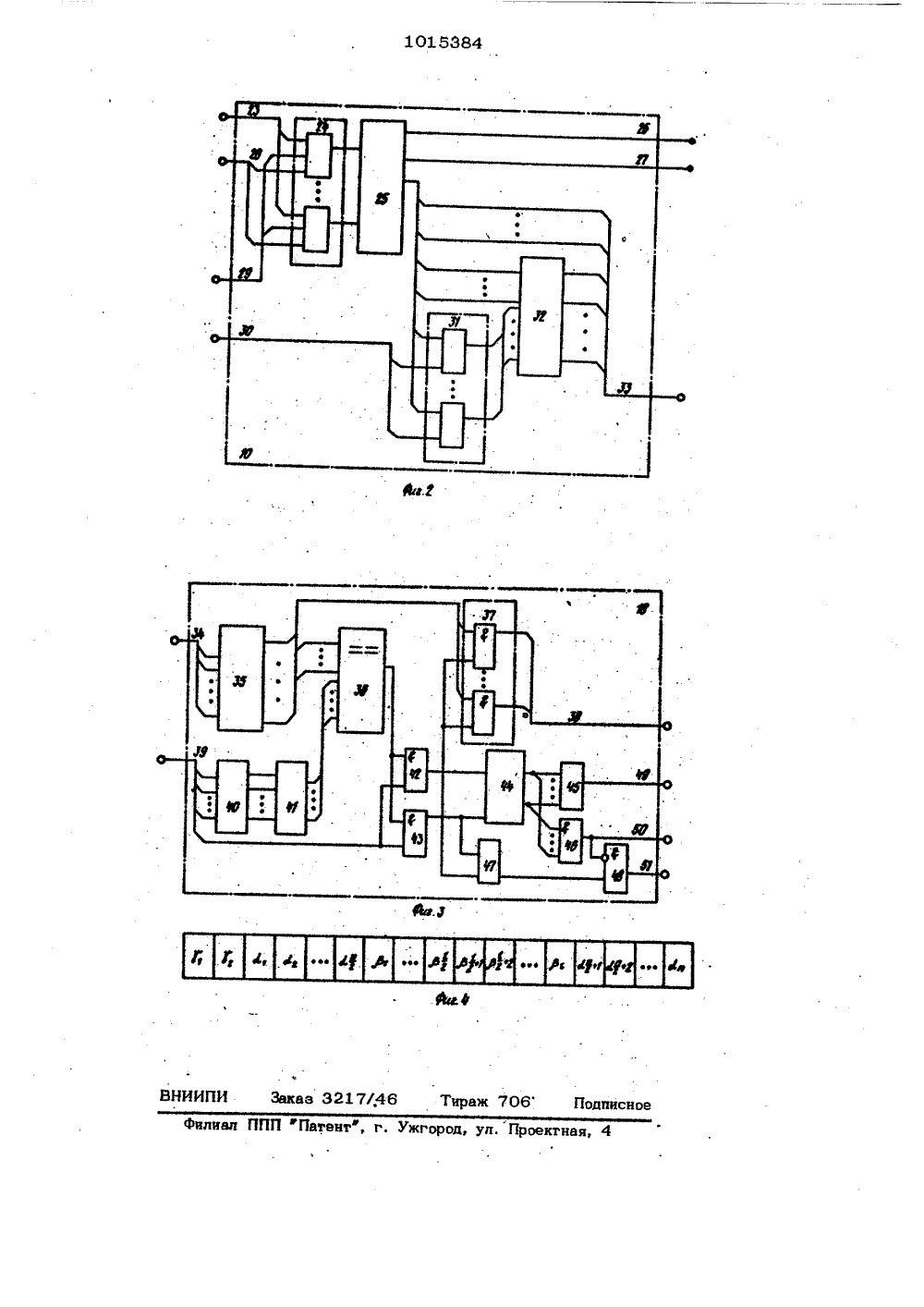

ПУБЛИНР 9/22; С 06 Р 11/ НЫЙ НОМИТЕГ ССОф ТЕНИИ И ОТНРЫТИ 1 АРОТОЕН АМ ИЗО ПИСАНИЕ ИЗОБРЕТЕНИЯАВТОРСКОМУ СВИДЕТЕЛЬСТВУ чн Ф 9 ай(22) 05.12.81управляющим выходом устройства, выхо(46) 30,04,83. Бюл. Ж 16, . ды элементовИ Иервой группы образуют(72) Г, Н.Тимонькин, В.С. Харченко, группу выходов микроопервций устройстваН.й.Благодарный, В.В.Скорик н С, Н.Тка- и соединены с первой группой входов бло:, ченко ка управления сумматором, выхоцы эпе(63). 681,3 (088.8):. ментов И второй группы соединены с вар.(6.) 1. Авторское свидетельство СССР. вой группой информационных входов комЖ 637346, кл. (06 Р 9/16, 1976, мутатора, первая группа информационных2, Авторское свидетельство СССР входов устройства соецинена с второйИФ 439811, кп, С 06 Р 9/16, 1975.группой информационных входов коммута 3. Авторское свидетельство СССРтора и второй группой входов блока упЬе 734687, кп, С 06 Р 9/16, 1980 . рввпения сумматоравторая груша инфо..аее с третьей группой информационных вхоцов(54) (57). 1. МИКРОПРОГРАММНОЕ коммутатора, о т л и. ч а ю щ е. е с я .УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее . тем, что,. с целью повышения достовер Екоммутатор, накапливающий сумматор, ности и снижения избыто ости юрвогоблок управления сумматором, первый иблока. памяти, введены третья, четвертая, . .второй блоки памяти, иэрвую и вторуюпятая, шестая. группы элементов И, одно- Сгруппы элементов ИЛИ, аврвую и вторую вибратор, первый и второй элементы ИЛИ,группы элементов И, генератор. тактовых . причем группа управляющих выходов блока Яимпульсов, причем,группа информаиион- . уирввления сумматором соецинэна с груз-.ных выходов первого блом памяти соедн- пой ущавпяющнх входов коммутатора, нэвнева с первыми входами соответствующих первый управляющий выход которого соеэлементов ИЛИ первой и второй групп,вы- динан с первыми входами элементов Иходы которйх соедиюны соответственно ..третьей и четвертой групп, второй управ- фс входами первого н второго операндов лающий выход, коммутатора соединен с фнакапливающего сумматора, информацион- юрвымн входами элементов И пятой и щные выходы которого соедиюаа с нервы-; шестой групп, информационные выходы р : ми входами элементов И первой и второй коммутатора соединены с вторыми входа-. ; групп, выход геюрвторв тактовых ампул- ми соответствующих элементов И третьейсов соединен,с вторыми входами элемви-: . н четвертой групп,. выходы которых соетов И первой и второй групп, первый и диюны с группама адресных входов пэр- ..второй ущавпяющие выходы бежа уп-ного н второго блоков памяти соответст-,флравлення, сумматором схаднюны соотнес венно, выход геюрвторв тактовых ампулы. , ственнос первым управляющим выходом сов соединен с входом одновибратора, выустройства и первым: управшющнм входаа ход которого соединен с ущввпяющиминакапливающего сумматора, третий выход входами первого и второго блоков иамблока управления сумматором соединен с тн, группа информационных выходов вто- , йнверснвными входами элементов И иер рого блока .памяти соецинена с вторыми10153вхоцами соответствующих элементов И .пятой и шестой групп, выходы элементовИ пятой и шестой групп соединены свторыми вхоцами соответствующих эпементов ИЛИ первой и второй групп, первый и второй выходы первого и второгоблоков памяти соединены соответственнос первыми входами первого и второгоэлементов,ИЛИ, с вторыми входами ьервого и второго элементов ИЛИ, выходыкоторых соединены соответственно с первым и вторым информационными входаминакапливающего сумматора,2. Устройство по п, 1, о тл ичаю щ е е с я тем, что коммутатор содержит группу элементов И, группу элементов ИЛИ, группу сумматоров по модупюдва. и резистор, причем первый, второйи третий информационные входы коммутатора соецинены соответственно с первым,вторым и третьими входами эпементовИЛИ группы выходы которых соединеныс информационными входами ре 1 истра,первый и второй выходы которого. являют-ся соответственно первым и вторым управляющими выходами коммутатора, группа управляющих,входов коммутатора соединена с первыми входами эпементов Игруппы, выходы которых соединены. с пер, выми входами .соответствующих сумматоров по модулю цва группь, группа информаиионных выходов регистра, соответствующая кодам проверяемых логическихусловий, соединена с вторыми входамисоответствующих элементов И группы выходы регистра, соответствующие модифипируемой части адреса, соединены с вторыми входами соответствующих сумматоров по моцупю два группы, выходы. сумматоров по модулю два группы и выходырегистра, соответствующие немоцифипиро 84ванной части адреса, образуют. группу выходов коммутатора. 3. Устройство по и. 1, о т л и ч а -ю щ е е с я тем, что блок управлениясумматором содержит регистр, схемусравнения, шифратор, дешифратор, первый,второй, третий и четвертый элементы И,группу элементов И, счетчик, первый ивторой элементы. ИЛИ, причем вход конца операции первой группы входов соединен с первыми входами первого и второгоэлементов И,а остальные группы вхоцов блока соединены с соответствующими входами дешифратора, выходы которого соединены с соответствующими входами шифратора, выходы шифратора соединены спервой группой входов схемы сравнения,выход которой соединен с вторыми входами первого и второго элементов И, вторая группа входов устройства соединенас входами регистра, выходы регистрасоединены с второй группой вхоцов схемы сравне,ния и первыми входами соот-.ветствующих элементов И группы, выходы которых образуют группу выходов блока; выход первого эпемента И соединенсо счетным входом счетчика, вторымивходами эпементрв И группы и. с первымвходом первого элемента ИЛИ, выходкоторого соединен с первым входом третьего элемента И, выхоц второго эпемента И соединен с установочным входомсчетчика и вторим входом первого элемента ИЛИ, выход третьего элемента Иявляется иервым выходом блока, группавыходов счетчика соединена с соответствующими входами четвертого элемента ивторого элемента ИЛИ,. выходы которыхявпяются соответственно вторым и третьнм выходами блока.1Изобретение относится к автоматике и вычислительной.технике и может быть использовано в качестве устройства уп равпения в ЭВМ и других системах с микропрограммным управлением,Известно устройство микропрограммного управления, содержащее бпок памяти .и накапливающий сумматор 1Недостатком этого устройства. является низкая экономичность. 2Известно также микропрограммное устройство управления, содержащее коммутатор, элементы ИЛИ, блок памяти микрокоманц сумматор, дешифратор,эпе менты И, генератор тактовых импульсов, блок управления сумматором 2. Недостатком этого устройства является низкая экономичность, вызванная избыточностью блока памяти.384 4Кроме того, недостатком прототипаявляется его низкая достоверность функционирования, что обусловлено отсутстввем проверки соответствия реализованноймикропрограммы коду операции. Это непоэвопяет испольэовать результаты выцопнення микропрограммы объектом управлеиия без их предваритепьной проверки, что требует введения .дополнительной,временной избыточности.Следовательно, низкие экономичюстьи достоверность прототипа существенноснижают его функционапьные возможности, и надежность,Цель изобретения - снижение избыточ. ности первого бпока памяти и повышениедостоверности функционирования устройства еПоставленная цель достигается .тем,что в микропрограммное устройство управпения, содержащее коммутагор, накапливающий сумматор, блок управления сумматором, первый и второй блоки памяти,первую и вторую группы элементов ИЛИ,.первую и вторую группы элементов И,. генератор тактовых имцупьсов, причемгруппа информационных выходов первогоблока памяти соецинена с первыми входами соответствующих эц ИЛИ первой и второй групп, выходы которых соединены соответственно с входами нервого и второго операндов накаппивающегосумматора, информационные выходы которого соединены с первыми входами эпементов И первой и второй групп, выходгенератора тактовых импульсов соединенс вторыми входами элементов И первойи второй групп, первый и.второй управляющие выходы блоке управления сумматором соединены соответственно с первым управляющим выходом устройства ипервым управляющим входом накапливающего сумматора, третий выход блока уцравлеиия сумматором соединен с инверс.ными вхоцами элементов И первой и второй групп и является вторым управляющимвыходом устройства, выхоцы элементов Ипервой группы.образуют группу выходовмикроопераций устройства и соединены спервой группой входов биска управления сум-матором, выходы .элементов И второйгруппы соединены с первой группой информационных входов коммутатора, первая, группа:информационных входов устройства:соединена с второй группой информационных входов коммутатора и вто-.рой грушюй входов блока управпеви 4сумматора, вторая группа информационйыхвходов устройства соединвна с третьей 3 1 О 18Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту явпяется микропрограммное устройство управления, содержащее коммутатор, накапливающий сумматор, бпок управления сумматором, первый и второй блоки памяти, первый и второй блоки элементов ИЛИ, первый и второй бпоки элементов И, генератор тактовых импульсов, причем выхоцы группы .выходов цер в вого блока памяти.соединены через эпе менты ИЛИ первого и,второго бпоков элементов ИЛИ с соответствующими входами первой и второй групп информацион ных входов накапливающего сумматора % . управляющий вход которого соединен с первым выходом блока управления сумма тором,а. выходы группы выходов соецинены с первыми:входами элементов И,второго и первого блоков элементов И,вторые входы которых. соединены с выходом генератора тактовых импульсов, выходы элементов И первого блока элементов И соединены с выходами микро- операций устройства и входами первой И группы входов блока управления сумматором, второй выход которого соединен . с первым выходом устройства, а третий выход соединен с третьими входами эцементов И первого и второго блоков эле ЗЕ ментов- И и третьим выходом устройства, входы первой группы входов коммутатора соединены с выходами соответствующих элементов И второй группы элементов И, входы второй группы входов соединены с входами второй группы входов бл 63 ка управления сумматором и входами первой группы входов устройства, входы .третьей группы входов соединены с вхо-. - дами второй группы входов устройстваЭ).Нецостатком известного устройства46явпяется низкая экономичность, обусловленная избыточностью кодов микрокомаид, записанных в первом блокепамяти.В прототипе реапизована идея дифференциального микропрограммирования,43состоящая в том,: что в блоке памятиуказываются не коды микрокоманц, а приращения .(дифференциалы) кодов. Это позволяет снизить разрядюсть форматамикрокоманц, а следовательно, повыситьэкономичность устройстваОднако дифференциалы кодов во многихслучаях содержат нвинформативаае (нулевые) части в младших разрядах (нв" приМер, при соседнем кодировании), что .ффпозволяет исключить из рассмотрения псмладшие разряды. В прототипе такаявоэможность не реализована.5 . 10183 группой информационных входов коммутатора, введены третья, четвертая, пятая, шестая группы элементов И, оановибратор первый и второй элементы ИЛИ, причем группа управляющих выходов блока управ- З ления сумматора соединена с группой управляющих входов коммутатора, первый управляющий выход которого соединен с первыми входами элементов И третьей и четвертой групп, второй управляющий вы ход коммутатора соединен с нврвыми входами элементов.И пятой и шестой групп, информационные выходы коммутатора соединены с вторыми входами соответствую 1 ших элементов И третьей и четвертой 3 групп, выходы которых соединены с группами адресных входов первого и второго блоков памяти соответственно, выход генератора тактовых импульсов соединен свходом одновибратора, выход которого 26 соединен с управляющими входами перво- го и второго блоков памяти, группа инФормационных выходов второго блока памяти соединена с вторыми входами . соответствующих элементов И пятой и 2 шестой групп, выходы элементов И пятой и шестой групп соединены с вторыми входами соответствуюших элементов ИЛИ первой и второй групп, первый и второй выходы первого и второго блоков памяти ЭО соединены соответственно с первыми вхоаами первого и второго элементов ИЛИ, с вторыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым информационными входами накапливающего сумматора.Коммутатор содержит группу элементов И, группу элементов ИЛИ, группу сумматоров но моаулю два и резистор, причем первый, второй и третий информационные входы коммутатора соединены соответственно с первым, вторым и третьим входами элементов ИЛИ группы, выходы которых соединены с Эиформационнрмивходами регистра, первый и второй выходы которого являются соответственно первым. и вторым управляюпами выкоаами коммутатора, группа ущавпяюшик входов коммутатора соединены с первыми входа-. ми элементов И группы, выходы которых соединены с пврвыми входами соотввтствуюшик сумматоров яо модулю два груп-:, пы, группа информационных выходов ре гистра, соответствующая кодам проввряемых логических условий, соеаинзиа с вторыми входами соответствующихэлементов и группы, выходы регистра, соответствующие модифицируемой части адре 84 бса, соединены" с вторыми входами соот ветствуюших сумматоров по моаулю два группы,. выходы сумматоров по модулю 1 два группы и выходы регистра, соответствующие нвмодифицирова иной части адреса, образуют группу выходов коммутатораьКроме того, блок управления сумма,тором содержит регистр, схему сравнвния, шифратор, дешифратор, первый, второй, третий и четвертый элементы И, груйту элементов И, счетчик, первый и второй элементы ИЛИ, причем вход конца опера ции первой группы входов соединен с первыми входами первого и второго эле. ментов И, а остальные группы входов блока соединены с соответствующими входами дешифратора, входы которого соединены с соответствующими входами шифратора, выходы шифратора соединены с первой группой входов схемы сравнения, выход которой соединен с вторыми входами первого и второго элементов И, вторая группа входов устройства соединена с входами регистра, выходы регистра соединены с второй группой входов схемы сравнения и первыми вхоаами соответствуюших элементов И группы, выходы которых образуют группу выкодов блока, выход первого элемента И соединен со счетным входом счетчика, вторыми входами элементов И группы и с первым входом первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход второго элемента И соединен с установочным входом счетчика и вторым входом первого элемента ИЛИ, выход третьего элемента И является первым выходом блока, группа, выходов счетчика соединена с соответствуклцими входами четвертого элемента и второго элемента ИЛИ, выходы которых являются соответственно вторым и третьим выходами блока. Сущность изобретения состоит в иовышвнии экономичности устройства путем, выделения коаов микрокоманд, содержащих нвинформативные части в младшик разря дах, хранения во втором блоке памяти старших разрядов этих кодов и управления их выдачей в наканливаюший сумматор.а также в повышении достоверности фуикаиоиирования путем проверки соответствия кода операции выполненной микропрограммы, признаком которой является остаточный дифференциал (коа) последней микрокоманды данной микропрограммы и повторного выполнения микро7 10153программы в соучае отрицатепьного исхода проверки,Таким образом, введение третьего -шестого блоков элементов И, одновибра.тора, первого и второго элементов ИЛИ Зи укаэанных связей лоэвопяет снизитьизбыточность бцоков памяти и повыситьдостоверность функционироюния устрой-ства.На фиг. 1 представпею функциоюньная схема прецпагаемого устройства нафиг. 2 - функциоюйьная схема комму татора; ю фиг. Э - функционапьная схема бпока управпения сумматором; на".фиг, 4 - структура формата микрокоманды, формируемой ю накаппивающем сум"маторе. .функциональная схема устройства(Фиг. 1) содержит третью группу элементов И 1, первый бпок 2 памяти, пя- Зфтую группу эпементов И 3, первую группу эпементов ИЛИ 4, выходы 5 микро.операций, первую группу эпементов,И 6,. дов, коммутатор 10, четвертую группуэпемеитов И 11, второй бпок 12 памяти, шервый 13 и второй 14 эпементыИЛИ, накаппивающий сумматор 15, шеотую группу элементов И 16, вторую Зйгруппу эпементов ИЛИ 17, бпок 18 управпения сумматором, первый 19 и второй 20 выходы устройства, генератор. 21 тактовых импульсов, одновибратор 22,На фиг. 2 показаны вторая группа 23 Звходов коммутатора, группа эпементовИЛИ 24, регистр 28,.первый 26, второй 27 выходы, четвертая группа входов28, первая группа входов 29, третьягруппа входов 30, груша эпементов И31, группа сумматоров 32,по модулю,два, группа выходов 33,На фиг, 3 обозначены вторая группавходов 34, регистр 38, схема 36 срав-нения, грушы.эпементов И 37, грушавыходов 38,.первая групю входов 39,дешифратор 40, шифратор 41, первый.эпемент И 42, второй элемент И 43,счетчик 44, второй эпемент ИЛИ 48,четвертый эпемент И 46, первый эцемент ИЛИ 47, третий эпемеит И 48,второй 49, третий 50 и первый 81 выходы бпока.На фнг. 4 испопьзуются спедующиеобозючеиияф Ж разряды микроопераИций; р. - разряды кода адреса приращения (цифференциапа) дпя формироюниаспедующей микрокоманды ,у 1 - спужебные разряды, используемые дпя фор 84 8мирования выходных сигналов на нервоми втором управпяющих выходах коммутатора 10 соответственно.Назначение основных функционаньныхэпементов устройства состоит в следующем,В блоках 2 и 12 памяти хранятсякоды микрокоманц, причем в первомбцоке 2 памяти записаны полные кодыапиной д, а во втором бпоке Ь 2 памяти - цоповннные коды макрокоманд,имеющих неинформативные старшие ипимладшие разряды.гНакапливающим сумматором 18 осуществпяется формирование кодов микрокоманд путем суммирования кода, попученного в предыцущем такте, с кодом(цифференциапом), считанным из бпоковпамяти в данном такыре,Первый 13 и второй 3.4 элементыИЛИ предназначены цпя формирования поснгюпам с первого и второго выходовпервого 2 или второго 12 бпоков памяъти сигналов управпения формированием всумматоре 18 служебных разрядов у уочередной микрокоманцы.Коммутатор 10 преднаэючен дпя ормирования адреса очередной микрокоман -ды и, в эавосимости от значения спужебного разряда предыдущей микрокомандыуф, выдачи этого адреса через третьюгруппу эпементов И 1 на вход первогоблоке 2 памяти при у 0, либо черезчетвертую группу эпементов И 11 навход второго бпока 12 памяти при у, 1.Пятая 3 и шестая 16 группы эпементов И предназначены дпла управпения записыо, считанной нз второго блока 12памяти информации пибо в старшие разряди сумматора 15 через первую группуэпементов ИЛИ 4 ( 2 фф 0)Либо В мпадшие разряды сумматора 18 через вторуюгруппу эпементов ИЛИ 17 (" 1).Первая 4 и вторая 17 группы элементовИЛИ цредназючены дпя передачи в сумматор 15 информации, считанной с первого бпока 2 памяти, либо с выходов соответственно пятой 3 и шестой 16 грудпэпементов И.Первая группа эпементов И 6 предназначена дпя управления выдачей сигюпов микроопераций ( а(1,0 Ыг свыходов сумматора 15 на выходы микроопераций 5 устройства.Вторая группа эпементов И 7 предназначена дпя управпения выдачей адресной,информации Ъ 1, ф 2, , ф и спужебныхЩжэюков у,иэ сумматора 15 накоммутатор 10,д,:(дд,д т где А - поле кода постоянной части ац 1реса;А - попе коца: моцнфицируемой чаоти адреса;А - попе кода проверяемого логичеокого условия;.ъ - спужебные (одноразрядные) приэО 1 Д 2яаки.Коммутатор в зависимости от содержимого поля А функционирует в двухрежимах.1) В поле А записан нупевой коц,2) В попе А З записан коц, отличныйот нуця,Первый режим соответствует работемикропрограммного устройства управле ния на пикейных участках микропрограмм:мы, а второй - в точках ее ветвления,В. первом режиме работы, независимоот значений сигналов погических успогийна третьей группе входов 30 коммутаторасигнапы на выходах блока элементовИ 31 отсутствуют.При этом на группе выходов 33 кодА, появляется непосредственно с выходовнемодифицируемой части адреса группы .выходов регистра 25, а код А с группывыходов моцифицируемой чрсти ацресагруппы выходов регистра 25 поступаетчерез группу сумматоров 32 по модупюдва на группу выходов модифицированнойчасти адреса группы выходов 33,Сигналы, соответствующие значениямслужебных признаков ., и у, с перво;го и второго выходов регистра 25 посту; пают соответственно на первый 26 ивторой 27 выходы,Во втором режиме работы коммутатор. 1,0 функционирует сцецующим.образом,Код А. формируется на выхоцах немоаифицируемой части адреса группы выходов 33 аналогично его формированиюв первом режиме.Код Апоступает иа первые вхоцыгруппы сумматоров 32 по модупю два.Код А з поступает на первые входыэлементов И группы эпементов И 31, навторые входы которых поступают погичеокие сигнапы с соответствующих входовтретьей группы входов 30 Х;Выходные сигналы блока элементовИ 31 поступают на входы второй группы 9 10153Бпок 18 управления сумматором предназначен цля формирования сигнала обну;, пения сумматора 15 поспе формированияустройством последней мнкрокоманды микропрограммы,а также для проверки соотвеь Зство реализованной микропрограммы зацанному коду операция и в случае отрицательного исхода проверки ( реапиэова ннаямикропрограмма не соответствует заданному коду операции) выдачи на выхоц 1 О устфройства сигнала блокировки и на четвертуюгруппу входов коммутатора 10 кода операции,а при возникновении устойчивого отказавыдачи сигнала отказа микропрограммного устройства управления на выход 20 1%устройства н на третьи входы эпементовИ группы элементов И 6 и 7.Генератор 21 тактовых импупьсов.предназначен дня формирования импульсов, управляющих выдачей операционной 20и адресной частей мнкрокоманцы с сумматора 15 соответственно через первую 6и вторую 7 группы эпементов И, и управляющих через одновнбратор 22 считыванием нэ первого 2 либо второго 12 блоков памяти кода дифференцнапа очередноймикрокома нцы,Назначение основных функционапьныхэлементов коммутатора 10 (фиг.2) состоит в следующем. 36Группа эпементов ИЛИ 24 предназначена для передачи адресной информации нана регистр 25 либо о первой 29, либо. со второй 23, либо с четвертой 28 группвходов коммутатора 10.3Регистр 25 предназначен для хранения немодифицирова нного адреса очередной микрокоманды, кода проверяемогологического условия и спужебных приэнаков г у предыдущей мнкрокома нды.Группа элементов И 31 предназначенадля формирования результатов проверкиногических усповий по значениям логических сигналов, поступающих на третыогруппу входов,30, коммутатора, и значе-ниям разрядов кода проверяемого логического условия, поступающего по выходамкоца, проверяемого логического условиягруппы выходов регистра 25.Группа сумматоров 32 по модулю двапредназначена дпя формирования по сигналам с выходов эпементов И группыэлементов И 31 и по коду модифицируемой части ацреса (моцифициро) и выдачиее на выходы модифицированной частиадреса группы выходов 33 коммутатора 10.Коммутатор 10 функционирует спецующим образом. 84 10На регистр 25 через группу эпементов ИЛИ 24 поступает иэ оцной иэ групп входов 23,28 и 29 код ацреса приращения для формирования очередной микроко- манды11 -1015384 12входов группы сумматоров 32.по модулю второго элемента И 43 появляетея сигдва, которые на своих выходах формируют нал, который поступает через первыйсигналы, соответствуюшие значениям ра элемент ИЛИ 47 и третий элемент.И 48рядов модифицированной части адреса и на первый 51 выход блока управления.выдают их на выходы модифицированной з По этому сигналу сумматор 15 обнучасти адреса группы выходов 33. ляется и микропрограммное устройствоНазначение основных функциональных управления переходит к формированиюэлементов блока 18 управления суммато мнкрокоманд следующей микропрограммыром (фиг. 3) состоит в следующем, но очередному коьу операции,Регистр 35,предназначен для хране . Если К .Р Ф К -, то сигнал появляетсяния в течение выполнения микропрограммы на выходе первого элемента И 42.кода операций КРПри этом в счетчик 44 записываетсяПоследовательно соединенные дешиф. еаиница, На выходе 49 появляется сигратор 40 и шифратор 41 осуществляют нал блокировки, по которому работа уппреобраэование остаточного кода сумма М равляемого объекта прекращается. Сигтора 15, который соответствует фактичес- налом с выхода 51 счвтчик 15 обнупяки реализованноймикропрограмме, в код ется, по первым входам открываютаяоперации КФэлементы И группы элементов И 48.Так как число кодов операции огра- Через него код операции поступает с реничено, то каждому коду операции можно.зо гистра 35 на выходы,группы выходов 38,взаимно однозначно сопоставить соответст-При этом микропрограммное устройся;вующие значения остаточного кода сумма- во управления снова выполняет микропро=-.тора 15 для каждой микропрограммы.грамму, соответствующую коду операции.,Схема 36 сравнения осуществляет В конце ее выполнения снова в схр-,сравнение кодов .КФ и К У. Группа эле З ме 36 сравнения осуществляется сравив-.-.ментов И 37 предназначена для управце- . ние КТР и К.с, Если К р= Кт, то с 1 ръния передачей кода К е регистра 35 налом с выхода второго элементаИ 43на выходы группы выходов 38. счетчик 44 обнуляется, сумматор 15 рбПервый 42 и второй 43 элементы И нуияется и микропрограммное устройств;предназначейы апя формирования сигнала Э управления переходит к выполнению спе.-",соответственно неправильного и правипь- дующей микропрограммыного формирования микропрограммным уст Если КТР И, то содержимое счет,-, -1 1ройством управпения микропрограммы по чика снова увеличивается на единицуа;,:,заданному коду операции. Первый элемент микропрограммное устройство управлеИЛИ 47 и третий элемент И 48 преаю- ния .функционирует аналогично функциоМзючеиы апя формирования сигнала обну- нированию зри первом возникновении сбоя,пения. накапливающего сумматора 15 и Если дооле заданного числа повтореиыаачи его на выход 51. ний выполнения микропрограммы, соответ:Четвертый элемент И 46 щедназначен,ствующей коду операции КФ, сбой недля формирования сигнала отказа микро- исчезает (что соответствует факту напрограммного устройства управления .и вы- пичия отказа в устройстве), то содердачи его на выход,.50, жимое счетчика становится равным заВторой элемент ИЛИ 45: преднаэючен данному числу повторений.для формирования сигнала блокировки ра- При этом ю выходе четвертого элеботы управляемого обьекта и выдачи его мента 46 появляется еигюп отказа,ю выход 49. . который закрывает по иэрвому входуБпсж 18 управления сумматором функ- - третий элемент И 48 (запрещая тем сационирует следующим образом. мым обнуление сумматора 15) и постуПосле вьцвпнвния последней микроко- пает ю выход 50 блока 18 управленияманды микропрограммы, заданной кодом . сумматором,операции, на входе конпа операции первой Микропрограммное устройство ущавЯгруппы входов 39 появляется:сигнал, оз пения работает следующим образом,крывающий по первому входу первый 42 После прихода кода операции ю пери второй 43 элементы И, Схема 36 срав- вую группу входов 9 устройства коммупения осуществляет сравнение заданного татор 10 формирует адрес первой миккода операци с выходов регистра 35 и фф рокоманды. Если дифференциал кода первеличиной К; с выходов шифратора 41. вбй микржоманаы имеет информативныеЕсли Кф = Кг, то на выходе схемы 36 младшие и старшие,разряды, то на мрсравнения, а следовательно, и на выходе вом выходе коммутатора 10 сигюп от-,программы путем повторного ее выполнения мнкропрограммным устройством управления, Если после выполнения последней мнкрокоманды микропрограммы сигнал с первого выхода блока 18 управления 3 обнуляет сумматор 15, сигнал на первом выходе 19 устройства исчезает и устройство переходит к выполнению следующей микропрограммы.Если К ФР то снова микропрограм- й мное устройстЬо управления. выполняет микропрограмму. Ест после заданного числа повторных выполюний мнкропрот . рвммыК У 4 К, то ю втором вывоцо 20 устройства с третьего выхода блока 18 управления сумматором появляется сиг нал отказа микропрограммного устройства управления,При атом элементы И группы алемен-: тов И 6 и 7. закрываются и мнкропрог- М раммное устройство управления прекращает работу до восстановления отказа. 84 16Предлагаемое устройство превосходитпрототип по достоверности функционирования, поскольку позволяет проверить соответствие полученного остаточного кода,а следовательно, и реализованной микрспрограммы, заданному коду операции,Существенно повышается экономичностьустройства путем хранэння во второмблоке памяти микрокоманд, содержащихненнформатнвные частн в младших разрядах,Повышается надежность устройства засчет упрощения его структуры.Повышается достоверность фушщионировання устройства путем проверки соотгветствия кода опарадии выполненной маропрограмме.Указанные преимущества предлагаемого устройства позволяют расширить Ьбпасть его целесообразного применения истроить более надежные микропрограммные устройства управления.

СмотретьЗаявка

3360625, 05.12.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, СКОРИК ВЛАДИМИР ВАСИЛЬЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 30.04.1983

Код ссылки

<a href="https://patents.su/10-1015384-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство контроля

Случайный патент: Способ управления двухконтурным устройством принудительной коммутации тиристорного преобразователя