Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

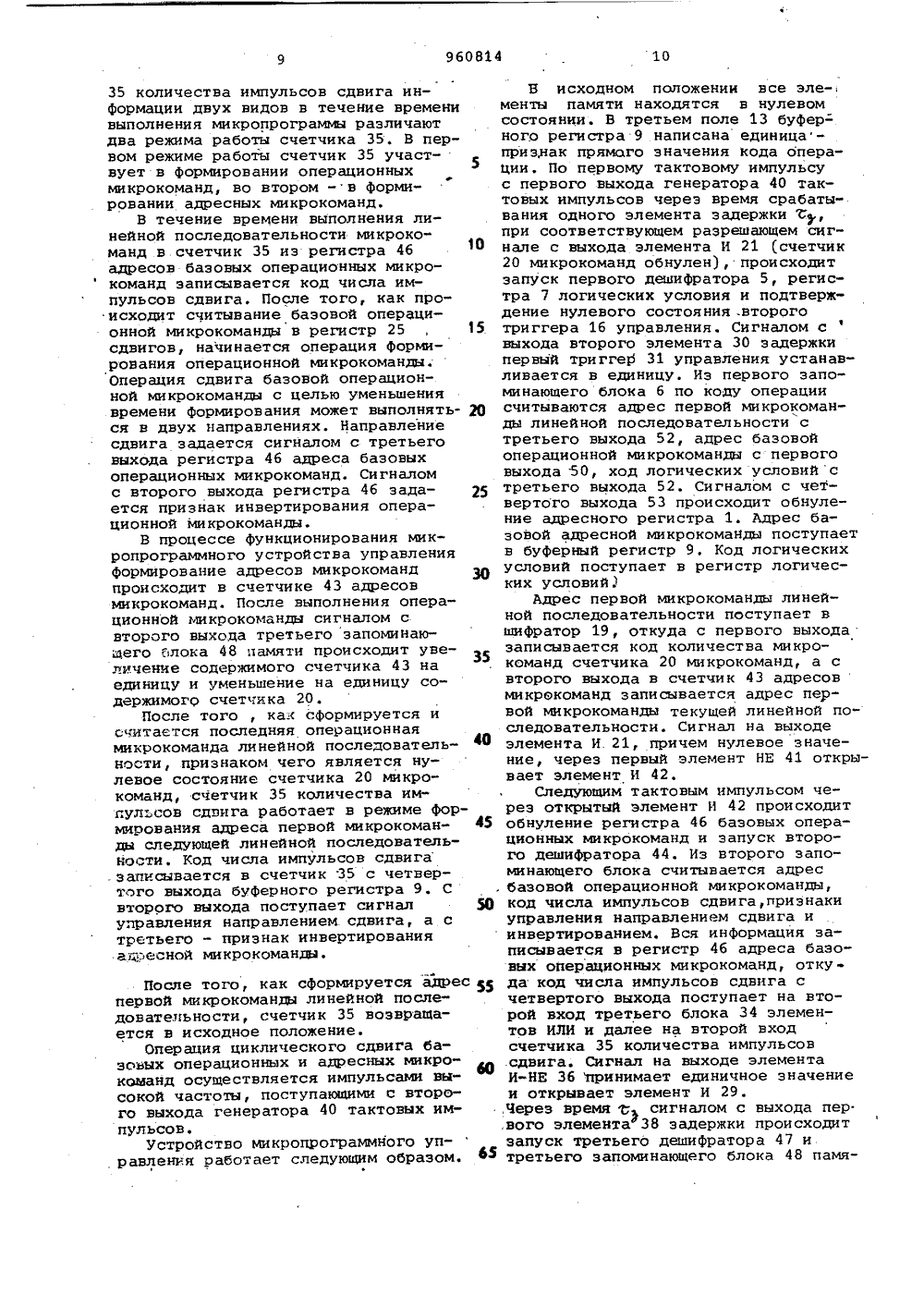

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеса убпик 1 ц 960814(61) Дополнительное к авт. свид-ву(22) Заявлено 08.12. 80 (21 3214761/18-24 51.М. Кл.з С 06 Е 9/22 с присоединением заявки Но -Государственный комитет СССР по делам изобретений и открытий(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ Изобретение относится к цифровойвычислительной технике и может бытьиспользовано в качестве устройствауправления ЭВМ с микропрограммнымпринципом управления,Известно устройство микропрограммного управления, содержащее запоминающие блоки для хранения адресных иоперационных микрокоманд, буферныйрегистр, регистр адреса и регистрлогических условий, счетчики количества микрокоманд и адресов микрокоманд, шифратор, дешифраторы, триггеруправления, лЬгические элементы И,И-НЕ, НЕ, элементы задержки и генератор тактовых импульсов 1.Недостатком указанных устройствявляется низкая экономичность, обусловленная большой избыточностью запоминающих блоков.Наиболее близким к изобретению потехнической сущности является устройство микропрограммного управления,содержащее последовательно соединенные первый дешифратор, первый запоминающий блок, буферный регистр, второйвход которого соединен с выходом первого блока элементов И, а первый выход через второй блок элементов Исоединен с первым входом регистра сдвига базовой адресной микрокоманды,второй вход которого является входомкода операции устройства, вход логических условий которого соединен спервым входом первого блока элементов И, второй вход которого соединенс выходом регистра логических условий,первый вход которого соединен с вторым выходом первого запоминающего блока, третий выход которого через шифратор соединен с первым входом счетчика количества микрокоманд, второй выход шифратора соединен с первым входом счетчика адреса микрокоманд,выход которого через второй дешифратор, второй запоминающий блок, регистр адреса базовых операционныхмикрокоманд, третий дешифратор и третий запоминающий блок соединен сосчетными входами счетчика адреса микрокомацд и счетчика количества микрокоманд, вцходы которого через первыйэлемент Й соединены с первыми входами второго ,. третьего, а через первый 25 элемент НЕ - четвертого элемента И,выход которого соединен с вторымвходом дешифратора и входом установкив нуль регистра адреса. базовой операционной микрокоманды, а второй вхоп ЗО четвертого элемента И соединен спервым выходом генератора тактовых импульсов, а через первый элемент задержки - с входом установки в нуль регистра сдвига базовых операционных микрокоманд, вторыми входами третьего дешифратора и. третьего эле мента И и входом второго элемента задержки, выход которого соединен с единичным выходом первого триггера управления и вторым входом первого элемента И, выход которого соединен О с вторым входом второго блока элементов И, выход третьего элемента И соединен с входами установки в нуль буферйого регистра, регистра логических .условий, счетчика адреса 15 микрокоманд и вторым входом первого дешиФратора, нулевой выход первого триггера управления соединен с первым входом третьего блока элементов И, второй вход которого соединен с выходом регистра сдвига базовых операционных микрокоманд, первый вход которого соединен с вторым выходом третьего запоминающего блока, второй выход генератора тактовых импульсов соединен с вторым входом пятого элемента И, выход которого соединен с первым входом шестого .элемента И и со счетным входом счетчика импульсов количества сдвига, выходы котороГо через элемент И-ЙЕсоединены с вторым входом шестого элемента И, а через второй элемент НЕ - с нулевым входом первого триггера управления, четвертый выход первого запоминающего блока соединен с тре тьим входом регистра сдвига базовых адресных микрокоманд2 .К недостатку устройства относится , большое время формирования операционных микрокоманд путем циклического 40 сдвига базовых операционных микроЭкоманд в одном направлении.Выполнение операции циклического сдвига базовой операционной микро- команды в одном направлении приводит к увеличению времени формирования операционных микрокоманд, а следовательно определяет повышенные требования к работе генератора тактовых импульсов.50Целью изобретения является повышение быстродействия.Поставленная цель достигается тем, что в устройство микропрограммного 1 правления с базовыми множествами микрокоманд, содержащее последовательно соединенные первый дешифратор, первый запоминающий блок, буФерный регистр, второй вход которого . соединен с выходом первого блока элементов И, а первый выход через второй блок элементов И соединен с первым входом регистра сдвига базовой адресной микрокоманды, второй вход кОторого является входом кода операции устройства, вход логических уеловий которого соединен с первым входом первого блока элементов И, вто-рой вход которого соединен с выходом регистра логических условий, первый вход которого соединен с вторым выходом первого запоминающего блока, третий выход которого через шифратор соединен с первым входом счетчика количества микрокоманд, второй выход шифратора соединен с первым входом счетчика адреса микрокоманд, выход которого через второй дешифратор, второй запоминающий регистр адреса базовых операционных микрокоманд, третий дешифратор и третий запоминающий блок соединен со счетными выходами счетчика адреса микрокоманд и счетчика количествакрокоманд, выходы которого через первый элемент И соединены с первыми входами второго, третьего, а через первый элемент ЙЕ - четвертого элемента И, выход которого соединен с вторым входом дешифратора и входом установки в нуль регистра адреса базовой операционной микрокоманды, а второй вход четвертого элемента И соединен с первым выходом генератора тактовых импульсов, а через первыйэлемент задержки - с входом установкив нуль регистра сдвига базовых операционных микрокоманд,вторыми входами третьего дешифратора и третьего элемента И и входом второго элемента задержкивыход которого соединен с единичнымвыходом первого триггера управленияи вторым входом первого элемента И,выход которого соединен с вторымвходом второго блока элементов И, выход третьего элемента И соединен с входами установки в нуль. буферного регистра, регистра логических условий, счетчика адреса микрокоманд и .вторым входом первого дешифратора, нулевой выход первого триггера управления соединен с первым входом третьего блока элементов И, второй вход которого соеднинен с выходом регистра сдвига базовых операционных микрокоманд, первый вход которого соединен с вторым выходом третьего запоминающего блока, второй выход генератора тактовых импульсов соединен с вторым входом пятого элемента И, выход которого соедийен с первым входом шестого элемента И исо счетным входом счетчика импульсов количества сдвига, выходы которого через элемент И-НЕ соединены с вторым входом шестого элемента И, а через второй элементНЕ - с нулевым входом первого триггера управления, четвертый выход первого запоминающего блока соединен с третьимвыходом регистра сдвига базовых адресных микрокоманд, дополнительно введены три блока элементов ИЛИ, четыре блока элементов И, четыре элемента И,(адВА год АВторой этап оптимизации первого 50 запоминающего блока аналогичен оптимизации третьего запоминающего блокаи состоит в том, что из множествабазовых адресных (операционных) микрокоманд (16 А Щ 6 ) формируется укоро ченное множество базовых адресных(ОперацИОННЫХ) МИКрОКОМанд 06 д (Ябо ) га. Ме ЦУ множестваЪАИ 06 А ЩОБИЦ ) существует зависимостьпоскольку функцией отображения мноЖесТва Бд ОБ) На МНожесТвО (16 А ОБ )является операция инвертирования.На чертеже представлена Функциональная блок-схема устройства микропрограммного управления .с базовыми И множествами микрокоманд. элемент ИЛИ и второй триггер управления, причем первый вход первого блока элементов ИЛИ соединен с выходом третьего блока элементов И, выход первого элемента ИЛИ является выходом микроопераций устройства, а второй вход соединен с выходом четвертого блока элементов И, первый вход которого соединен с первым входом тфетьего блока элементов И, второй вход - с вторым выходом регистра сдвига базовых Операционных микро- команд, а третий вход - с третьим входом третьего блока элементов И и с вторым выходом регистра адреса базовых операционных микрокоманд, третий выход которого соединен с инверсным входом седьмого и первым входом восьмого элементов И, выходы которых соединены соответственно с вторым и третьим входами регистра сдвига базовых операционных микрокоманд, а вторые входы соединены с выходом шестого элемента И и с первыми входами девятого и десятого элементов И, выходы которых соединены соответственно с четвертым и пятым входами регистра сдвига базовых адресных микрокоманд,а вторые входы соединены с вторым выходом буферного регистра, третий выход которого соединен с первыми входами пятого и шестого . блоков элементов И, вторые входы которых соединены с первым и вторым выходом регистра сдвига базовых адресных микрокоманд соответственно, а выходы - с гервым и вторым входами второго блока элементов ИЛИ, выход которого соединен с вторым входом первого дешифратора, четвертый выход буферного регистра соединен с первым входом седьмого блока элементов И, второй вход которого соединен с выходом второго элемента НЕ, третийвход - с единичным выходом второго триггера управления и первым входом элемента ИЛИ, второй вход которого соединен с единичным выходом первого триггера управления, а выход - с первым вхо" дом пятого элемента И,единичный вход второго триггера управления соединен с выходом четвертого элемента И, вы- ход седьмого блока ЭЛементов И соединен с первы м входом третьего блока элементов ИЛИ, второй вход которого соединен с четвертым выходом регистра адреса базовых операционныхмикрокоманд,а выход - с первым вхо дом счетчика количества импульсов сдвиСущность изобретения состоит в повышении быстродействия и экономичности устройства микропрограммного управления за счет Формирования адресных и операционных микрокоманд, входящих в реализуем(е микропрограммы из множества базовых адресных и операционных микрокоцанд, записанных в первый и третий запоминающие блоки, путем выполнения операций инвертирования и реверсивного сдвига.Оптимизация первого запоминающего блока состоит из двух этапов и заключается в там, что на первом этапе из всего множества адресных микрокоманд Я, = ц , (Ъ= 1,й, где к - количество линейных последова. тельностей, входящих в реализуемыемикропрограмия), формируется некото рое множество базовых адресных микБ(6 со рокоманд Я = с(. Между множествами Яд и Ябд существует отношение С(.Од Ябд (о(-(и (1 д,- которое сле дует из того, что функцией отображения (о множествана множестве с, является функция циклического сдвига каждого элемента множества Оо на заданное число разрядов Ъ. Из каждо го элемента с( СО может быть получено по крайней мере МОэлементов множества (1 д.Так, например, для того чтобы задать множество адресных микрокоманд 25 (д =оооо, ооо 1, оо 1 о, оо 11, о 1 оо, 0110достаточно задать множествобазовых адресных микрокоманд Я0000, 0001,0011.При этОм коды из мнОжества Я 6 А отображаются на множестве (1 слеА дующим образом оооо ь = о оооо 0001 ЬУстройство содержит регистр 1сдвига базовых адерсных микрокоманд,пятый и шестой блоки 2 и 3 элементовИ, второй блок 4 элементов ИЛИ, первый дешифратор 5, первый блок б памяти, регистр 7 логических условий,первый блок 8 элементов И, буферныйрегистр 9, имеющий четыре поля: поле10 задания базового адреса, поле 11задания числа сдвигов, поле 12 признака направления сдвига, поле 13признака инвертирования адресноймикракоманды, второй блок 14 элементов И, седьмой блок 15 элементов И,второй триггер 16 управления, десятый и девятый элементы И 17 и 18 15соответственно,шифратор 19, счетчик20 колйчества микрокоманд, первыйэлемент И 21, второй элемент И 22,шестой элемент И 23, восьмой элементИ 24, регистр 25 сдвига базовых операОционных микрокоманд, третий, четвертый блоки элементов И 26 и 27 соответственно, первый блок 28 элементовИЛИ, седьмой элемент И 29, второйэлемент 30 задержки, первый триггер 2531 управления, элемент ИЛИ 32, пятый элемент И 33, третий блок 34элементов ИЛИ, счЕтчик 35 количестваимпульсов сдвига, элемент И-НЕ 36,второй элемент НЕ 37, первый элемент ЗО38 задержки, третий элемент И 39,генератор 40 тактовых импульсов, первый элемент НЕ 41 и четвертый эле.мент И 42, счетчик 43 адреса микрокоманды второй дешифратор 44, второй блок памяти 45, регистр 46 адреса базовых операционных микрокоманд,третий дешифратор 47, ту етий блок48 памяти, вход 49 кода операций регистра сдвига базовых адресных микрокоманд, первый, третий, второй и46четвертый выходы -50-53 первого запоминающего блока, вход 54 значенийлогических условий, выход 55 микроопераций устройстваВ первом запоминающем блоке б 45памяти хранятся базовые адресныемикрокоманды.Первый выход 50 первого запоминающего блока б предназначен для записи базовых адресных микрокоманд 5 Ов буферный регистр 9,Первое поле 10 буферного регистра 9 предназначено для хранениябазовой адресной микрокоманды, второе виоле 12 представляет собой поле 55метки, в котором записывается единичное зчачение сигнала, если адрес микрокоманды, считываемой из первого запоминающего блока б, записанный в ре;истр 1 сдвига базовых адресных микрокоманд 1, используетсяв прямом виде, и значение нуля - если в инверсном виде. Третье поле 13представляет собой пбле метки, значе-,ние которой равно единице, если сдвигбазовой операционной микрокоманды необходимо осуществлять в сторонустарших разрядов, и нулю, когда сдвигнеобходимо осуществлять в сторонумладших разрядов.Регистр 1 сдвига базовых адрес-ных микрокоманд предназначен дляосуществления операции циклическогосдвига и является реверсивным. Регистр 7 логических условий осуществляет хранение кода - логических условий в течение времени выполнениятекущей линейной последовательностис целью модификации адреса первоймикрокоманды очередной линейной последовательности по результатам проверки значений соответствующих логических условийШиФратор 19 предназначен для формирования кода адреса первой микрокоманды и кода микрокоманд в последовательности. Счетчик 20 микрокомандпредназначен для счета числа выполненных микрокоманд по сигналам считывания микрокоманд из третьего запоминающего блока 48 памяти. Первый ивторой триггеры 31 и 16 управления, аа также счетчик 35 количества импульсов сдвига образуют узел управлениявыполнением операций циклическогосдвига. Регистр 25 сдвига базовыхоперационных микрокоманд является реверсивным и служит для формированияоперационных микрокоманд,Генератор 40 тактовых импульсов иимеет два выхода, первый из которыхпредназначен для тактирования работыустройства микропрограммного управления импульсами с частотой следования Е, а второй выход - для осуществления операций сдвигов импульсами счастотой следования Г, причем ЕК, -Во втором запоминающем блоке 45 памяти.хранятся адреса базовых операционных микрокоманд,Регистр 46 адреса базовых операционных микрокоманд имеет четыре выхода: по первому выходу считываетсяадрес базовой операционной микрокоманды, по второму - сигнал управления инвертированием базовой операционной)микрокоманды, по третьему - сигналуправления направлением сдвига базовой операционной микрокоманды, почетвертому - код числа импульсовсдвига.В третьем запоминающем блоке 48памяти хранятся базовые операционные микрокоманды, составляющие неполное множество базовых операционных микрокоманд.В счетчик 35 количества импульсовсдвига записывается информация околичестве импульсов сдвига, необходииах для формирования операционныхмикрокоманд, а также информация околичестве импульсов сдвига, необходижх для формирования адресных микрокоманд. В связи с записью в счетчик35 количества импульсов сдвига информации двух видов в течение времени выполнения микропрограммы различают два режима работы счетчика 35. В первом режиме работы счетчик 35 участвует в формировании операционных микрокоманд, во втором - в формировании адресных микрокоманд.В течение времени выполнения линейной последовательности микрокоманд в счетчик 35 из регистра 46 адресов базовых операционных микро- команд записывается код числа импульсов сдвига. После того, как происходит считывание базовой операционной микрокоманды в регистр 25 , 15 сдвигов, начинается операция формирования операционной микрокоманды. Операция сдвига базовой операционной микрокоманды с целью уменьшения времени Формирования может выполнять ся в двух направлениях. Направление сдвига задается сигналом с третьего выхода регистра 46 адреса базовых операционных микрокоманд. Сигналом с второго выхода регистра 46 зада ется признак инвертирования операционной микрокоманды.В процессе функционирования микропрограммного устройства управления Формирование адресов микрокоманд 30 происходит в счетчике 43 адресов микрокоманд. После выполнения операционной микрокоманды сигналом с второго выхоца третьего запоминающего блока 48 памяти происходит увеличение содержимого счетчика 43 на единицу и уменьшение на единицу содержимого счетчика 20.После того , ка. сформируется и считается последняя операционная микрокоманда линейной последователь ности, признаком чего является нулевое состояние счетчика 20 микро- команд, счетчик 35 количества импульсов сдвига работает в режиме форжрования адреса первой микрокоман ды следующей линейной последовательности. Код числа импульсов сдвига . записывается в счетчик 35 с четвертого выхода буферного регистра 9. С второго выхода поступает сигнал 50 управления направлением сдвига, а с третьего - признак инвертирования а;Ресной микрокоманды. После того как сформируется адрес 55 первой микрокоманды линейной последовательности, счетчик 35 возвращается в исходное положение.Операция циклического сдвига базовых операционных и адресных микро- команд осуществляется импульсами высокой частоты, поступающими с второго выхода генератора 40 тактовых импульсов.Устройство микропрограммного управления работает следующим образом. ф 5 В исходном положении все эле-, менты памяти находятся в нулевом состоянии. В третьем поле 13 буфер= ного регистра 9 написана единица- признак прямого значения кода операции, По первому тактовому импульсу с первого выхода генератора 40 тактовых импульсов через время срабатывания одного элемента задержки :, при соответствующем разрешающем сигнале с выхода элемента И 21 (счетчик 20 микрокоманд обнулен), происходит запуск первого дешифратора 5, регистра 7 логических условия и подтверждение нулевого состояния .второго триггера 16 управления. Сигналом с выхода второго элемента 30 задержки первый триггер 31 управления устанавливается в единицу. Из первого запоминающего блока 6 по коду операции считываются адрес первой микрокоманды линейной последовательности с третьего выхода 52, адрес базовой операционной микрокоманды с первого выхода 50, ход логических условий с третьего выхода 52. Сигналом с чет- вертого выхода 53 происходит обнуление адресного регистра 1. Адрес базовой адресной микрокоманды поступает в буферный регистр 9, Код логических условий поступает в регистр логических условий 1Адрес первой микрокоманды линейной последовательности поступает в шифратор 19, откуда с первого выхода записывается код количества микро- команд счетчика 20 микрокоманд, а с второго выхода в счетчик 43 адресов микрокоманд записывается адрес первой ьжкрокоманды текущей линейной последовательности. Сигнал на выходе элемента И. 21, причем нулевое значение, через первый элемент НЕ 41 открывает элемент И 42.Следующим тактовым импульсом через открытый элемент И 42 происходит обнуление регистра 46 базовых операционных микрокоманд и запуск второго дешифратора 44. Из второго запоминающего блока считывается адрес базовой операционной микрокоманды, код числа импульсов сдвига, признаки управления направлением сдвига и инвертированием. Вся информация записывается в регистр 46 адреса базовых операционных микрокоманд, откуда код числа импульсов сдвига с четвертого выхода поступает на второй вход третьего блока 34 элементов ИЛИ и далее на второй вход счетчика 35 количества импульсов сдвига, Сигнал на выходе элемента ИНЕ 36 принимает единичное значение и открывает элемент И 29.Через времясигналом с выхода пер. вого элемента 38 задержки происходит запуск третьего дешифратора 47 и третьего запоминающего блока 48 памя 960814ти. С первого выхода сосчитывается код базовой операционной микрокоманды и записывается в регистр 25 сдвига. Сигналом с второго выхода происходит формирование адреса очередной микрокоманды линейной последователь- ности. путем увеличения на единицу содержимого счетчика 43 адресаСодержимое счетчика 20 микрокоманд уменьшается на единицу тем же сигналом. 10После того, как запишется код базовой операционной микрокоманды в регистр 25, тактовые импульсы высокой частоты с второго выхода генератора 40 тактовых импульсов через 15 открытый пятый элемент И 33 поступают на счетный вход счетчика 35 и на второй вход шестого элемента И 23, с выхода которого они поступают на вторые входы седьмого и восьмого 20 элементов И 29 и 24 соответственно, На первые входы этих элементов поступает сигнал управления с четвертого выхода регистра 46 адреса базовых операционных микрокоманд, 25В момент обнуления счетчика 35 сигнал на выходе элемента И-НЕ 36 равен нулю. Он закрывает шестой элемент И 23, а также через второй элемент НЕ 37 производит установку в нуль первого триггера 31 управления. Нулевой сигнал с выхода триггера 31 поступает на первые входы третьего и четвертого блоков элеменрв И 26- 27 соответственно. На второй вход третьего блока элементов И 26 поступают прямые значения разрядов кода операционной микрокоманды, а на второй,вход четвертого блока элементов И 27 - обратные их значения.40В зависимости от значения управляющего сигнала с второго выходарегистра 46 адреса базовых операционных микрокоманд происходит считывание прямого или инверсного кода операционной микрокоманды из регистра 25. Код операционной микрокоманды поступает на один из входов первого блока 28 элементов ИЛИ, выход которого является выходом устройства.50Через время С сигналом с выхода второго элемента 30 задержки происходит установка в единицу первого триггера 31 управления, Единичный сигнал с единичного выхода триггера 31 поступает через элемен ИЛИ 32 и открывает пятый элемент И 33. Очередным тактовым импульсом с первого выхода генератора 40 тактовых импульсов через открытый элемент И 42 происходит обнуление регистра 46 адреса ф базовых операционных микрокоманд и запуск второго дешифратора 44, В дальнейшем работа устройства микропрограммного управления аналогична описанной. 63 После того, как сосчитается последняя операционная микрокоманда линейной последовательности тактовым импульсом с выхода элемента И 22 происходит передача кода базовой адресной микрокоманды с первого выхода регистра 9 через второй блок 14 элементов И в регистр 1 сдвига базовых адресных микрокоманд. Этим же сигнатом второй триггер 16 управления устанавливается в единичное состояние. Сигналом с единичного выхода триггера 16 элемент И 33 открывается, и происходит запись кода числа сдвигов базовой адресной микрокоманды через седьмой блок 15 элементов И и третий блок 34 элементов ИЛИ в счетчик 35 количества импульсов сдвига. В результате на выходе элемента И-НЕ 36 появляется единичный сигнал, который поступает на второй нход шестого элемента И 23 и открывает его.Импульсы высокой частоты с второго выхода генератора 40 тактоных имимпульсов поступают на счетный вход счетчика 35 количества импульсов сдвига, а также через шестой элемент И 23 - на первые входы девятого и десятого элементов И 18 и 17 соответ,ственно. Кроме того, импульсы высо,кой частоты с выхода шестого элемента И 23 поступают на вторые входы элементов И 24 и 29, в результате чего производится циклический сдвиг нулевого кода регистра 25.На вторые входы девятого и десятого элементов И 18 и 17 поступает сигнал управления направлением сдвига с второго выхода регистра 9.После того, как заканчивается операция сдвига базовой адресной микро- команды в регистре 1, состояние счетчика 35 количества импульсов сдвига становится нулевым, происходит обнуление первого триггера 31 управления и единичный сигнал с его нулевого выхода поступает на первые входы третьего 26 и четвертого 27 блоков элементов И, а также на третьи.нходы пятого 2 и шестого 3 блоков элементов И.Поскольку в регистре 25 записан нулевой код, то считывание информации из него не происходит.В зависимости от значения сигнала, поступающего с третьего выхода регистра 9, по коду (прямому или инверсному) адреса первой микрокоманды линейной последовательности через первый или второй входы второго блока элементов ИЛИ по сигналу с выхода элемента И 39 происходит считывание адреса первой микрокоманды линейной последовательности из первого запоминающего блока 6, В дальнейшем работа схема повторяется, 9 б 0814 14Объем запоминающих блоков предлагаемого устройства микропрограммного управления оценивается выражениемФ й Ь р +М +Мд И)+ЙВ)ЦЙ ф%2.ф 60 460 М 60где М М, - разрядности базовых адресных и операционных микрокоманд;М - число базовых операцибоонных микрокоманд.Из сравнения величин И, и Мя следует, чтоАИ = И - ХО 70 Утак какМ М, М М, М (Х1Следовательно, предлагаемое устройство превосходит известное.по быстродействию и экономичности и,позволяет строить устройства с меныйим объемом запоминающих блоков.формула изобретенияУстройство микропрограммного управления,содержащее первый дешифра.тор, выход которого подключен к входу первого блока памяти, выход адреса базовой операционной микрокоманды которого подключен к входу базового адреса буферного регистра, вход логических условий которого подключен к выходу первого блока элементов И, выход поля задания базового адреса буферного регистра соединен с первым входом второго блока элементов И, выход которого подключен к первому входу регистра сдвига базовой адресной микрокоманды, второй вход которого подключен к входу кода операции устройства, первый вход первого блока элементов И соединен с входом логических условий устройства, а второй вход подключен к выходу регистра логических условий, первый вход которого соединен с выходом кода логических условий первого блока памяти, выход адреса первой микрокомандя которого подключен к входу шифратора, первый выход которого соединен с информационным входом счетчика количества микрокоманд, а второй выход - с информационным входом счетчика адреса микрокоманд, выход которого подключен к первому входу второго дешифратора, выход которого соединен со вторым блоком памяти, выход которого подключен к информационному входу регистра адреса базовых операционных микрокоманд, первый выход которого подключен к первому входу третьего дешифратора, выход которого соединен со входом третьего блока памяти, первый выход которого соединен со счетным входом счетчика адреса микрокоманд и счетчика коли-.чества микрокоманд, выходы которого подключены ко входам первого элемента И, выход которого соединен с первым входом второго элемента И, третьего элемента И и через первый элемент НЕ с первым входом четвертого элемента И, выход которого подключен ко вто рому входу второго дешифратора ивходу установки в нуль регистра ад реса базовой операционной микрокоманды, второй вход четвертого элемента И соединен с первым выходом генерато ра тактовых импульсов и через первыйэлемент задержки - со входом установки в нуль регистра сдвига базовых операционных микрокоманд, со вторым входом третьего дешифратора, со вторым входом третьего элемента И и,входом второго элемента задержки, выход которого соединен с единичным выходом первого триггера управления и вторым входом первого элемента И, выход кото рого соединен со вторым входом второго блока элементов И, выход третьего элемента И соединен со входом установки в нуль буферного регистра, регистра логических условий, счетчика адреса микрокоманд и вторым входом первого дешифратора, нулевой выход первого триггера управления соединен с первым входом третьего блока элементов И, второй вход которого соединен с выходом регистра сдвиЗ 5 га базовых операционных микрокоманд,первый вход которого соединен со вторым выходом третьего блока памяти, второй выход генератора тактовых импульсов соединен со вторым входом 40 пятого элемента И, выход которогосоединен с первым входом шестого элемента И и со счетным входом счетчика импульсов количества сдвига, выходы которого через элементы И-НЕ со единены со вторым входом шестого элемента И, а через второй элемент НЕ - со входом нуля первого триггера управления, выхо д обнуления первого блока памяти подключен к третьему 5 О входу регистра сдвига базовых адресных микрокоманд, о т л и ч а ю щ е - е с я тем, что, с целью повышения быстродействия, в него дополнительно введены три блока элементов ИЛИ, четыре блока элементов И, четыре элемента И, элемент ИЛИ и второй триггер управления, причем первый вход первого блока элементов ИЛИ соединен с выходом третьего блока элементов И, выход первого элемента ИЛИ является выходом микроопераций устройства, а второй вход соединен с выходом четвертого блока элементов И, первый вход которого подключен к первому входу третьего блока элементов И, второй И вход - к второму выходу регистра.сдвига базовых операционных микрокоманд, а третий вход - к третьему входутретьего блока элементов И и к второму выходу регистра адреса фазовыхоперационных микрокоманд, третий выход которого соединен с инверсным 5входом седьмого и первым входом восьмого элементов И, выходы которых соединены соответственно с вторым и третьим входами регистра сдвига базовыхоперационных микрокоманд, а вторые 19входы соединены с выходом шестого элемента И и с первыми входами девятогои деСятого элементов И, выходы которых соединены соответственно с четвертим и пятым входами регистра сдви-га базовых адресных микрокоманд, авторые входы соединены с вторым выходом буферного регистра, третий выход которого соединен с первыми входами пятого и шестого блоков элементов И, вторые входы которых соединены с первым и вторым выходом регистра сдвига базовых адресных микрокоманд соответственно, а выходы - с первым и вторым входами второго блокаэлементов ИЛИ, выход которого соединен с вторым входом первого дешифратора, четвертый выход буферного регистра соединен с первым входом седьмого блока элементов И, второй вход которого соединен с выходом второго элемента НЕ, третий вход - с единичным выходом второго триггера управления и первым входом элемента ИЛИ, второй вход которого соединен с единичным выходом первого триггера управления, а выход - с первым входом пятого элемента И, единичный вход второго триггера управления соединен с выХодом четвертого элемента И, выход седьмого блока элементов И соединен с первым входом третьего блока элементов ИЛИ, второй вход которого соединен с четвертым выходом регистра адреса базовых операционных микро- команд, а выход - с первым входом счетчика количества импульсов сдвига.Источники информации,принятые во внимание при экспертизеЙ;-.- Авторское свидетельство СССРР 763898, кл.С 06 Р 9/22, 1978,. Авторское свидетельство СССРпо заявке Р 2915890/18-24,кл.6 06 Р 9/22, 1980 прототип).

СмотретьЗаявка

3214761, 08.12.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.09.1982

Код ссылки

<a href="https://patents.su/9-960814-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Интегро-дифференциальный вычислитель

Следующий патент: Устройство микропрограммного управления

Случайный патент: Масса для изготовления алмазного инструмента