Микропрограмный процессор с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

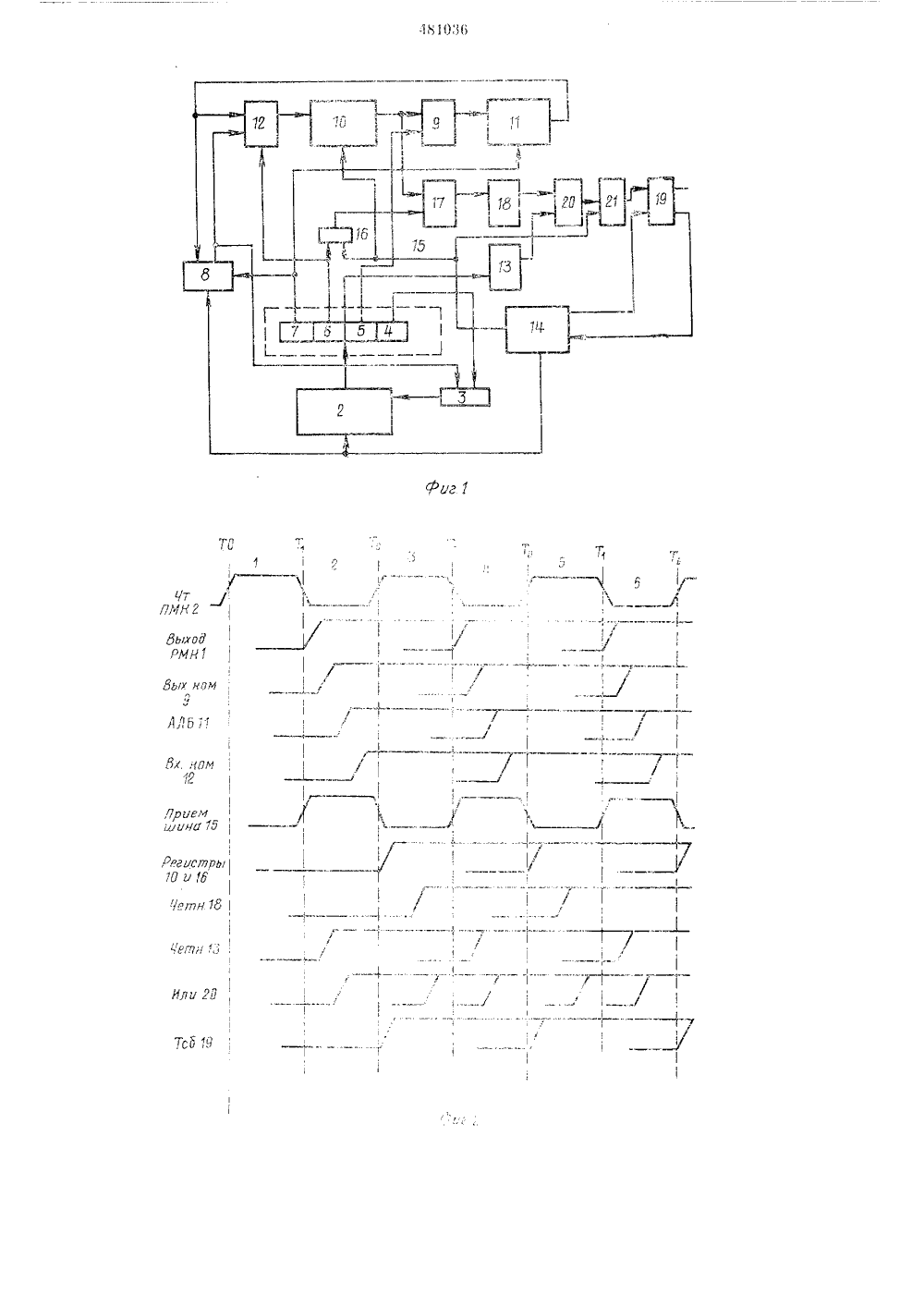

е , .,г ОПИСАНИЕ ИЗОБРЕТЕНИЯ пп 48 О 36 Союз Советских Социалистических Республик(51) М,исоединением заявки Ме Государственный комите Совета Министров СССР по делам изобретенийи открытий 3) Приоритет убликовано 15.08,75. ллстець Л. 3пя 05.01.76(54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР С КОНТРОЛ Изобретение относится к вычислительной технике и, в частности, к проектированшо процессоров с контролем.Известны микропрограммные процессоры с контролем, содержащие блок памяти микро- команд, регистр адреса, регистр микрокоманд первый узел контроля на четность, арифметико-логический блок, блок регистров, входной и выходной коммутаторы, блок сопряжения с оперативной памятью и блок синхро. низации. Первый вход блока памяти микро- команд соединен с выходом регистра адреса, первый вход которого соединен с первым выходом регистра микрокоманд, вход которого соединен с выходом олока памяти мцкрокоманд, второй вход которого соединен с первым выходом блока синхронизации и с первым входом блока сопряжения с оперативной памятью, выход которого соединен со вторым входом регистра адреса и с первым входом входного коммутатора, выход которого соединен с первым входом блока регистров, второй вход которого соединен шиной синхронизации приема со вторым выходом блока синхронизации, а выход соединен с первым входом выходного коммутатора, выход которого соединен с первым входом арифметикологического блока, выход которого соединен со вторыми входами входного коммутатора и блока сопряжения с оперативной памятью,третий вхол которого соединен со вторым входом арцфметцко-логического блока ц со вторым выходом регистра мцкрокоманд, третий выход которого соединен с третьим входом 5 входного коммутатора. Четвертый выход регистра микрокомацл соединен со вторым вхолом выходного коммутатора, а пятый выход соединен со вхолом первого узла контроля на четцость.1 о Целью цзобрстения является увеличениебыстродействия процессора.Поставленная цель достигается тем, чтопроцессор дополнительно содержит дополнительный регистр, контрольньй коммутатор, 15 второй узел контроля на четность, элементыИЛИ, И, триггер фиксации сбоя, Первый виол дополнительного регистра соединен с третьим выходом регистра микрокоманд, а выход соединен с первым входом контрольно го коммутора, второй вход которого соединенс выходом блока регистров. а выход - со входом второго узла контроля ца четцость, выход которого соединен с первым входом элемецта ИЛИ, второй вход которого соединен с 25 выходом первого узла контроля на четность,а выход соединен с первым входом элемента И, выход которого соединен со входом установки в единицу триггера фиксации сбоя, вход гашения которого соединен с третьим ЗО выходом блока синхронизации, нулевой выход(ро 3 10) 1)т)ц;СПК - )01,т ( С 1)т о сЦ Ь 1 С т Ц:( Р т ): )т.т Ц:1:) Ц Р Ц С;т: Ы(:ЬЦ .Л 1: И Тт:Ц Ь трГН(. р 1 тк рт Пыл 1: к ): )1".: Г(,), БРОЙ ) зс,. 1.0)1, тцтБ (,1 с;,1)НГ.1 ТОРОМ д К 1 с ц Роя схо;цт цсрелдча шформациц через выхолцой кохху - татор 9 в ярифхетцко-логический блок 11, ес прсобразовацце в соответствии с типом мцкрокомацлы ц подксцочецце ерез вхолцой коммутатор 12 ко вхолу блока рспстров 1 О. К концу второго такта устацовцтгя такке состояние узла 13, коцтролируощего четцость информации в регцстре мцкрокомацл 1. Во втором такте блок сццхроццздццц 14 выпабя- Т Ы В Я Е Т С Ц ГЦ Я Л Н Я 1 Ц Ц Ц Е С Ц Ц Х Р 0 Ц Ц 3 ЯЦ 1 Ц П ,) С. ма 15, по залнему фроцт) которого результат выполценя мцкрокомацл.1 зяцгцвдется в соотВетстВуоцц 1 Й регцстр, устяцяв 1 цвястг 5 дополнцтельныи регцст) 16, я также ,стдцяВ- лцвается в елцнцчцое состояние трпггср фцксаии сбоя 19, если узел 13 обцарукцл сбой в регистре мцкрокоманл 1.В третьем такте возбужлается сцгцдл чтсция следующей мцкрокоманлы цз олокд памяти микрокомацл 2. Олновременцо г чтгццсм слелующей мцкрокомацлы в соответгтцц содержацием лополццтельного регстра 16 к коцтрольцому коммутатору 17 полключтгя тот регцст 1), В соторыЙ оыл прццят рез;л,тдт выполнения текущей мцкрокомяцлы. 1 узел 18 проверцт этот результат ця четногть ц вь)- рабатывает соответствуОпий гцгцял ца свгсм выходе, который через элемент И г 1 И 2 поступает ца вхол элемента И 2,. По окоцчан третьего тяктя ПОВяя .)1 крокохяцля принимается в регистр мцкрокомал 1.В четвертох такте выполцяется цовдя мкрокомацла и по заднему фронт; с:гцялд ця шине сицхроццзаииц прцема 15 ее результат срццяется В Одцц цз регцстров б,чокя гистров 10. По залцему фроцт 5 гцгцдлд цд шине сцнхроццзациц приема 15 пр 1 цдл: Нп сигнала сбоя на выходе элехе.пя И.1 И 20 через элемецт И 21 процсхолцт устдцовка в ели яичное состояние триггера фикса п:111 сооя 19, кот 01)ый блокцру ст )яооту бчОКЯ синхронизации 14, и процессор прц это Остдцавливается. Если сбой це зяфиксцровац, в пятом тдк;кг происхочит выборка очерелцой мцкрокомдцды, а в шестом тякке ее вьи )лцецце К)ое ТОГО, В Ц ЕГТС)Х ТЯ 1 СТС ППОЦЗВОЛЦТС 51 1 СОЦТПОЛвыборки этой мцкрс)комдцлы в регцстр м)кпс)- команчы 1 и коцтроль выполцецця прель лмщей мцкрокомацлы и т. л.КЯ к Вглно па Времеццой Лц 2 ГС) ям м, коцтроль выполцецця тек щей мцкроко)ацлы совмеПец по времени г чтсцце., ц ыполцеиГм слелуоцей мцкрокомяцлы. Благодаря этому сОВмсцец 110 ВПО,чце 1 це кяк,чой .11 КРОкомЯ 11- ды осуществляется за лва такта, и ицк. работы проесс 01)я тас 1(с ГОГтав,1 яет лвя такта..) кпоцпогр:1 мц 1 Й процеггоп г коцтпОлс.1, Г О л Р ) Нс д1й О л 0 к и д х 51 тц х ц с р 0 ко .д ц л, р сгцстр длрггд, регистр хцкросомдцл. Первьй узел коцтрозя цд чстцогть. др.1)мст.со-логцчсскцй б,.ок. блок регистров. ВхолцоцВыхолцой коммутаторы, блок сопряжсця с оператцвцой памятНо и блок гцпхро):зяпцц. Прцчсх перВый Вхол блОК 2 1.ямятц мпкрокомдцл соелццсц с нхолом рсгцстрд адреса, первьш вхол которого сослццсн с первым вьхолом регистр д ис росс) м д цл, вхол которого соелицец с вхолом блока пдмятц мцкрокоманл, второй вхол которгго соелцпец с первым вьхолом бло),д сццхТо 1:зяпцп ц с первым вхолом блокя Гогряжецця с Опсс)ятцзцОЙ пяхятыо, Вьхол которого ссслпцец со вторым вхолом пегцстра длрггд ц с псрвзм Вхочом Вхолцого комммтатора, вьхол которого соелцчен с первым вхоло., блока рсгцстров, второй вхол которого сослццец нкой гццхрогцздПц прцгмд со вторым вьхолом блока сццхроццзяццц, а вы- ХОЛ СОЕ)птЕЦ С ПЕРВЫМ ВХОЛОМ ВЫХОДНОГО сохутяторя, вьхол котот)ОГО сослццГН с пер вь м вхоло)ч дрцфметцко-логцчегкого блока, вхол которого гоелцнец го втор.хц вхоламц вхоЛцого козхутдтора и блока сопряжения с опсрятвцой пях;ятью, третий вхол которого гоелццен со вторым вхолох ярпд).,стцсо-логп:еского блока и со вторым выхолом рсгпстра м)крокохдцл, тпетцЙ Выхол соторого гоелццсц с третьнм вхолом вхолцого коммутатора, четвертый выхол регцстрд мцкрокомдцд соелццс: со вторым входом вьхолцого коммутаторд. а пятый выхол соелццец со холом первого узласптроля цд стцость, 0 т л и ч д юц и й г я тех, что. г пельо пов.Нцецця быстролсйствця идоцсссоря. Оц дополццтс,ц.цо солсрж:т лополц: тс льцый регистр, кочтрольцьЙ сохммтятор, Второц зг 1 соцт)Рля цд четцогть, элемецть И,Т 1 И , 11 тпцггс) фцкгяццц сбоя. П 5 чцг 1 "Г;)чнй гхол )ополНтельЦГГО С)ГГЦГТО Д "ОГЛ П 1 ГЦТРГТ ) М ВЫХОЧОМ реп.стпд м.с)оком дил, д нхол соглццсц с первы холг соцтрольцого коммутатора, второй хол которого гоелццгц г ыхолом ОЛОКД ПСГГТ, Д В 1 ХР, - ГО ХОЛОМ ВТОРО. го хз-д коцт -я цд четцогть. нхол которого гое; Пгц г 1 Г) 5 хс)лом эчегцтд И,1 И, вь. Ол котопого госш,Гц го вхолс мгтдцовкц В ГЛПНПц "ППГГсч;1 1 цКсдго.ц сбоя, ВХОД д 1 ИЕЦ)5. :Ото)Р. 0 ГРГЛ)ГЦ Г ТПГ. Ц 1 ЫХОЛОМ бчокд ппхр 1 яцц, д цу,.евой хол трцггг)д 11)цкгяи;ц;Ооя соел Нсц го вхолом блока сццхроцизд;цп. второй выхол котопого соелцс шцчой гц х)оцз; и 11 прцемд со вторьм.1 вхочдмлопочццтсльцого регцстрд ц элсмец:иЧт иьи мьи комЛя. к 7 йрвемегыснрмоютн

СмотретьЗаявка

1885226, 21.02.1973

ПРЕДПРИЯТИЕ ПЯ Г-4128

ЕВДОЛЮК ЮРИЙ МАКСИМОВИЧ, КРАМФУС ИЛЬЯ РОМАНОВИЧ, СТЕПАНОВ ВИКТОР НИКОЛАЕВИЧ, УЛЬЯНОВА ЕЛЕНА КОНСТАНТИНОВНА

МПК / Метки

МПК: G06F 11/16, G06F 9/22

Метки: контролем, микропрограмный, процессор

Опубликовано: 15.08.1975

Код ссылки

<a href="https://patents.su/4-481036-mikroprogramnyjj-processor-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограмный процессор с контролем</a>

Предыдущий патент: Накопительный “п”-разрядный сумматор

Следующий патент: Специализированная электронная машина для анализа определителей

Случайный патент: Центробежно-вибрационная установка