Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

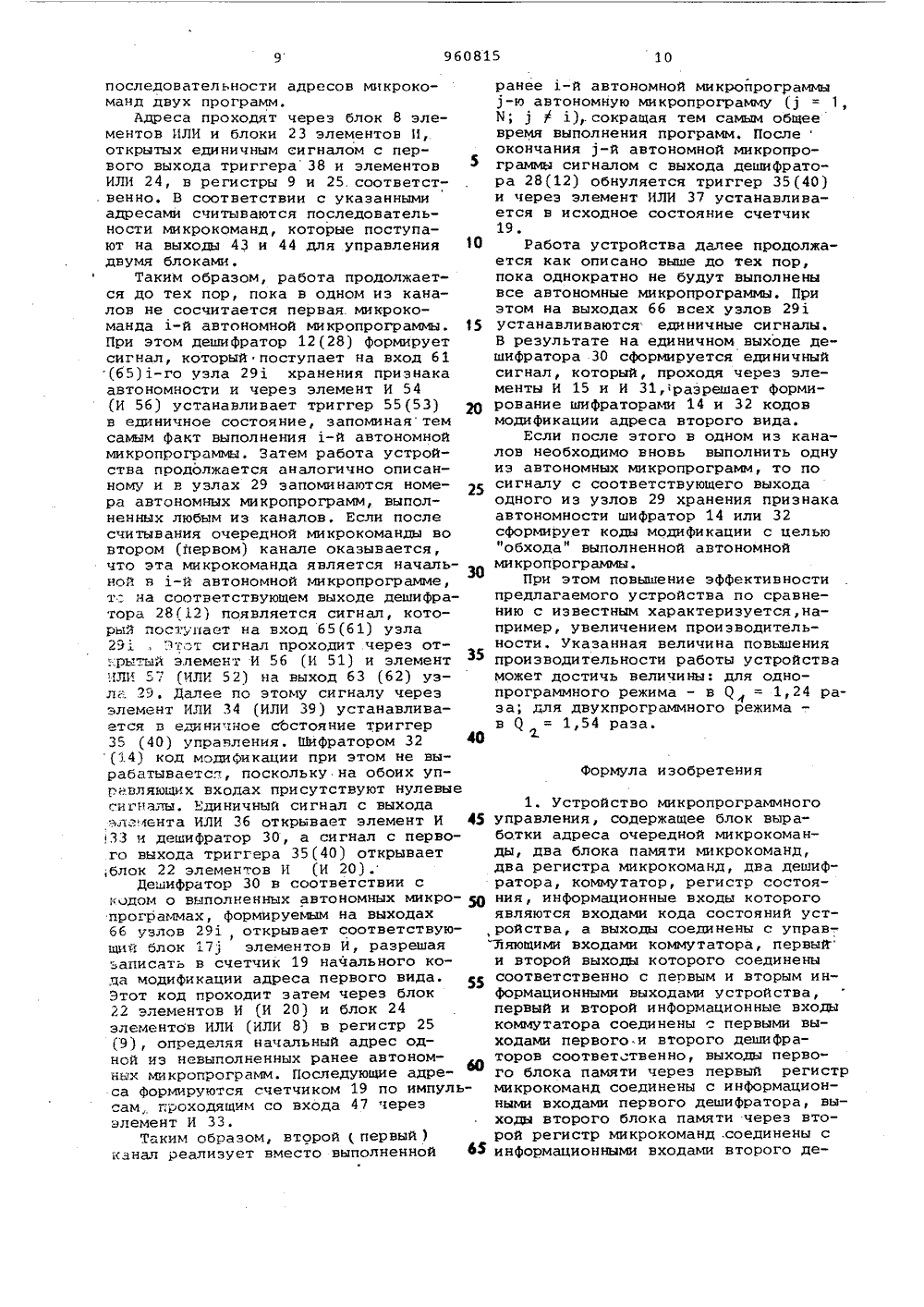

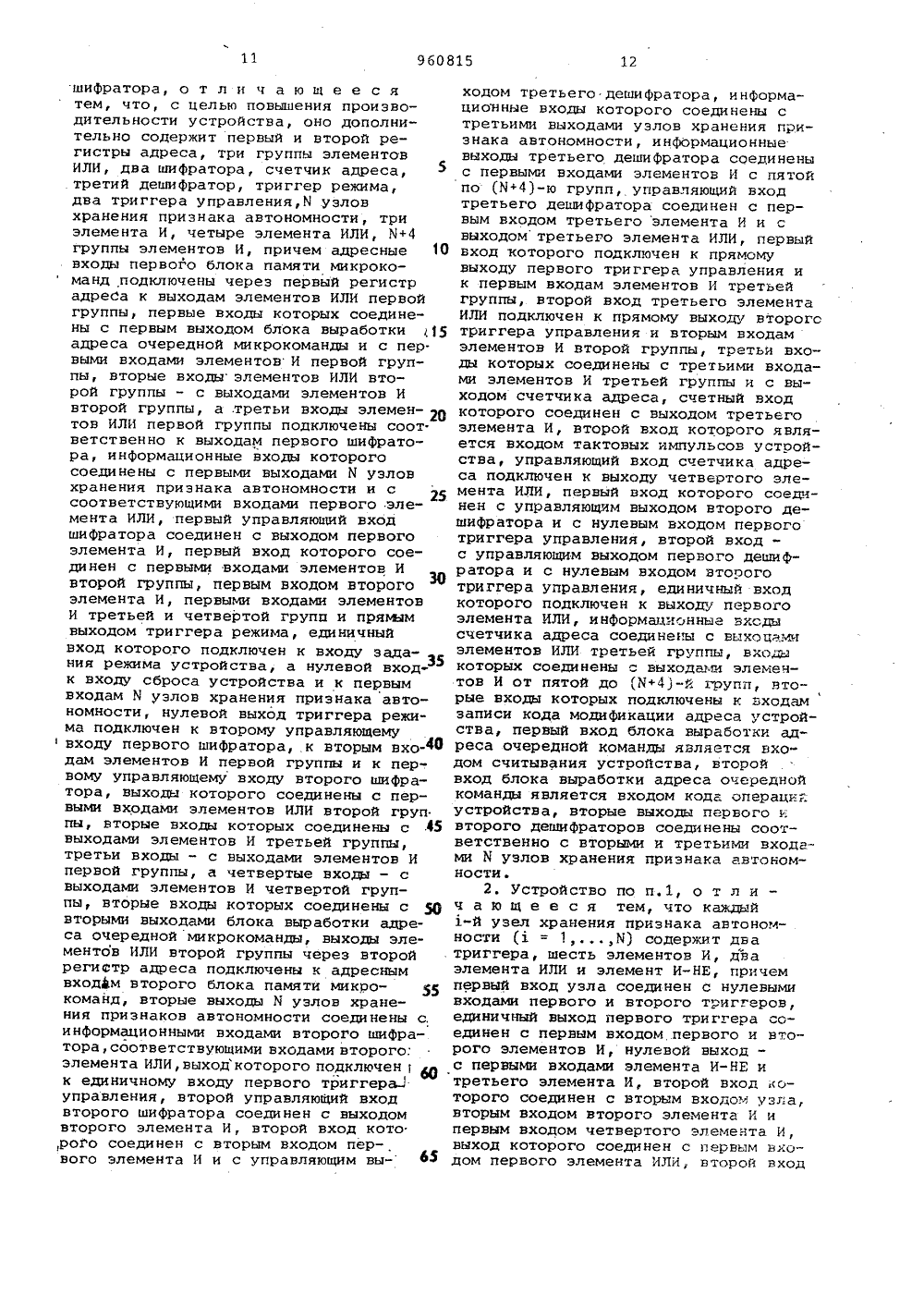

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик р 11960815(22) Заявлено 09,02,81(21) 3247201/18-24с присоединением заявки Мо 51 М. Кп.з 6 06 Е 9/22 Государственный комитет СССР по делам изобретений н открытийДата опубликования описания 2309.82 В.С.Харченко, Н,К,Вайда, И.П.Варбаш, В,И.Сидоренко,Г.Н,Тимонькин, М.П,Ткачев и С,Н,Ткаченко(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства управления микропрограь- мных процессоров управляющих или вычислительных систем, допускающих мультипрограммную обработку информации.Известно устройство микропрограммного управления, обеспечивающее надежность функционирования управляющих и вычислительных систем эа счет резервирования и перестройки на раз.личных уровнях иерархии соответствующей структуры, начиная от функциональных элементов и кончая процессорами в целом. Это устройство содержит два запоминающих блока, два регистра адреса, два коммутатора, два триггера управления, элементы И и ИЛИ 13.Его недостатками являются низкие функциональные возможности, обусловленные малой гибкостью и универсальностью устройства.Наиболее близким техническим решением к изобретению является устройство микропрограммного управления, содержащее блок выработки адреса очередной микрокоманды, два блока памяти ми крокоманд, дв а ре ги стра ми крокоманд, два дешифратора, коммутатор, регистр состояния, причем входы регистра состояния являются первыми входами устройства, а выходы соединены с управляющими входами коммутатора, первые выходы которого соединены с первыми выходами устройства, вторые выходы соединены с вторыми выходами устройства, первые входы соединены с информационными выходами первого дешифратора микрокоманд, входы которого соединены с выходами первого регистра микрокоманд, входы которого соединены с выходами первого блока памяти микрокоманд, вторые входы коммутатора соединены с информационными выходами второго дешифратора микрокоманд,входы которого соединены с выходами второго регистра микрокоманд, входы которого соединены с выходами второго блока памяти микрокоманд 1,21.Недостатками этого устройства являются низкие функциональные возможности, обусловленные малой гибкостью и универсальностью его работы. Малая гибкость и универсальность работы объясняются, например, отсутствием возможности обеспечить мультипро 960815граммную работу управляемых объектов. Кроме того, из-за слабой адаптации устройства к реализуемым программам время их выполнения завышается, что приводит к понижению эффективного быстродействия известного устройства,Цель изобретения - повышение производительности устройства.Поставленная цель достигаетсятем, что в устройство микропрограммного управления, содержащее блоквыработки адреса очередной микрокомайды, два блока памяти микрокоманд, два регистра микрокоманд, двадешифратора, коммутатор, регистр состояния, информационные входы которого являются входами кода состояний устройства, а выходы соединены суправляющими входами коммутатора,первый и второй выходы которого соединены соответственно с первым ивторым информационными выходами устройства, первый и второй информационные входы коммутатора соединены спервыми выходами первого и второгодешифратора соответственно, выходыпервого блока памяти через первыйрегистр микрокоманд соединены с информационными входами первого дешифратора, выходы второго блока памятичерез второй регистр микрокомандсоединены с информационными входамивторого дешифратора, дополнительновведены первый и второй ревистрыадреса, три группы элементов ИЛИ,два шифратора, счетчик адреса, третий дешифратор, триггер режима,два триггера управления, И узловхранения признака автономности, триэлемента И, четыре элемента ИЛИ,И+4 группы элементов И, причем адресные входы первого блока памятимикрокоманд подключены через первыйрегистр адреса к выходам элементовИЛИ первой группы, первые вход которых соединены с первым выходом 45блока выработки адреса очередноймикрокоманды и с первыми входамиэлементов И первой группы, вторыевходы элементов ИЛИ второй группы -с выходами элементов И втоРой гРУплы, а третьи входы элементов ИЛИпервой группы подключены соответственно к выходам первого шифратора,информационные входы которого соединены с первыми выходами И узловхраАния признака автономности и ссоответствующими входами первого элемента ИЛИ, первый управляющий входшифратора соединен с выходом первогоэлемента И, первый вход которого соединен с первыми входами элементов И 60второйгруппы, первым входом второгоэлемента И, первыми входами элементов И третьей и четвертой групп ипрямым выходом триггера режима, единичный вход которого подключен к вхо ду задания режима устройства, а нулевой вход - к входу сброса устройства и к первым входам В узлов хранения признака автономности, нулевой выход триггера режима подключен к второму управляющему входу первого шифратора, к вторым входам элементов И первой группы и к первому управляющему входу второго шифратора, выходы которого соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И третьей группы, третьи входы - с выходами элементов И первой группы, а четвертые входы - с выходами элементов И четвертой группы, вторые входы которых соединены с вторыми выходами блока выработки адреса очередной микро- команды, выходы элементов ИЛИвторой группы через второй регистр адреса подключены к адресным входам второго блока памяти микрокоманд, вторые входы И узлов хранения признаков автономности соединены с информационными входами второго шифратора, соответствующими входами второго элемента ИЛИ, выход. которого подключен к единичному входу первого триггера управления, второй управляющий вход второго шифратора соединен с выходом второго элемента И, второй вход которого соединен с вторым входом первого элемента И и с управляющим выходом третьего дешифратора,информационные входы которого соединены с третьими выходами И узлов хранения признака автономности, информационные выходы третьего дешифратора соединены с первыми входами элементов И с пятой по (И+4)-ю групп, управляющий вход третьего дешифратора соединен с первым входом третьего элемента И и с выходом третьего "лемен-. та ИЛИ, первый вход которого подключен к прямому выходу первого триггера управления и к первым входам элементов И третьей группы, второй вход третьего элемента ИЛИ подключен к прямому выходу второго триггера управления и вторым входам элементов И второй группы, третьи входы которых соединены с третьими входами элементов И третьей группы и с выходом счетчика адреса, счетный вход которого соединен с выходом третьего элемента И, второй вход которого является входом тактовых импульсов устройства, управляющий вход счетчика адреса подключен к выходу четвертого элемента ИЛИ, первый вход которого соединен с управляющим выходом второго дешифратора и с нулевым входом первого триггера управления, второй вход - с управляющим выходсм первого дешифратора и с нулевым входом второго триггера управления,единичный вход которого подКлючен к вы40 45 50 55 60 65 ходу первого элемента ИЛИ, информационные входы счетчика адреса соединены с выходами элементов ИЛИ третьей группы, входы которых соединены с выходами элементов И от пятой до (Я+4)-й групп, вторые входы которых подключены к входам записи кода модификации адреса устройства, первый вход блока выработки адреса очередной команды является входом считывания устройства, второй вход блока выработки адреса очередной команды является входом кода операций устройства, вторые выходы первого и второго дешифраторов соединены соответственно с вторыми и третьими входами М узлов хранения признака автономности,При этом каждый 1-й узел хранения признака автономности (1 = 1М) содержит два триггера, шесть элементов И, два элемента ИЛИ и элемент И-НЕ, причем первый вход узла соединен с нулевыми входами первого и второго триггеров, единичный выход первого триггера соединен с первыми входами первого и второго элементов И, нулевой выход - с первыми входами элемента И-НЕ и третьего элемента И, второй вход которого соединен с вторым входом узла, вторым входом второго элемента И и первым входом четвертого элементаИ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого с:единен с выходом второго элемента И, а выход является первым выходом узла, второй выход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, второй вход которого соединен с первыми входами пятого и шестого элементов И и третьим входом узла, второй вход четвертого элемента И соединен с единичным выходом первого триггера и вторым входом шестого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход пятого элемента И соединен с единичным входом первого триггера, выход . третьего элемента И соединен с единичным входом второго триггера, нулевой выход которого соединен с вторыми входами пятого элемента И и элемента И-НЕ, выход которого является третьим выходом узла.Увеличение производительности предлагаемого устройства достигается за счет работы как в одчопрограммномрежиме (параллельно выполняется однапрограмма), так и в трех новых режимах: двухпрограммном (одновременновыполняются две различные программы);двухпрограммном с увеличением эффективного быстродействия (одновременно выполняются две различные програмьь, при этом автономные микро 5 1 О 15 20 25 30 35 программ выполняются в двух каналаходин раз);однопрограммном с увеличением эффективного быстродействия(параллельно выполняется одна программа, при этом каждая автономнаямикропрограмма выполняется один раз).На фиг.1 представлена функциональная схема устройства микропрограммного управления; на фиг.2 - функциональная схема узла хранения признака автономностиУстройство микропрограммного управления содержит блок 1 выработкиадреса очередной микрокоманды, состоящий из регистра 2 адреса, блока3 памяти, информационного регистра 4,с полем 5 задания адреса очередноймикрокоманды первой программ А, полем 6 задания адреса очередной микрокоманды второй программы А и полем7 задания адреса следующей адресноймикрокоманды, группу 8 элементов ИЛИ,регистр 9 адреса, блок 10 памяти микрокоманд, регистр 11 микрокоманд, дешифратор 12 микрокоманд, коммутатор13, шифратор 14, элемент И 15, регистр 16 состояния, (И+4)-ю группу171 элементов И (1 = 1И),группу 18 элементов ИЛЙ, счетчик 19адресов, группу 20 элементов И,группу 21 элементов И, группу 22элементов И, группу 23 элементов И,группу 24 элементов ИЛИ, регистр 25адреса, блок 26 памяти микрокоманд,регистр 27 микрокоманд, дешиФратор28 микрокоманд, И узлов 29 храненияпризнака автономности, дешифратор30, элемент И 31, шифратор 32, эле.мент И 33, элемент ИЛИ 34, триггер35 управления, элемент ИЛИ 36, элемент ИЛИ 37, триггер 38 режима,элемент ИЛИ 39, триггер 40 управления,входы 41 и 42, выходы 43 и 44,выходы 45-49 устройства.Узел 29 хранения признака автономности состоит (Фиг,2) из элементов И 50 и 51, элемента ИЛИ 52,триггера 53, элемента И 54, триггера55, элемента И 56, элемента ПЛИ 57,элементов И 58 и 59, элемента И-НЕ60, входа 61, выходов 62 и 63,входов 64 и 65, выхода 66.Устройство программного управления в однопрограммном режиме работает следующим образом.В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии, На входы 45 устройства поступают информационные сигналы о состоянии работоспособности функциональных узлов устройства и управляемых им объектов. При этом на выходе регистра 16 формируются соответствующие управляющие сигнаПусть все Функциональные узлы уст - ройства и управляемых им объектов ра 960815отказавшего канала или к отказавше му блоку.Рассмотрим работу устройства вдвухпрограммном режиме.В этом случае каждый из каналовмикропрограммного управления реали- бО зует свою программу. Двухпрограммному режиму соответствует единичное состояние триггера 38.режима,На вход 42 поступает код операции,по которому блок выработки адреса 65 очередной микрокоманды Формирует ботоспособны, Тогда на управляющие входы коммутатора 13 подаются управляющие сигналы, обеспечявающие коммутацию первых выходов 43 коммутатора 13 и устройства с первыми входами, а вторых выходов 44 коммутатора и устройства с вторыми входами.В блок 1 выработки адреса очередной микрокоманды через шестые входы 42 устройства подается код операции. Код операции задает начальные адреса очередных микрокоманд первой и второй программ. Адрес очередной микрокоманды первой программы считается с первых выходов (поля 5 регистра 4) блока 1 выработки адреса очередной микрокоманды, адрес очередной микрокоманды второй програмьы - с вторых выходов (поля б регистра 4) того же блока. Адрес очередной микрокоманды первой программы поступает через первую групп 8 элементов ИЛИ на первый регистр 9, а через четвертую группу 21 элементов И (на первые входы с вторых выходов триггера 38 режима поступает в однопрограммном режиме разрешающий сигнал) и вторую группу 24 элементов ИЛИ на второй регистр 25. Так как в однопрограммном режиме работы устройства на первом выходе триггера 38 режима сигнал не формируется, то через первую группу 20 элементов И, третью группу 22 элементов .И, вторую группу 23 элементов И, цпервый элемент И 15 и второй элемент И 31 коммутация не производится. Следовательно, на вторые и третьи входы первой группы 8 элементов ИЛИ и на вторые, третьи и четвертые входы второй группы 24 элементов ИЛИ сигналы не поступают.Адреса сформированных в регистрах 9 и 25 выполняемых очередных микрокоманд поступают соответственно на первый и второй блоки 10 и 26 памяти микрокоманд. В соответствии с адресами выполняемых очередных микрокоманд из первого и второго блоков 10 и 26 выбираются выполняемые микрокоманды первой програмьы, которые поступают соответственно на первый и второй регистры 11 и 27 микрокоманд. Далее сигналы с первого и второго регистров 11 и 27 микрокоманд считываются соответственно на первый .и второй дешифраторы 12 и 28 микрокоманд, с информационных выходовкоторых,через коммутатор 13 сигйалы подаются соответственно на первый и второй выходы 43 и 44 устройства. Таким образом, последовательность микрокоманд первой програмьы поступает .на выходы 43 и 44 устройства, обеспечивает работу соответствующих объектов управления (операционных блоков, например),В случае необходимости подачи последовательности ми крокома нд первойпрограммы только на первые выходы43 устройства или только на вторыевыходы 44 устройства изменяют кодсостояния работоспособности функциональных узлов устройства и управляемых им объектов, подаваемый на первые входы 45 устройства. При этомна выходах регистра 16 формируютсясигналы, обеспечивающие соответствующую коммутацию в коммутаторе 13,После считывания первой микрокоманды 1-й автономной микропрограммы из первого и второго блоков 10 15 и 26 памяти микрокоманд на информационных выходах первого и второгодешифраторов 12 и 28 микрокоманд в1-ом разряде поля признака автонсмности считывается единица. В соответ ствии с этим на второй и третий входы 61 и 65 1-го узла 29 хранения признака автономности поступают сигналы, по которым через элементы И 54и 58 осуществляется установка в еди 25 ничное состояние триггеров 53 и 55. Если затем в ходе выполнения программ устройство вновь переходит к реализации 1-й автономной микропрограммы, то на входы 61 и 65 узла 291 поступают сигналы, которые проходятчерез элементы И 51, ИЛИ 52 и И 56,ИЛИ 57 на выходы 62 и 63. Сигналы сэтих выходов проходят на 1-е информационные .входы шифраторов 14 и 32соответственно, которые выдают кодымодификации адреса второго вида. Врезультате на регистрах 9 и 25 сформируются адреса очередных микрокоманд, которые определяют .адреса начальных микрокоманд, следующих за 40 1-й автономной микропрограммой. Следовательно, повторное выполнение ранее встречающейся автономной ьикропрограммы не происходит, что ускоряет реализацию всей программы в 45 целом. далее устройство в этом режиме продолжает функционировать аналогично описанному. Если в процессефункционирования выходит из строя один из узлов устройства или управля 50 емого блока, что Фиксируется регистром 16, то на выходах коммутатора 13 Формируются сигналы, которые блокируют прохождение микрокоманд от960815 Формула изобретения 55 последовательности адресов микрокоманд двух программ.Адреса проходят через блок 8 элементов ИЛИ и блоки 23 элементон И, открытых единичным сигналом с первого выхода триггера 38 и элементов ИЛИ 24, в регистры 9 и 25.соответственно. В соответствии с указанными адресами считываются последовательности микрокоманд, которые поступают на выходы 43 и 44 для управления 1 О двумя блоками.Таким образом, работа продолжается до тех пор, пока в одном из каналов не сосчитается первая.микрокоманда 1-й автономной микропрограммы. 15 При этом дешифратор 12(28) формирует сигнал, который поступает на вход 61 (65)-го узла 29 хранения признака автономности и через элемент И 54 (И 56) устананливает триггер 55(53) 20 н единичное состояние, запоминая тем самым факт выполнения 1-й автономной микропрограммы. Затем работа устройства продолжается аналогично описанному и н узлах 29 запоминаются номера автономных микропрограмм, выполненных любым из каналов. Если после считывания очередной микрокоманды во втором (первом) канале оказывается, что эта микрокоманда является начальной н 1-й автономной микропрограмме, т: на соотнетстнующем выходе дешифратора 28(12) появляется сигнал, который поступает на вход 65(61) узла 29 : Эт:т сигнал проходит .через от:,Рытый элемент И 56 (И 51) и элемент ИЛИ 57 (ИЛИ 52) на выход 63 (62) узл 29. Далее по этому сигналу через элемент ИЛИ 34 (ИЛИ 39) устанавливается н единичное состояние триггер 35 (40) управления. Шифратором 32 40 (14) код модификации при этом не вырабатываетсп, поскольку на обоих упРавляющих входах присутствуют нулевые сигналы. Единичный сигнал с выхода элэ ынта ИЛИ Зб открывает элемент И 45 ЗЗ и дешифратор 30, а сигнал с первого выхода триггера 35 (40) открывает;блок 22 элементов И (И 20).Дешифратор 30 в соответствии с кодом о выполненных антономных микро Опрограммах, формируемым на выходахбб узлов 291, открывает соответствующий блок 17 элементов И, разрешаязаписать н счетчик 19 начального кода модификации адреса первого вида.Этот код проходит затем через блок22 элементов И (И 20) и блок 24элементов ИЛИ (ИЛИ 8) н регистр 25(9), определяя начальный адрес одной из невыполненных ранее автономных микропрограмм. Последующие адреса формируются счетчиком 19 по импульсам, гроходящим со входа 47 черезэлемент И ЗЗ,Таким образом, второйпервый )канал реализует вместо выполненной ранее 1-й автономной микропрограммы1-ю автономную микРопрограмму (3 = 1Х; 1 1 1),.сокращая тем самым общеевремя выполнения программ. Послеокончания 1-й автономной микропрограммы сигналом с выхода дешифратора 28(12) обнуляется триггер 35(40)и через элемент ИЛИ 37 устанавливается н исходное состояние счетчик19.Работа устройства далее продолжается как описано выше до тех пор,пока однократно не будут выполненывсе автономные микропрограммы. Приэтом на выходах 66 всех узлов 29устанавливаются единичные сигналы,В результате на единичном выходе дешифратора 30 сформируется единичныйсигнал, который, проходя через элементы И 15 и И 31,разрешает формирование шифраторами 14 и 32 кодовмодификации адреса второго вида.Если после этого в одном из каналов необходимо вновь выполнить однуиз автономных микропрограмм, то посигналу с соответствующего выходаодного из узлов 29 хранения признакаавтономности шифратор 14 или 32сформирует коды модификации с целью"обхода" выполненной автономноймикропрограммы.При этом повышение эффективностипредлагаемого устройства по сравнению с известным характеризуется,например, увеличением производительности. Указанная величина повышенияпроизводительности работы устройстваможет достичь величины: для однопрограммного режима - в Я = 1,24 раза; для двухпрограммного режима -в Я = 1,54 раза,2. 1. Устройство микропрограммного управления, содержащее блок выработки адреса очередной микрокоманды, два блока памяти микрокоманд, два регистра микрокоманд, два дешифратора, коммутатор, регистр состояния, информационные входы которого являются входами кода состояний уст,ройства, а выходы соединены с управ"ляющими входами коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым информационными выходами устройства, первый и второй информационные входы коммутатора соединены первыми выходами первого.и второго дешифраторов соответ твенно, выходы первого блока памяти через первый регистр микрокоманд соединены с информационными входами первого дешифратора, выходы второго блока памяти через второй регистр микрокоманд .соединены с информационными входами второго де 960815 12шифратора, о т л и ч а ю щ е е с я тем, что, с целью повышения производительности устройства, оно дополнительно содержит первый и второй регистры адреса, три группы элементов ИЛИ, два шифратора, счетчик адреса,5 третий дешифратор, триггер режима, два триггера управления, И узлов хранения признака автономности, три элемента И, четыре элемента ИЛИ, И+4 группы элементов И, причем адресные 1 О входы первого блока памяти микрокоманд подключены через первый регистр адреса к выходам элементов ИЛИ первой группы, первые входы которых соединены с первым выходом блока выработки 15 адреса очередной микрокоманды и с пер. выми входами элементов И первой группы, вторые входы элементов ИЛИ второй группы - с выходами элементов И второй группы, а .третьи входы элемен О тов ИЛИ первой группы подключены соответственно к выходам первого шифратора, информационные входы которого соединены с первыми выходами И узлов хранения признака автономности и с соответствующими входами первого элемента ИЛИ, первый управляющий вход шифратора соединен с выходом первого элемента И, первый вход которого соединен с первыми входами элементов И второй группы, первым входом второго элемента И, первыми входами элементов И третьей и четвертой групп и прямым выходом триггера режима, единичныйвход которого подключен к входу задания режима устройства, а нулевой входк входу сброса устройства и к первым входам И узлов хранения признака автономности, нулевой выход триггера режима подключен к второму управляющемувходу первого шифратора, к вторым вхоО дам элементов И первой группы и к первому управляющему входу второго шифратора, выходы которого соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с 45выходами элементов И третьей группы,третьи входы - с выходами элементов И первой группы, а четвертые входы - свыходами элементов И четвертой группы, вторые входы которых соединены с 5 Овторыми выходами блока выработки адреса очередной микрокоманды, выходы элементов ИЛИ второй группы через второй регистр адреса подключены к адресным входйм второго блока памяти микро команд, вторые выходы И узлов хранения признаков автономности соединены с информационными входами второго шифратора, соответствующими входами второго:элемента ИЛИ,выходкоторого подключенк единичному входу первого триггера. управления, второй управляющий вход второго шифратора соединен с выходом второго элемента И, второй вход кото ,рого соединен с вторым входом первого элемента И и с управляющим выходом третьего дешифратора, информационные входы которого соединены с третьими выходами узлов хранения признака автономности, информационные выходы третьего дешифратора соединены с первыми входами элементов И с пятой по (И+4)-ю групп, управляющий вход третьего дешифратора соединен с первым входом третьего элемента И и с выходом третьего элемента ИЛИ, первый вход которого подключен к прямому выходу первого триггера управления и к первым входам элементов И третьей группы, второй вход третьего элементаИЛИ подключен к прямому выходу второготриггера управления и вторым входам элементов И второй группы, третьи входы которых соединены с третьими входами элементов И третьей группы и с выходом счетчика адреса, счетный вход которого соединен с выходом третьегоэлемента И, второй вход которого является входом тактовых импульсов устройства, управляющий вход счетчика адреса подключен к выходу четвертого элемента ИЛИ, первый вход которого соединен с управляющим выходом второго дешифратора и с нулевым входом первого триггера управления, второй вход - с управляющим выходом первого дешифратора и с нулевым входом второго триггера управления, единичный вход которого подключен к выходу первого элемента ИЛИ, информационные входы счетчика адреса соединены с выхоцами элементов ИЛИ третьей группы, входы которых соединены с выходюи элементов И от пятой до (И+4)-й групп, вторые входы которых подключены к входам записи кода модификации адреса устройства, первый вход блока выработки адреса очередной команды является входом считывания устройства, второйвход блока выработки адреса очередной команды является входом кода операци-,;устройства, вторые выходы первого ивторого дешифраторов соединены соответственно с вторыми и третьиья входами И узлов хранения признака автономности.2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что каждый 1-й узел хранения признака автономности (3. = 1Щ содержит два триггера, шесть элементов И, два элемента ИЛИ и элемент И- НЕ, причем первый вход узла соединен с нулевыми входами первого и второго триггеров, единичный выход первого триггера соединен с первым входом .первого и второго элементов И, нулевой выход - с первыми входами элемента И-НЕ и третьего элемента И, второй вход которого соединен с вторым входом узла, вторым входом второго элемента И и первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ,. второй входкоторого соединен с выходом второгоэлемента И, а выход является первым-выходом узла, второй выход которогосоединен с выходом второго элементаИЛИ, первый вход которого соединен свыходом первого элемента И, второйвход которого соединен с первыми входами пятого и шестого элементов И итретьим входом узла, второй входчетвертого элемента И соединен с единичным выходом первого триггера и вто рым входом шестого элемента И, выходкоторого соединен с вторым входом второго элемента ИЛИ, выход пятого эле-мента И соединен с единичным входом . первого триггера, выход третьего элемента И соединен с единичным входомвторого триггера, нулевой выход которого соединен с вторыми входами пятого элемента И и элемента И-НЕ, выходкоторого является третьим выходом узла. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРУ 646333, кл,б Об Р 9/22, 1979.2. Авторское свидетельство СССРУ 556439, кл.С 06 Г 9/22, 1977прототип)960815 7283/59 Тираж 731 ПодписноВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д.4/5 Зак лиал ППП "Патентф, г.ужгород, ул.Проектная,Составитель Л.Логачева Редактор А.Шишкина Техред М.Тепер Корректор Е.Рошко

СмотретьЗаявка

3247201, 09.02.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА Н. И. КРЫЛОВА

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, СИДОРЕНКО ВАЛЕНТИН ИВАНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.09.1982

Код ссылки

<a href="https://patents.su/8-960815-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Устройство для микропрограммного управления

Случайный патент: Воздухоочиститель для двигателя внутреннего сгорания