Система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1795499

Авторы: Березкин, Дубова, Хацкелевич

Текст

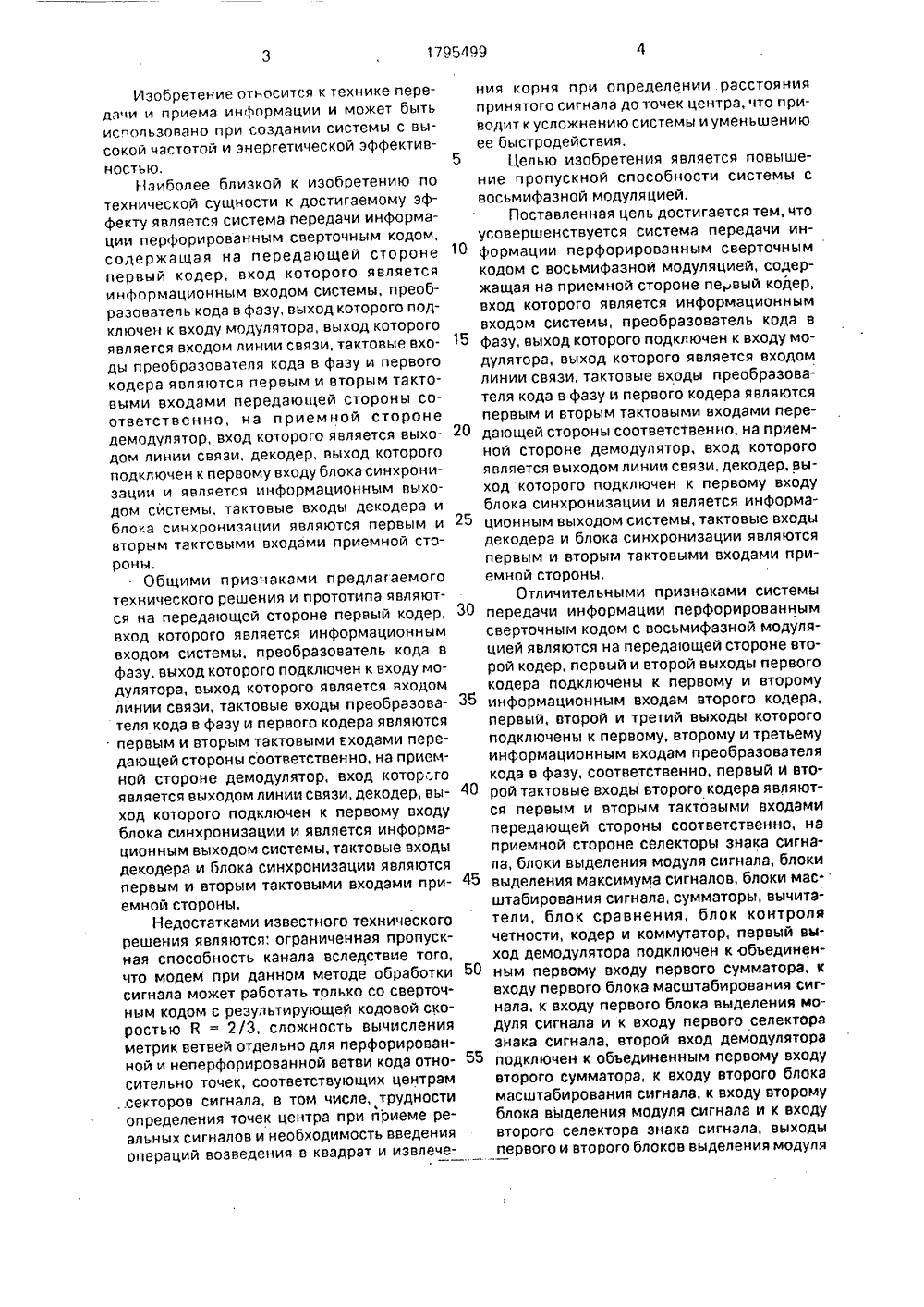

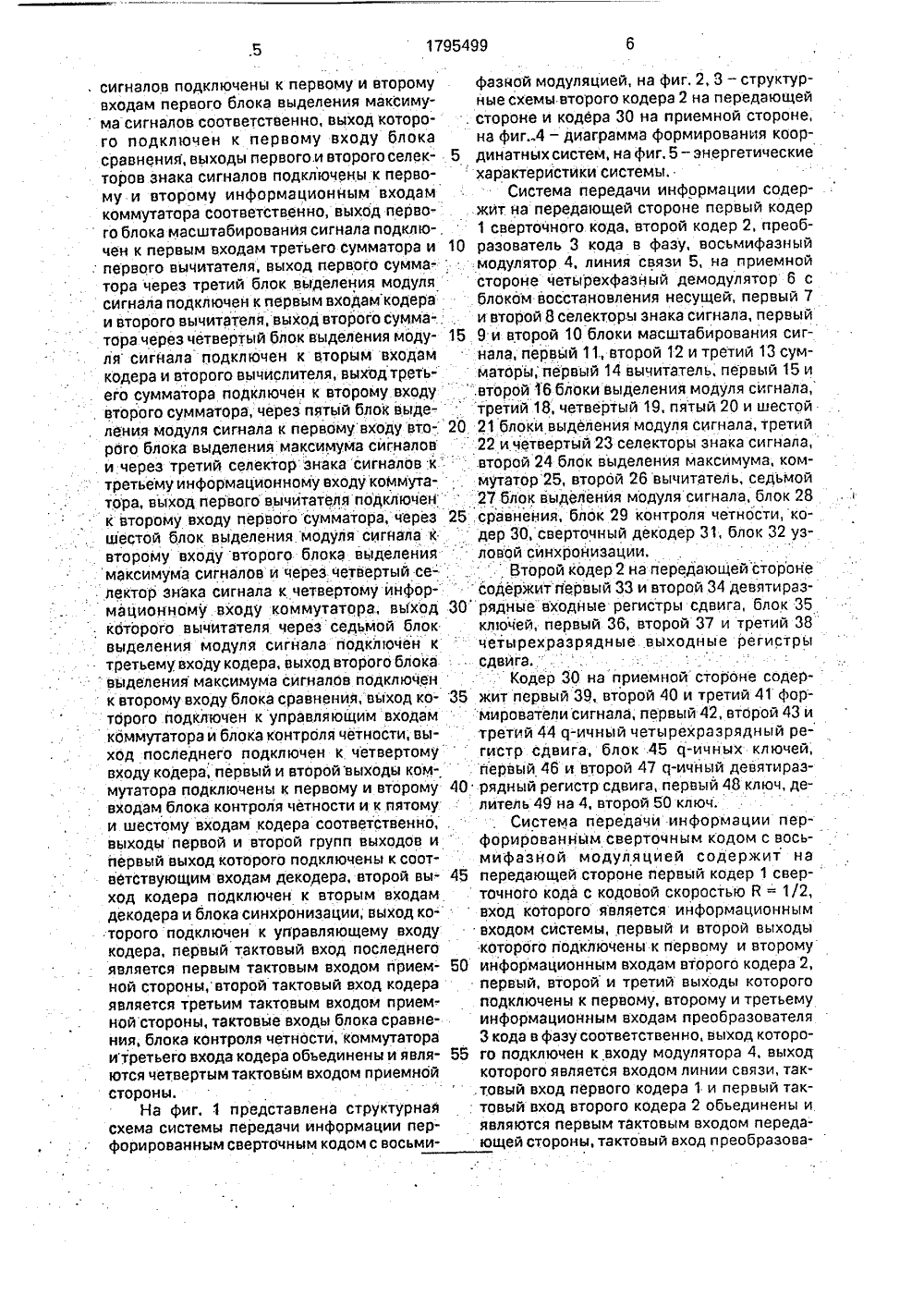

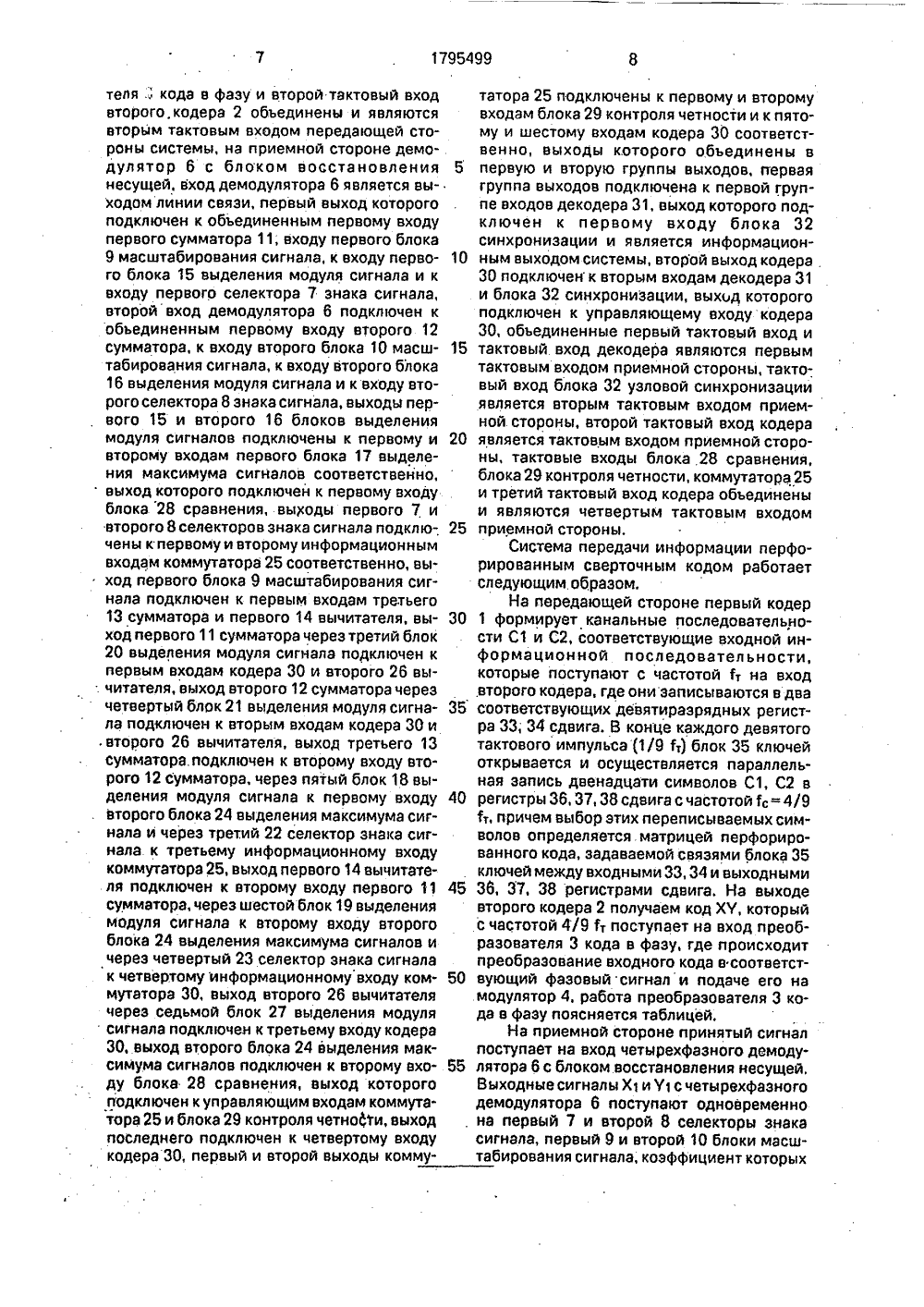

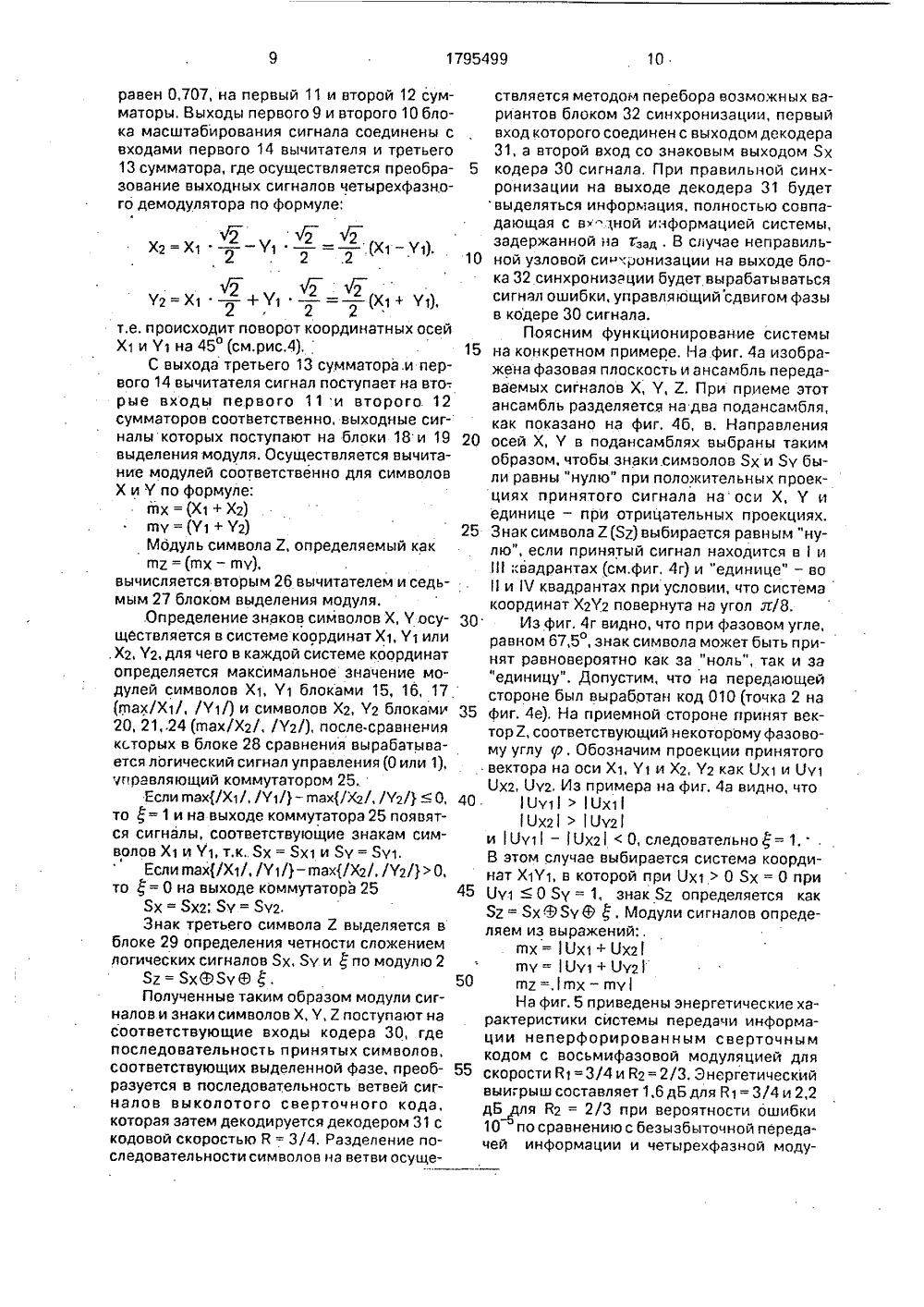

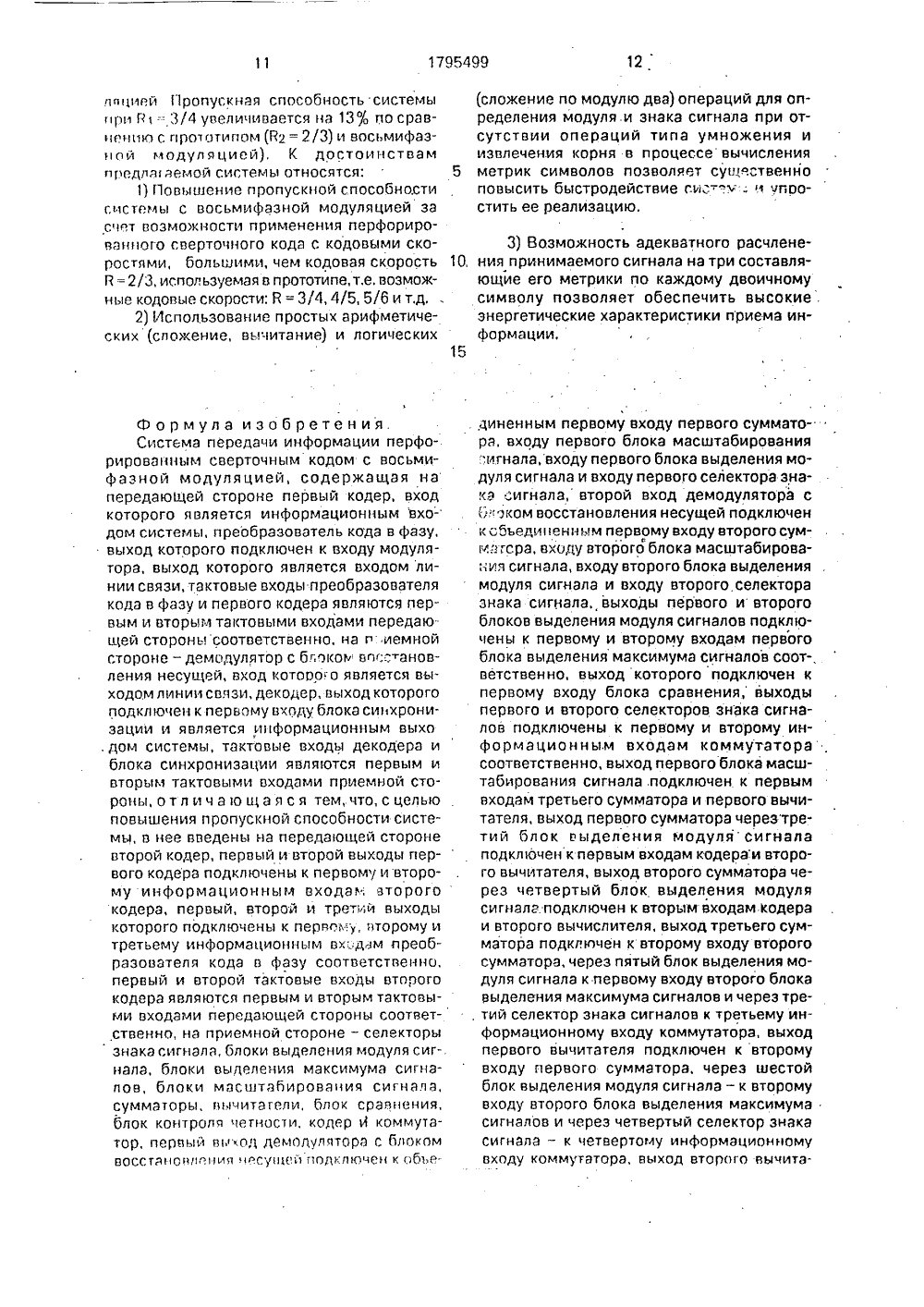

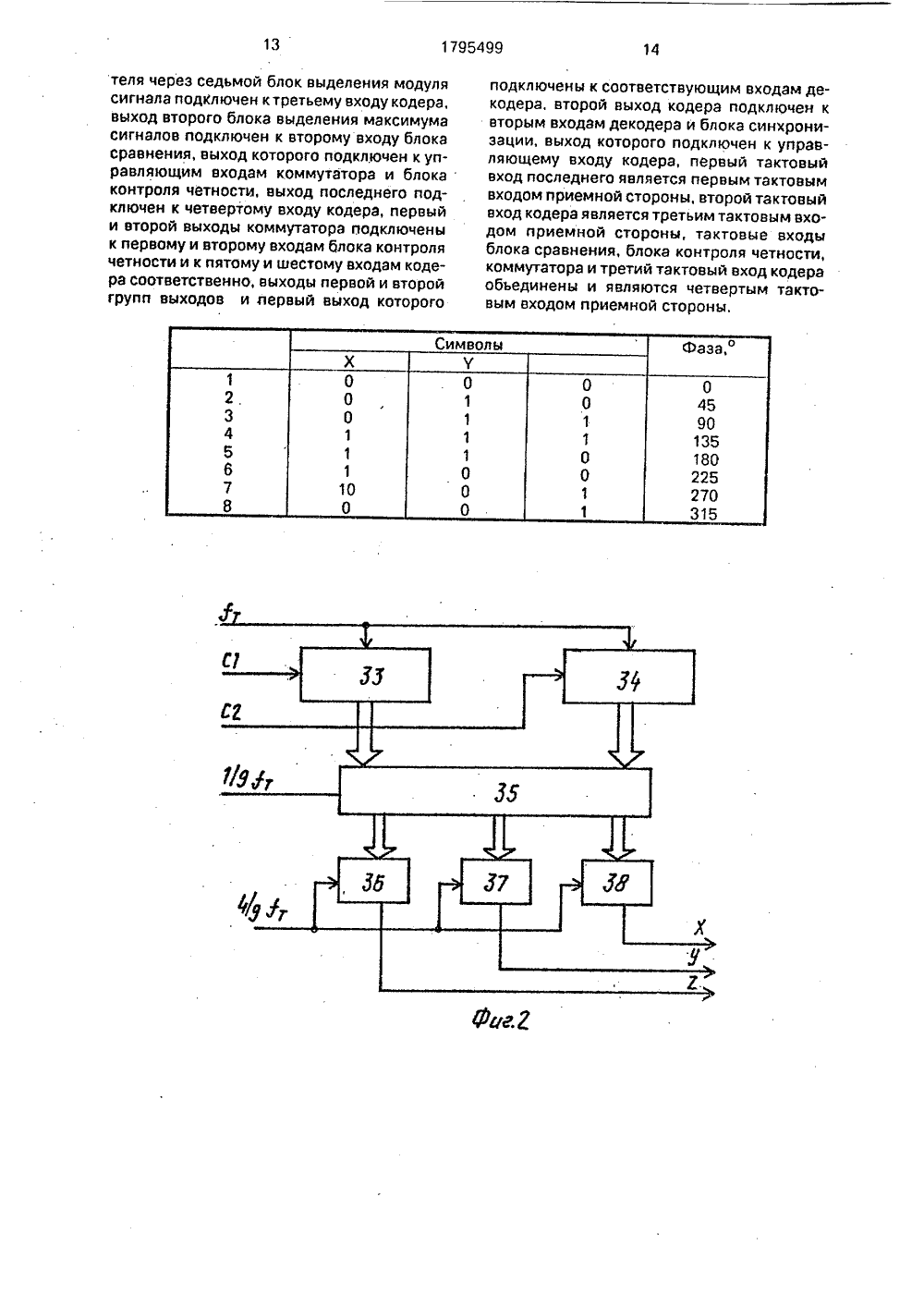

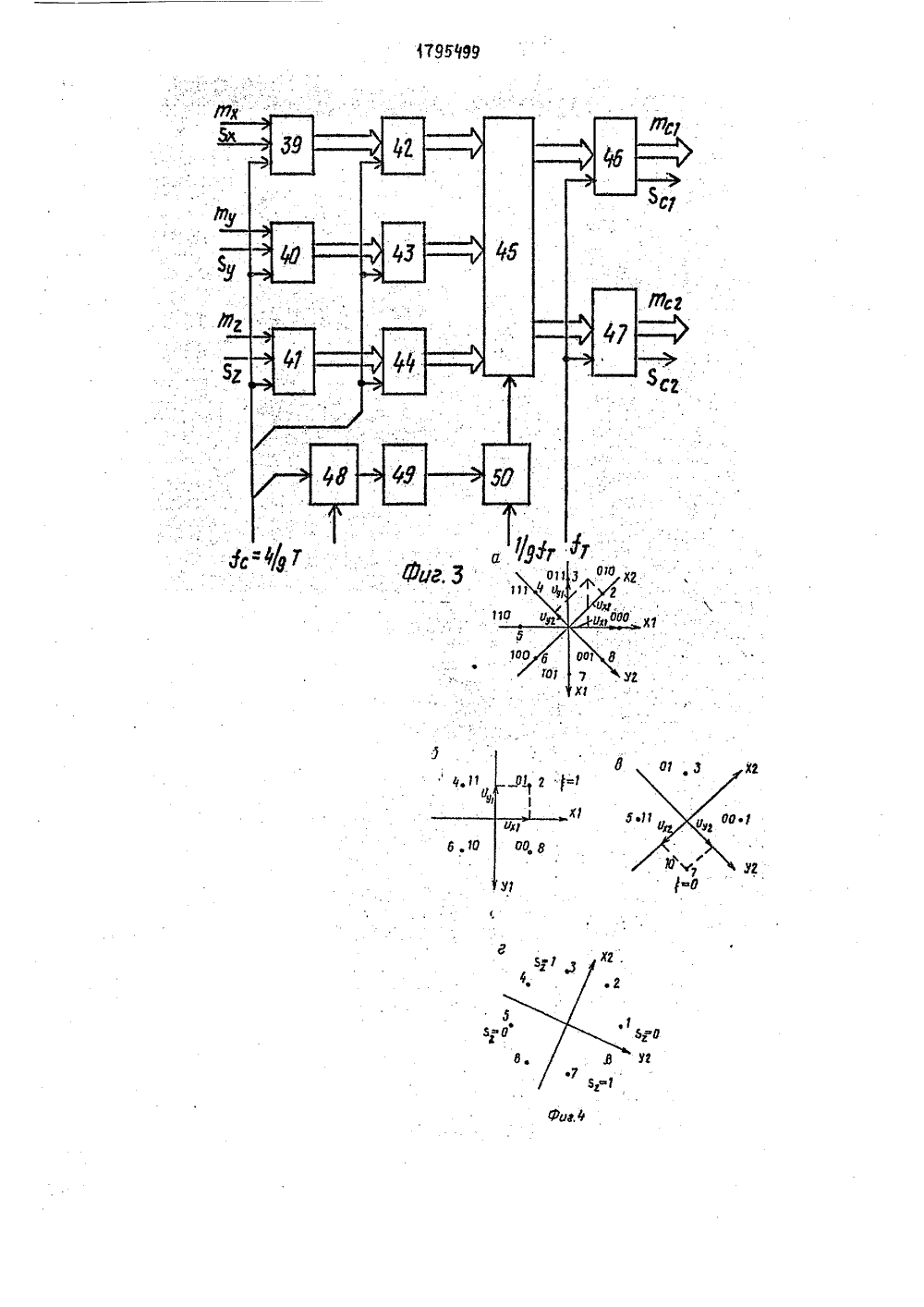

%6 едов СУДАРСТВЕННОЕ ПАТЕНТНОДОМСТВО СССРОСПАТЕНТ СССР) К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(21) 4810592/24 (22) 03.04.90 (46) 15.02.93. Бюл. (71) Научно-иссл ательский институт приборостроения (72) Я.Д.Хацкелевич, Т,Ф.Дубова и В,В.Березкин (56) Бансет В.Л., Дорофеев В.М. Цифровые методы в спутниковой связи. М.: Радио и связь, 1988, с, 214-217,. (54) СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ ПЕРФОРИРОВАННЫМ СВЕРТОЧНЫМ КОДОМ С ВОСЬМИФАЗНОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к технике передачи информации и может быть использовано при создании системы с высокой частотной и энергетической эффективностью. Целью изобретения является повышение пропускной способности системы с восьмифазной модуляцией. Система передачи информации перфорированным сверточным кодом с восьмифазной модуляциейЮ содержит на передающей стороне первыи кодер 1 сверточного кода, второй кодер 2, преобразователь 3 кода в фазу, восьмифазный модулятор 4, линию связи 5, на приемной стороне - четырехфазный модулятор 6 с блоком восстановления несущей, первый 7 и второй 8 селекторы знака сигнала, первый 9 и второй 10 блоки масштабирования сигнала, первый 11, второй 12 и третий 13 сумматоры, первый вычитатель 14, первый 15 и второй 16 блоки выделения модуля сигнала, первый блок 17 выделения максимума сигнала, третий 18, четвертый 19, пятый 20 и шестой 21 блоки выделения модуля сигнала, третий 22 и четвертый 23 селекторы знака сигнала, второй блок 24 выделения максимума, коммутатор 25, второйвычитатель 26 седьмой блок 27 выделения модуля сигнала, блок 28 сравнения, блок 29 контроля четности, кодер 30, сверточный декодер 31, блок 32 узловой синхронизации, функционально соединенные между собой, 1 табл., 5 ил.Изобретение относится к технике передачи и приема инФормации и может быть использовано при создании системы с высокой частотой и энергетической эффективностью,Наиболее близкой к изобретению по технической сущности к достигаемому эффекту является система передачи информации перфорированным сверточным кодом, содержащая на передающей стороне первый кодер, вход которого является информационным входом системы, преобразователь кода в фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне демодулятор, вход которого является выходом линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является информационным выходом системы. тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны.Общими г 1 ризнаками предлагаемого технического решения и прототипа являются на передающей стороне первый кодер, вход которого является информационным входом системы, преобразователь кода в фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне демодулятор, вход катар;го является выходом линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является информационным выходом системы, тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны.Недостатками известного технического решения являются: ограниченная пропускная способность канала вследствие того, что модем при данном методе обработки сигнала может работать только со сверточным кодом с результирующей кодовой скоростью й - 2/3, сложность вычисления метрик ветвей отдельно для перфорированной и неперфорированной ветви кода относительно точек, соответствующих центрам ,.секторов сигнала, в том числе, трудности определения точек центра при йриеме реальных сигналов и необходимость введения операций возведения в квадрат и извлечения корня при определении расстояния принятого сигнала до точек центра, что приводит к усложнению системы и уменьшению ее быстродействия.Целью изобретения является повышение пропускной способности системы с восьмифазной модуляцией.Поставленная цель достигается тем, чтоусовершенствуется система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией, содержащая на приемной стороне первый кодер, вход которого является информационным входом системы, преобразователь кода в 15 фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами пере дающей стороны соответственно, на приемной стороне демодулятор, вход которого является выходом линии связи, декодер, вцход которого подключен к первому входу блока синхронизации и является информа ционным выходом системы, тактовые входыдекодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны.Отличительными признаками системы З 0 передачи информации перфорированнымсверточным кодом с восьмифазной модуляцией являются на передающей стороне второй кодер, первый и второй выходы первого кодера подключены к первому и второму Зб информационным входам второго кодера,первый, второй и третий выходы которого подключенц к первому, второму и третьему информационным входам преобразователя кода в фазу, соответственно, первый и вто рой тактовые входы второго кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне селекторы знака сигнала, блоки выделения модуля сигнала, блоки 45 выделения максимума сигналов, блоки масштабирования сигнала, сумматоры, вычитатели, блок сравнения, блок контроля четности, кодер и коммутатор, первый выход демодулятора подключен к объединен ным первому входу первого сумматора, квходу первого блока масштабирования сигнала, к входу первого блока выделения модуля сигнала и к входу первого селектора знака сигнала, второй вход демодулятора 55 подключен к объединенным первому входувторого сумматора, к входу второго блока масштабирования сигнала, к входу второму блока выделения модуля сигнала и к входу второго селектора знака сигнала, выходы первого и второго блоков выделения модуля, сигналов подключены к первому и второму фазйой модуляцией, на фиг. 2, 3 - структурвходам первого блока выделения максиму- ные схемы второго кодера 2 на передающеймасигналов соответственно, выход которо- . стороне и кодера 30 на приемной стороне,го подключен к первому входу блока на фиг,4 - диаграмма формирования коорсравнения, выходы первого.и второго селек динатных систем, нэ фиг. 5 - энергетическиеторов знака сигналов подключены к перво- характеристики системы,му и второму информационным входам Система передачи информации содеркоммутатора соответственно, выход перво- жит на передающей стороне первый кодерго блока масштабирования сигнала подклю-, 1 сверточного кода, второй кодер 2, преобчен к первым входам третьего сумматора и 10 разователь 3 кода в фазу, вооьмифэзный. первого вычитателя, выход первого сумма- .: модулятор 4, линия связи 5, на приемнойтора через третий блок выделения модуля стороне четырехфазный демодулятор 6 ссигнала подключен к первым входамкодера блоком восстановления несущей, первый 7и второго вычитателя, выход второго сумма-.; и второй 8 селекторы знака сигнала, первыйтора через четвертый блок выделения моду 9 и второй 10 блоки масштабирования сигля сигнала подключен к вторым входам: нала, первый 11, второй 12 итретий 13 сумкодера и второго вычислителя, выходтреть- маторы,первый 14 вычитатель, первый 15 и. его сумматора поДключен к второму входу ,второй 16 блоки выделения модуля сигнала,, второго сумматора, через пятый блок выде- . третий 18, четвертый 19, пятый 20 и шестойления модуля сигнала к первому входу вто 21 блоки выделения модуля сигнала, третийрого блока выделения максимума сигналов 22 и четвертый 23 селекторы знака сигнала,. и через третий селектор знака сигналов к " второй 24 блок выделения максимума, комтретьему информационному входу коммута- мутатор 25, второй 26 вычитатель, седьмойтора, вйход первого вычитателя подключен27 блок выделения модуля сигнала, блок 28к второму входу первого сумматора, через 25 .сравнения, блок 29 контроля четности, кошестой блок выделения модуля сигнала к дер 30, сверточный декодер 31, блок 32 узвторому входу второго блока выделения . ловойсйнхройизации.максимума сигналов и через четвертый се-Второйкодер 2 напередающейсторонелектор знака сигнала к четвертому инфор-содержит первый 33 и второй 34 девятиразмационному. входу коммутатора, выход 30 рядные-входные регистры сдвига, блок 35. которого вычитателя через седьмой блок ключей, первый 36, второй 37 и третий 38 выделения модуля сигнала подключен кчетырехразрядные .выходные регистрытретьему входу кодера, выход второго блока сдвига.выделения максимума сигналов подключен Кодер 30 на приемной стороне содерк второму входу блока сравнения, выход ко жит первый 39, второй 40 и третий 41 форторого подключен к управляющим входам: мирователи сигнала, первый 42, второй 43 икоммутатора и блока контроля четности, вы- третий 44 о-ичный четырехразрядный ре-ход последнего подключен к четвертому гистр сдвига, блок .45 ц-ичных ключей,входу кодера, первый и второй выходы ком- первый 46 и второй 47 ц-ичйый девятиразмутатора подключены к первому и второму 40 рядный регистр сдвига, первый 48 ключ, девходам блока контроля четности и к пятому литель 49 нэ 4, второй 50 ключ.и шестому входам кодера соответственно, Система передачи информации первыходы первой и второй групп выходов и форированным сверточным кодом с восьпервыйвыходкоторогоподключеныксоот- мифазной модуляцией содержит навЕтСтвуюЩим входам декодера, второй вы передающей стороне первый кодер 1 сверход кодера подключен к вторым входам точного кода с кодовой скоростью В = 1/2,декодера и блока синхронизации; выход ко-вход которого является информационнымторого подключен к управляющему входу входом системы, первый и второй выходыкодера, первый тактовый вход последнего которого подключены к первому и второмуявляется первым тактовым входом прием информационным входам второго кодера 2,ной стороны,второй тактовый вход кодера первый, второй и третий выходы которогоявляется третьим тактовым входом прием- подключены к первому, второму и третьемуной стороны, тактовые входы блока сравне- информационным входам преобразователяния, блока контроля четности, коммутатора 3 кода в фазу соответственно, выход котороитретьего входа кодера обьединены и явля го подключен к входу модулятора 4, выходются четвертым тактовым входом приемной которого является входом линии связи, такстороны.товый вход первого кодера 1 и первый такХа фиг, 1 представлена структурная товый вход второго кодера 2 объединены исхема системы передачи информации пер- являются первым тактовым входом передафорированным сверточным кодом с восьми- ющей стороны, тактовый вход преобразова-теля . кода в фазу и второй тактовый вход второго, кодера 2 объединены и являются вторым тактовым входом передающей стороны системы, на приемной стороне демодулятор 6 с блоком восстановления несущей, вход демодулятора 6 является выходом пинии связи, первый выход которого подключен к объединенным первому входу первого сумматора 11, входу первого блока9 масштабирования сигнала, к входу первого блока 15 выделения модуля сигнала и к входу первого селектора 7 знака сигнала, второй вход демодулятора 6 подключен к обьединенным первому входу второго 12 сумматора, к входу второго блока 10 масштабирования сигнала, к входу второго блока 16 выделения модуля сигнала и к входу второго селектора 8 знака сигнала, выходы первого 15 и второго 16 блоков выделениямодуля сигналов подключены к первому и 101520 второму входам первого блока 17 выделения максимума сигналов соответствейно,выход которого подключен к первому входу блока 28 сравнения, выходы первого 7 и второго 8 селекторов знака сигнала подклю чены к первому и второму информационным входам коммутатора 25 соответственно, выход первого блока 9 масштабирования сигнала подключен к первым входам третьего 13 сумматора и первого 14 вычитателя, вы- ЗО ход первого 11 сумматора через третий блок 20 выделения модуля сигнала подключен к первым входам кодера 30 и второго 26 вы. читателя, выход второго 12 сумматора через четвертый блок 21 выделения модуля сигна ла подключен к вторым входам кодера 30 и ,второго 26 вычитателя, выход третьего 13 сумматора. подключен к второму входу второго 12 сумматора, через пятый блок 18 выделения модуля сигнала к первому входу 40 . второго блока 24 выделения максимума сигнала и через третий 22 селектор знака сигнала к третьему информационному входу коммутатора 25, выход первого 14 вычитателя подключен к второму входу первого 11 45 сумматора, через шестой блок 19 выделения модуля сигнала к второму входу второго блока 24 выделения максимума сигналов и через четвертый 23 селектор знака сигнала к четвертому информационномувходу ком мутатора 30, выход второго 26 вычитателя через седьмой блок 27 выделения модуля сигнала подключен к третьему входу кодера 30, выход второго блока 24 выделения максимума сигналов подключен к второму вхо ду блока 28 сравнения, выход которого гюдключен к управляющим входам коммутатора 25 и блока 29 контроля четности. выходпоследнего подключен к четвертому входу кодера 30, первый и второй выходы коммутатора 25 подключены к первому и второму входам блока 29 контроля четности и к пятому и шестому входам кодера 30 соответственно, выходы которого объединены в первую и вторую группы выходов, первая группа выходов подключена к первой группе входов декодера 31, выход которого подключен к первому входу блока 32 синхронизации и является информационным выходом системы, второй выход кодера .30 подключен к вторым входам декодера 31 и блока 32 синхронизации, выход которого подключен к управляющему входу кодера 30, объединенные первый тактовый вход и тактовый вход декодера являются первым тактовым входом приемной стороны, тактовый вход блока 32 узловой синхронизации является вторым тактовым входом приемной стороны, второй тактовый вход кодера является тактовым входом приемной стороны, тактовые входы блока .28 сравнения, блока 29 контроля четности, коммутатора 25 и третий тактовый вход кодера объединены и являются четвертым тактовым входом приемной стороны.Система передачи информации перфорированным сверточным кодом работает следующим. образом.На передающей стороне первый кодер 1 формирует канальные последовательности С 1 и С 2, соответствующие входной информационной последовательности, которые поступают с частотой 1 т на вход второго кодера, где они записываются в два соответствующих девятиразрядных регистра 33; 34 сдвига, В конце каждого девятого тактового импульса (1/9 т) блок 35 ключей открывается и осуществляется параллельная запись двенадцати символов С 1, С 2 в регистры 36, 37, 38 сдвига с частотой 1 с = 4/9 1 т, причем выбор этих переписываемых символов определяется. матрицей перфорированного кода, задаваемой связями блока 35 ключей между входными 33, 34 и выходными 36, 37, 38 регистрами сдвига. На выходе второго кодера 2 получаем код ХУ, который с частотой 4/9 бт поступает на вход преобразователя 3 кода в фазу, где происходит преобразование входного кода в соответствующий фазовый сигнал и подаче его на модулятор 4, работа преобразователя 3 кода в фазу поясняется таблицей,На приемной стороне принятый сигнал поступает на вход четырехфазного демодулятора 6 с блоком восстановления несущей. Выходные сигналы Х 1 и У 1 с четырехфазного демодулятора 6 поступают одновременно на первый 7 и второй 8 селекторы знака сигнала, первый 9 и второй 10 блоки масштабирования сигнала, коэффициент которыхравен 0,707, на первый 11 и второй 12 сумматоры. Выходы первого 9 и второго 10 блока масштабирования сигнала соединены с входами первого 14 вычитателя и третьего 13 сумматора, где осуществляется преобра зование выходных сигналов четырехфэзного демодулятора по формуле:/2 У 2 1/2У 2 = Х 1 - +% - = - (Х 1+ У 1),22 2т.е. происходит поворот координатных осейХ 1 и У 1 на 45 (см.рис,4).15С выхода третьего 13 сумматора.и первого 14 вычитателя сигнал поступает на вто-.рые входы первого 11 и второго. 12сумматоров соответственно, выходные сигналы которых поступают на блоки 18 и 19 20выделения модуля, Осуществляется вычитание модулей соответственно для символовХ и У по формуле:вх = (Х 1+ Х 2)ву = (У 1+ У 2) 25Модуль символа 2, определяемый каквг = (вх - ву).вычисляется вторым 26 вычитателем и седьмым 27 блоком выделения модуля.Определение знаков символов Х, У осущЕствляется в системе координат Х 1, У 1 или. Х 2, У 2, для чего в каждой системе координатопределяется максимальное значение модулей символов Х 1, У 1 блоками 15, 16, 17(вах/Х 1/, /У 1/) и символов Х 2, У 2 блоками 3520, 21,.24 (вах/Х 2/, /У 2/), после. сравнениякоторых в блоке 28 сравнения вырабатывается логический сигнал управления (О или 1),выправляющий коммутатором 25,Если вах(/Х 1/, /У 1/- тэх 1/Х 2/, /У 2/) 0, 40.то = 1 и на выходе коммутатора 25 появятся сигналы, соответствующие знакам символов Х 1 и У 1, т.к Ях = Ях 1 и Яу = Яу 1.Если вах(/Х 1/, /У 1/) - вах(/Х 2/, /У 2/)О,то ф = 0 на выходе коммутатора 25 45ЯХ = ЯХ 2 Яу = ЯУ 2Знак третьего символа Е выделяется вблоке 29 определения четности сложениемлогических сигналов Ях, Яу и ф по модулю 2Яг = ЯхЯув 4, 50Полученные таким образом модули сигналов и знаки символов Х, У,Е поступают насоответствующие входы кодера 30, гдепоследовательность принятых символов,соответствующих выделенной фазе, преобразуется в последовательность ветвей сигналов выколотого сверточного кода,которая затем декодируется декодером 31 скодовой скоростью В = 3/4. Разделение последовательности символов на ветви осуществляется методом перебора возможных вариантов блоком 32 синхронизации, первый вход которого соединен с выходом декодера 31, а второй вход со знаковым выходом Ях кодера 30 сигнала, При правильной синхронизации на выходе декодера 31 будет выделяться информация, полностью совпадающая с в "1 ной информацией системы, задержанной на гзал, В случае неправильной узловой сид;ронизации на выходе блока 32 синхронизации будет вырабатываться сигнал ошибки, управляющийсдвигом фазы в кодере 30 сигнала.Поясним функционирование системы на конкретном примере, На фиг. 4 а изображена фазовая плоскость и ансамбль передаваемых сигналов Х, У, Е, При приеме этот ансамбль разделяется на двэ подансамбля, как показано на фиг, 4 б, в. Направления осей Х, У в подансамблях выбраны таким образом, чтобы знаки. символов Ях и Яу были равны "нулю" при положительных проекциях принятого сигнала наоси Х, У и единице - при отрицательных проекциях, Знак символа 2 (Яг) выбирается равным "нулю", если принятый сигнал находится ви И квадрантах (см.фиг, 4 г) и "единице" - вои у квадрантах при условии, что система координат Х 2 У 2 повернута на угол л/8.Из фиг. 4 г видно, что при фазовом угле, равном 67,5, знак символа может быть принят равновероятно как за "ноль", так и за "единицу". Допустим, что на передающей стороне был выработан код 010 (точка 2 на фиг. 4 е). На приемной стороне принят вектор 7, соответствующий некоторому фазовому углу р, Обозначим проекции принятого вектора на оси Х 1, У 1 и Х 2, У 2 как Ох 1 и ОУ 1 Ох 2, ОУ 2. Из примера на фиг, 4 а видно, чтоОУ 1Ох 1Ох 2ОУ 2иОУ 1-Ох 2О, следовательно ф = 1,. В этом случае выбирается система координат Х 1 У 1, в которой при Ох 10 Ях = 0 при ОУ 10 Яу = 1, знак Яг определяется как Яг = ЯХВЯу 9 . Модули сигналов определяем из выражений;,вХ= ОХ 1+ ОХ 2ву =ОУ 1 + ОУ 2вг =,вх - вуНа фиг,5 приведены энергетические характеристики системы передачи информации неперфорированным сверточным кодом с восьмифазовой модуляцией для скорости В 1=3/4 и В 2 = 2/3. Энергетический выигрыш составляет 1,6 дБ для В 1=3/4 и 2,2 дБрля В 2 = 2/3 при вероятности ошибки 10 по сравнению с безызбыточной передачей информации и четырехфазной моду1795499 10 15 ллцией Гропускнэя способность системы при Г 1=: 3/4 увеличивается на 13% по сравнению с прототипом (82 = 2/3) и восьмифазн Ой модуляцией), К достоинствам Гподладемой системы относятся:1) 1 ОВшение пропускной способности системы с восьмифазной модуляцией за счет возможности применения перфорированного сверточного кода с кодовыми скоростями, большими, чем кодовая скорость В = 2/3, используемая в прототипе, т,е, возможные кодовые скорости: Р =-3/4,4/5,5/6 и т.д.2) Использование простых арифметических (сложение, вычитание) и логических Формула изобретения.Система передачи информации перфорироваа ым сверточным кодом с восьмифазной модуляцией, содержащая на передающей стороне первый кодер, вход которого является информационным входом системы, преобразователь кода в фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на и иемной стороне - демодулятор с бгокол впсс ановления несущей, вход котоооГо является выходом линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является иформационным выхо . дом системы, тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны, о т л и ч а о щ а я с я тем, что, с целью повышения пропускной способности системы, в нее введены на передающей стороне второй кодер, первый и второй выходы первого кодера подключены к первом/ и второму информационным входам второго кодера, первый, второй и третий выходы которого подключены к первом, второму и третьему информационным вхсдм преобразователя кода в фазу соответственно, первый и второй тактовые входы второго кодера являются первым и вторым тактовь- ми входами передающей стороны соответственно, на приемной стороне - селекторы знака сигнала, блоки выделения модуля сигнала. блоки вьделения максимума сигналов, блоки масштабирования сигнала, сумматоры, вьитатели, блок сравнения, блок контроля четности, кодер И коммутатор, первый Вь.од демодулятора с блоком восстэОВ;ив ВсуЬВЙ ГОдключе) к Обье(сложение по модулю два) операций для определения модуля.и знака сигнала при отсутствии операций типа умножения и извлечения корня в процессе вычисления метрик символов позволяет существенно повысить быстродействие си:.-"-.ъ . и упростить ее реализацию,3) Возможность адекватного расчленения принимаемого сигнала на три составляющие его метрики по каждому двоичному символу позволяет обеспечить высокие энергетические характеристики приема информации,диненным первому входу первого суммато- "ра, входу первого блока масштабирования,игнала, входу первого блока выделения модуля сигнала и входу первого селектора знакэ сигнала, второй вход демодулятора с 6:жом восстановления несущей подключен к объедиенным первому входу второго сумма гсра, входу второго блока масштабирования сигнала, входу второго блока выделения модуля сигнала и входу второго селектора знака сигнала. выходы первого и второго блоков выделения модуля сигналов подключены к первому и второму входам первого блока выделения максимума сигналов соот-, ветственно, выход которого подключен к первому входу блока сравнения, выходы первого и второго селекторов знака сигналов подключены к первому и второму информационным входам коммутатора соответственно, выход первого блока масштабирования сигнала. подключен к первым входам третьего сумматора и первого вычитателя, выход первого сумматора черезтретий блок Выделения модулясигнала подключен к первым входам кодераи второго вычитателя, выход второго сумматора через четвертый блок выделения модуля сигнала. подключен к вторым входам кодера и второго вычислителя, выход третьего сумматора подключен к второму входу второго сумматора, через пятый блок выделения модуля сигнала к первому входу второго блока выделения максимума сигналов и через тре, тий селектор знака сигналов к третьему информационному входу коммутатора, выход первого вычитзтеля подключен к второму входу первого сумматора, через шестой блок выделения модуля сигнала - к второму входу второго блока выделения максимума сигналов и через четвертый селектор знака сигнала - к четвертому информационному Входу коммутатора, ВыхОд вторОГО Вычитэтеля через седьмой блок выделения модуля сигнала подключен к третьему входу кодера, выход второго блока выделения максимума сигналов подключен к второму входу блока сравнения, выход которого подключен к управляющим входам коммутатора и блока контроля четности, выход последнего подключен к четвертому входу кодера, первый и второй выходы коммутатора подключены к первому и второму входам блока контроля четности и к пятому и шестому входам кодера соответственно, выходы первой и второй групп выходов и первый выход которого подключены к соответствующим входам декодера. второй выход кодера подключен к вторым входам декодера и блока синхронизации, выход которого подключен к управляющему входу кодера, первый тактовый вход последнего является первым тактовым входом приемной стороны, второй тактовый вход кодера является третьим тактовым входом приемной стороны, тактовые входы блока сравнения, блока контроля четности, коммутатора и третий тактовый вход кодера объединены и являются четвертым тактовым входом приемной стороны.1795499 О г.Г ставитель И.Кузне хред М.Моргентал Корректор А.Обручар то Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 10 Заказ 433 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раущская наб 4/5

СмотретьЗаявка

4810592, 03.04.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИБОРОСТРОЕНИЯ

ХАЦКЕЛЕВИЧ ЯКОВ ДАВЫДОВИЧ, ДУБОВА ТАМАРА ФЕДОРОВНА, БЕРЕЗКИН ВЛАДИМИР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G08C 19/28

Метки: восьмифазной, информации, кодом, модуляцией, передачи, перфорированным, сверточным

Опубликовано: 15.02.1993

Код ссылки

<a href="https://patents.su/9-1795499-sistema-peredachi-informacii-perforirovannym-svertochnym-kodom-s-vosmifaznojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией</a>

Предыдущий патент: Передающее устройство телеуправления

Следующий патент: Устройство для передачи командной информации с рассредоточенных пунктов управления

Случайный патент: Литейная форма