Устройство для ввода в эвм дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

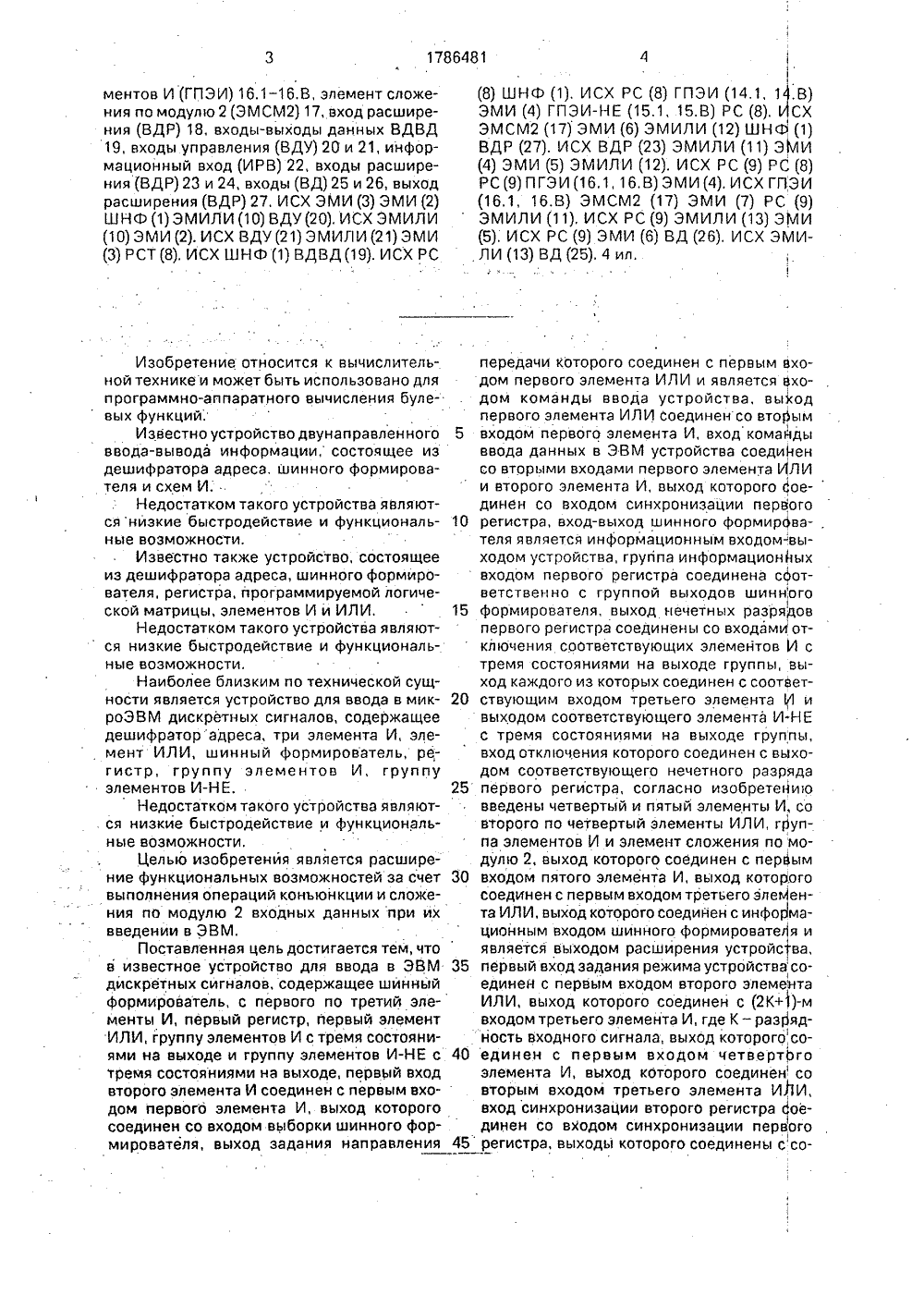

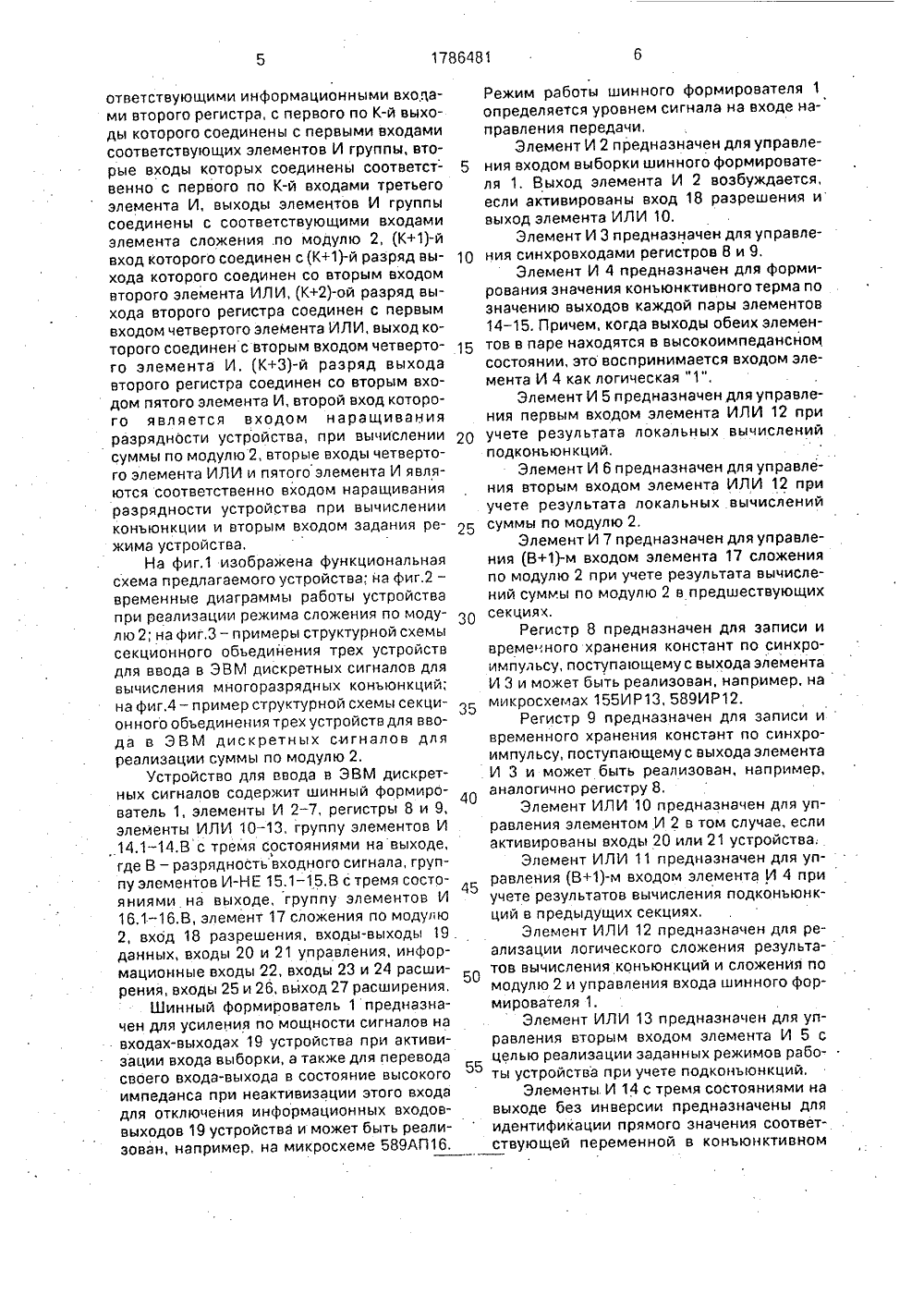

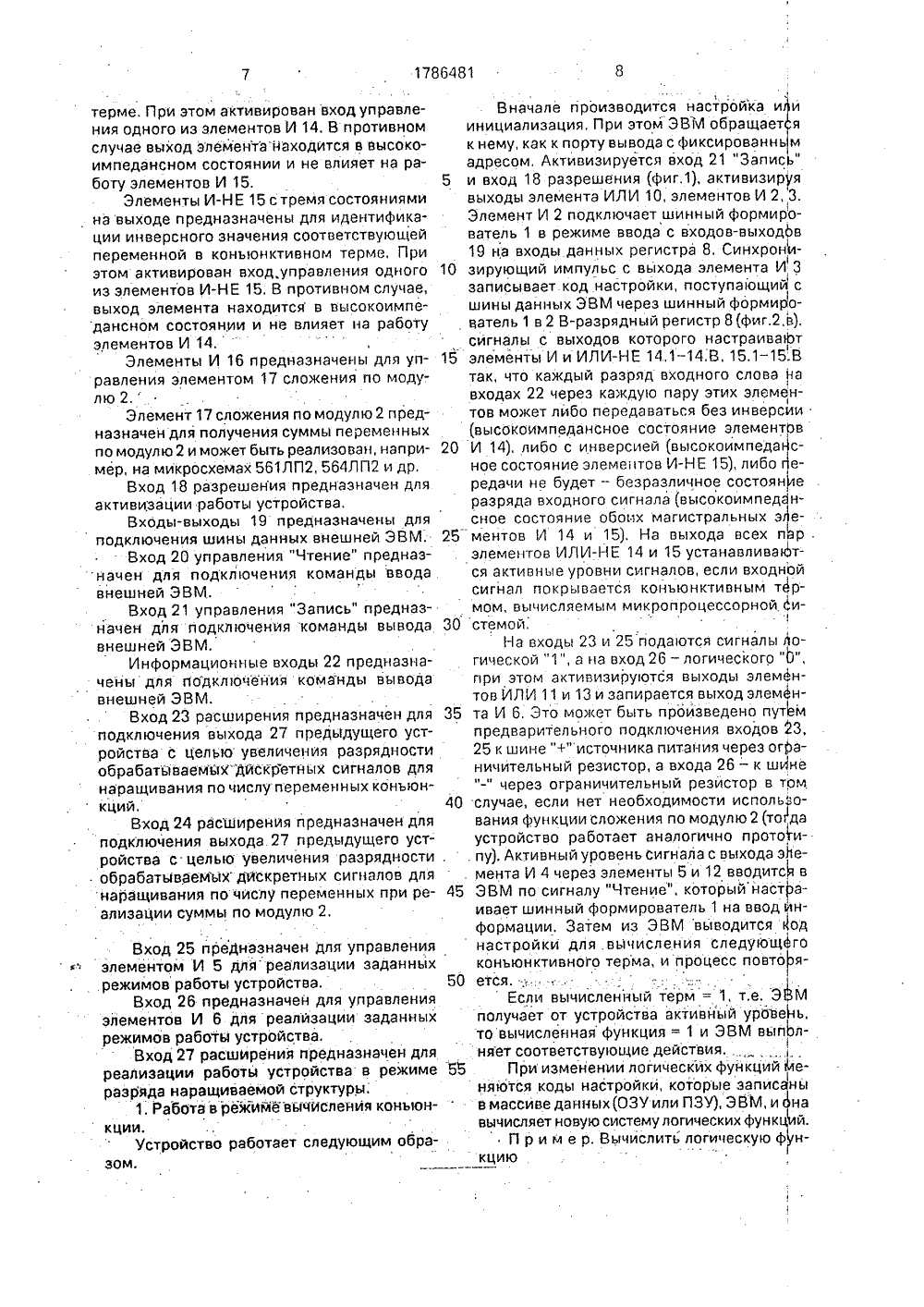

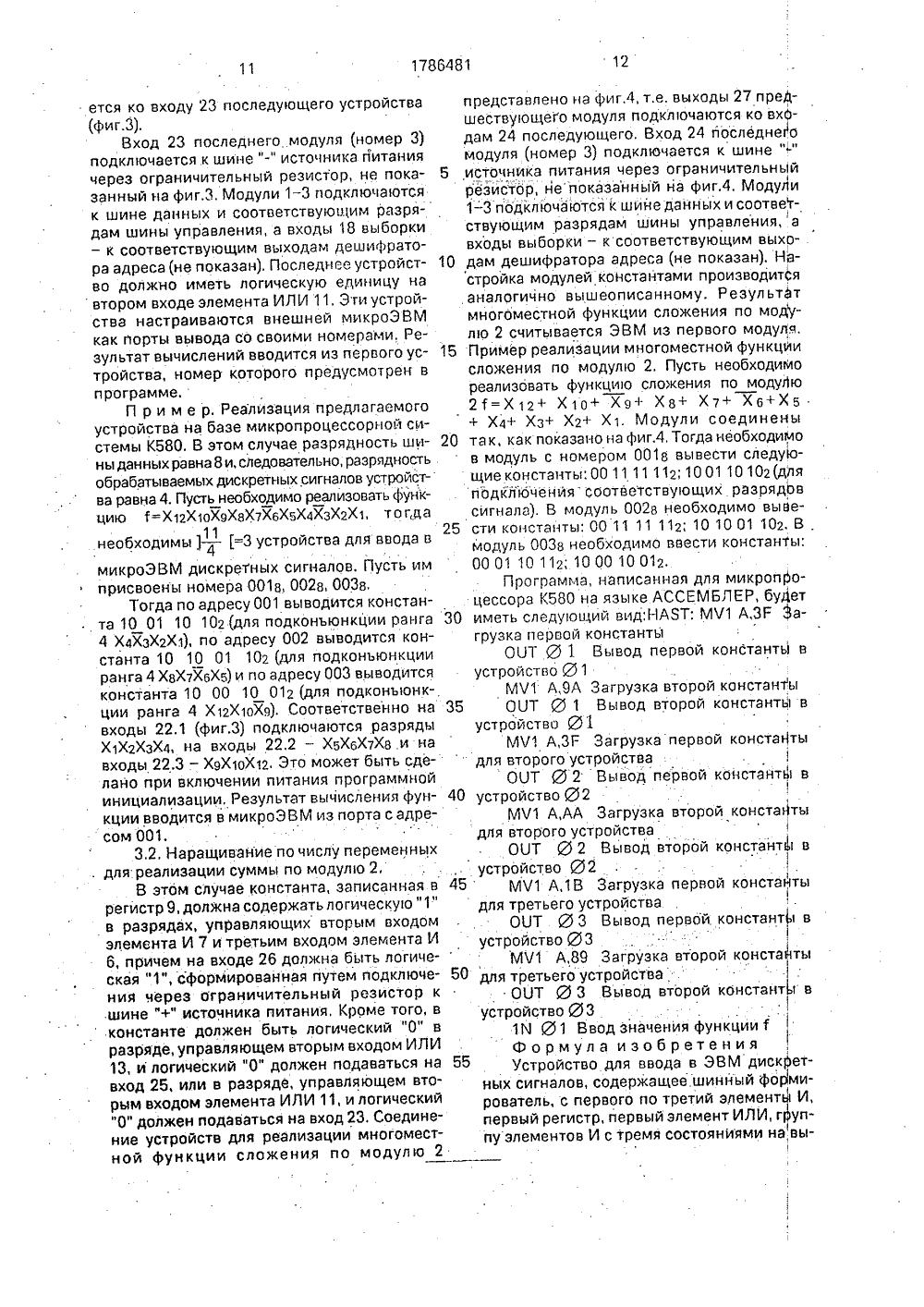

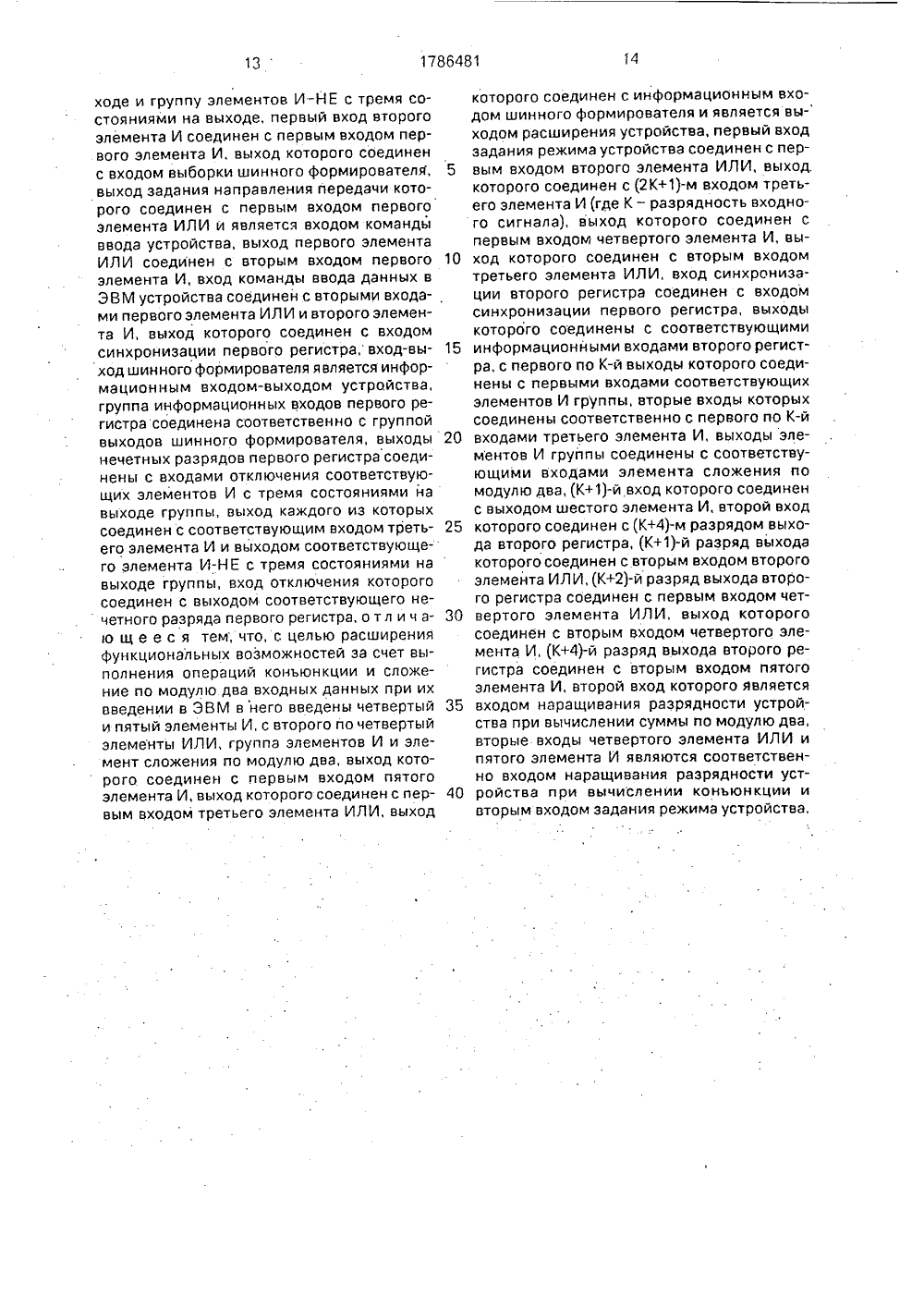

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 78648 9) .ь 2.0. 3/00, 30 АНИЕ ИЗОБРЕТ АВТОР Ф,Тюриаритонпределев микроми норм ычисли зин,нной реализапроцессорных ами ввода-вытельная техниельство СССР13/00, 1987,Я ВВОДА В ЭВМ ДИОВГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(46) 07.01,93, Бюл. М (72) В.А,Несмелов, С. А.А,Шевченко и В.А.Х (56) Иванов Г,И, О рас ции булевых функций системах с логически вода. - Автоматика и в ка, 1983, В 5, с.58,Авторское свидет М 1314375, кл. 6 06 Р (54) УСТРОЙСТВО ДЛ СКРЕТНЫХ СИГНАЛ(57) Использование: программно-аппаратное вычисление булевых функций. Цель: расширение функциональных возможностей за счет выполнения операций конъюнкции и сложения по модулю 2 входных данных при их введении в ЭВМ, Сущность изобретения: устройство содержит: шинный формирователь(ШНФ) 1, элементы И(ЭМИ) .2-7, регистры (РС) 8 и 9, элементы ИЛИ (ЭМИЛИ)10-13, группуэлементов И стремя состояниями на выходе (ГПЭИ) 14,1 - 14,В, где В - разрядность входного сигнала, группу элементов И - .НЕ с тремя состояниями на выходе (ГПЭИ-НЕ) 15.1 - 15,В, группу эле5 10 15 20 30 40 ментов И (ГПЭИ) 16.1 - 16,В, элемент сложения по модулю 2 (ЭМСМ 2) 17, вход расширения (ВДР) 18, входы-выходы данных ВДВД 19, входы управления (ВДУ) 20 и 21, информационный вход (ИРВ) 22, входы расширения (ВДР) 23 и 24, входы (ВД) 25 и 26, выход расширения (ВДР) 27. ИСХ ЭМИ (3) ЭМИ (2) ШНФ (1) ЭМИЛИ(10) ВДУ(20), ИСХ ЭМИЛИ (10) ЭМИ (2). ИСХ ВДУ(21) ЭМИЛИ (21) ЗМИ (3) РСТ(8), ИСХ ШНФ (1) ВДВД(19). ИСХ РС Изобретение относится к вычислительной технике и может быть использовано дляпрограммно-аппаратного вычисления булевых функций;Известно устройство двунаправленноговвода-вывода информации, состоящее издешифратора адреса, шинного формирователя и схем И.Недостатком такого устройства являются низкие быстродействие и функциональные возможности,Известно также устройство, состоящееиз дешифратора адреса, шинного формирователя, регистра, программируемой логической матрицы, элементов И и ИЛИ,Недостатком такого устройства являют ся низкие быстродействие и функциональные возможности,Наиболее близким по технической сущности является устройство для ввода в микроЭВМ дискретных сигналов, содержащеедешифратор адреса, три элемента И, элемент ИЛИ, шинный формирователь, регистр, группу элементов И, группуэлементов И-НЕ,Недостатком такого устройства являют. ся низкие быстродействие и функциональные воэможности.Целью изобретения является расширение функциональных возможностей за счетвыполнения операций конъюнкции и сложения по модулю 2 входных данных при ихвведении в ЭВМ,Поставленная цель достигается тем, чтов известное устройство для ввода в ЗВМдискретных сигналов, содержащее шинныйформирователь, с первого по третий элементы И, первый регистр, первый элементИЛИ, группу элементов И с тремя состояниями на выходе и группу элементов И-НЕ стремя состояниями на выходе, первый входвторого элемента И соединен с первым входом первого элемента И, выход которогосоединен со входом выборки шинного формирователя, выход задания направления(8) ШНФ (1). ИСХ РС (8) ГПЭИ (14.1, 1,В) ЭМИ (4) ГПЭИ-НЕ (15.1, 15.В) РС (8), ЧСХ ЭМСМ 2 (17) ЗМИ (6) ЭМИЛИ (12) ШНФ (1) ВДР (27). ИСХ ВДР (23) ЭМИЛИ (11) ЭМИ (4) ЭМИ (5) ЭМИЛИ (12). ИСХ РС (9) РС (8) РС(9) ПГЭИ (16,1, 16.В) ЭМИ(4). ИСХ ГПЗИ (16,1, 16.В) ЭМСМ 2 (17) ЭМИ (7) РС (9) ЭМИЛИ (11), ИСХ РС(9) ЭМИЛИ (13) ЭМИ (5); ИСХ РС (9) ЭМИ (6) ВД (26). ИСХ ЭМИЛИ (13) ВД (25). 4 ил.передачи которого соединен с первым входом первого элемента ИЛИ и является входом команды ввода устройства, выкод первого элемента ИЛИ соединен со вторым входом первого элемента И, вход команды ввода данных в ЭВМ устройства соединен со вторыми входами первого элемента ИЛИ и второго элемента И, выход которого соединен со входом синхронизации первого регистра, вход-выход шинного формирОвателя является информационным входом-выходом устройства, группа информационных входом первого регистра соединена соответственно с группой выходов шинного формирователя, выход нечетных разрядов первого регистра соединены со входами отключения соответствующих элементов И с тремя состояниями на выходе группы, выход каждого из которых соединен с соответствующим входом третьего элемента И и выходом соответствующего элемента ИНЕ с тремя состояниями на выходе группы, вход отключения которого соединен с выходом соответствующего нечетного разряда первого регистра, согласно изобретению введены четвертый и пятый элементы И, со второго по четвертый элементы ИЛИ, группа элементов И и элемент сложения по модулю 2, выход которого соединен с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соедийен с информационным входом шинного формирователя и является выходом расширения устройства, первый вход задания режима устройствасоединен с первым входом второго элемента ИЛИ, выход которого соединен с (2 К+1)-м входом третьего элемента И, где К - разрядность входного сигнала, выход которогосоединен с первым входом четвертрго элемента И, выход которого соединен со вторым входом третьего элемента И 4 И, вход синхронизации второго регистра соединен со входом синхронизации первого 45 регистра, выходы которого соединены ссо 1786481ответствующими информационными входами второго регистра, с первого по К-й выходы которого соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены соответст- венно с первого по К-й входами третьего элемента И, выходы элементов И группы соединены с соответствующими входамиэлемента сложения .по модулю 2, (К+1)-йвход которого соединен с (К+1)-й разряд выхода которого соединен со вторым входомвторого элемента ИЛИ, (К+2)-ой разряд выхода второго регистра соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, (К+3)-й разряд выходавторого регистра соединен со вторым входом пятого элемента И, второй вход которого является входом наращивания разряднОсти устройства, при вычислениисуммы по модулю 2, вторые входы четвертого элемента ИЛИ и пятого элемента И являются соответственно входом наращивания разрядности устройства и ри вычисленииконъюнкции и вторым входом задания режима устройства,На фиг.1 изображена функциональная схема предлагаемого устройства.; на фиг,2 - временные диаграммы работы устройства при реализации режима сложения по модулю 2; на фиг,3 - примеры структурной схемы секционного объединения трех устройствдля ввода в ЭВМ дискретных сигналов длявычисления многоразрядных конъюнкций; на фиг.4 - пример структурной схемы секционного объединения трех устройств для ввода в ЭВМ дискретных сигналов для реализации суммы по модулю 2,Устройство для ввода в ЭВМ дискретных сигналов содержит шинный формирователь 1, элементы И 2 - 7, регистры 8 и 9, элементы ИЛИ 10 - 13, группу элементов И 14,1 - 14. В с тремя состояния ми на выходе, где В - разрядность входного сигнала, группу элементов И-НЕ 15.1 - 15.В с тремя состояниями на выходе, группу элементов И16,1 - 16.В, элемент 17 сложения по модулю 2, вход 18 разрешения, входы-выходы 19 данных, входы 20 и 21 управления, информационные входы 22, входы 23 и 24 расширения, входы 25 и 26, выход 27 расширения,Шинный формирователь 1 предназначен для усиления по мощности сигналов на входах-выходах 19 устройства при активизации входа выборки, а также для переводасвоего входа-выхода в состояние высокого импеданса при неактивизации этого входадля отключения информационных входов- выходов 19 устройства и может быть реализован, например, на микросхеме 589 АП 16, 5 10 Режим работы шинного формирователя 1 определяется уровнем сигнала на входе направления передачи.Элемент И 2 предназначен для управления входом выборки шинного формирователя 1, Выход элемента И 2 возбуждается, если активированы вход 18 разрешения и выход элемента ИЛИ 10.Элемент И 3 предназначен для управления синхровходами регистров 8 и 9. Элемент И 4 предназначен для формирования значения конъюнктивного терма позначению выходов каждой пары элементов14 - 15. Причем, когда выходы обеих элементов в паре находятся в высокоимпедансномсостоянии, это воспринимается входом элемента И 4 как логическая "1".Элемент И 5 предназначен для управления первым входом элемента ИЛИ 12 при20 учете результата локальных вычисленийподконъюнкций,Элемент И 6 предназначен для управления вторым входом элемента ИЛИ 12 приучете результата локальных вычислений25 суммы по модулю 2,Элемент И 7 предназначен для управления (В+1)-м входом элемента 17 сложенияпо модулю 2 при учете результата вычислений суммы по модулю 2 в предшествующих30 секциях,Регистр 8 предназначен для записи ивреме,ного хранения констант по синхроимпульсу, поступающему с выхода элементаИ 3 и может быть реализован, например, намикросхемах 155 ИР 13, 589 ИР 12,Регистр 9 предназначен для записи ивременного хранения констант по синхроимпульсу, поступающему с выхода элементаИ 3 и может быть реализован, например,40 аналогично регистру 8Элемент ИЛИ 10 предназначен для управления элементом И 2 в том случае, еслиактивированы входы 20 или 21 устройства;Элемент ИЛИ 11 предназначен для управления (В+1)-м входом элемента И 4 приучете результатов вычисления подконъюнкций в предыдущих секциях,Элемент ИЛИ 12 предназначен для реализации логического сложения результа-тов вычисления конъюнкций и сложения помодулю 2 и управления входа шинного формирователя 1.Элемент ИЛИ 13 предназначен для управления вторым входом элемента И 5 сцелью реализации заданных режимов работы устройства при учете подконъюнкций,Элементы. И 14 с тоемя состояниями навыходе без инверсии предназначены дляидентификации прямого значения соответствующей переменной в конъюнктивномтерме. При этом активирован вход управления одного из элементов И 14. В противном случае выход элементанаходится в высокоимпедансном состоянии и не влияет на работу элементов И 15.Элементы И-НЕ 15 с тремя состояниями на выходе предназначены для идентификации инверсного значения соответствующей переменной в коньюнктивном терме, При этом активирован вход. управления одного из элементов И-НЕ 15, В противном случае, выход элемента находится в высокоимпедансном состоянии и не влияет на работу элементов И 14,Элементы И 16 предназначены для управления элементом 17 сложения по модулю 2,тЭлемент 17 сложения по модулю 2 и редназначен для получения суммы переменных по модулю 2 и может быть реализован, например, на микросхемах 561 ЛП 2, 564 ЛП 2 и др.Вход 18 разрешения предназначен для активизации работы устройства.Входы-выходы 19 предназначены для подключения шины данных внешней ЭВМ.Вход 20 управления "Чтение" предназначен для подключения команды ввода внешней ЭВМ,Вход 21 управления "Запись" предназначен для подключения команды вывода внешней ЭВМ,Информационные входы 22 предназначены для подключения командь 1 вывода внешней ЭВМ.Вход 23 расширения предназначен для подключения выхода 27 предЫдущего устройства с целью увеличения разрядности обрабатываемйх "дйскретйых сигналов для наращивания по числу переменных конъюнкций.Вход 24 расширения предназначен для подключения выхода. 27 предыдущего устройства с целью увеличения разрядности обрабатываемыхдйскретных сигналов для наращивания по числу переменных при реализации суммы по модулю 2,Вход 25 преДназначен для управления элементом И 5 длят" реализации заданных режимов работы устройства,Вход 26 предназначен для управления элементов И 6 дляреализации заданных режимов работы устройства,Вход 27 расширения предназначен для реализации работы устройства в режиме разряда наращиваемой структуры,1, Работа в режимевйчисслеийя конъюнкции.Устройство работает следующим образом.Вначале производится настройка и и инициализация, При этом ЭВМ обращает я к нему, как к порту вывода с фиксированнь м адресом, Активизируется вход 21 нЗапис " 5 и вход 18 разрешения (фиг.1), активизируя выходы элемента ИЛИ 10, элементов И 2, 3. Элемент И 2 подключает шинный формирователь 1 в режиме ввода с входов-выходов 19 на входы данных регистра 8, Синхронй зирующий импульс с выхода элемента И 3 записывает код.настройки, поступающий с шины данных ЭВМ через шинный формиро 1 ватель 1 в 2 В-разрядный регистр 8 (фиг.2,в), сигналы с выходов которого настраивают 15 элементы И и ИЛИ-НЕ 14,1 - 14.В, 15,1-15,В так, что каждый разряд входного слова на входах 22 через каждую пару этих элемен 1 тов может либо передаваться без инверсии . (высокоимпедансное состояние элементов 20 И 14), либо с инверсией (высокоимпедайсное состояние элементов И-НЕ 15), либо гередачи не будет - безразличное состоянле разряда входного сигнала (высокоимпед 4 нсное состояние обоих магистральных эе ментов И 14 и 15). На выхода всех пар . элементов ИЛИ-НЕ 14 и 15 устанавливантся активные уровни сигналов, если входной сигнал покрывается конъюнктивным термом, вычисляемым микропроцессорной. Си стемой,На входы 23 и 25 подаются сигналы логической н 1", а на вход 26 - логического н 0", при этом активизируются выходы элемЕнтов ИЛИ 11 и 13 и запирается выход элем 4 н та И 6, Это может быть произведено путем предварительного подключения входов 23, 25 к шине н+" источника питания через ограничительный резистор, а входа 26 - к шине "-" через ограничительный резйстор в том 40 случае, если нет необходимости использования функции сложения по модулю 2 (тогда устройство работает аналогично протоги. пу), Активный уровень сигнала с выхода эле. мента И 4 через элементы 5 и 12 вводитс в 45 ЭВМ по сигналу "Чтение". которыйнастраивает шинный формирователь 1 на ввод иинформации, Затем из ЭВМ выводится код настройкй для.вычисления следующего конъюнктивного терма, и процесс повто я етсяЕсли вычисленный терм = 1, т,е, Элей получает от устройства активййй уровень, то вычисленная функция = 1 и ЭВМ выпЬлняет соответствующие действия, 55 При изменении логических функций меняются коды настройки, которые записаны а массиве данных(ОЗУ или ПЗУ), ЭВМ, и на вычисляет новую систему логических функ Ьй.П р и м е р. Вычислить логическую ф нкцию40 45 50 55 1=аЬс ч ОКоды настроек, которые выносятся в массив данных, будут иметь следующий вид:10 10 10 002 = М 1; 00 00 00 012 = М 2;00 01 00 002= Мз. Программанаписанная для микропроцессора К 580, на языке АССЕМБЛЕР будет иметь следующий вид;РРА: .Х 1 Н, 1 ТАВЕ Инициализация памятиС 1.С; МОЧ А, М Взять маску К ООТ РОВТ 1 Программировать устройство маской К1 М РОВТ 1 Ввести значение терма ОВА А Установить флагиИЕ ЕС Закончить вычисления, если терм =01 ЙХ Н,Модифицировать память ЗОВ А Обнуление ААОО М Проверка окончания данных И 2 С 1 С Вычислить очередной терм ЕС 1; МЧ 1 С, ЯЯ Вычисленный терм= ЯМР МО Переход на метку "функция = Я ЕС 1 2: МЧ 1 С, 01 Вычисленная функция =1, С=11 МР М 1 Переход на метку "функция =1" ТАВ 1, ОВ А 8,4 Я,ЯЯЕМОЗдесь в исходных данных 00 - маркер окончания таблицы данных.Таким образом, устройство работает аналогично работе прототипа,2, Работа в режиме вычисления суммы по модулю 2.В этом режиме на вход 25 подается сиг. нал логического нуля, а на вход 26 - логической единицы аналогично вышеописанному (фиг.1). ЭВМ, обращаясь к устройству как к порту вывода, производит двукратную выдачу констант по адресу, активизирующему вход 18, При этом вначале константа записывается в регистр 8 (фиг.2, г) по заднему фронту синхроимпульса на выходе элементе 3 И (фиг,2, в), затем при выдаче второй константы первая переписывается в регистр 9 (фиг.2,д), а вторая записывается в регистр 8 (фиг,2, г), т,к, входы синхрониза.ции регистров объединены, В первой константе используется В+4 разряда, где В - разрядность входа 22, Во второй константе используются 2 В разрядов, так как было описано выше, Вторая константа с выхода регистра 9 управляет группой элементов И 16, элементами ИЛИ 11 и 13, элементами И 6 и 7. Если нет необходимости расширения разрядности обрабатываемых дискретных сигналов, то на второй вход элемента И 7 с выхода регистра 9 должен поступать логический нуль, а на второй вход элемента ИЛИ 11 - логическая "1". 5 10 15 20 25 30 35 На третий вход элемента И 6 для производства вычислений только по модулю 2 подается сигнал логической "1", а на второй вход элемента ИЛИ 13 - сигнал логического "0". На входы элементов И 16 группы подаются нули в том случае, если соответствующий разряд входного сигнала не участвует в образовании суммы по модулю 2. С целью вычисления суммы по модулю 2 от. инверсии входных сигналов должны быть с помощью константы в регистре 8 подключены соответствующие элементы И-НЕ 15 с тремя состояниями на выходе. При вычислении суммы по модулю 2 от инверсируемых значений входных разрядов должен быть подключен соответствующий элемент И 14 группы с тремя состояниями на выходе. Ес-ли разряд входного сигнала 22 не участвует в образовании суммы по модулю 2, то состояние соответствующих. элементов И 14, ИНЕ 15 может быть произвольно (естественно, кроме запрещенного, когда одновременно подключены оба элемента), Тогда элемент 17 сложения по модулю 2 формирует сумму по модулю 2 (фиг.2,з) от заданных разрядов входного сигнала 22 (включая и заданные инверсии) (фиг.2,ж) и передает вычисленные значения через элемент 6 И и элемент 12 ИЛИ на вход 27 (фиг,2, е) и вход шинного формирователя 1 и по шине данных 19 (фиг,2, а) - во внешний микропроцессор.3. Работа в режиме разряда наращиваемой структуры.3.1, Наращивание по числу переменных конъюнкций,В этом случае константа, выведенная в регистр 9, должна подавать логический "0" на второй вход элемента ИЛИ 11 (фиг.1), Кроме того, на третий вход элемента И 6 подается логический "0" для подключения формирования суммы по модулю 2, на второй вход элемента ИЛИ 13 подается логическая "1" для подключения элемента И 5, В этом случае настройка группы элементов И 14 и И-НЕ 15 аналогична режиму 1. Однако элемент И 4 формирует логическую "1" только в том случае, если на вход 23 поступит логическая "1" с выхода 27 аналогичного устройства для ввода дискретных сигналов, настроенного на вычисление второй подконьюнкции в том случае, если разрядности одного устройства не достаточно (естественно, подконъюнкция, вычисляемая первым устройством, также должна покрывать свою долю разрядов входных сигналов). Для вычисления многоразрядных конъюнкций устройства для ввода дискретных сигналов подключаются последовательно, т.е. выход 27 предшествующего устройства подключа 1786481ется ко входу 23 последующего устройства (фиг.З).Вход 23 последнего модуля (номер 3) подключается к шине "-" источника питания через ограничительный резистор, не показанный на фиг.З, Модули 1 - 3 подключаются к шине данных и соответствующим разрядам шины управления, а входы 18 выборки - к соответствующим выходам дешифратора адреса (не показан). Последнее устройство должно иметь логическую единицу на втором входе элемента ИЛИ 11, Эти устройства настраиваются внешней микроЭВМ как порты вывода со своими номерами, Результат вычислений вводится из первого устройства, номер которого предусмотрен в и рограмме.П р и м е р. Реализация предлагаемого устройства на базе микропроцессорной системы К 580. В этом случае разрядность шины данных равна 8 и, следовательно, разрядность обрабать 1 ваемых дискретных сигналов устройства равна 4. Пусть необходимо реализовать функцию т=Х 12 Х 1 оХоХвХ 7 ХБХвХ 4 ХэХ 2 Хь то гда необходимы ) - =З устройства для ввода в11микроЭВМ дискретных сигналов, Пусть им присвоены номера 0018, 002 в, 003 в,Тогда по адресу 001 выводится константа 10 01 10 102(для подконьюнкции ранга 4 Х 4 ХэХ 2 Х 1), по адресу 002 выводится константа 10 10 01 102 (для подконьюнкции ранга 4 ХэХ 7 ХбХ 5) и по адресу 003 выводится константа 10 00 10 012 (для подконьюнкции ранга 4 Х 12 Х 1 оХэ). Соответственно на входы 22.1 (фиг,З) подключаются разряды Х 1 Х 2 ХзХ 4, на входы 22.2 - ХБХоХ 7 Ха и на входы 22.3 . - ХэХ 1 оХ 12, Это может быть сделано при включении питания программной инициализации, Результат вычисления функции вводится в микроЭВМ из порта с адресом 001.3,2, Наращивайие по числу переменных . для реализации суммы по модулю 2,В этом случае константа, записанная в регистр 9, должна содержать логическую "1" в разрядах, управляющих вторым входом элемента И 7 и третьим входом элемента И 6, причем на входе 26 должна быть логическая "1", сформированная путем подключения через ограничительный резистор к шине "+" источника питания, Кроме того, в константе должен быть логический "0" в разряде, управляющем вторь 1 м входом ИЛИ 13, илогический "0" должен подаваться на вход 25, или в разряде, управляющем вторым входом элемента ИЛИ 11, и логический "0" должен подаваться на вход 23. Соединение устройств для реализации многоместной функции сложения по модулю 2представлено на фиг,4, т,е. выходы 27 предшествующего модуля подключаются ко вхО- дам 24 последующего, Вход 24 йоследнего модуля (номер 3) подключается к шине 5 источника питания через ограничительный резистор, непоказанный на фиг.4. Модули 1 - 3 подключаются к шйне данных и соотвеТствующим разрядам шины управления, а входы выборки - к соответствующим выходам дешифратора адреса (не показан). На 10 стройка модулей констайтами производитСя аналогично вышеописанному. Результат многоместной функции сложения по модулю 2 считывается ЭВМ из первого модуля. Пример реализации многоместной функции сложения по модулю 2, Пусть необходимо реализовать функцию сложения по модулю 2 т=Х 12+ Х 1 о+ Х 9+ Ха+ Х 7+ Хб+Х 5+ Х 4+ Хэ+ Х 2+ Х 1. Модули соединены 20 так, как показано на фиг,4, Тогда необходимо в модуль с номером 001 в вывести следующие константы: 00 11 11 112; 10 01 10 102 (для иодключения соответствующих разрядов сигнала). В модуль 002 з необходимо вывести константы: СО 11 11 112; 10 10 01 102. В 25 модуль 003 з необходимо ввести константы устройство Я 1 МЧ 1 А,ЗГ Загрузка первой константы для второго устройства .ООТ Я 2 Вывод первой константы в устройство 02МЧ 1 А,АА Загрузка второй константы 40 для второго устройстваООТ Я 2 Вывод второй константй в устройство Я 2МЧ 1 А,1 В Загоузка первой константы для третьего устройстваООТ Я 3 Вывод первой. констант в устройство 03МЧ 1 А,89 Загрузка второй константы для третьего устройстваООТ Я 3 Вывод второй константьг в устройство ЯЗ1 Й 01 ВвоД значения функции 1 Формула изобретения Устройство для ввода в ЭВМ дискретных сигналов, содержащее.шинйый формирователь, с первого по третий элементв И, первый регистр, первый элемент ИЛИ, группу элементов И с тремя состояниями на,вы 00 01 10 112; 10 00 10 012Программа, написанная для микропроцессора К 580 на яэь 1 ке АССЕМБЛЕР, будет 30 иметь следующий вид;НАЯТ; МЧ 1 А,ЗР Загрузка пероой константыООТ 01 Вывод первой константь вустройство Я 1МЧ 1 А,9 А Загрузка второй константы 35 ООТ Я 1 Вывод второй константц входе и группу элементов И-НЕ с тремя состояниями на выходе, первый вход второго элемента И соединен с первым входом первого элемента И, выход которого соединен с входом выборки шинного формирователя, 5 выход задания направления передачи которого соединен с первым входом первого элемента ИЛИ и является входом команды ввода устройства, выход первого элемента ИЛИ соединен с вторым входом первого 10 элемента И, вход команды ввода данных в ЭВМ устройства соединен с вторыми входами первого элемента ИЛИ и второго элемента И, выход которого соединен с входом синхронизации первого регистра,вход-вы ход шинного формирователя является информационным входом-выходом устройства, группа информационных входов первого регистра соединена соответственно с группой выходов шинного формирователя, выходы 20 нечетных разрядов первого регистра соединены с входами отключения соответствующих элементов И с тремя состояниями на выходе группы, выход каждого из которых соединен с соответствующим входом треть его элемента И и выходом соответствующего элемента И-НЕ с тремя состояниями на выходе группы, вход отключения которого соединен с выходом соответствующего нечетного разряда первого регистра, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения операций конъюнкции и сложение по модулю два входных данных при их введении в ЭВУ внего введены четвертый 35 и пятый элементы И, с второго по четвертый элементы ИЛИ, группа элементов И и элемент сложения по модулю два, выход которого соединен с первым входом пятого элемента И, выход которого соединен с пер вым входом третьего элемента ИЛИ, выход которого соединен с информационным входом шинного формирователя и является вы- ходом расширения устройства, первый вход задания режима устройства соединен с первым входом второго элемента ИЛИ, выход, которого соединен с (2 К+1)-м входом третьего элемента И (где К - разрядность входного сигнала), выход которого соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, вход синхронизации второго регистра соединен с входом синхронизации первого регистра, выходы которого соединены с соответствующими информационными входами второго регистра, с первого по К-й выходы которого соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены соответственно с первого по К-й входами третьего элемента И, выходы элементов И группы соединены с соответствующими входами элемента сложения по модулю два, (К+1)-й вход которого соединен с выходом шестого элемента И, второй вход которого соединен с (К+4)-м разрядом выхода второго регистра, (К+1)-й разряд выхода которого соединен с вторым входом второго элемента ИЛИ, (К+2)-й разряд выхода второго регистра соединен с первьм входом четвертого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, (К+4)-й разряд выхода второго регистра соединен с вторым входом пятого элемента И, второй вход которого является входом наращивания разрядности устройства при вычислении суммы по модулю два, вторые входы четвертого элемента ИЛИ и пятого элемента И являются соответственно входом наращивания разрядности устройства при вычислении конъюнкции и вторым входом задания режима устройства,1786481 2 Р 1 Составитель В.Наз Техред М,Моргент Корректор М,дндрущ дактор изводственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 10 аз 248 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4813523, 11.04.1990

ПЕРМСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА В. И. ЧУЙКОВА

НЕСМЕЛОВ ВЛАДИМИР АРКАДЬЕВИЧ, ТЮРИН СЕРГЕЙ ФЕОФЕНТОВИЧ, НАЗИН ВЛАДИМИР ИВАНОВИЧ, ШЕВЧЕНКО АНАТОЛИЙ АЛЕКСЕЕВИЧ, ХАРИТОНОВ ВАЛЕРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 3/00, G06F 3/023

Метки: ввода, дискретных, сигналов, эвм

Опубликовано: 07.01.1993

Код ссылки

<a href="https://patents.su/9-1786481-ustrojjstvo-dlya-vvoda-v-ehvm-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода в эвм дискретных сигналов</a>

Предыдущий патент: Тригонометрический преобразователь

Следующий патент: Устройство для ввода в микроэвм дискретных сигналов

Случайный патент: Устройство для моделирования систем дифференциальных уравнений гиперболического