Устройство для ввода в микроэвм дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

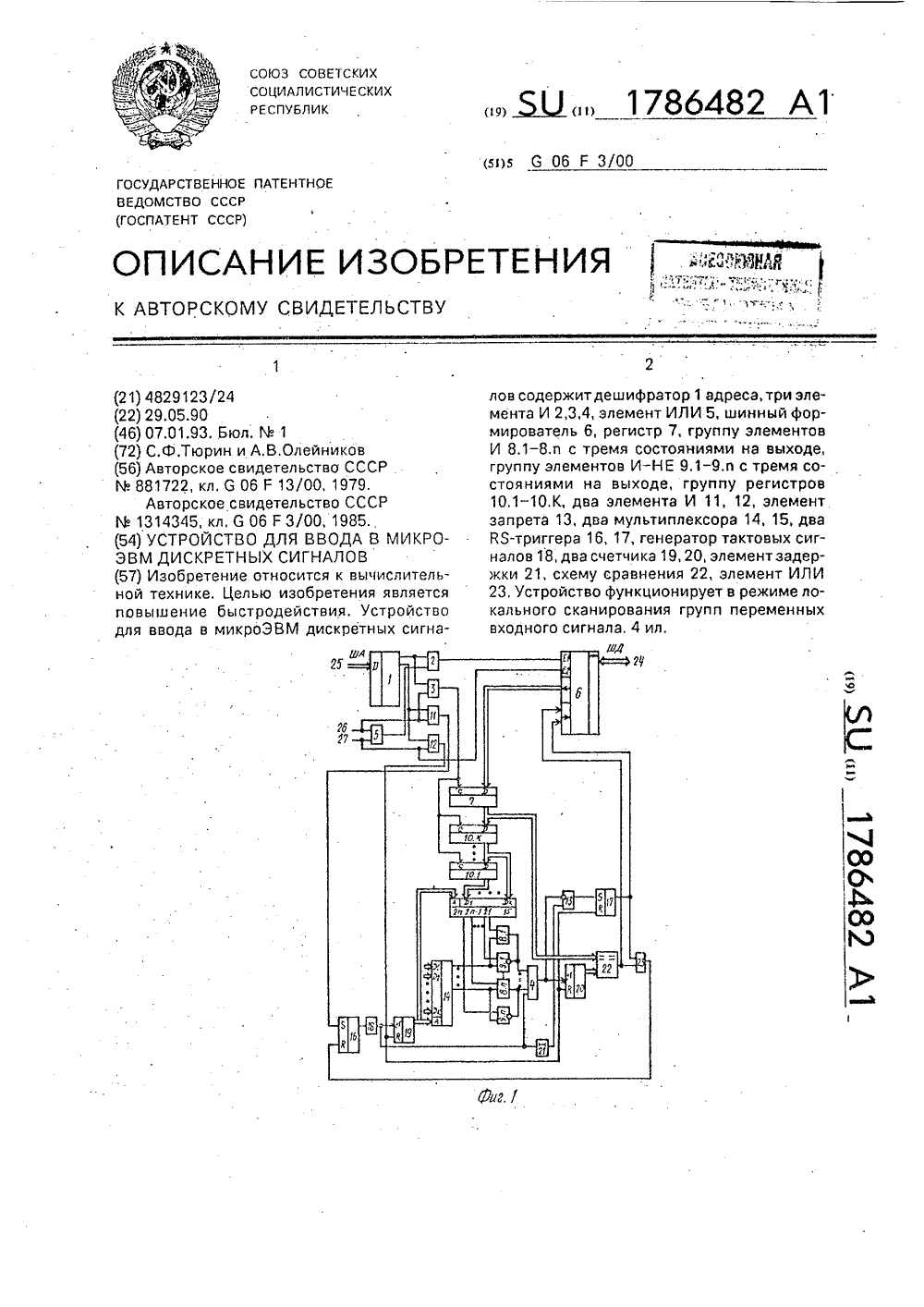

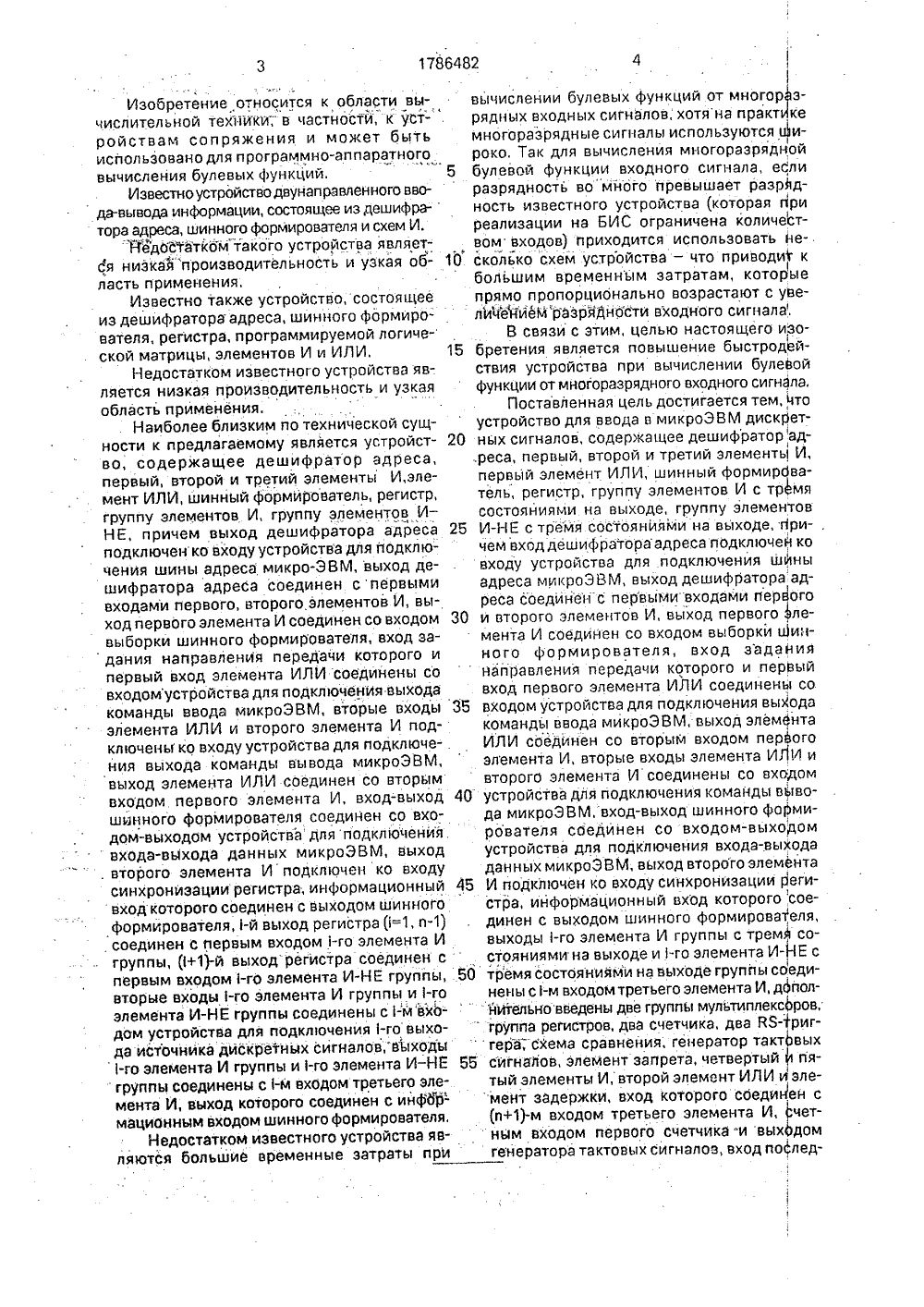

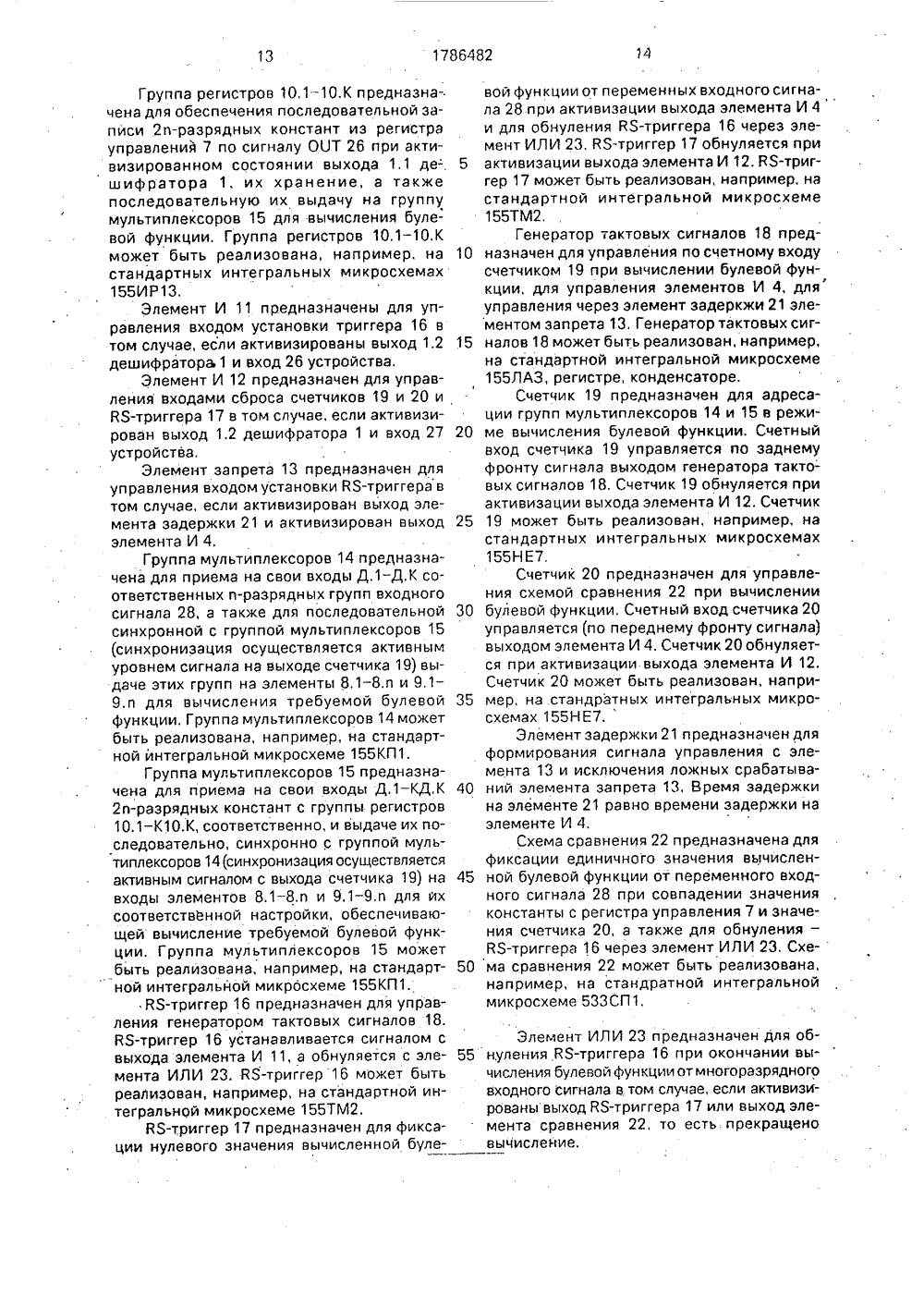

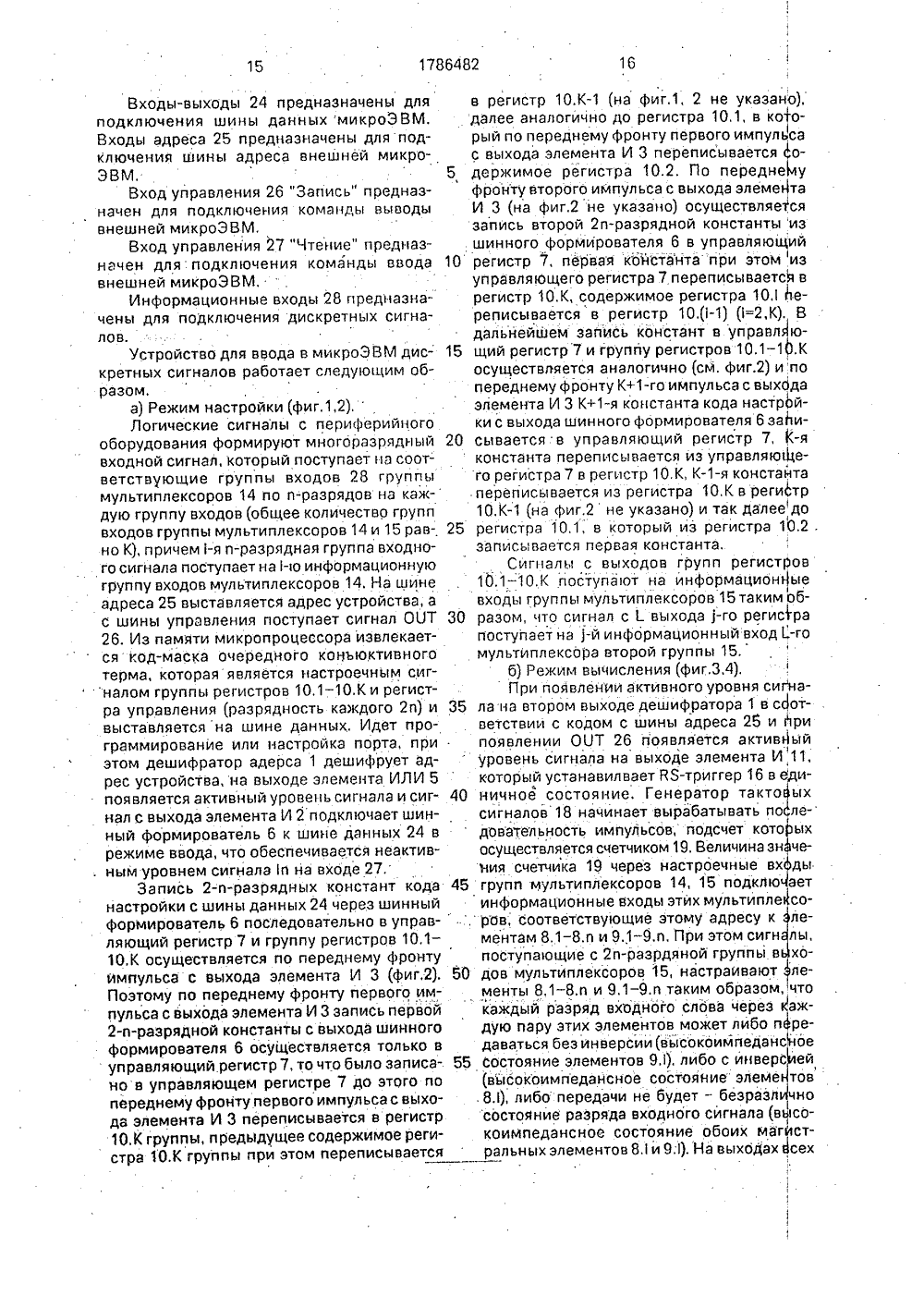

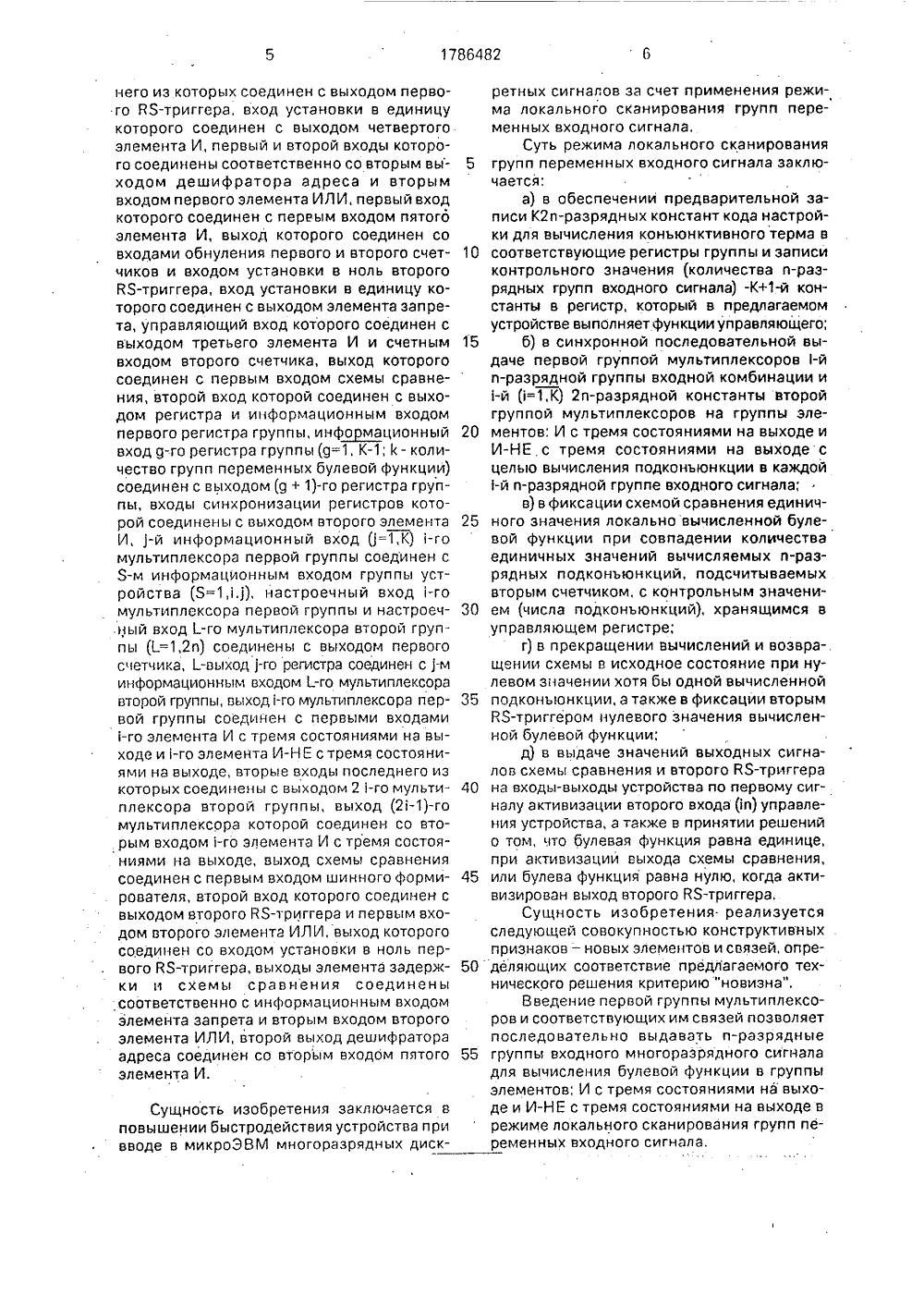

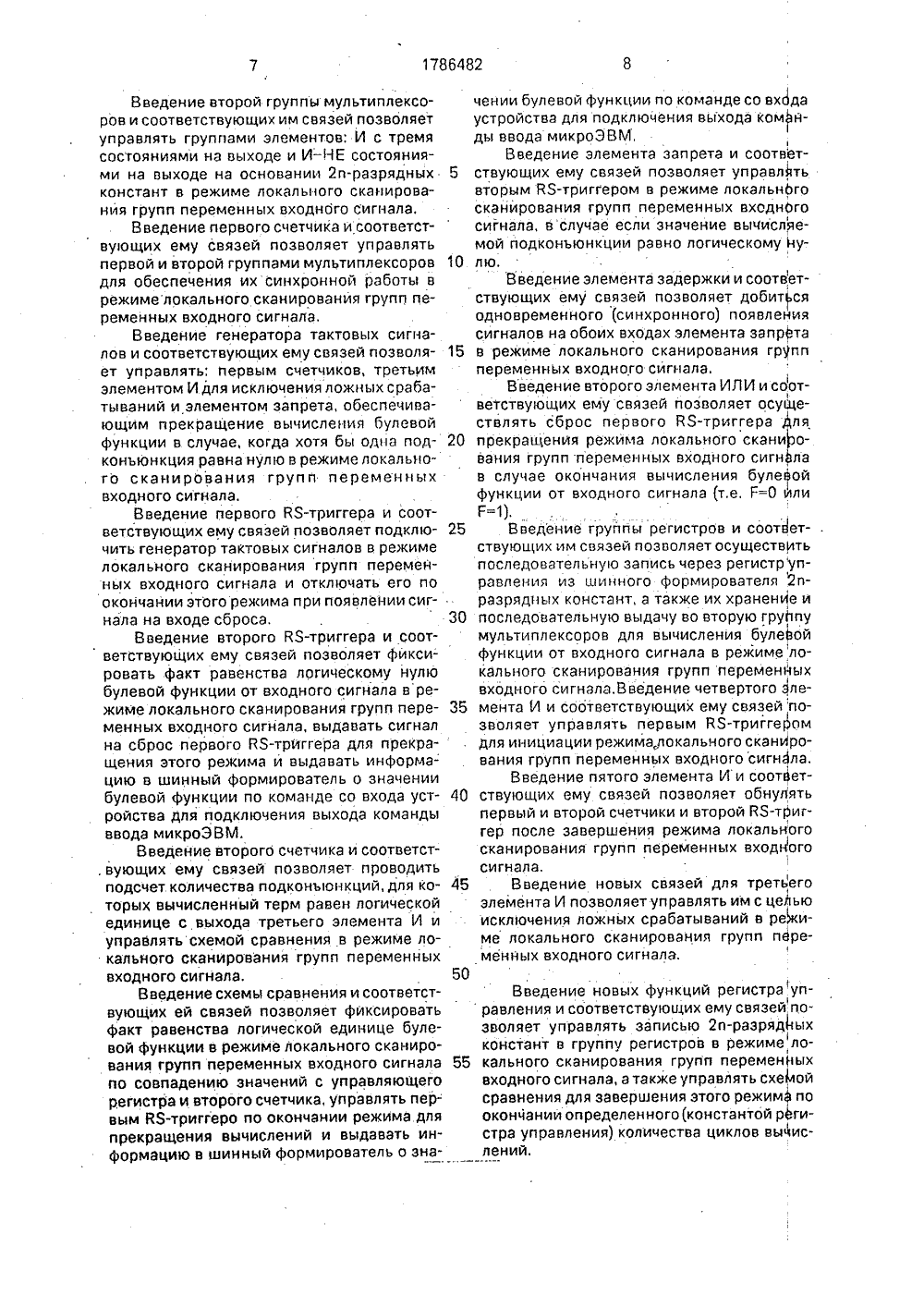

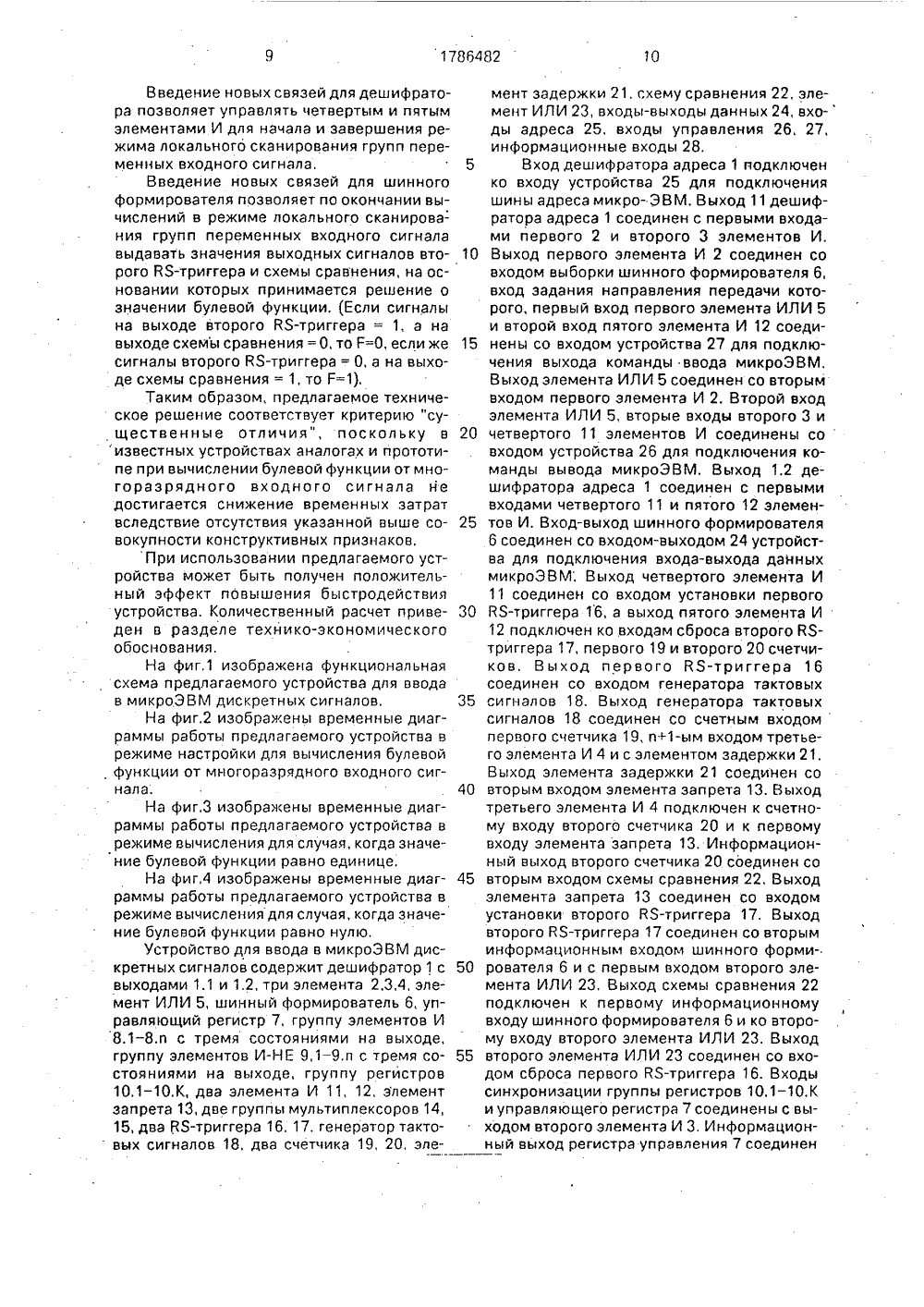

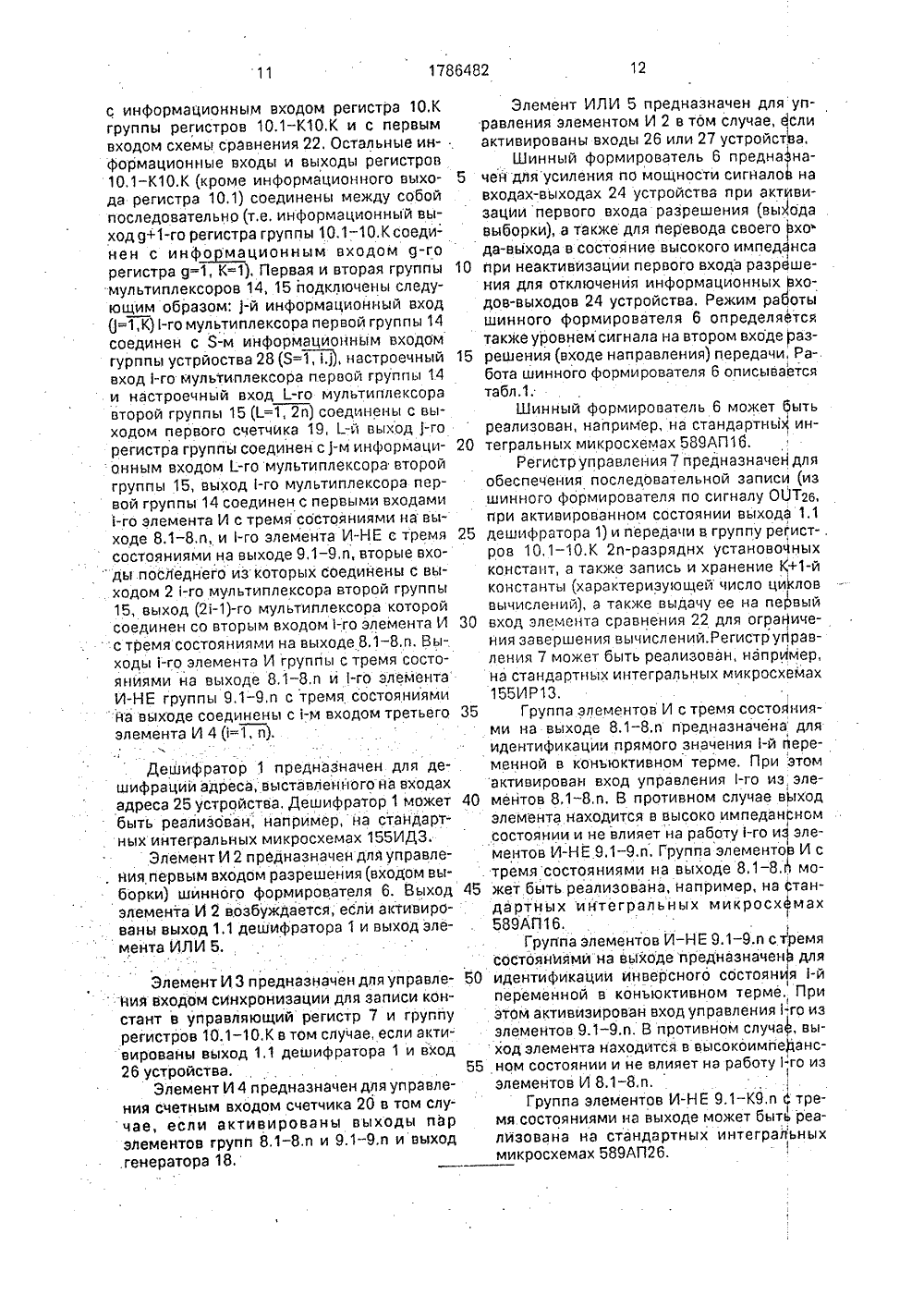

";сРОЮ ГОСУДАРСТВЕННОЕ ПАТЕНТВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) САНИЕ ИЗО ВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1(56) Авторское свидетельство СССР М 881722, кл, 0 06 Р 13/00, 1979.Авторское свидетельство СССР М 1314345, кл, 6 06 Р 3/00, 1985.(54) УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ(57) Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия, Устройство для ввода в микроЭВМ дискретных сигналов содержит дешифратор 1 адреса, три элемента И 2,3,4, элемент ИЛИ 5, шинный формирователь 6, регистр 7, группу элементов И 8.1 - 8,п с тремя состояниями на выходе, группу элементов И - НЕ 9.1 - 9,п с тремя состояниями на выходе, группу регистров 10.1-10,К, два элемента И 11, 12, элемент запрета 13, два мультиплексора 14, 15, два ЯЯ-триггера 16, 17, генератор тактовых сигналов 18, два счетчика 19, 20, элемент задержки 21, схему сравнения 22, элемент ИЛИ 23, Устройство функционирует в режиме локального сканирования групп переменных входного сигнала, 4 ил.МОЧ А, М; К 1 записать в аккумуляторпроцессора ООТ РОВТ 1; Записать константу 1-ю врегистр управления 7 1 ИХН; Определить адрес константы 2-й МОЧ А, М, К 2 записать в аккумулятор ООТ РОВТ 1; Записать константу 2-ю врегистр управления 7, 1,-ю в регистр 10.К11 цХ Н; Определйть адрес константы КМОЧА, М; К+1 записать в аккумулятор ООТ РОВТ 1; Записать константу К+1-ю в регистр управления 7, )-ю в регистр 10,)Программа вычисленияРВО: ОПТ РОВТ 2; установка триггера 16 М 1: 1 И РОВТ 1; ввод сигналов с ВЯ- триггера 17 и схемы сравнения 22ОВА; установка флагов1 Е М 1; переход, если вычисления не завершеныСР 1 002; сравнить с константой 002 12 М 2; перейти на М 2, конъюнкция и Г=-1 1 Е МЗ; перейти на МЗ, конъюнкция и Г=О ТАВ 11: ОВ, А 5. 66, 5 А, 00, 03ТАВ 12: ОВ 48, 88, 00, 00, 02ЕМОДля обнуления ВЯ-триггера 16, счетчиков 19,20 ЮРОВТ 2; обнуление ВЯ-триггера 16, счетчиков 19, 20Дпя вычисления другой логической функции, зависящей от 16 переменных при использовании четырехвходовых мультиплексоров заменяются исходные данные,Г 2= Х 1 Х 2 ХиХ 16 Ч Х 6 Х 6 ХОХ 1 о- для первой конъюнкции01 10 00 00= К 1(подконъюнкция Х 1 Х 2) 00 ОО ОО 00 = К 200 ОО ОО 00 = КЗ00 01 ОО 10 =. К 4 (подконъюнкция ХиХм)00 00 01 00 = Купр- для второй конъюнкции00 00 00 00 = К 110 01 00 01 = К 2 (подконъюнкция Х 5 Х 6 Хв)00 10 00 00 = КЗ (подконъюнкция Х 1 о)00 00 00 ОО=К 4ОО 00 00 11 = КупрТАВ 1 1: ОВ 60, 00, 00, 12, 04ТАВ 1 2: ОВ 00, 91, 20, 00, 03.Технико-зкономическую эффективность устройства можно оценить коэффициентом сокращения временных затрат при вычислении конъюнктивного терма для многоразрядного входного сигнала, который будет определяться по формуле:5 10 ЬКоЪ1 где ь - время для вычисления булевой функции прототипом;Ь - время для вычисления булевой фуН- кции данного устройства;К - колицество устройств прототипа, необходимых для вычисления булевой функции от многоразрядного входного сигналЭ,Поскольку то - г зо +чтогде газо - время записи кода настройки прототипа; бто - время считывания результатОввычисления прототипа;исп =ало(К+1)+чт 1,где пю - время считывания результатов вЫцислений предлагаемым устройством,д 730 К + ччто К2 Т 0ао 1 к+т 5+е;Поскольку ччто = гчт 1, то коэффициентсокращения временных зэтратдля К 2 больше единицы, причем с увеличением К он возрастает пропорционально,Таким образом, для вычисления бу 4 евой функции от многоразрядного входногосигнала данное устройство позволяет Сократить временные затраты, поскольку Нетребует программногоопроса каждого уСтройства (как это происходит при выцисЛении булевой функции от многоразрядндговходного сигнала).Формула изобретенияУстройство для ввода в микроЭВМ дискретных сигналов, содержащее дешифратор адреоа, первый, второй и третийэлементы И, первый элемент ИЛИ, шинныйформирователь, регистр, группу элементовИ с тремя состояниями на выходе, группу40 элементов И-НЕ с тремя состояниями навыходе, причем вход дешифратора адресасоединен с шиной адреса микроЭВМ, первый выход дешифраторэ адреса соединей спервымивходами первого и второго элементов И, выход первого элемента И соединен с входом разрешения выборки шинногоформирователя, вход разрешения заданиянаправления передачи которого и первыйвход первого элемента ИЛИ соединенФ свходомпризнака команды ввода даннныхмикроЭВМ, выход первого элемента ИЛИсоединен с вторым входом первого элемента И, вторые входы первого элемента И 1 Ии второго элемента И соединены с входомпризнака команды вывода данных микроЭВМ, вход-выход шинного формирователясоединен с входом-выходом устройства, выход второго элемента И соединен с входомсинхронизации регистра, ифнормационныйвход которого соединен с выходом шиннЬго121 1786482 22 регистра группы ц=.1,К, К - количество групп переменных булевой функции) соединен с информационным входом о-го регистра группы, входы синхронизации регистров 5 которой соединены с выходом второго элемента И, )-й информационный вход 1)=1,К) 1-го мультиплексора первой группы соединен с Я-м информационным входом группы устройства (Я=Щ); настроечный вход 1-го 10 мультиплексора первой группы и настроечный вход 1:го мультиплексора второй группы (1 =1,2 п) соединены с выходом первого счетчика, 1:й) выход )-го регистра группы соединен с )-м информационным входом 1: 15 го мул ьтиплексора второй груп и ы, выход 1 го мультиплексора первой группы соединен с первыми входами 1-го элемента И с тремя состояниями на выходе и 1-го элемента И-НЕ стремя состояниями на выходе, вторые вхо ды последнего из которых соединены с выходом 2 1-го мультиплексора второй группы, выход (1-1)-го мультиплексора которой соединен с вторым входом 1-го элемента И с тремя состояниями на выходе, выход схемы 25 сравнения соединен с первым входом шинного формирователя, второй вход которого соединен с выходом второго ВЯ-триггера и первым входом второго элемента ИЛИ, выход которого соединен с входом установки 30 в "0" первого ВЯ-риггера, выходы элементазадержки и схемы сравнения соединены соответственно с информационным входом элемента запрета и вторым входом второго элемента ИЛИ, второй выход дешифратора 35 адреса соединен с вторым входом пятогоэлемента И,Таблица 1 Состояние вхо ов Е 2 (вход направления передачиЕ 1 (вход выборки) О 0 0 Таблица 2 формирователя, выходы 1-го элемента И с тремя состояниями на выходе группы (1=1,п, и-разрядность группы переменных) и 1-го элемента И-НЕ с тремя состояниями на выходе группы соединены с 1-м входом третьего элемента И, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит две группы мультиплексоров, группу регистров, два счетчика, два КЯ-триггрера, схему сравнения, генератор тактовых сигналов, элемент ЗАПРЕТ, четвертый и пятый элементы И, второй элемент ИЛИ и элемент задержки, вход которого соединен с (и+1)-м входом третьего элемента И, счетным входом первого счетчика и выходом генератора такто.вых сигналов, вход последнего из коорых соединен с выходом первого ВЯ-триггера, вход установки в "1" которого соединен с выходом четвертого элемента И, первый и второй входы которого соединены соответственно с вторым выходом дешифратора адреса и вторым входом первого элемента ИЛИ, первый вход которого соединен с первым входом пятого элемента И, выход которого соединен с входами обнуления первого и второго счетчиков и входом установки в "0" второго ЙЯ-триггера, вход установки в "1" которого соединен с выходом элемента запрета, управляющий вход которого соединен с выходом третьего элемента И и счетным входом второго счетчика, выход которого соединен с первым входом схемы сравнения, второй вход которой соединен с выходом регистра и информационным входом первого регистра группы, выход(у+1)-го Работа шинного формирователя 6Выходы-входы шинного формирователя 6 в высокоимпедансном состоянии Передача сигнала со входа устройства 24 в регистр упавления 7 Передача сигнала с выхода триггера 17 и элемента сравнения 22 на вход устройства241786482 гг Ялг Ф ль А,ОлейниковМоргентал Корр ор Е.Папп Реда кто аз 248 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при113035, Москва, Ж, Раушская наб., 4/5 Т СССРПроизводственно-издательскии комбин Состав ТехредИзобретение о-,носится к области вычислительной техники;" в частностй, к уст- .ройствам сопряжения и может бытьиспользовано для программно-аппаратноговычисления булевых функций. 5Известноустройстводвунаправленного ввода-вывода информации, состоящее из дешифратора адреса, шинного формирователя и схем И.Йеддсгатком такого устройства является низкаяпроизводительность и узкая область применения,Известно также устройство, состоящееиз дешифратораадреса, шинного формирователя, регистра, программируемой логической матрицы, элементов И и ИЛИ, 15Недостатком известного устройства является низкая производительность и узкаяобласть применения.Наиболее близким по технической сущности к предлагаемому является устройство, содержащее дешифратор адреса,первый, второй и третий элементы И,элемент ИЛИ, шинный формйрователь, регистр,группу элементов И, группу элементов И -НЕ, причем выход дешифратора адреса 25подключен ко входу устройства для подключения шины адреса микро-ЭВМ, выход де 30 команды ввода микроЭВМ, вторые входы 35 входом первого элемента И, вход-выход 40шйнного формирователя соединен со входом-выходом устройства для подключения. первым входом 1-го элемента И-НЕ группы, 50вторые входы 1-го элемента И группы и 1-го шифратора адреса соединен с первыми входами первого, второго элементов И, выход первого элемента И соединен со входом выборки шинного формирователя, вход за дания направления передачи которого и первый вход элемента ИЛИ соединены со входомустройства для подключения выхода элемента ИЛИ и второго элемента И подключены ко входу устройства для подключения выхода команды вывода микроЭВМ,выход элемента ИЛИ соединен со вторым входа-выхода данных микроЭВМ, выход второго элемента И подключен ко входу синхронизации регистра; информационный вход которого соединен с выходом шинного формирователя, 1-й выход регистра (=1, и) соединен с первым входом 1-го элемента И группы, (+1)-й выход регистра соединен с элемента И-НЕ группы соединены с 1-мвходом устройства для подключения 1-го выхода источника дискретных сигналов,выходы 1-го элемента И группы и 1-го элемента И-НЕ группы соединены с 1-м входом третьего элемента И, выход которого соединен с информационным входом шинного формирователя. Недостатком известного устройства являются большие временные затраты при вычислении булевых функций от многоразрядных входных сигналов, хотяна практике многоразрядные сигналы используются иироко, Так для вычисления многоразрядной булевой функции входного сигнала, если разрядность во много превышает разрядность известного устройства (которая при реализации на БИС ограничена количеством входов) приходится использовать не-.сколько схем устройства - что приводи 1 к большим временным затратам, которые1прямо пропорционально возрастают с увелич"ениемразрядности входного сигнала,В связи с этим, целью настоящего изобретения является повышение быстродействия устройства при вычислении булевой функций от многоразрядного входного сигнала,Поставленная цель достигается тем, чтоустройство для ввода в микроЭВМ дискретных сигналов, содеркащее дешифраторад,реса, первый, второй и третий элементь И, первый элемент ИЛИ, шинный формирОватель, регистр, группу элементов И с тремя состояниями на выходе, группу элементов И-НЕ с тремя состояниями на выходе, т 1 ри- .чем вход дешифратораадреса подключен ко входу устройства для подключения шины адреса микроЭВМ, выход дешифратора адреса соедйнен-с первыми входами перого и второго элементов И, выход первого лемента И соединен со входом выборки шинного формирователя, вход задаНия направления передачи которого и первый вход первого элемента ИЛИ соединены со входом устройства для подключения выХода команды ввода микроЭВМ, выход элемента ИЛИ соединен со вторым входом первого элемента И, вторые входы элемента ИЛИ и второго элемента И соединены со входом устройства для подключения команды вывода микроЭ В М, вход-выход шинного формирователя соединен со входом-выходом устройства для подключения входа-выхода данных микроЭВМ, выход второго элемента 5 И подключен ко входу синхронизации регистра, информационный вход которого соединен с выходом шинного формирователя, выходы 1-го элемента И группы с тремя состояниями на выходе и 1-го элемента И-НЕ с тремя состояниями на выходе группы соединены с 1-м входом третьего элемента И, дОпол"нительно введены две группы мультиплексоров, " группа регистров, два счетчика, два ВЯ-триггера,схема сравнения, генератор тактовых 5 сигналов, элемент запрета, четвертыйф пятый элементы И, второй элемент ИЛИ и элемент задержки, вход которого соединен с (и+1)-м входом третьего элемента И, четным входом первого счетчика и выходом генератора тактовых сигналов, вход поблед 13 1786482Группа регистров 10,1 - 10,К предназначена для обеспечения последовательной записи 2 п-разрядных констант из регистрауправления 7 по сигналу ООТ 26 при активизированном состоянии выхода 1,1 дешифратора 1, их хранение, а такжепоследовательную их выдачу на группумультиплексоров 15 для вычисления булевой функции. Группа регистров 10,1 - 10.Кможет быть реализована, например, на 10стандартных интегральных микросхемах155 ИР 13,Элемент И 11 предназначены для управления входом установки триггера 16 втом случае, если активизированы выход 1.2 15дешифратора 1 и вход 26 устройства,Элемент И 12 предназначен для управления входами сброса счетчиков 19 и 20 иВЯ-триггера 17 в том случае, если активизирован выход 1.2 дешифратора 1 и вход 27 20устройства,Элемент запрета 13 предназначен дляуправления входом установки ВЯ-триггера втом случае, если активизирован выход элемента задержки 21 и активизирован выход 25элемента И 4,Группа мультиплексоров 14 предназначена для приема нэ свои входы Д,1-Д,К соответственных и-разрядных групп входногосигнала 28, а также для последовательной 30синхронной с группой мультиплексоров 15(синхронизация осуществляется активнымуровнем сигнала на выходе счетчика 19) выдаче этих групп на элементы 8,1 - 8,п и 9.1 -9,п для вычисления требуемой булевой 35функции, Группа мультиплексоров 14 можетбыть реализована, например, на стандартной интегральной микросхеме 155 КП 1.Группа мультиплексоров 15 предназначена для приема на свои входы Д,1 - КД,К 402 п-рэзрядных констант с группы регистров10.1 - К 10.К, соответственно, и выдаче их последовательно, синхронно с группой мультиплексоров 14 (синхронизация осуществляетсяактивным сигналом с выхода счетчика 19) на 45входы элементов 8.1 - З,п и 9,1 - 9,п для ихсоответственной настройки, обеспечивающей вычисление требуемой булевой функции. Группа мультиплексоров 15 можетбыть реализована, например, на стандартной интегральной микросхеме 155 КП 1,ВЯ-триггер 16 предназначен для управления генератором тактовых сигналов 18.ВЯ-триггер 16 устанавливается сигналом свыхода элемента И 11, а обнуляется с элемента ИЛИ 23. ВЯ-триггер 16 может бытьреализован, например, на стандартной интегральной микросхеме 155 ТМ 2.ВЯ-триггер 17 предназначен для фиксации нулевого значения вычисленной булевой функции от переменных входного сигнала 28 при активизации выхода элемента И 4 и для обнуления ВЯ-триггера 16 через элемент ИЛИ 23, ВЯ-триггер 17 обнуляется при активизации выхода элемента И 12. ВЯ-триггер 17 может быть реализован, например, на стандартной интегральной микросхеме 155 ТМ 2,Генератор тактовых сигналов 18 предназначен для управления по счетному входу счетчиком 19 при вычислении булевой функции, для управления элементов И 4, для управления через элемент задеркжи 21 элементом запрета 13, Генератор тактовых сигналов 18 может быть реализован, например, на стандартной интегральной микросхеме 155 ЛАЗ, регистре, конденсаторе.Сцетчик 19 предназначен для адресации групп мультиплексоров 14 и 15 в режиме вычисления булевой функции. Счетный вход счетчика 19 управляется по заднему фронту сигнала выходом генератора тактовых сигналов 18, Счетчик 19 обнуляется при активизации выхода элемента И 12, Счетчик 19 может быть реализован, например, на стандартных интегральных микросхемах 155 Н Е 7,Сцетчик 20 предназначен для управления схемой сравнения 22 при вычислении булевой функции. Счетный вход счетчика 20 управляется (по переднему фронту сигнала) выходом элемента И 4. Счетчик 20 обнуляется при активизации выхода элемента И 12, Счетчик 20 может быть реализован, например, на стандратных интегральных микросхемах 155 Н Е 7.Элемент задержки 21 предназначен для формирования сигнала управления с элемента 13 и исключения ложных срабатываний элемента запрета 13, Время задержки нэ элементе 21 равно времени задержки на элементе И 4.Схема сравнения 22 предназначена для фиксации единицного значения вычисленной булевой функции от переменного входного сигнала 28 при совпадении значения константы с регистра управления 7 и значения счетцика 20, а также для обнуления - ВЯ-триггерэ 16 через элемент ИЛИ 23, Схема сравнения 22 может быть реализована, например, на стандратной интегральной микросхеме 533 СП 1,Элемент ИЛИ 23 предназначен для обнуления ВЯ-триггера 16 при окончании вычисленияя булевой функции от многоразрядного входного сигнала в том случае, если активизированы выход ВЯ-триггера 17 или выход элемента сравнения 22, то есть прекращено вычисление.1786482 15 16регистр 10,К(на фиг,1, к не указанО),алее аналогично до регистра 10.1, в ко оый по переднему фронту первого импульсавыхода элемента И 3 переписывается Соеркимое регистра 10.2. По переднемуронту второго импульса с выхода элемента3 (на Фиг,2 не указано) осуществляетсяапись второй 2 п-разрядной константы изинного формирователя 6 в управляющийегистр 7, первая константа при этом изправляющего регистра 7 переписывается вегистр 10,К, содержимое регистра 10, пееписывается в регистр 10.(-1) (=2,К), Вальнейшем запись констант в управляюий регистр 7 и группу регистров 10.1 - 1.Ксуществляется аналогично (см. Фиг,2) и поереднему фронту К+1-го импульса с выходалемента И 3 К+1-я константа кода настрЬйи с выхода шинного формирователя 6 запиывается в управляющий регистр 7, К-яонстанта переписывается из управляющео регистра 7 в регистр 10,К, К-я констайтаереписывается из регистра 10.К в регистрО,К(на Фиг.2 не указано) и так далее доегистра 10.1, в который из регистра 10.2.аписывается первая константа.Сигналы с выходов групп регистров0.1 - 10.К поступают на информационалыеходы группы мультиплексоров 15 таким обазом, что сигнал свыхода )-го регистраоступает на -й информационный вход ,-гоультиплексора второй группы 15,б) Режим вычисления (фиг.3,4).При появлении активного уровня сигнаа на втором выходе дешифратора 1 в соотетствии с кодом с шины адреса 25 и приоявлении О.Т 26 появляется активныйровень сигнала на выходе элемента И 11,оторый устанавилвает ЯЯ-триггер 16 в едиичное состояние. Генератор тактовыхигналов 18 начинает вырабатывать послеовательность импульсов, подсчет которыхсуществляется счетчиком 19, Величина знфчеия счетчика 19 через настроечные вх дырупп мультиплексоров 14, 15 подклю ает информационные вхоров, соответствующиментам 8,1-8.п и 9 1 -поступающие с 2 п-ра ы этих мультипле соэтому адресу к ле,и, При этом сигнлы, рдяной группы вйхораивают ледов мультипл ксоров 15, наст менты 8.1 - 8.п и 9.1 - 9.п таким каждый разряд вхбдного слов дую пару этих элементов мож даваться без инверсии (вы око бразом,что через ажт либо премпе ансное с д ), либо с инверс е стояние- элеме то удет - безразл ного сигнала (в ентов нсное ачи не яда вхо е состо нтов 8,Состояние элем (высокоимпеда . 8.), либо перед состояние разр коимпедансно ральных элеме яние обоих магисти 9;), На выхоДах всех Входы-выходы 24 предназначены для в подключения шины данных микроЭВМ, д Входы адреса 25 предназначены для под- р ключения шины адреса внешней микро- с ЭВМ,5 дВход управления 26 "Запись" предназ- Ф начен для подключения команды выводы И внешней микроЭВМ, зВход управления 27 "Чтение" предназ- ш начен для подключения команды ввода 10 р внешней микроЭВМ, УИнформационные входы 28 предназна- р цены для подключения дискретных сигна- р лов. дУстройство для авода в микроЭВМ дис щ кретных сигналов работает следующим об- о разом, иа) Режим настройки (фиг,1,2),э Логические сигналы с периферийного к оборудования формируют многоразрядный 20 с входной сигнал, который поступает на соот- к ветствующие группы входов 28 группы г мультиплексоров 14 по и-разрядов на каж- и дую группу входов (общее количество групп 1 входов группы мультиплексоров 14 и 15 рав р но К), причем -я и-разрядная группа входно- з го сигнала поступает на -ю информационную группу входов мультиплексоров 14, На шине . 1 адреса 25 выставляется адрес устройства, а в с шины управления поступает сигнал ООТ 30 р 26. Из памяти микропроцессора извлекает- и сякод-маска очередного конъюктивного м терма, которая является настроечным сигналом группы регистров 10.1-10,К и регистра управления (разрядность какдого 2 п) и 35 л выставляется на шине данных., Идет про- . в граммирование или настройка порта, при и этом дешифратор адерса 1 дешифрует ад-у рес устройства, на выходе элемента ИЛИ 5к появляется активный уровень сигнала и сиг н нал с выхода элемента И 2 подключает шин- с ный формирователь 6 к шине данных 24 в д режиме ввода, что обеспечивается неактив- о . ным уровнем сигнала и на входе 27. нЗапись 2-и-разрядных констант кода 45 г настройки с шины данных 24 через шинный формирователь 6 последовательно в управ--, ляющий регистр 7 и группу регистров 10,1- 10,К осуществляется по переднему фронту импульса с выхода элемента И 3 (фиг.2). 50 Поэтому по переднему фронту первого импульса с выхода элемента И 3 запись первой 2-и-разрядной константы с выхода шинного формирователя 6 осуществляется только в управляющий регистр 7, то что было записа но в управляющем регистре 7 до этого по переднему фронту первого импульса с выхода элемента И 3 переписывается в регистр 10.К группы, предыдущее содержимое регистра 10.К группы при этом переписываетсянего из которых соединен с выходом первого ВЯ-триггера, вход установки в единицу которого соединен с выходом четвертого элемента И, первый и второй входы которого соединены соответственно со вторым вы- ходом дешифратора адреса и вторым входом первого элемента ИЛИ, первый вход которого соединен с первым входом пятогб элемента И, выход которого соединен со входами обнуления первого и второго счетчиков и входом установки в ноль второго ВЯ-триггера, вход установки в единицу которого соединен с выходом элемента запрета, управляющий вход которого соединен с выходом третьего элемента И и счетным входом второго счетчика, выход которого соединен с первым входом схемы сравнения, второй вход которой соединен с выходом регистра и информационным входом первого регистра группы, информационный вход о-го регистра группы (у=1, К; 1 - количество групп переменных булевой функции) соединен с выходом (9+ 1)-го регистра группы, входы синхронизации регистров которой соединены с выходом второго элемента И, -й информационный вход Д=1,К) -го мультиплексора перрой группы соединен с Я-м информационным входом группы устройства (Я=1), настроечный вход -го мультиплексора первой группы и настроечный вход :го мультиплексора второй группы : - 1,2 п) соединены с выходом первого счетчика,-выход 1-го регистра соединен с -м информационным входом :го мультиплексора второй группы, выход -го мультиплексора первой группы соединен с первыми входами -го элемента И с тремя состояниями на выходе и -го элемента И-НЕ стремя состояниями на выходе, вторые входы последнего из которых соединены с выходом 2 -го мультиплексора второй группы, выход (2-1)-го мультиплексора которой соединен со вторым входом -го элемента И с тремя состояниями на выходе, выход схемы сравнения соединен с первым входом шинного формирователя, второй вход которого соединен с выходом второго ВЯ-триггера и первым входом второго элемента ИЛИ, выход которого соединен со входом установки в ноль первого ВЯ-триггера, выходы элемента задержки и схемы сравнения соединены сОответственно с информационным входом элемента запрета и вторым входом второго элемента ИЛИ, второй выход дешифратора адреса соединен со вторым входом пятого элемента И. Сущность изобретения заключается в повышении быстродействия устройства и ри вводе в микроЭВМ многоразрядных диск 10 15 20 25 50 деляющих соответствие предлагаемого тех 55 30 35 40 45 ретных сигналов за счет применения режима локального сканирования групп переменных входного сигнала,Суть режима локального сканирования групп переменных входного сигнала заключается.а) в обеспечении предварительной записи К 2 п-разрядных констант кода настройки для вычисления конъюнктивного терма в соответствующие регистры группы и записи контрольного значения (количества и-разрядных групп входного сигнала) -К+1-й константы в регистр, который в предлагаемом устройстве выполняет функции управляющего;б) в синхронной последовательной выдаче первой группой мультиплексоров -й и-разрядной группы входной комбинации и -й (=1,К) 2 п-разрядной константы второй группой мультиплексоров на группы элементов: И с тремя состояниями на выходе и И-НЕ с тремя состояниями на выходе с целью вычисления подконъюнкции в каждой -й и-разрядной группе входного сигнала;в) в фиксации схемой сравнения единичного значения локально вычисленной булевой функции при совпадении количества единичных значений вычисляемых и-разрядных подконъюнкций, подсчитываемых вторым счетчиком, с контрольным значением (числа подконъюнкций), хранящимся в управляющем регистре;г) в прекращении вычислений и возвра-. щении схемы в исходное состояние при нулевом значении хотя бы одной вычисленной подконъюнкции, а также в фиксации вторым РЯ-триггером нулевого значения вычисленной булевой функции;д) в выдаче значений выходных сигналов схемы сравнения и второго ВЯ-триггера на входы-выходы устройства по первому сигналу активизации второго входа (и) управления устройства, а также в принятии решений о том, что булевая функция равна единице, при активизации выхода схемы сравнения, или булева функция равна нулю, когда активизирован выход второго ВЯ-триггера,Сущность изобретения реализуется следующей совокупностью конструктивных . признаков - новых элементов и связей, опренического решения критерию "новизна",Введение первой группы мультиплексоров и соответствующих им связей позволяет последовательно выдавать и-разрядные группы входного многоразрядного сигнала для вычисления булевой функции в группы элементов; И с тремя состояниями на выходе и И-НЕ с тремя состояниями на выходе в режиме локального сканирования групп переменных входного сигнала, 1786482Введение второй группы мультиплексоров и соответствующих им связей позволяет управлять группами элементов: И с тремя состояниями на выходе и И-НЕ состояниями на выходе на основании 2 п-разрядных констант в режиме локального сканирования групп переменных входного сигнала.Введение первого счетчика и соответствующих ему связей позволяет управлять первой и второй группами мультиплексоров для обеспечения их синхронной работы в режимелокального сканирования групп переменных входного сигнала,Введение генератора тактовых сигналов и соответствующих ему связей позволяет управлять; первым счетчиков, третьим элементом И для исключения ложных срабатываний и элементом запрета, обеспечивающим прекращение вычисления булевой функции в случае, когда хотя бы одна подконъюнкция равна нулю в режиме локального сканирования групп переменных входного сигнала.Введение первого ВЯ-триггера и соответствующих ему связей позволяет подключить генератор тактовых сигналов в режиме локального сканирования групп переменных входного сигнала и отключать его по окончании этого режима при появлении сигнала на входе сброса.Введение второго ЯЯ-триггера и соответствующих ему связей позволяет фиксировать факт равенства логическому нулю булевой функции от входного сигнала в режиме локального сканирования групп переменных входного сигнала, выдавать сигнал на сброс первого ВЯ-трйггера для прекращения этого режима и выдавать информацию в шинный формирователь о значении булевой функции по команде со входа устройства для подключения выхода команды ввода микроЭ ВМ.Введение второго счетчика и соответст. вующих ему связей позволяет проводить подсчет количества подконъюнкций, для которых вычисленный терм равен логической единице с выхода третьего элемента И и управлять схемой сравнения в режиме локального сканирования групп переменных входного сигнала,Введение схемы сравнения и соответствующих ей связей позволяет фиксировать факт равенства логической единице булевой функции в режиме локального сканирования групп переменных входного сигнала по совпадению значений с управляющего регистра и второго счетчика, управлять первым ЙВ-триггеро по окончании режима для прекращения вычислений и выдавать информацию в шинный формирователь о эначении булевой функции по команде со входаустройства для подключения выхода ком йды ввода микроЭВМ,Введение элемента запрета и соответ 5 ствующих ему связей позволяет управлятьвторым ВЯ-триггером в режиме локальнЬгосканирования групп переменных входнОгосигнала, вслучае если значение вычисляемой подконъюнкции равно логическому ну 10 лю.Введение элемента задержки и соответствующих ему связей позволяет добитьсяодновременного (синхронного) появлениясигналов на обоих входах элемента запрета15 в режиме локального сканирования групппеременных входного сигнала,Введение второго элемента ИЛИ и соответствующих ему связей позволяет осуществлять сброс первого ВЯ-триггера для20 прекращения режима локального сканирования групп переменных входного сигнвлав случае окончания вычисления булевойфункции от входного сигнала (т,е, Г=О илиГ=1).25 Введение груйпы регистров и соответствующих им связей позволяет осуществитьпоследовательную запись через региструправления из шинного формирователя 2 празрядных констант, а также их хранение и30 последовательную выдачу во вторую группумультиплексоров для вычисления булевойфункции от входного сигнала в режиме локального сканирования групп переменныхвходного сигнала. Введение четвертого эле 35 мента И и соответствующих ему связей позволяет управлять первым ВЯ-триггеромдля инициации режима. локального сканирования групп переменных входногосигнала.Введение пятого элемента И и соответ 40 ствующих ему связей позволяет обнулятьпервый и второй счетчики и второй ВЯ-триггер после завершения режима локальногосканирования групп переменных входногосигнала,45 Введение новых связей для третьегоэлемента И позволяет управлять им с цельюисключения ложных срабатываний в рекиме локального сканирования групп переменных входного сигнала,50Введение новых функций региСтра управления и соответствующих ему связей поэволяет управлять записью 2 п-разрядныхконстант в группу регистров в режиме ло 155 кального сканирования групп переменныхвходного сигнала, а также управлять схейойсравнения для завершения этого режим 4 поокончании определенного(константой регистра управления) количества циклов вычислений,510 50 Введение новых связей для дешифратора позволяет управлять четвертым и пятым элементами И для начала и завершения режима локального сканирования групп переменных входного сигнала.Введение новых связей для шинного формирователя позволяет по окончании вычислений в режиме локального сканирования групп переменных входного сигнала выдавать значения выходных сигналов второго ВЯ-триггера и схемы сравнения, на основании которых принимается решение о значении булевой функции. (Если сигналы на выходе второго ВЯ-триггера = 1, а на выходе схемы сравнения =О, то Е=О, если же сигналы второго ВЯ-триггера = О, а на выходе схемы сравнения = 1, то Р=1),Таким образом, предлагаемое техническое решение соответствует критерию "существенные отличия", поскольку в известных устройствах аналогах и прототипе при вычислении булевой функции от многоразрядного входного сигнала не достигается снижение временных затрат вследствие отсутствия указанной выше совокупности конструктивных признаков.При использовании предлагаемого устройства может быть получен положительный эффект повышения быстродействия устройства, Количественный расчет приведен в разделе технико-зкономического обоснования.На фиг,1 изображена функциональная схема предлагаемого устройства для ввода в микроЭВМ дискретных сигналов.На фиг,2 изображены временные диаграммы работы предлагаемого устройства в режиме настройки для вычисления булевой функции от многоразрядного входного сигнала.На фиг,3 изображены временные диаграммы работы предлагаемого устройства в режиме вычисления для случая, когда значение булевой функции равно единице.На фиг,4 изображены временные диаграммы работы предлагаемого устройства в режиме вычисления для случая, когда значение булевой функции равно нулю.Устройство для ввода в микроЭВМ дискретных сигналов содержит дешифратор 1 с выходами 1,1 и 1,2, три элемента 2,3,4, элемент ИЛИ 5, шинный формирователь 6, управляющий регистр 7, группу элементов И 8,1 - 8.п с тремя состояниями на выходе, группу элементов И-НЕ 9,1 - 9,п с тремя состояниями на выходе, группу регистров 10,1 - 10.К, два элемента И 11, 12, элемент запрета 13, две группы мультиплексоров 14, 15, два ВЯ-триггера 16, 17, генератор тактовых сигналов 18, два счетчика 19, 20, эле 15 20 25 30 35 40 45 мент задержки 21, схему сравнения 22, элемент ИЛИ 23, входы-выходы данных 24, вхо-ды адреса 25, входы управления 26, 27, информационные входы 28,Вход дешифратора адреса 1 подключен ко входу устройства 25 для подключения шины адреса микро- ЭВМ, Выход 11 дешифратора адреса 1 соединен с первыми входами первого 2 и второго 3 элементов И, Выход первого элемента И 2 соединен со входом выборки шинного формирователя 6, вход задания направления передачи которого, первый вход первого элемента ИЛИ 5 и второй вход пятого элемента И 12 соединены со входом устройства 27 для подключения выхода команды ввода микроЭВМ. Выход элемента ИЛИ 5 соединен со вторым входом первого элемента И 2, Второй вход элемента ИЛИ 5, вторые входы второго 3 и четвертого 11 элементов И соединены со входом устройства 26 для подключения команды вывода микроЭВМ. Выход 1,2 дешифратора адреса 1 соединен с первыми входами четвертого 11 и пятого 12 элементов И. Вход-выход шинного формирователя 6 соединен со входом-выходом 24 устройства для подключения входа-выхода данных микроЭВМ; Выход четвертого элемента И 11 соединен со входом установки первого ВЯ-триггера 16, а выход пятого элемента И 12 подключен ко входам сброса второго ВЯ- триггера 17, первого 19 и второго 20 счетчиков, Выход первого ВЯ-триггера 16 соединен со входом генератора тактовых сигналов 18, Выход генератора тактовых сигналов 18 соединен со счетным входом первого счетчика 19, и+1-ым входом третьего элемента И 4 и с элементом задержки 21. Выход элемента задержки 21 соединен со вторым входом элемента запрета 13. Выход третьего элемента И 4 подключен к счетному входу второго счетчика 20 и к первому входу элемента запрета 13, Информационный выход второго счетчика 20 соединен со вторым входом схемы сравнения 22. Выход элемента запрета 13 соединен со входом установки второго ВЯ-триггера 17, Выход второго ВЯ-триггера 17 соединен со вторым информационным входом шинного формирователя 6 и с первым входом второго элемента ИЛИ 23, Выход схемы сравнения 22 подключен к первому информационному входу шинного формирователя 6 и ко второму входу второго элемента ИЛИ 23. Выход второго элемента ИЛИ 23 соединен со входом сброса первого ЯЯ-триггера 16. Входы синхронизации группы регистров 10.1 - 10. К и управляющего регистра 7 соединены с выходом второго элемента И 3. Информационный выход регистра управления 7 соединенс информационным входом регистра 10,К группы регистров 10,1 - К 10,К и с первым входом схемы сравнения 22, Остальные информационные входы и выходы регистров 10.1 - К 10.К (кроме информационного выхода регистра 10.1) соединены между собой последовательно (т.е, информационный выход д+1-го регистра группы 10,1 - 10. К соеди- нен с информаационным входом д-го регистра 9=1, К=1). Первая и вторая группы мультиплексоров 14, 15 подключены следующим образом: )-й информационный вход (1=1,К) 1-го мультиплексора первой группы 14 соединен с 3-м информационным входом гурппы устрйоства 28 (5=1, ц), настроечный вход 1-го мультиплексора первой группы 14 и настроечный вход 1:го мультиплексора второй группы 15 (1=1, 2 п) соединены с выходом первого счетчика 19, 1-й выход -го регистра группы соединен с 1-м информационным входом 1-го мультиплексора второй группы 15, выход 1-го мультиплексора первой группы 14 соединен с первыми входами 1-го элемента И с тремя состояниями на выходе 8,1 - 8,п, и 1-го элемента И-НЕ с тремя состояниями на выходе 9,1 - 9,п, вторые входы последнего из которых соедийены с выходом 2 1-го мультиплексора второй группы 15, выход (21-1)-го мультиплексора которой соединен со вторым входом 1-го элемента И с тремя состояниями на выходе 8,1-8,п. Выходы 1-го элемента И группы с тремя состояниями на выходе 8,1 - 8,п и 1-го элемента И-НЕ группы 9,1-9,п с тремя состояниями на выходе соеднены с 1-м входом третьего элемента И 4 (1=1, и).Дешифратор 1 предназначен для дешифрации адреса, выставленного на входах адреса 25 устройства. Дешифратор 1 может быть реализован, например, на стандартных интегральных микросхемах 155 ИДЗ.Элемент И 2 предназначен для управле. ния первым входом разрешения (входом выборки) шинного формирователя 6, Выход элемента И 2 возбуждается, если активированы выход 1,1 дешифратора 1 и выход элемейта ИЛИ 5,Элемент И 3 предназначен для управления входом синхронизации для записи констант в управляющий регистр 7 и группу регистров 10 1 - 10.К в том случае, если активированы выход 1,1 дешифратора 1 и вход 26 устройства,Элемент И 4 предназначен для управления счетным входом счетчика 20 в том случае, если активированы выходы пар элементов групп 8.1-8,п и 9.1-9.п и выход .генератора 18. Элемент ИЛИ 5 предназначен для управления элементом И 2 в том случае, дслиактивированы входы 26 или 27 устройства,Шинный формирователь 6 преднана 5 чен для усиления по мощности сигналов навходах-выходах 24 устройства при активизации первого входа разрешения (выХодавыборки), а также для перевода своего хо"да-выхода в состояние высокого импеданса10 при неактивизации первого входа разрешения для отключения информационных ходов-выходов 24 устройства, Режим работышинного формирователя 6 определяетсятакже уровнем сигнала на втором входе раз 15 решения (входе направления) передачи, Работа шинного формирователя 6 описываетсятабл.1.Шинный формирователь 6 может бытьреализован, например, на стандартныХ ин 20 тегральных микросхемах 589 АП 16,Регистр управления 7 предназначен дляобеспечения последовательной записи (изшинного формирователя по сигналу ООТ 26,при активированном состоянии выхода 1,125 дешифратора 1) и йередачи в группу регист- .ров 10,1 - 10.К 2 п-разряднх установочныхконстант, а также запись и хранение К+1-йконстанты (характеризующей число цикловвычислений), а также выдачу ее на первый30 вход элемента сравнения 22 для ограйичения завершения вычислений.Региструг 1 равления 7 может быть реализован, например,на стандартных интегральных микросхемах155 И Р 13.35 Группа элементов И с тремя состояниями на выходе 8.1-8,п предназначена дляидентификации прямого значения 1-й переменной в коньюктивном терме. При этомактивирован вход управления 1-го из, эле 40 ментов 8.1 - 8,п. В противном случае выходэлемента находится в высоко импедансномсостоянии и не влияет на работу 1-го и элементов И-НЕ 9.1 - 9.п. Группа элементов И стремя состояниями на выходе 8,1 - 8.п мо 45 жет быть реализована, например, на стандартных интегральных микросхемах589 АП 16.Группа элементов И-НЕ 9.1 - 9 и с тремясостояниями-на выходе предназначена для50 идентификации инверсного сбстоянИя 1-йпеременной в конъюктивном терме, Приэтом активизирован вход управления 1.го изэлементов 9.1 - 9.п. В противном случа, выход элемента находится в высокоимйеДанс 55 ном состоянии и не влияет на работу 1-го изэлементов И 8,1-8,п.Группа элементов И-НЕ 9.1 - К 9,птремя состояниями на выходе может быть реалйзована на стандартных интегральныхмикросхемах 589 АП 26,пар элементов 8 Л и 9 Л устанавливаются активные уровни сигналов, если входной сигнал покрывает конъюнктивный терм, вычисляемый микропроцессорной системой и при наличии стробирующего импуль- са с генератора тактовых сигналов 18 активный уровень сигнала с выхода элемента И 4 производит увеличение значения счетчика 20 по переднему фронту импульса на единицу, Таким образом, при)+1 импульсе генератора на входы элементов 8.1 - 8.п и 9.1-9,п поступают значения с х входов групп. мультиплексоров 14, 15 =1,К).Ка схему сравнения 22 с выхода регистра управления 7 поступает контрольный код, соответствующий количеству п-разрядных групп в вычисляемом конъюнктивном терме (аналогичный числу использующихся при его вычислении регистров групп 10.1 - 10,К), при совпадении значения второго счетчика со значением кода управляющего регистра 7 появляется активный уровень сигнала на выходе схемы сравнения 22, который сигнализирует о том, что вычисленный терм =1, Если же входной сигнал не . покрывается коньюнктивным термом, вычисляемым микропроцессорной системой, то отсутствующий активный уровень сигнала на выходе элемента И 4 (фиг.4) вызывает совместно с активным уровнем сигнала с генератора тактовых сигналов 18, прошедшим элемент задержки 21, появление активного уровня сигнала на входе установки ВЯ-триггера 17 и установку ВЯ-триггера 17 в состояние единицы. По сигналуи 27 (при выставлении на шине адреса 25 кода, вызывающего появление активного уровня сигнала на 1-м выходе дешифратора 1), настраивающим шинный формирователь 6 на ввод информации, производится опрос выходов схемы сравнения 22 и ВЯ-триггера 17 с целью проверки конца вычислений и определения значения вычисляемой булевой функции, Наличие логической единицы либо на выходе схемы сравнения 22, либо на выходе ВЯ-триггера 17 свидетельствует о завершении вычислений. Вычисление значения логической функции внешней микро- ЭВМ производится в соответствии со следующей табл,2,Как видно из табл,1 активный уровень сигнала(т,е, "1") на выходе схемы сравнения 22 свидетельствует о том, что вычисленный терм = 1 и в этом случае микро- ЭВМ формирует выходной сигнал, соответствующий вычисленному конъюнктивному терму,В любом случае, т.е, когда активный уровень сигнала появился на выходах схемы сравнения 22 или ВЯ-триггера 17, активный уровень сигнала с выхоа элемента ИЛИ 23Константы кодов настройки, которыевносятся в массив данных, будут иметь сле дующий вид:- для первой конъюнкции:10 10 01 01 = К 1 (подконъюнкцияХ 1 Х 2 ХзХ 4)01 10 01 10 = К 2 (подконьюнкция 35 Х 5 Х 8 Х 7 Х 8)01 01 10 10 = КЗ (подконьюнкцияХ 9 Х 10 Х 11 Х 12)00 00 00 00 = К 400 00 00 11 = Купр- второй конъюнкции01 00 10 00 = К 1 (подконъюнкция Х 1 Хз)10 00 10 00 = К 2 (подконъюнкция Х 8 Х 7)00 ОО 00 00 = КЗ00 00 00 00 = К 445 00 00 00 10 = КупрВ режиме настройки для вычисленияочередной коньюнкции константы записываются в регистры следующим образом:регистр 10.1 - К 1регистр 10.2 - К 2регистр 10,3 - КЗрегистр 10,4 - К 4регистр управления 7 - КупрПрограмма, написанная для микропро цессора К 580 на языке АССЕМБЛЕР, будетиметь следующий вид;Программа настройки:РВИ:Х 1 Н, ТАВ 1; Инициализация па- мяти 40 переводит ВЯ-триггер 16 в нулевое состояние,что вызывает останов генератора тактовых сигналов 18 (фиг,3,4). Затем на шине адреса 25выставляется адрес устройства, вызывающий5 появление актиного уровня сигнала на 1,2 дешифратора 1. По сигналу и 27 активный уровеньсигнала с выхода элемента И 12 вызывает установку в нулевое состояние счетчиков 19, 20 иВЯ-триггера 17 -схема готова для вычисления10 следующего конъюнктивного терма. В дальнейшемустройство работает аналогично, т е, микроЭВМ производит настройку на вычислениеочередного конъюнктивного терма функции втом случае, если предыдущий равен нулю, иначе15 она производит соответствующие действия попрограмме(финкция= 1), При вычислениидругихфункций устройство работает аналогично.Пример конкретного вычисления.Вычислить логическую функцию, зависящую от20 12 переменных при использовании четырехвходовых (К=4) мультиплексоров, разрядность шины данных 24 равна 8,Допустим, разрядность групп входногосигнала не превышает четырех (п 4),25Г 1=Х 1 Х 2 ХЗХ 4 Х 5 Х 8 Х 7 Х 8 Х 9 Х 10 Х 11 Х 12 Ч Х 1 ХзХ 5 Х 7

СмотретьЗаявка

4829123, 29.05.1990

ПЕРМСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА В. И. ЧУЙКОВА

ТЮРИН СЕРГЕЙ ФЕОФЕНТОВИЧ, ОЛЕЙНИКОВ АЛЕКСЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 3/00

Метки: ввода, дискретных, микроэвм, сигналов

Опубликовано: 07.01.1993

Код ссылки

<a href="https://patents.su/14-1786482-ustrojjstvo-dlya-vvoda-v-mikroehvm-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода в микроэвм дискретных сигналов</a>

Предыдущий патент: Устройство для ввода в эвм дискретных сигналов

Следующий патент: Устройство для ввода информации

Случайный патент: Устройство для нанесения порошковых материалов