Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1211881

Автор: Петренко

Текст

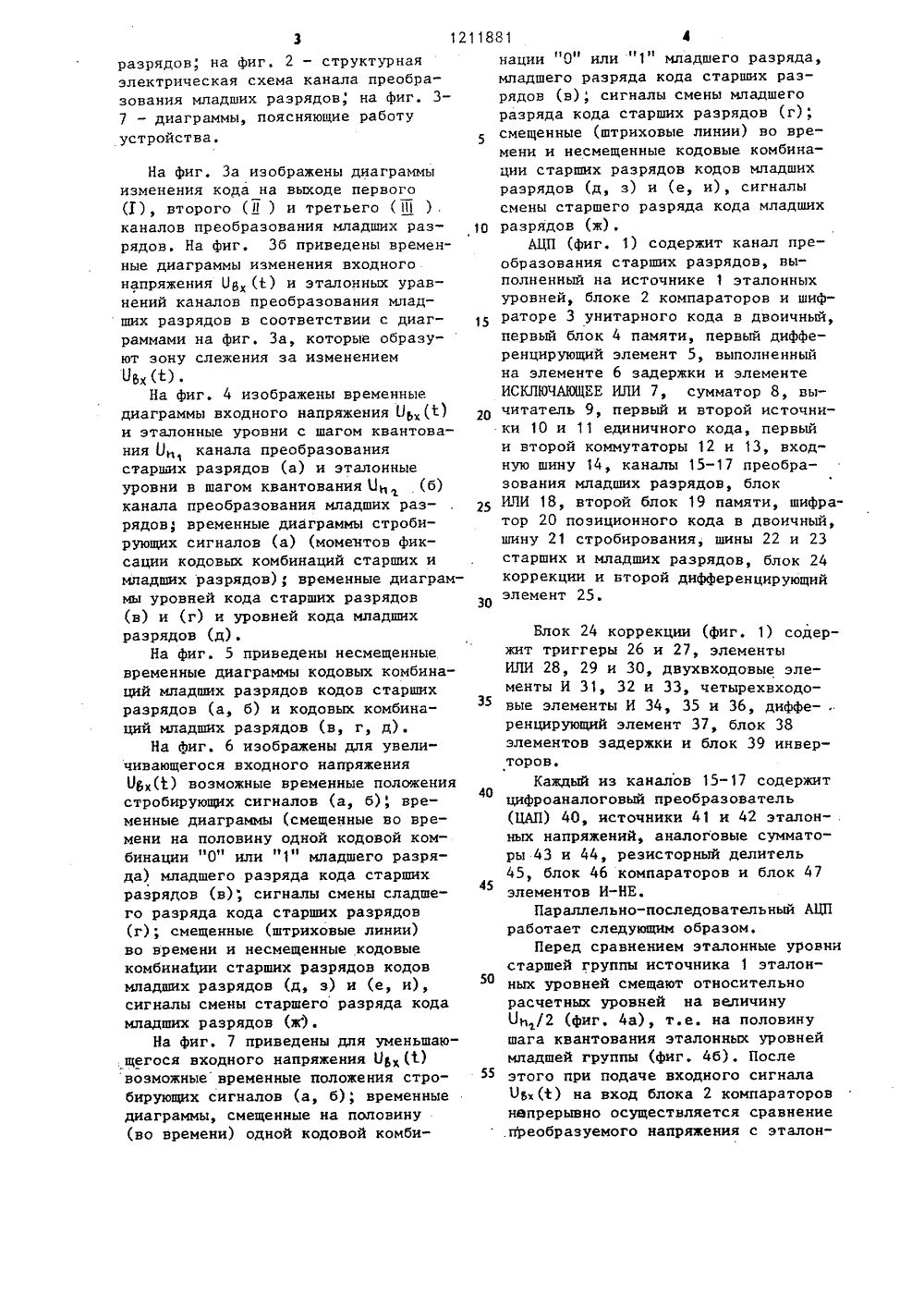

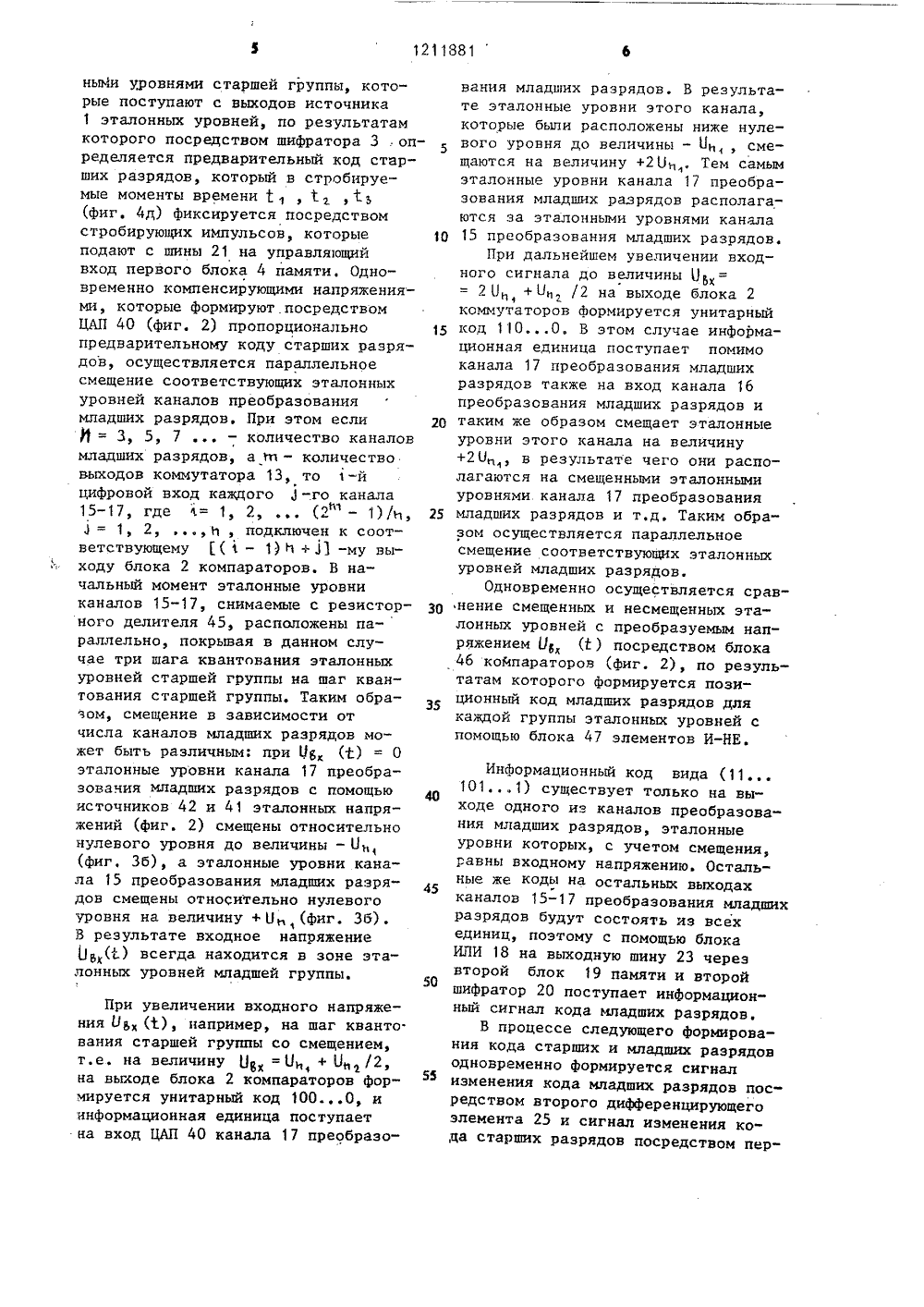

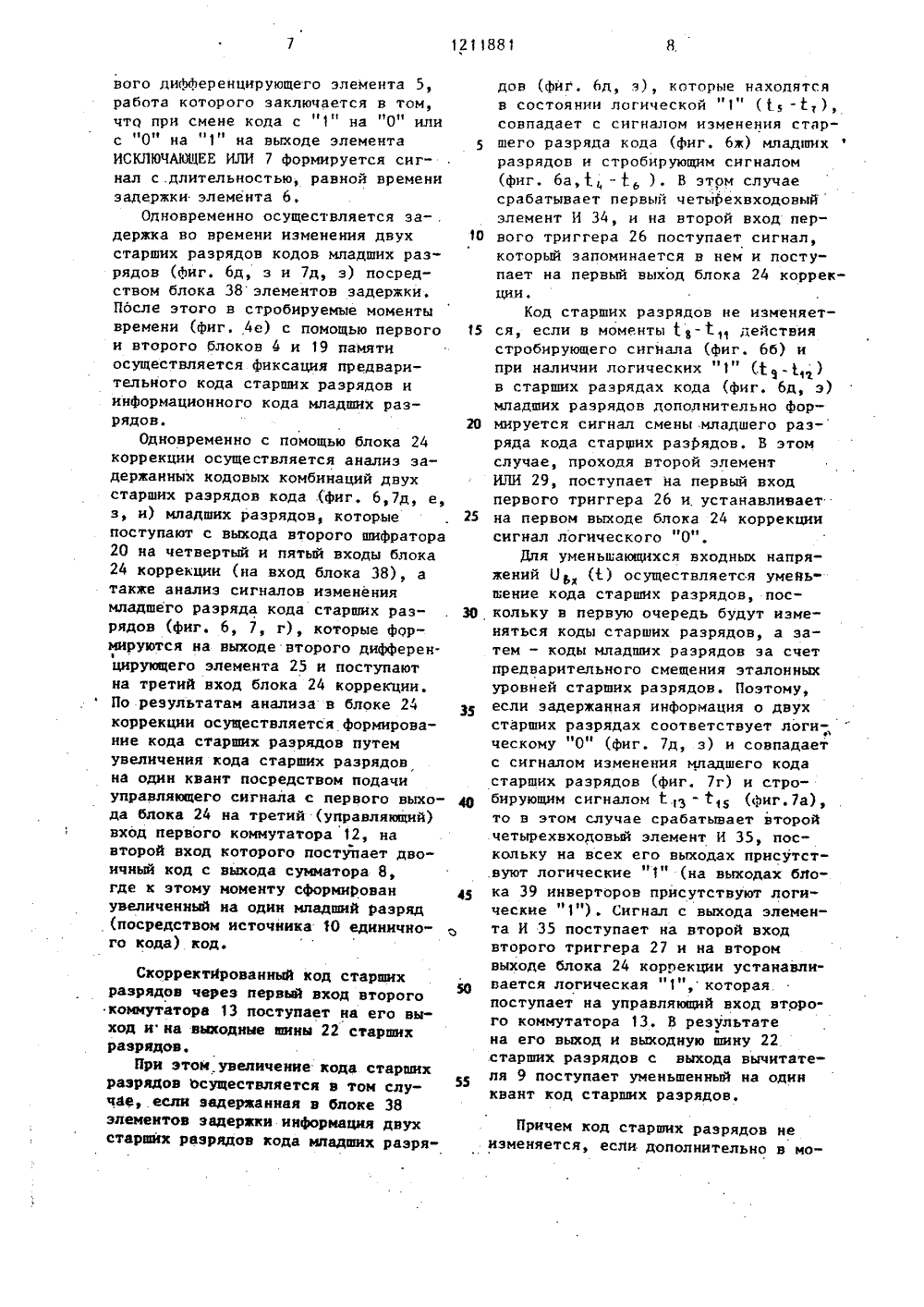

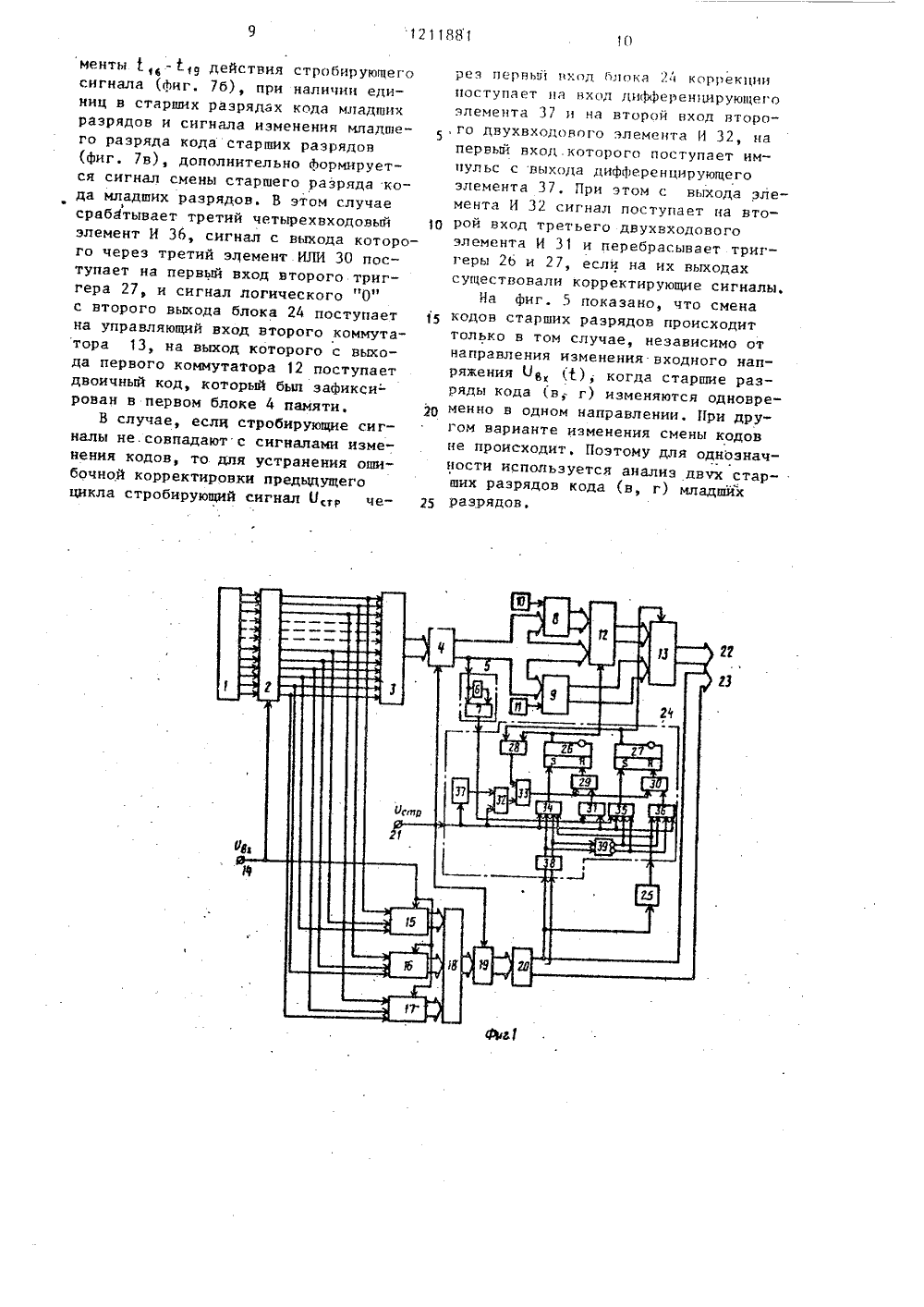

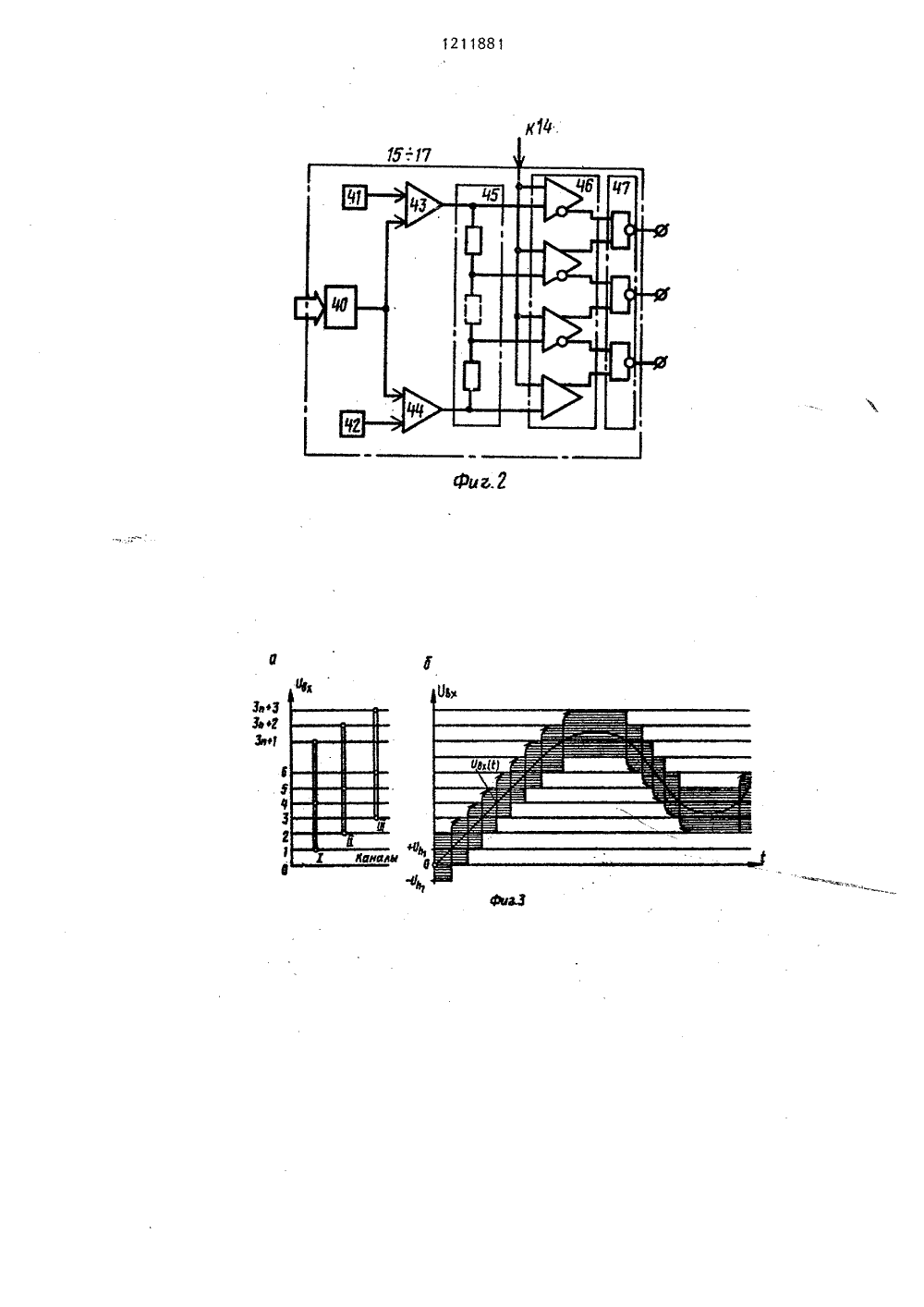

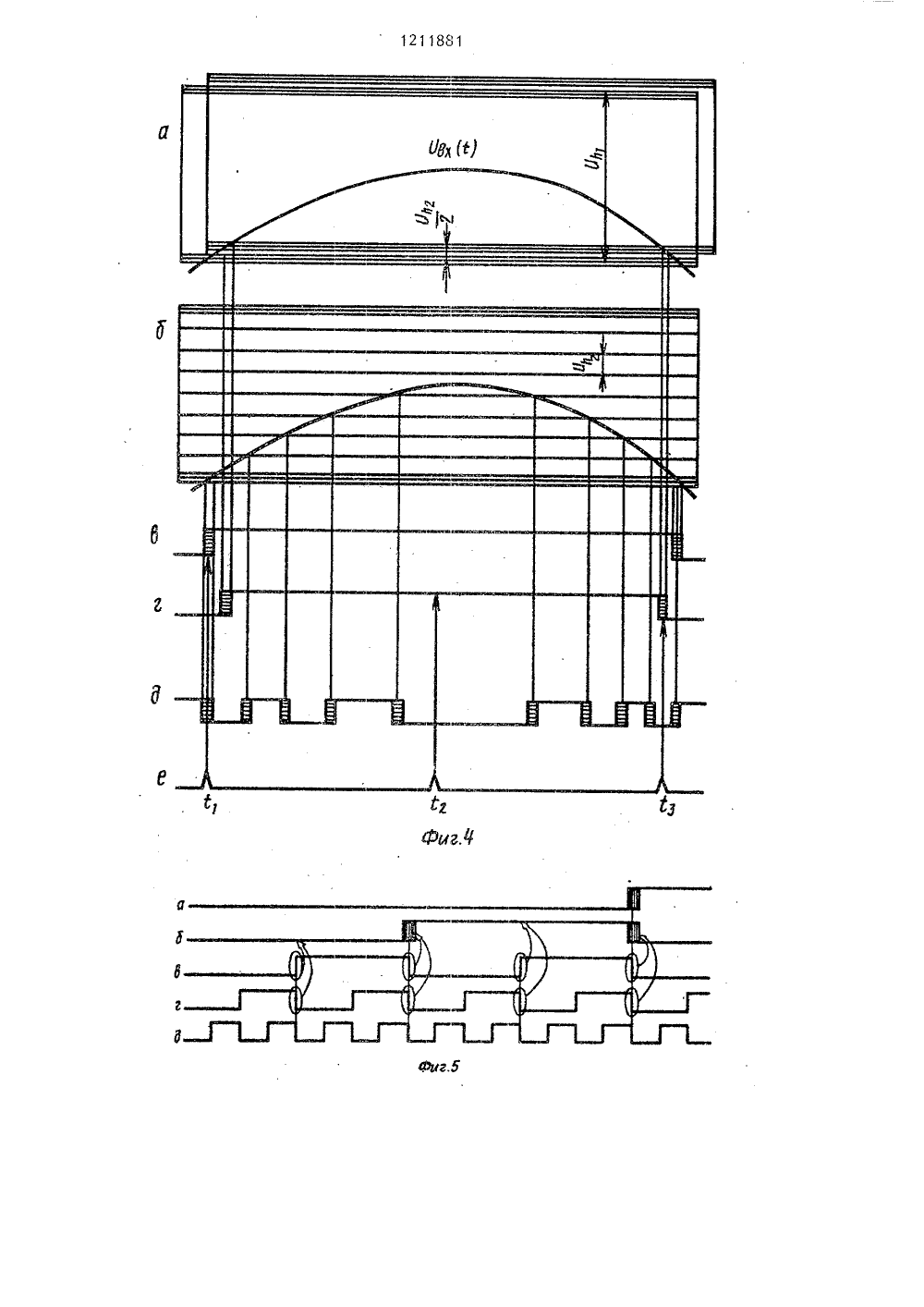

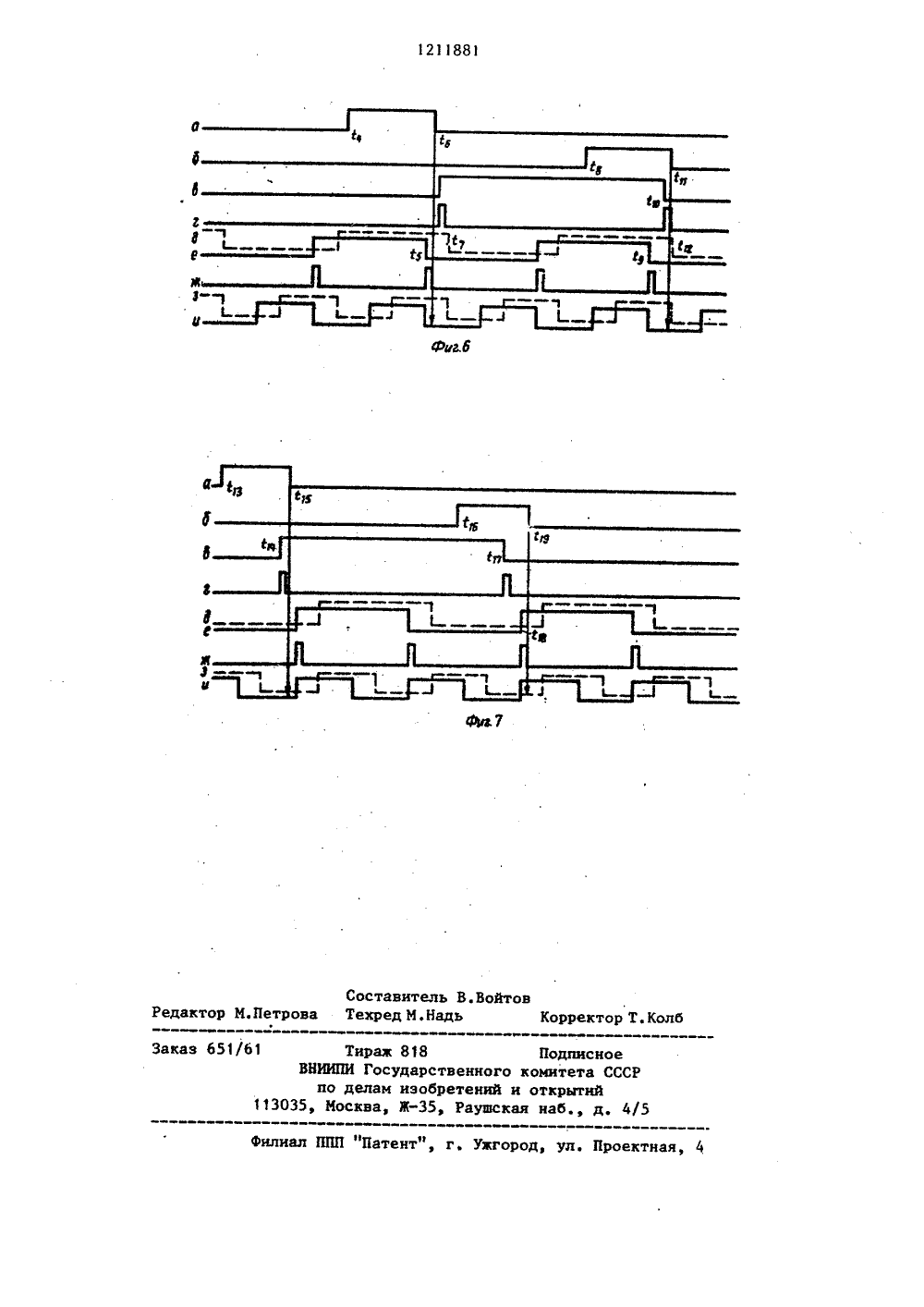

и ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АНИЕ ИЗОБР Н АВТОРСКОМУ СВИДЕТЕЛЬСТ(54)(57) 1. ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий канал преобразования старших разрядов, выполненныйна последовательно соединенных источнике эталонных чапряжений,блоке компараторов и шифраторе ун -тарного кода в двоичный, первыйкоммутатор и И , где 1 = 3, 5, 7.,каналов преобразования младшихразрядов, аналоговые входы которыхобъединены с сигнальным входом блока компараторов канала преобразования старших разрядов и являютсявходной шиной, о т л и ч а ю щ и йс я тем, что, с целью повышенияточности, в него введены блок коррекции, второй коммутатор, сумматор,вычитатель, первый и второй источники единичного кода, первый и второйблоки памяти, блок элементов ИЛИ,шифратор позиционного кода в двоичный и первый и второй дифференцирующие элементы, входы которых соответственно соединены с выходамимладшего разряда первого блока памяти и старшего разряда шифраторапозиционного кода в двоичный, выходы которого являются выходнымишинами младших разрядов, а входычерез вторрй блок памяти соединены с соответствующими выходами блока элементов ИЛИ, входы которого соединены с выходами соответствующих каналов преобразования младших разрядов, при этом у выходов второго коммутатора являются соответствующими выходными шинами старших разрядов, а 1 -й цифровой вход каждого 1 -го канала преобразования младших разрядов, где 1= 1, 2 (2 - 1) /, 3= 1, 2 и, под,ключен к соответствующему 1(-1)п + 1-му выходу блока компараторов канала преобразования старших разрядов, выходы шифратора унитарного кода в двоичный которого соответственно соединены с информационными входами первого блока памяти, стробирующий вход которого объединен с первым входом блока коррекции и стробирующим входом второго бло" ка памяти и является шиной стробирования, а выходы подключены к соответствующим первым входам сумматора, Фвычитателя и первого коммутатора, вторые входы которых соответственно соединены с выходом первого источника единичного кода, выходом второго источника единичного кода и соответствующими выходами сумматора, причем выходы вычитателя подключены к соответствующим первым входам второго коммутатора, вторые вхдр которого соединены с соответствующими выходами первого коммутатора, третий вход которого подключен к первому выходу блока коррекции, второй выход которого соединен с третьим входом второго коммутатора, второй и третий входы - соответственно121с выходами первого и второго,цифференцирующих элементов, а четвертый и пятый входы - соответственнос выходами старшего и предшествующего разрядов шифратора позиционногокода в двоичный,2. Преобразователь по и. 1, о т -л и ч а ю щ и й с я тем, что блоккоррекции выполнен на.первом .и втором триггерах, трех двухвходовыхэлементах И, трех четырехвходовыхэлементах И,трех элементах ИЛИ, дифференцирующем элементе, блоке инверторов и блоке элементов задержки,входы которого являются четвертыми пятым входами блока коррекциипервый вход которого объединен.спервыми входами первого и второгодвухвходовых и всех четырехвходовыхэлементов И и входом дифференцирующего элемента, выход которого соединен с вторым входом второго двухвходового элемента И, выход которого подключен к первому входу третьего двухвходового элемента И, второйвход которого соединен с выходомпервого элемента ИЛИ,Ю выход - с нервьпюи входами .второго и третьегоэлементов ИЛИ, вторые входы которыхподключены соответственно к выходам первого двухвходового и третьего четырехвходового элементов И, авыходы - соответственно к первым входам первого и второго триггеров, вторые входы которых соответственносоединены с выходами первого и второго четырехвходовых элементов И,а выходы подключены к соответствующим входам первого элемента ИЛИ иявляются соответственно первым ивторым выходами блока коррекции,второй вход которого объединен свторыми входами первого двухвходового элемента И и второго четырех 1881входового элемента И, третий и четвертый входы которого объединены соответственно с вторым и третьимвходами третьего четырехвходового элемента И и подключены к соответствующим выходам блока инверторов, входы которого соответственно объединены с вторым и третьим входами первого четырехвходового элемента И и подключены к соответствующим выходам блока элементов задержки, причем четвертые входы первого и третьего четырехвходовых элементов И объединены и являются третьим входом блока коррекции. 3, Преобразователь по п. 1, о т - . л и ч а ю щ и й с я тем, что каждый канал преобразования младших разрядов выполнен на цифроаналоговом преобразователе, первом и втором источниках эталонных напряжений, пер" вом и втором аналоговых сумматорах, делителе напряжения, блоке компараторов и блоке элементов И-НЕ, выходы которого являются соответствующими выходами канала преобразования младших разрядов, а входы соответственно подключены к выходам блока компараторов, первые входы которого объединены и являются аналоговым входом канала преобразования младших разрядов, цифровые входы которого соединены с соответствующими входами цифроаналогового преобразователя, выход которого соединен с первыми входами аналоговых сумматоров, вторые входы которых подключены к выходам соответствующих источников эталонных напряжений, а выходы - к соответствующим входам делителя напряжения выходы которого соединены с соответствующими вторыми входами блока компараторов.Изобретение относится к вычислительной и измерительной технике и может быть использовано для преобразования аналоговых сигналов в двоичный код,Цель изобретения - повьппение точности за счет одновременного формирования ходов старших и младших разрядов,На фиг. 1 изображена структурная электрическая схема параллельно-,последовательного аналого-цифрового преобразователя (АЦП) на примере трех каналов преобразования младшихразрядов, на фиг. 2 - структурнаяэлектрическая схема канала преобразования младших разрядов, на фиг. 37 - диаграммы, поясняющие работуустройства. На фиг. За изображены диаграммы изменения кода на выходе первого (1), второго (Б ) и третьего ( П ). каналов преобразования младших разрядов. На фиг, Зб приведены временные диаграммы изменения входного напряжения О И) и эталонных уравнений каналов преобразования младших разрядов в соответствии с диаграммами на фиг. За, которые образуют зону слежения за изменением ОьИ) .На фиг, 4 изображены временные диаграммы входного напряжения О и эталонные уровни с шагом квантования Ои, канала преобразования старших разрядов (а) и эталонные уровни в шагом квантования Ои (б) канала преобразования младших разрядов, временные диаграммы стробирующих сигналов (а) (моментов фиксации кодовых комбинаций старших и младших разрядов); временные диаграммы уровней кода старших разрядов (в) и (г) и уровней кода младших разрядов (д).На фиг. 5 приведены несмещенные временные диаграммы кодовых комбинаций младших разрядов кодов старших разрядов (а, б) и кодовых комбинаций младших разрядов (в, г, д).На фиг. 6 изображены для увеличивающегося входного напряжения ОЙ) возможные временные положения стробирующих сигналов (а, б), временные диаграммы (смещенные во времени на половину одной кодовой комбинации "0" или "1" младшего разряда) младшего разряда кода старших разрядов (в); сигналы смены сладшего разряда кода старших разрядов (г); смещенные (штриховые линии) во времени и несмещенные кодовые комбинаЦии старших разрядов кодов младших разрядов (д, з) и (е, и), сигналы смены старшего разряда кода младших разрядов (ж).На фиг. 7 приведены для уменьшающегося входного напряжения О И) возможные временные положения стробирующих сигналов (а, б); временные диаграммы, смещенные на половину (во времени) одной кодовой комби 11881 51015 20 25 элемент 25. 30 35 40 45 50 55 4нации "0" или "1" младшего разряда, младшего разряда кода старших разрядов (в), сигналы смены младшегоразряда кода старших разрядов (г);смещенные (штриховые линии) во времени и несмещенные кодовые комбинации старших разрядов кодов младшихразрядов (д, з) и (е, и), сигналысмены старшего разряда кода младшихразрядов (ж),АЦП (фиг. 1) содержит канал преобразования старших разрядов, выполненный на источнике 1 эталонныхуровней, блоке 2 компараторов и шифраторе 3 унитарного кода в двоичный,первый блок 4 памяти, первый дифференцирующий элемент 5, выполненныйна элементе 6 задержки и элементеИСКЛЮЧАЮЩЕЕ ИЛИ 7, сумматор 8, Вычитатель 9, первый и второй источники 10 и 11 единичного кода, первыйи второй коммутаторы 12 и 13, входную шину 14, каналы 15-17 преобразования младших разрядов, блок ИЛИ 18, второй блок 19 памяти, шифратор 20 позиционного кода в двоичный,шину 21 стробирования, шины 22 и 23 старших и младших разрядов, блок 24 коррекции и второй дифференцирующий Блок 24 коррекции (фиг, 1) содержит триггеры 26 и 27, элементы ИЛИ 28, 29 и 30, двухвходовые элементы И 31, 32 и 33, четырехвходовые элементы И 34, 35 и 36, дифференцирующий элемент 37, блок 38 элементов задержки и блок 39 инверторов.Каждый из каналов 15-17 содержит цифроаналоговый преобразователь (ЦАП) 40, источники 4 1 и 42 эталон- . ных напряжений, аналоговые сумматоры 43 и 44, реэисторный делитель 45, блок 46 компараторов и блок 47 элементов И-НЕ.Параллельно-последовательный АЦП работает следующим образом,Перед сравнением эталонные уровни старшей группы источника 1 эталонных уровней смещают относительно расчетных уровней на величину Ои /2 (фиг. 4 а), т.е. на половину шага квантования эталонных уровней младшей группы (фиг, 4 б). После этого при подаче входного сигнала 1)ьх й) на вход блока 2 компараторов нвпрерывно осуществляется сравнение .преобразуемого напряжения с эталон 121188140 45 50 55 ньяи уровнями старшей группы, которые поступают с выходов источника 1 эталонных уровней, по результатам которого посредством шифратора 3 .определяется предварительный код старших разрядов, который в стробируемые моменты времени 1(фиг. 4 д) Фиксируется посредством стробирующих импульсов, которые подают с шины 21 на управляющий вход первого блока 4 памяти. Одновременно компенсирующими напряжениями, которые формируют посредством ЦАП 40 (фиг. 2) пропорционально предварительному коду старших разрядов, осуществляется параллельное смещение соответствующих эталонных уровней каналов преобразования младших разрядов. При этом если И = 3, 5, 7- количество каналов младших разрядов, а п - количество выходов коммутатора 13, то 1-й цифровой вход каждого 1 в .го канала 15-17, где = 1, 2,(2- 1)/и,- 1, 2, ,11, подключен к соответствующему ( 1 - 1) И + 11 -му выходу блока 2 компараторов. В начальный момент эталонные уровни каналов 15-17, снимаемые с резистор- ного делителя 45, расположены параллельно, покрывая в данном случае три шага квантования эталонных уровней старшей группы на шаг квантования старшей группы. Таким образом, смещение в зависимости от числа каналов младших разрядов может быть различным: при Об (И = 0 эталонные уровни канала 17 преобразовачия младших разрядов с помощью источников 42 и 4 1 эталонных напряжений (фиг. 2) смещены относительно нулевого уровня до величины - Ои, (фиг, Зб), а эталонные уровни канала 15 преобразования младших разрядов смещены относительно нулевого уровня на величину + О,(фиг. Зб). В результате входное напряжение 0 всегда находится в зоне эталонных уровней младшей группы. 5 1 О 15 20 25 ЗО 35 При увеличении входного напряжения ОЬ (1), например, на шаг кванто. вания старшей группы со смещением, т.е. на величину О = 1 и, + Цт 2 э на вьгходе блока 2 компараторов Формируется унитарный код 1000, и информационная единица поступает на вход ЦАП 40 канала 17 преобразования младших разрядов. В результате эталонные уровни этого канала, которые были расположены ниже нулевого уровня до величины - 0 смещаются на величину +2 О. Тем самым эталонные уровни канала 17 преобразования младших разрядов располагаются за эталонными уровнями канала 15 преобразования младших разрядов.При дальнейшем увеличении входного сигнала до величины О= = 2 0 + Ц /2 на выходе блока 2 коммутаторов формируется унитарный код 1100, В этом случае информационная единица поступает помимо канала 17 преобразования младших разрядов также на вход канала 1 б преобразования младших разрядов и таким же образом смещает эталонные уровни этого канала на величину +2 О, в результате чего они располагаются на смещенными эталонными уровнями канала 17 преобразования младших разрядов и т.д, Таким образом осуществляется параллельное смещение соответствующих эталонных уровней младших разрядов.Одновременно осуществляется сравнение смещенных и несмещенных эталонных уровней с преобразуемым напряжением О И ) посредством блока 46 компараторов (фиг. 2), по результатам которого формируется позиционный код младших разрядов для каждои группы эталонных уровней с помощью блока 47 элементов И-НЕ. Информационный код вида (111011) существует только на выходе одного из каналов преобразования младших разрядов, эталонные уровни которых, с учетом смещения, равны входному напряжению. Остальные же коды на остальных выходах каналов 15-17 преобразования младших разрядов будут состоять из всех единиц, поэтому с помощью блока ИЛИ 18 на выходную шину 23 через второй блок 19 памяти и второй шифратор 20 поступает информационный сигнал кода младших разрядов.В процессе следующего Формирования кода старших и младших разрядов одновременно формируется сигнал изменения кода младших разрядов посредством второго дифференцирующего элемента 25 и сигнал изменения ко" да старших разрядов посредством пер 1211885 15 25 Скорректированный код старших разрядов через первый вход второго коммутатора 13 поступает на его выход и на выходные шины 22 старших разрядов.При этом увеличение кода старших разрядов ьсуществляется в том случае, если эвдержанная в блоке 38 элементов задержки информация двух старших разрядов кода младших раэря 55 вого дифференцирующего элемента 5, работа которого заключается в том, что при смене кода с "1" на "О" или с "О" на "1" на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 формируется сигнал с.длительностью, равной времени задержки элемента 6.Одновременно осуществляется за- . держка во времени изменения двух старших разрядов кодов младших разрядов (фиг. 6 д, 3 и 7 д, з) посредством блока 38 элементов задержки. После этого в стробируемые моменты времени (фиг. 4 е) с помощью первого и второго блоков 4 и 19 памяти осуществляется фиксация предварительного кода старших разрядов и информационного кода младших разрядов.Одновременно с помощью блока 24 коррекции осуществляется анализ задержанных кодовых комбинаций двух старших разрядов кода (фиг, 6,7 д, е, з, и) младших разрядов, которые поступают с выхода второго шифратора 20 на четвертый и пятый входы блока 24 коррекции (на вход блока 38), а также анализ сигналов изменения младшего разряда кода старших разрядов (фиг. 6, 7, г), которые формируются на выходе второго дифферен-цирующего элемента 25 и поступают иа третий вход блока 24 коррекции. По результатам анализа в блоке 24 коррекции осуществляется формирование кода старших разрядов путем увеличения кода старших разрядов на один квант посредством подачи управляющего сигнала с первого выхода блока 24 на третий (управляющий) вход первого коммутатора 12, на второй вход которого поступает двоичный код с выхода сумматора 8, где к этому моменту сформирован увеличенный на один младший разряд (посредством источника 1 О единичного кода) код. дов (фиг. 6 д, з), которые находятся в состоянии логической (1. -Й), совпадает с сигналом изменения старшего разряда кода (фиг. 6 ж) младпик ф разрядов и стробирующим сигналом (фиг. 6 а, 1 - 1 ). В этом случае срабатывает первый четырехвходовый элемент И 34, и на второй вход перного триггера 26 поступает сигнал, который запоминается в нем и поступает на первый выход блока 24 коррекции еКод старших разрядов не изменяется, если в моменты 1 - 111 действия стробирующего сигнала (фиг. 6 б) и при наличии логических " 1" Я- , ) в старших разрядах кода (фиг, 6 д, э) младших разрядов дополнительно формируется сигнал смены .младшего разряда кода старших разядов. В этом случае, проходя второй элемент ИЛИ 29, поступает на первый вход первого триггера 26 и. устанавливает на первом выходе блока 24 коррекции сигнал логического "О".Для уменьшающихся входных напряжений ОЬИ) осуществляется умейьшение кода старших разрядов, поскольку в первую очередь будут изме" няться коды старших разрядов, а затем - коды младших разрядов за счетпредварительного смещения эталонных уровней старших разрядов. Поэтому, если задержанная информация о двухстарших разрядах соответствует логи-, ческому "О" (фиг. 7 д, з) и совпадаетс сигналом изменения младшего кода старших разрядов (фиг. 7 г) и стробирующим сигналом й. - 1 з (фиг.7 а), то в этом случае срабатывает второй четырехвходовый элемент И 35, поскольку на всех его выходах присутствуют логические "1" (на выходах блока 39 инверторов присутствуют логические "1"), Сигнал с выхода элемента И 35 поступает на второй вход второго триггера 27 и на втором выходе блока 24 коррекции устанавливается логическая "1", которая.поступает на управляющий вход второ" го коммутатора 13. В результате на его выход и выходную шину 22 старших разрядов с выхода вычитателя 9 поступает уменьшенный на одинквант код старших разрядов,Причем код старших разрядов не изменяется, если дополнительно в моменты Й, - Ф.,9 действия стробирующего сигнала (фиг. 7 б), при наличии единиц в старших разрядах кода младших разрядов и сигнала изменения младшего разряда кода старших разрядов (фиг. 7 в), дополнительно формируется сигнал смены старшего разряда кода младших разрядов. В этом случае сраб 4 тывает третий четырехвходовый элемент И 36, сигнал с выхода которого через третий элемент ИЛИ 30 поступает на первый вход второго триггера 27, и сигнал логического "О" с второго выхода блока 24 поступает на управляющий вход второго коммутатора 13, на выход которого с выхода первого коммутатора 12 поступает двоичный код, который бып зафикси- рован в первом блоке 4 памяти.В случае, если стробирующие сигналы не.совпадают с сигналами изменения кодов, то для устранения ошибочной корректировки предыдущего цикла стробирующий сигнал (1 стр через первый цхол блока 24 коррекциипоступает ца вход диффереццирующегоэлемента 37 и ца второй вход второ, го двухвходоцого элемецта И 32, цапервый вход.которого поступает импульс с выхода диффереццирующегоэлемента 37. При этом с выхода элемента И 32 сигнал поступает ца второй вход третьего двухвходовогоэлемента И 31 и перебрасывает триггеры 2 Ь и 27, если на их выходахсуществовали корректирующие сигналы.На фиг. 5 показано, что сменакодов старших разрядов происходиттолько в том случае, независимо отнаправления изменения входного напряжения Ов Й); когда старшие разряды кода (в; г) изменяются одновре менно в одном направлении. При другом варианте изменения смены кодовце происходит, Поэтому для однозначности используется анализ двух старших разрядов кода (в, г) младших 25 разрядов,121881 фий акаэ 651 Тирах 818 ВНИИПИ Государственно по делам иэобретений 35, Москва, Ж"35, РаушПодписноео комитета СССРи открытийкая наб д. 4/5 илиал ППП "Патент", г. Ухгород, ул. Проектная, 4 Составитель В.Войтоведактор М.Петрова Техред М.Надь Корректор Т. Кол

СмотретьЗаявка

3679071, 27.12.1983

ПРЕДПРИЯТИЕ ПЯ В-2201

ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 1/34

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/9-1211881-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Преобразователь перемещения в код

Следующий патент: Преобразователь угла поворота вала в код

Случайный патент: Устройство для моделирования нейрона