Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1200294

Автор: Гришин

Текст

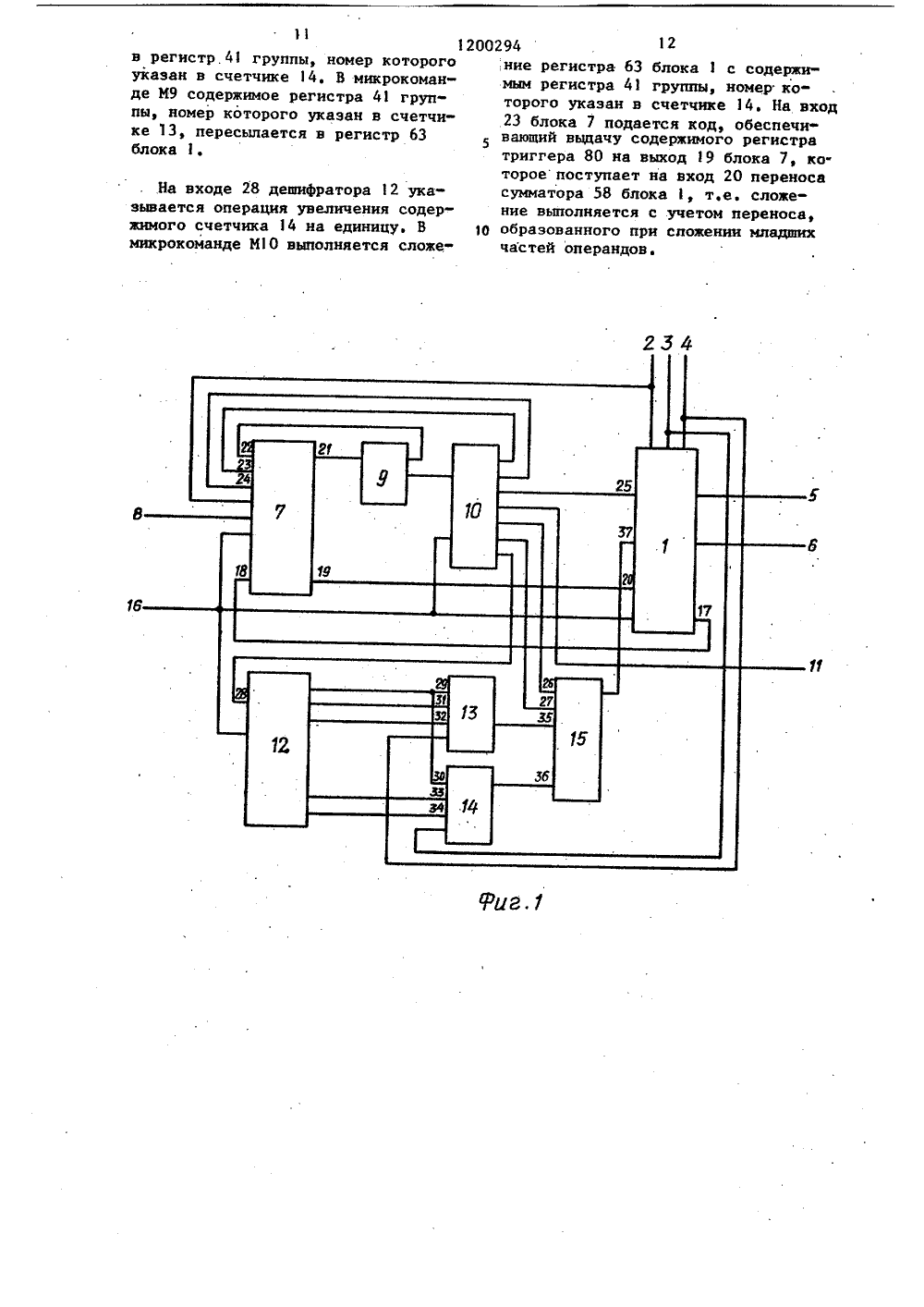

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 09) (11) 9 40 06 Р 15 00 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ИСАНИЕ ИЗОБРЕТЕНИЯ / дТОРСКОМУ СВИДЕТЕЛЬСТВУ "Ф 24( 21 ) 3709231(56) БерезенкКорягин Л.Н.лекты повышенМ.: Радио и сАвторскоеУ 1037263, кл Бюл. Р 47ин88.8 )о А.И., НазарьМикропроцессорнного быстродейвязь, 1981, с.свидетельствоС 06 Р 15/00 н А.Р.,ые комптвия.168,ССР1983,(54)(57) 1, ПРОЦЕССОР, содержащий операционный блок, блок формирования адреса, блок микропрограминой памяти и регистр микрокоманд, синхровход, информационный вход, выход управления чтением, выход управления записью, выход кода микроинструкции и выход операционного поля которого подключены соответственно к синхровходу процессора, информационному выходу блока микропрограммной памяти, первому и второму входам блока формирования адреса, первому входу операционного блока и управляющему выходу процессора, третий, четвертый, пятый, шестой и седьмой входы блока формирования адреса соединены соответственно с входом начальной установки процессора, адресным выходомблока микропрограммной памяти, выходом переноса операционного блока,синхровходом процессора и первым Информационным входом процессора, первый и второй выходы блока формирования адреса подключены соответственно к адресному входу блока микропрограммной памяти и второму входу операционного блока, адресный иинформационный выходы которого подключены к соответствующим выходам процессора, третий, четвертый, пятый и шестой входы операционного блока подключены соответственно к первому, второму и третьему информационным входам и синхровходу процессора, о т л и ч а ю щ и й с я тем, что, с целью повышения производительности, он содержит дешифратор, два реверсивных счетчика и коммутатор, причем управляющий вход и первый, второй и третий информационные входы и выход коммутатора соединены соответственно с выходом первого уп- Ж равляющего поля регистра микрокоманд, выходами первого и второго реверсивных счетчиков, информационным выходом ( регистра микрокоманд и седьмым входом операционного блока, синхровход . процессора и выход второго управляющего поля регистра микрокоманд подключены соответственно к управляющему и информационному входам дешифратора, первый выход которого подключенк входам записи первого и второго реверсивных счетчиков, а второй, третий, четвертый и пятый выходы - соответственно к входам сло-. жения и вычитания первого и второгореверсивных счетчиков, информацион- ные входы которых подключены соответственно к второму и третьему инФормационным входам процессора.2. Процессор по п. 1, о т.л и ч аю щ и й с я тем, что операционный блок содержит дешифратор микроинструкций, дешифратор выбора регистра, одиннадцать групп элементов И, пять.1200 групп элементов ИЛИ, группу регист- ров, группу элементов НЕ, сумматор, .пять элементов И, элемент ИЛИ, регистр адреса и сдвиговый регистр, вход и выходы дешифратора микроииструкций соединены соответственно с первым входом блока и первыми входами первого, второго, третьего, четвертого и пятого элементов И, первыми входами элементов И первой, второй, ;третьей, .четвертой, пятой, шестой седьмой и восьмой групп, информационный вход, вход параллельной записи, вход сдвига, последовательный информационный вход, выход и последовательный выход .сдвигового регистра соединены соответственно с выходами элементов ИЛИ первой группы, выходом первого элемента И, выходом второго элемента И, вторым входом блока, информационным выходом блока и вторым входом третьего элемента И, вторые входы первого и второго элементов И соединены с шестым входом блока, второй вход четвертого элемента И соединен с выходом переноса сумматора, первый и второй входы и .выход элемента ИЛИ соединены соответственно с выходами третьего и четвертого элементов И и выходом переноса блока, информационный вход, выход и синхровход регистра адреса соединены соответственно с выходом элементов ИЛИ первой группы, выходом адреса блока, выходом пятого элемента И, второй вход которого соединен с шестым входом блока, второй вход и выход элементов И первой группы соединены соответственно с выходом элементов НЕ группы и первым входом элементов ИЛИ первой группы, второй вход и выход элементов И второй группы соединен соот- . ветственно с выходами элементов ИЛИ второй группы и вторыми входами элементов ИЛИ первой группы, второй вход и выход элементов И третьей 294группы соединены соответственнос выходами элементов. И девятой группы и третьим входом элементов ИЛИпервой группы, второй вход и выходэлементов И четвертой группы соединены соответственно с выходом сумматора и четвертым входом элементов.ИЛИ первой группы, первый и второйвходы и выход элементов И 3 ф 1 третьей группы соединены соответственно с выходами элементов И пятой и шестой групп и первыми входами элементов ИЛИ второй группы, элементов Идевятой группы и сумматора, первый ивторой входы и выход элементов ИЛИчетвертой группы соединен соответственно с выходами элементов И седьмойи восьмой групп, входами элементовНЕ группы и вторыми входами элементов ИЛИ второй группы, элементов Идевятой группы и сумматора, вход переноса которого соединен с вторымвходом блока, вторые входы элементов И пятой группы соединены с объединенными третьим, четвертым и пятым входами блока, вторые входыэлементов И шестой и восьмой группсоединены с информационным выходомблока, вход и выходы дешифратора выбора регистра соединены соответственно с седьмым входом блока, первыми входами элементов И десятойи одиннадцатой групп, второй входэлементов И десятой группы соединенс шестым входом блока, синхровходы, информационные входы и выходырегистров группы соединены соответственно с выходами соответствующих;элементов И десятой группы, выходами элементов ИЛИ первой группы, вторыми входами элементов И одиннадцатой группы, вторые входы и выходыэлементов ИЛИ четвертой группы соединены соответственно с выходами элементов И одиннадцатой группы и вторыми входами элементов И седьмойгруппы.200294 3Цель изобретения - повышение производительности процессора.На фиг,1 изображена функциональная схема процессора; на фиг,2 - функциональная схема операционного блока; на фиг.3 - Функциональная схема блока формирования адреса; на фиг.4 - алгоритм выполнения микропрограмм. Процессор содержит операционный блок 1, информационные входы 2-4 процессора, адресный 5 и информационный 6 выходы процессора, блок 7 формиро.вания адреса, вход 8 начальной установки процессора, блок 9 микропро-. граммной памяти, регистр 10 микрокоманд, управляющий выход 11 процессора, дешифратор 12, реверсивные счетчики 13 и 14, коммутатор 15 и синхровход 16 процессора, выход 17 переноса блока 1, вход 18 признаков блока 7, выход 19 признаков блока 7, вход 20 блока 1, выход 21 блока 7, входы 22-24 блока 7, вход 25 блока 1, входы 26 и 27 коммутатора 15, вход 28 дешифратора 12, вход 29 счетчика 13, вход 30 счетчика 14, входы 31 и 32 счетчика 13, входы 33 и 34 счетчика 4, входы 35 и 36 коммутатора 15 вход 37 блока 1. Блок 1 (Фиг.2 ) содержит дешифратор 38 микроинструкций, дешифратор 39 выбора регистра, группу элементов И 40, группу регистров 41, группы элементов И 42, ИЛИ 43, И 44, И 45, ИЛИ 46, И 47, И 48, ИЛИ 49, НЕ 50, ИЛИ 51, И 52, И 53, ;И 54, И 55, И 56 и ИЛИ 57, сумматор 58 элемент И 59, элемент И 60, элемент И 61, регистр 62 адреса, сдвиговой регистр 63, элементИ 64, элемент И 65 и элемент ИЛИ66.. Бйок 7 формирования адреса(фиг.З) содержит дешифратор 67 микроинструкций, .группы элементов И 68, И 69, И 70, И 71, И 72 и ИЛИ 73, регистр 74, группу элементов И 75, дешифратор 76 чтения, дешифратор 7 записи, элемент И 8, элемент И 79, триггеры 80 и 81 элементы И 82 и 83 и элемент Юф 84.Введенные условные обозначения: В; -. адрес микрокоманды; РС - регистр 41 группы, используемый в качестве программного счетчика; Р- регистр62 блока 1; Р - сдвиговый регистр63 блока 1; Р 1 - регистр 4 груп 41 43пы блока 1, номер которого указан5 счетчиком 13; Р - регистр 41группы блока 1, номер которого указан счетчиком 14; С 413 = 4 и С 414= 3 - мнкрооперации загрузки счетчиков 13 и 14 информацией на входах 31 О и 4 процессора; С 413+1 и С 414+1Иикрооперации увеличения на единицу содержимого реверсивных счетчиков 13 и 14; 4 Т - микрооперация чтения информации из блока внешней5 памяти, указывается на выходе 11процессора; Т = СО - запись в триггер 80 блока 7 значения на выходе 17блока 1; С = Т - выдача значениятриггера 80 блока 7 на вход 20 бло 20 ка 1,Процессор работает следующим образом.Для приведения процессора в исходное.состояние на вход 8 подаетсянулевой сигнал начальной загрузки. При этом на выходе 21 блока 7образуется нулевой адрес, которыйявляется начальным адресом .микропрограммы начальной загрузки. По это 30 му адресу из блока 9 выбираетсямикрокоманда М 1. Каждая микрокоман-да состоит из двух частей: адресной и исполнительной, Адресная частьпоступает на вход 22 управленияадресом блока 7, а исполнительная3. на информационные входы регистра 10,По сигналу синхронизации в соответствии с укаэанным типом, переходав регистр 74 блока 7 записываетсяадрес следующей микрокоманды, а ис 40 полнительная часть текущей микрокоманды записывается в регистр. 10.Таким образом, выборка микрокоманды опережает на один такт ее выполнение, следовательно, в первом45 микрокомандном цикле операционныйблок 1, дешифратор 12 и коммутатор 15выполняют неопределенные действия,соответствующие кодам, образбвавшимся в регистре 10 после включения50 процессора. После первого синхросигнала навходе 16 сигнал "Начальная установка" переводится в единичное состоя ниение и адрес с выхода регистра 74 через элементы И 75 группы поступа.ет на вход блока микропрограммнбй памяти. Таким образом, выборка последую 120029420 щих адресов определяется регистром74 блока 7.Адресная часть микрокоманды состоит из двух частей: в первой частиуказывается тип перехода, во второйадрес перехода. Сигналы, соответствующие типу перехода, во второй -адрес перехода. Сигналы, соответствующие типу перехода, поступают навход дешифратора 67,а сигналы, соответствующие адресу перехода, - навторые входы групп элементов И68-71. В зависимостй от того, на какой выходе дешифратора 67 образуетсяединичный сигнал, адрес следующей 15микрокоманды определяется либо безусловно по адресу перехода, указанному в адресной части микрокоманды,либо с учетом сигналов на входе 18блока 7, либо с учетом состояниятриггеров 80 и 81 или 1 безусловнопо коду, образованному на входе 2блока 7,Код адреса следующей микрокоманды, образованный одним из перечисленных способов, поступает через группы элементов ИЛИ 73 на информационный вход регистра 74 и по заднемуфронту синхросигнала на входе 16 записывается в регистр 74.. 30Исполнительная часть микрокоманды состоит из семи полей. Код, подаваемый с первого выхода регистра 10на вход 23 блока 7, определяет Функцию дешифратора 76 чтения, в зависимости от которой на выходе 19 блока 7 образуется либо содержимое триггеров 80 и 81, либо значения логического 0 или логической "1", Код,подаваемый с второго выхода регистра 10 на вход 24 блока 7,определяетфункцию дешнфратора 77 записи, в зависимости от которой по заднему фронту синхросигнала на входе 16 производится либо запись в один из триггеров 80 или 81 значения, присутствующего на входе 18 блока 7, либо значе"ние триггеров остается без изменения.Работа блока 7 при этом заключается в следующем. Если производится 0запись в какой-либо триггер данныхнавходе 18 блока 7, то единичный сигнал, образованный на одном из выходов дешифратора 77, открывает элемент И 78 или 79. Поступающий на 55.: вход 16 синхроимпульс выполняет запись значения сигнала на входе 18блока 7. При выдаче состояния какого-лиоо триггера на выход 19 блока 7 по единичному сигналу на соответствующем выходе дешифратора 76 открывается, элемент И 82 или 83 и содержимое триггера соответственно 80 или 81 через элементы И 82 и ИЛИ 84 или И 83 и ИЛИ 84 поступает на выход 19 блока 7. При выполнении многих операций процессор обращается к блоку внешней памяти (не показан ), При выполнении операций записи информации в блок внешней памяти на управляющем выходе 11 устанавливается сигнал, соответствующий режиму записи.Адрес, по которому производится запись, и данные формируются соответственно на выходах 5 и 6 процессора. При чтении информации изблока внешней памяти на управляющем выходе 11 устанавливается сигнал чтения, при этом данные с выхода внешней памяти поступают на входы 2-4 процессора.Код, поступающий с выхода регистра 10 на вход 28 блока 12, определяет одну из функций дешифратора 12, В результате этого выполняются операции, загрузка реверсивных счетчиков 13 и 14 данными, образованными соответственно на входах 4 и 3 процессора; +1 в счетчик 13; -1 из счетчик 13; +1 в счетчик 14; -1 из счетчика 14.Код, поступающий с выхода регистра 10 на вход 26 блока 15, определяет функцию дешифратора 85 блока 15 которая заключается в выборе номера канала, который должен быть подключен к выходу коммутатора 15. Единичное значение на одном из выходов дешифратора 85 открывает одну из групп элементов И 86 - 88, и информация соответственно с одного из входов 27, 35 и 36 блока 15 поступает через соответствующую группу элементов И и через группу элементов ИЛИ 89 навход 37 блока 1.Информация, записываемая в реверсивные счетчики и поступающая с выхода регистра 10 на вход 27 блока 15, по своему смыслу является номером одного из регистров 41 группы блока 1. Таким образом, код,поступающий с выхода коммутатора 15 на вход 37 блока 1, определяет функцию дешифратора 39 блока 1, которая заключается в выборе одного из регистров 41 группы в качестве одного из операн1200294 8дов. Второй операнд и тип ействиядействия при этом с сдвигающего выхода сигналвыполняемого над операндами, определя- поступает на вход элемента И 64 иется кодом, поступающим с выхода ре- при наличии единичного сигнала нагистра 10 на вход 25 блока 1. втором входе элемента И 64 постукачестве второго операнда может 5 пает через элементы И 64 и ИЛИ 66 набыть выбран либо регистр 63 блока , выход 7 блока . Кроме того, по сиглибо данные об азованнд , р з ванные на входах калу синхронизации результат опера 2-4 процессора.ции записывается в один из регистровНад операциями блок 1 выполняет 41 группы в зависимости от того, наарифметико логические и сдвиговые О каком из элементов И 40 группы наоперации. Арифметико-логические опе- первом входе присутствует единичрации в блокевыполняются над двумя ный сигнал, поступающий с выхода деоперандами, которые поступают с вы- шифратора 39,ходов группы элементов ИЛИ 46 и с вы- Рассмотрим алгоритм выполненияходов группы элементов .ИЛИ 49. На вы операции сложения двух регистровходе группы элементов ИЛИ 46 данные (фиг 4 ) в случа елиг. в случае увеличения количест"образуются либо с входов 2-4, либо с ва регистров общег на регистров о щего назначения.,выхода 6 процессора в зависимости от В адресной ча М 1адресно части микрокоманды Мтого, какая из групп элементов И 44 формируется безусловный переход кили 45 открыта единичным сигналом, 20 микрокоманде М 2 ймикрокоманде , а исполнительнойпоступающим с выхода дешифратора 38, части указывается операция обнулеНа выходе группы элементов ИЛИ 49 ния одного из регистров 41 группы,данные образуются либо с выходов который выбран в качестве программнообозначим его РС (.ходов 6 пРоцессоРа также в зависи- . 25 Условимссловимся, что, если на каком-либомости от того, какая группа элементов И 47 или 48выходе регистра 10 формируется код,тов или открыта единичным который указывает на отсутствие аксигналом, поступающим с выхода дешиф- тивных действий того или иного блоратора 38ка, то этот выход при пояснении принВыбранные операнды поступают на ЗО ципа действия упоминаться не будет.входы групп элементов НЕ 50, ИЛИ 51 Таким образом в микрок М 1и сумматора , на выходе ко- тивные действия выполняет толькоторь 1 х образуются соответственно результаты логических операций НЕ, В адресной части микрокоманды М 2ИЛИ, .И или сумма операндов. При пе указывается безусловный переход креполнении сумматора 58 на его выхо- микрокоманде МЗ, а в исполнительнойде переноса образуется единичный части - пересылка данных из ресигнал переноса, поступающий на вход гистра РС в регистр 62 блока 1, вэлемента, И 65, и при наличии единич- результате этого на выходе 5 блоканого сигнала на втором входе элемен- О образуется нулевой адрес внешнейта И 65, поступающего с выхода дешиф- памяти. В микрокоманде МЗ на выходератора 38, сигнал переноса через эле-процессора указывается сигналменты И 65 и ИЛИ 66.поступает на вы- чтения из внешней памяти, в реэульход 17 блока 1. тате чего содержимое нулевого адВ зависимости от того, какая групреса внешней памяти поступает напа элементов И 53 - 56 открыта еди- входы 2-4 процессора, в частностиничным сигналом с выхода дешифра- значение на входе 2 процессоратора 38, результат соответствующей поступает на вход 2 блока 7;операции НЕ, ИЛИ, И, сумма поступа- На вход 28 дешифратора 2 подаетет через соответствующую группу эле О ся код, указывающий на загрузку рементов И и ИЛИ 57 на входы регист- версивных счетчиков 13 и 4 нфо62ров и 63 и на входы регистров 41 цией, присутствующей на входах 4 и 3группы. процессора. По сигналу синхронизацииРезультат выполненной операции в , информация записывается в счетчикизависимости от наличиЯ единичного 13 и 4 По своемусигнала на входах элементов И 59-61 мация представляет собой номера репо сигналу синхронизации на входе 16 гистров 41гистров группы блока ), над котозаписывается соответственно в регист 62 63рыми необходимо выполнить действиеры и и регистр 63 со сдвигом, команды.Далее результат суммирования через элементы И 56 группы и ИЛИ 57 группы поступает на входы регистра 63. По сигналу синхронизации при наличии единичного сигнала на входе элемента И 60 с выхода дешифратора 38 9 1200294 10В адресной части микрокоманды МЗ , производится запись результата в реУказывается переход к микрокоманде гистр 63.М 4, в адресной части которой укаэыва- В адресной части микрокоманды М 6 ется переход по коду, присутствующе- указывается переход к микрокоманде . му на входе 2 блока 7 В результате 5 М 2, а в исполнительной части - слоэтого единичным сигналом с выхода де жение содержимого регистра 41 группы шифратора 67 открываются элементы И блока 1, номер которого указан в 72 группы, код с входа 2 через эле- счетчике 14, и содержимого регистменты И 72 группы и ИЛИ 73 группы по- ра 63 блока 1. Результат записываступает на вход регистра 74 и по сиг ется в регистр 41 группы блока 1, налу синхронизации записывается ад- Начиная с микрокоманды М 2 действия рес следующей микрокоманды М 5, кото- процессора повторяются. рый является начальным адресом мик- Таким образом, операция сложения ропрограммы, реализующей операциюсложения двух регистров, 15 команд. Сложение двух ячеек внешнейВ исполнительной части микроко- памяти потребует большего количестманды М 4 указывается операция уве- ва микрокоманд, так как необходиличения на единицу содержимого .мо выполнить микрооперации вычислепрограммного счетчика РС. В .адресной ния адресов этих ячеек и считывания части микрокоманды М 5 указывается 20 данных из внешней памяти. безусловный переход к микрокоманде Рассмотрим алгоритм микропрограм- . Мб, а в исполнительной части - опера- мы сложения двух пар регистров ция пересылки содержимого одного из ( фиг.4 ) в случае обработки операндов регистров 41 группы, номер которого большей разрядности, чем разряд- записан в счетчик 13, в регистр 63. 25 ность процессора. блока 1, Для этого на вход 26 коммута- Действия микрокоманд М 2 и МЗ опитора 15 подаетЧя код, обеспечиваю- саны ранее. В адресной части микрокощий прохождение сигналов с входа 35 манды М 4 указывается переход по коду через элементы И группы и элементы на входе 2 блока 7, т.е. к микроко- ИЛИ группы блока 15 на вход 37 дешиф маиде М 7, в адресной части которой ратора 39 блока 1. указывается переход к микрокомандеСодержимое выбранного регистра 41 М 8. В исполнительной части микрокогруппы через соответствующие элемен- ,манды М 7 указывается пересылка реты И 42 группы и ИЛИ 43 группы по- гистра 41 группы, номер которого ступают на вход элементов И 47 груп указан в счетчике 13, в регистре 6335пы. При выполнении операции пересыл- блока 1. В адресной части микрококи одного из.регистров 41 группы манды М 8 указан безусловный переход в регистр 63 на выходах дешифратора к микрокоманде М 9, от которой выпол образуются нулевые сигналы, посту- няется переход к М 10 и далее к М 2, лающие на входы элементов И 44 груп завершая команду сложения пар регистпы, И 45 группы, И 48 группы, И 53ров.1 группы,И 54 группы иИ рупЙ 56 г пы иВ исполнительной части микрокоманединичные сигналы, поступающие нады М 8 указывается сложение содержимо-.го регистра 63 блока 1 и регистра 4145ется операция сложения содержимого грйсчетчике 14. Перенос, образованны егистра 41 группы, поступающего наР РИ 47 на выходе 17 блока 1 при сложении, вход сумматора через элементын вхо 8 7. Н группы и ИЛИ 491 группы, с нулевым поступает на входн вхо 1 блока . а вход24 блока 7 с выхода регистра 10 поаю на запись входе сумматора с выхв хода элементов ступает код, указывающийзначения на входе 18 в триггер 80. ИЛИ 46 группы.На вход 28 дешифратора 12 подаетсякод, указывающий на увеличение содержимого реверсивного счетчика 13,на единицу.По сигналу синхронизации выполняются все перечисленные действия,На входе 28 дешифратора 12 указывается операция увеличения содержимого счетчика 14 на единицу. В микрокоманде М 10 выполняется сложе 1200294 12Р. РУппы номеР котоРого ние регис 63 б 1указан в счетчике 14. В микрокоман мым регистра 41 группы, номер ко де М 9 содержимое регистра 41 гРУп- торого указан в счетчике 14. На вход пы, номер которого указан в счетчи блока 7 подается код, обеспечике 13, пересылается в регистр 63 вающий выдачу содержимого регистра блока триггера 80 на выход 19 блока 7, ко.торое поступает на вход 20 переноса сумматора 58 блока 1, т.е. сложение выполняется с учетом переноса,10 образованного при сложении младвихчастей операндов.Составитель Л.ЛогачеваТехред А Бойко Петраш Редак Подписиомитета СССРоткрытийская наб., д. 4/5 аказ 7869/5 ВН.Проектная,.У 5 Тираж 709 ИИПИ Государственногопо делам изобретений 33035, Москва, Ж, Р Корректор И.Иу

СмотретьЗаявка

3709231, 15.03.1984

ПРЕДПРИЯТИЕ ПЯ В-8185

ГРИШИН ВЛАДИМИР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 23.12.1985

Код ссылки

<a href="https://patents.su/9-1200294-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Многоканальный сигнатурный анализатор

Следующий патент: Устройство для моделирования размещения плоских геометрических объектов

Случайный патент: Способ отбора высокопродуктивных форм колосовых злаковых культур