Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

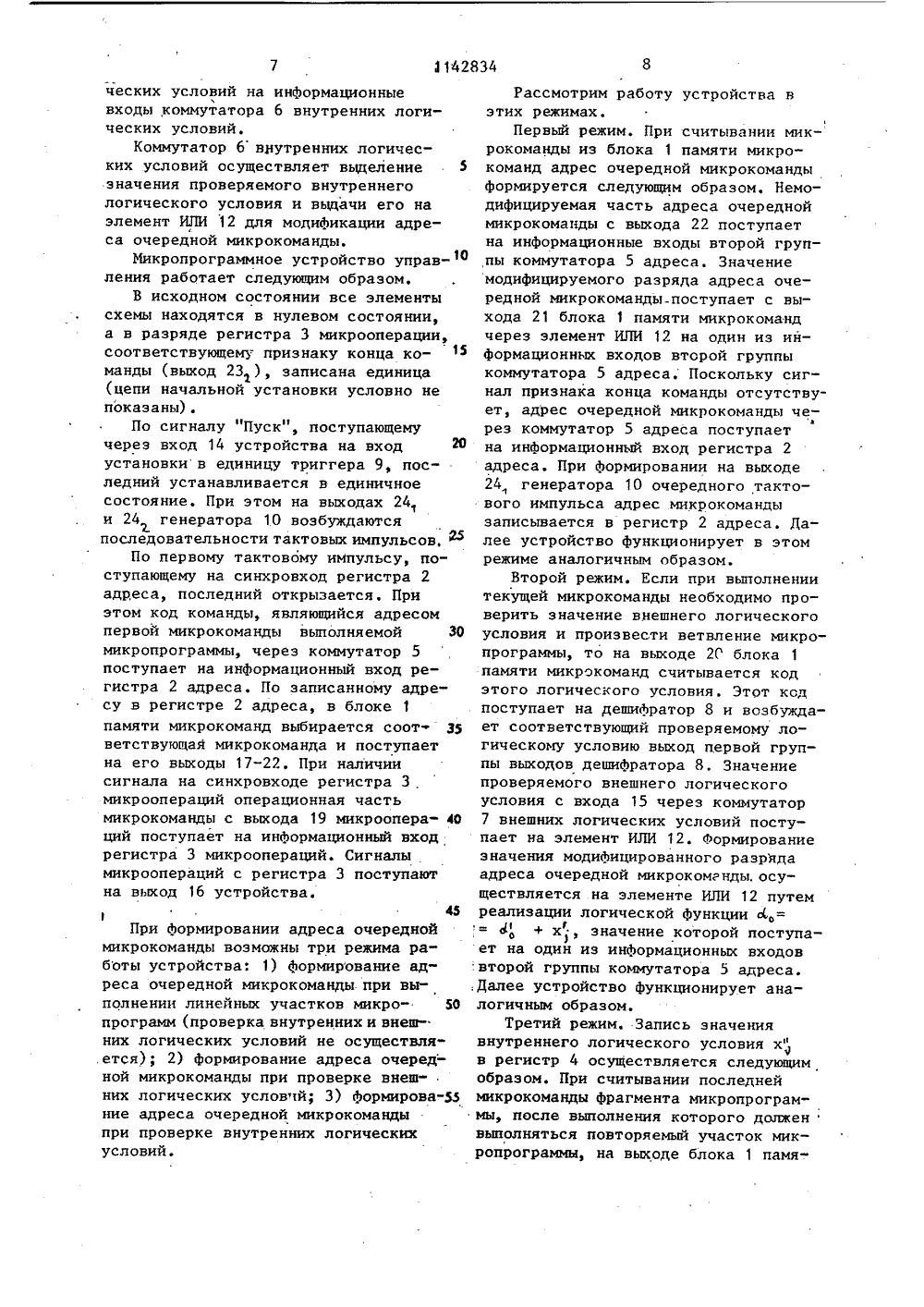

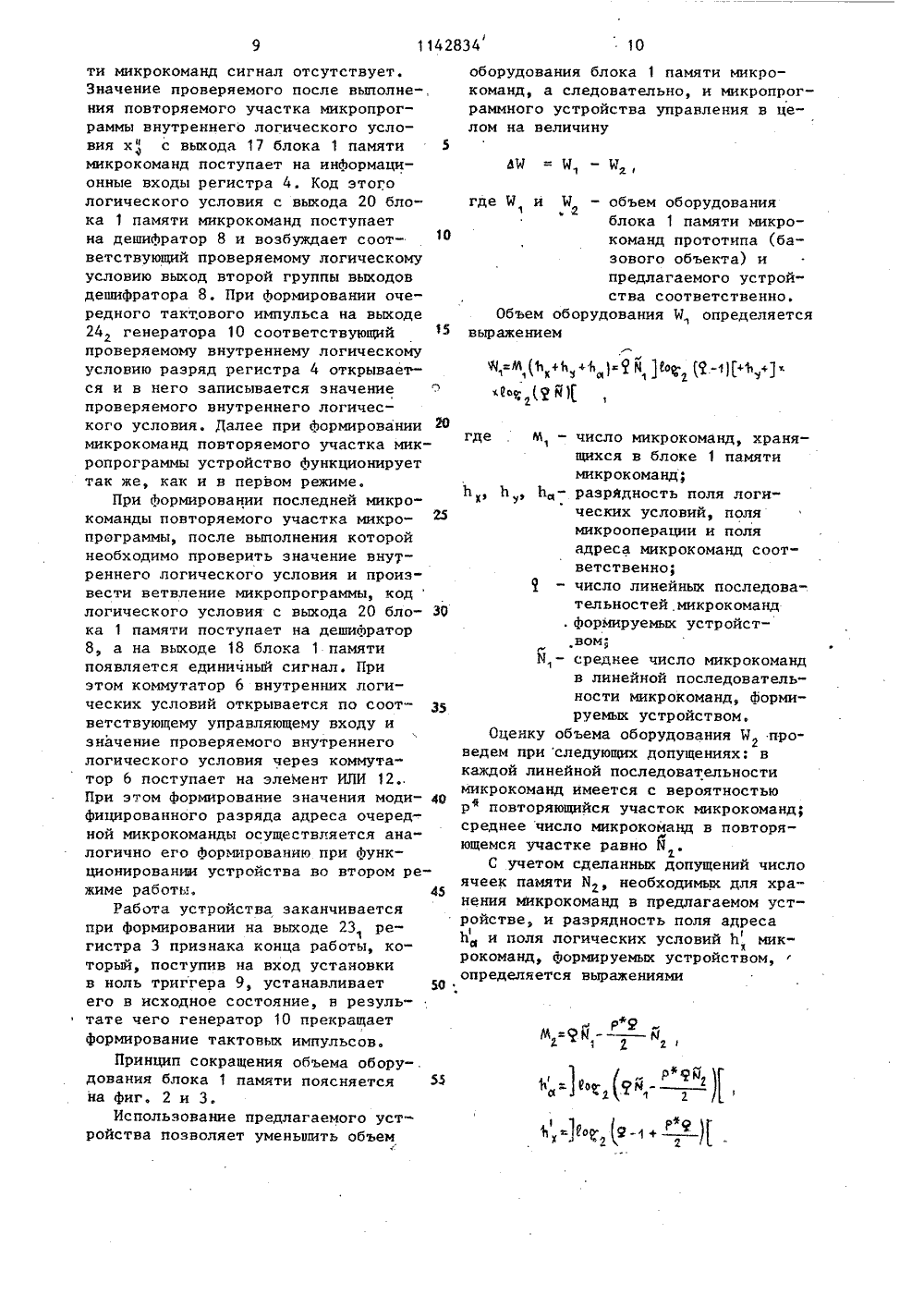

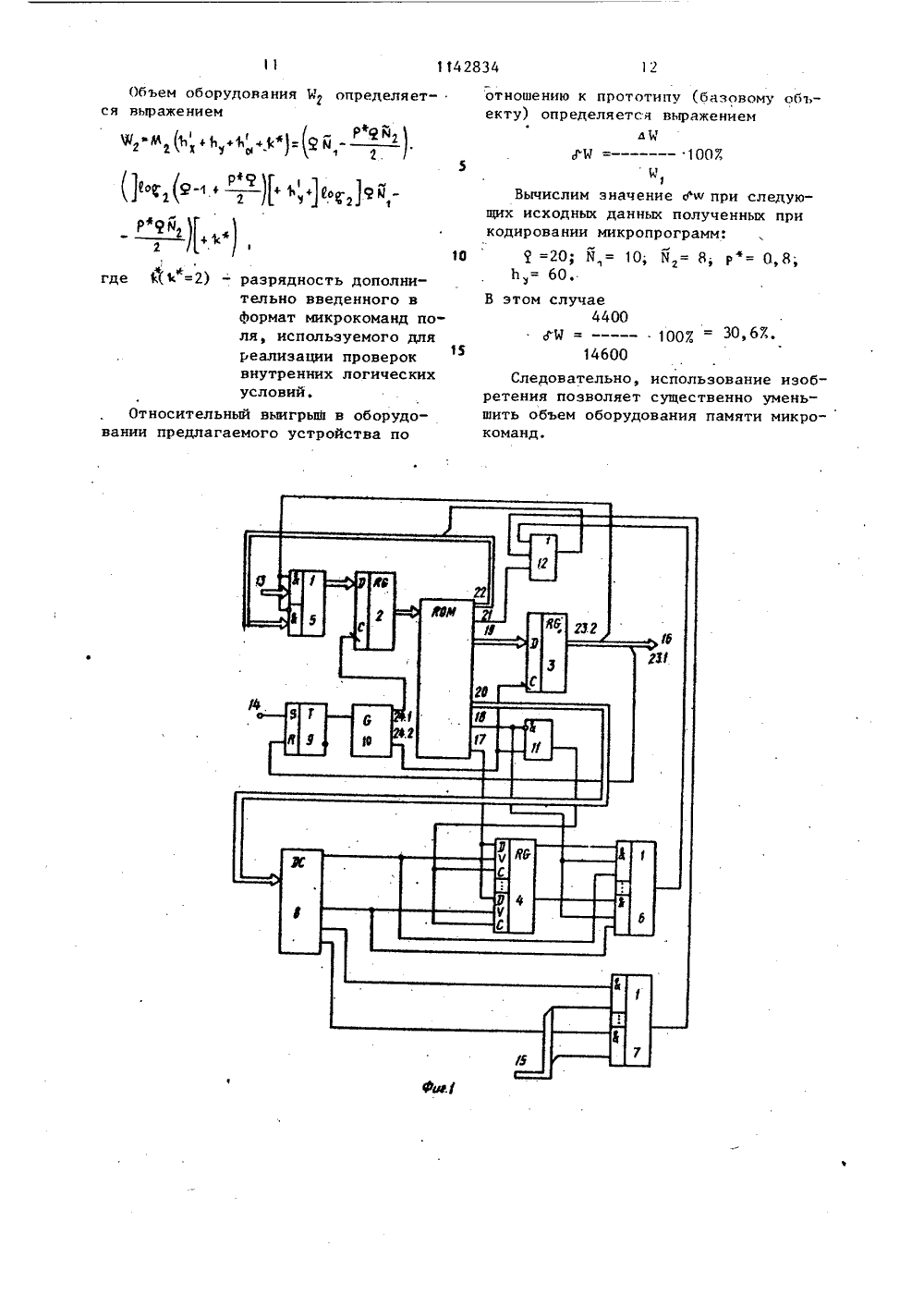

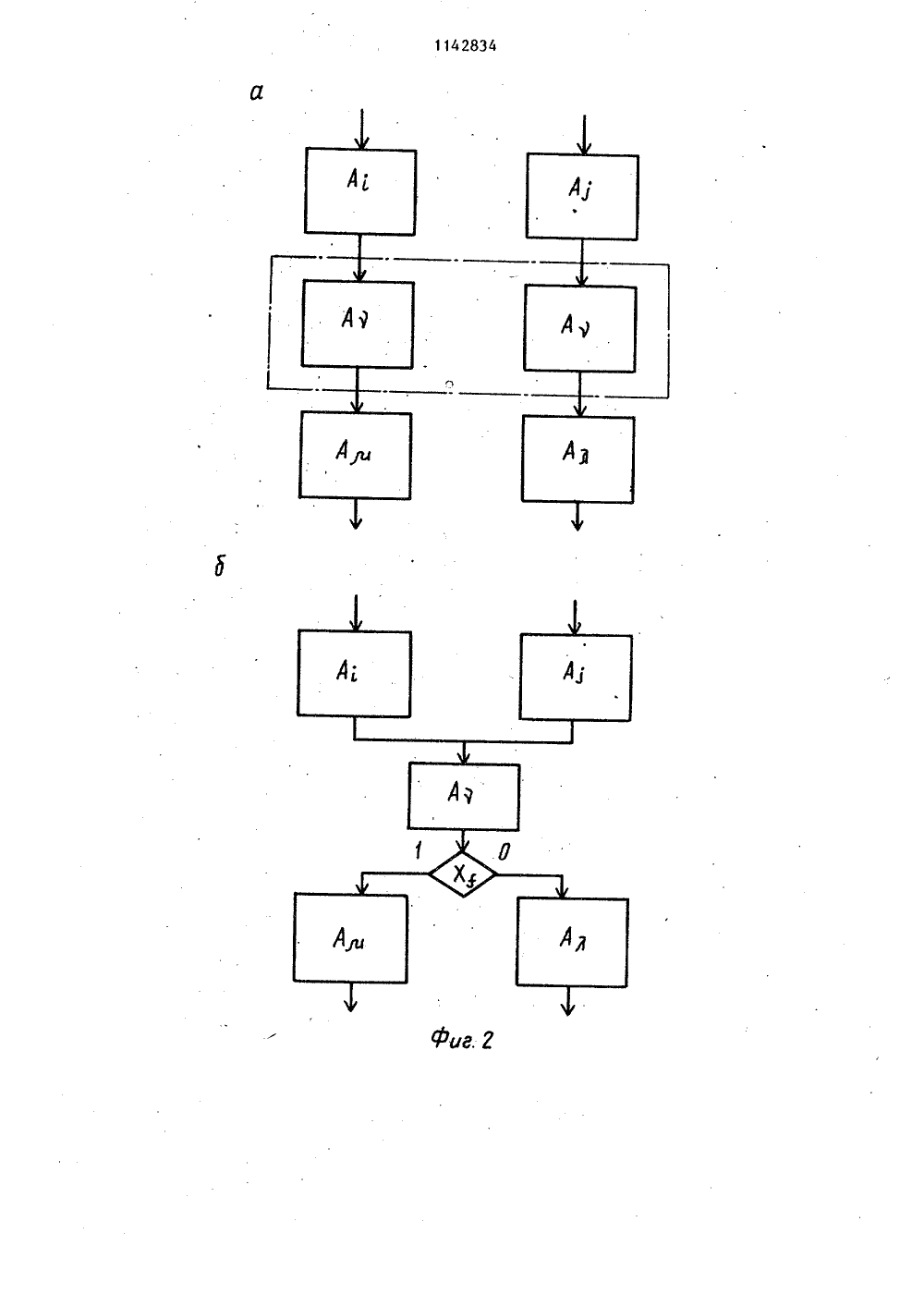

(51) С 06 Р 9/22 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАНИЕ ИЗОБРЕ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(54) (57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее блок памятимикрокоманд, регистр адреса, регистр ,микроопераций, коммутатор адреса,коммутатор внешних логических усло- .вий, дешифратор, триггер пуска и генератор тактовых импульсов, причемвход кода команды устройства соединен с первым информационным входомкоммутатора адреса, выход которогосоединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памятимикрокоманд, п адресных выходов(в - количество немодифицируемыхразрядов адреса следующей микрокомаиды) немодифицируемых разрядов которого соединены с соответствующими Финформационными входами второй группы коммутатора адреса, выход кодамикроопераций блока памяти микрокоманд соединен с информационнымвходом регистра микроопераций, выход признака конца команды которогодинен с управляющим входом коммура адреса, выход признака конца работы регистра микроопераций соединен с входом установки в ноль триггера пуска, выход которого соединенс входом запуска генератора тактовыхимпульсов, первый и второй выходыкоторого соединены соответственнос входами синхронизации регистра адреса и регистра микроопераций, выходкода управления внешними устройствами которого является выходом устройства, выход кода логических условийблока памяти микрокоманд соединен свходом дешифратора, первая группавыходов которого соединена с группойуправляющих входов коммутатора внешних логических условий, группа ин- Сформационных входов которого является группой входов логических условийустройства, вход установки в единицутриггера пуска является входом пускаустройства, о т л и ч а ю щ е е с ятем, что, с целью сокращения объемаоборудования, оно содержит регистрвнутренних логических условий, коммутатор внутренних логических усло- ффвий, элемент И и элемент ИЛИ, причем 4 ффадресный выход модифицируемого разряда блока памяти микрокоманд соединенс первым входом элемента ИЛИ, выходкоторого соединен с (в +1)-м информационным входом второй группы ком- Зффмутатора адреса, второй и третийвходы элемента ИЛИ соединены соответственно с выходами коммутатора внеш-них логических условий и коммутаторавнутренних логических условий, информационные входы которого соедине11428:34 ны с выходами регистра внутреннихлогических условий, информационныйвход которого соединен с выходомкода внутренних логических условийблока памяти микрокоманд, выход признака анализа внутренних логическихусловий которого соединен с инверсным входом элемента И и со стробирующим входом коммутатора внутренних 1Изобретение относится к автоматике и вычислительной технике и можетбыть использовано при построениицентральных устройств управления ЭВМи вычислительных систем. 5Известно микропрограммное устройство управления, содержащее два блока памяти, дешифратор, регистр адреса,. триггер, элемент НЕ, два блокаэлементов И 13, 10Недостатком этого устройства является узкая область применения,обусловленная ограничениями на топологию выполняемых микропрограмм.Известно микропрограммное устройство управления, содержащее регистрадреса, дешифратор, блок памяти микрокоманд, триггер условия, элементи 23,Недостатком этого устройства является низкая экономичность, обусловленная отсутствием специальных технических средств для исключения избыточности блока памяти.Наиболее близким к предлагаемому 25по технической сущности и достигаемому эффекту является микропрограммное устройство управления с принудительной адресацией, содержащеетриггер .пуска, генератор тактовых З 0импульсов, дешифратор логических условий, коммутатор внешних логическихусловий, постоянное запоминающееустройство (ПЗУ) микрокоманд, регистры адреса и микрокоманд, дешифратормикроопераций, элемент НЕ, коммутатор адреса, причем вход пуска устройства соединен с единичным входомтриггера пуска, выход которого соединен с входом генератора тактовых импульсов, выход которого соединен с логических условий, группа управляющих входов которого соединена с нторой группой выходов дешифратора и сгруппой входов управления записьюрегистра внутренних логических условий, вход синхронизации которогосоединен с выходом элемента И, прямой вход которого соединен с вторымвыходом генератора тактовых импульсов. входом считывания постоянного запоминающего устройства микрокоманд, адресный вход которого соединен с выходом регистра адреса, первый и второй выходы регистра микрокоманде соединены с входами дешифраторов .внешних логических условий и мирокопераций соответственно, группа выходов которого соединена с выходами устройства, а выход "Конец работы" соединен с нулевым входом триггера пуска, выходы дешифратора логических условий сое= динены с управляющими входами коммутатора внешних логических условий, входы логических условий устройства соединены с информационными входами коммутатора внешних логических условий, выход которого через элемент НЕ соединен с управляющим входом коммутатора адреса, выход которого соединен с входом регистра адреса, выход ПЗУ микрокоманд соединен с входом регистра микрокоманд, адресный выход которого соединен с информационными входами коммутатора адреса 1 3 3.Недостатком указанного устройства является большсй объем оборудования ПЗУ микрокоманд, что обусловлено отсутствием технических средств, позволяющих исключить повторное хранение многократно используемых участков микропрограмм, имеющих разныхпоследователей.Цель изобретения - сокращение объема оборудования.Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, коммутатор, адреса, коммутатор внешних логических условий, дешифратор, триггер пуска и генератор тактовых импульсов, причем вход кода команды устройства соединен с первым информационным входом 5 коммутатора адреса, выход, которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, в адресных выходовФо (в - количество немодифицирузмых разрядов адреса следующей микрокоманды) немодифицируемых разрядов которого соединены с соответствующими е информационными входами второй груп пы коммутатора, адреса, выход кода микро" операций блока памяти микрокоманд соединен с информационным входом ре - гистра микроопераций, выход признака конца команды которого соединен с Ю управляющим входом коммутатора адреса, выход признака конца работы ре" гистра микроопераций соединен с входом установки в ноль триггера пуска, выход которого соединен с входом за пуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхронизации регистра адреса и регистра микроопераций, выход кода управления 30 внешними устройствами которого явля- ется выходом устройства, выход кода логических условий блока памяти микрокоманд соединен с входом дешифратора, первая группа выходов котороГо 5 соединена с группой управляющих входов коммутатора внешних логических условий, группа информационных входов которого является группой входов логических условий устройства, вход установки в единицу триггера пуска является входом пуска устройства, введены регистр внутренних логических условий, коммутатор внутренних логических условий, элемент И и эле мент ИЛИ, причем адресный выход модифицируемого разряда блока памяти микрокоманд соединен с первым входом элемента ИЛИ, выход которого соединен с (п 1 + 1)-м информационным входЬм 5 О второй группы коммутатора адреса, второй и третий входы элемента ИЛИ .соединены соответственно с выходами коммутатора внешних логических условий и коммутатора внутренних логи , ческих условий, информационные входы которого соединены с выходами регистра внутренних логических условий,информационный вход которого соеди.нен с выходом кода внутренних логических условий блока памяти микрокоманд, выход признака анализа внутренних логических условий которогосоединен с инверсным входом элемента И и со стробирующим входом коммутатора внутренних логических условий, группа управляющих входов которого соединена с второй группой выходов дешифратора и с группой входовуправления записью регистра внутренних логических условий, вход синхронизации которого соединен с выходомэлемента И, прямой вход которого соединен с вторым выходом генераторатактовых импульсов,Сущность изобретения состоит всокращении объема оборудования памяти микрокоманд путем исключения повторяющихся участков микропрограмм,имеющих разных последователей. Этодостигается за счет введения внутренних логических условий формирования их значений, хранения с использованием специальных техническихсредств и проверки их после выполнения соответствующих участков микропрограмм,На фиг. 1 приведена функциональная схема предлагаемого микропрограммного устройства управления; на фиг. 2 фрагмент микропрограммы, реализуемойв прототипе (а) и в предлагаемомустройстве (б); на фиг. 3 поясняетсяпринцип сокращения объема ПЗУ в предлагаемом устройстве (б) по срарнениюс прототипом (а)Микропрограммное устройство управления (фиг, 1) содержит блок 1 памяти микрокоманд, регистр 2 адреса,регистр 3 микроопераций, регистр 4внутренних логических условий, коммутатор 5 адреса, коммутатор 6 внутренних логических условий, коммутатор 7 внешних логических условий,дешифратор 8, триггер 9 пуска, гене-,ратор 10 тактовых импульсов, элементИ 11, элемент ИЛИ 12, вход 13 кодакоманды устройства, вход 14 пускаустройства, вход 15 логических условий и выход 16.Кроме того, на фиг. 1 показанывыход 17 значения внутреннего логического условия, выход 18 признакаанализа внутренних логических усло-,вий, выход 19 кода микроопераций,выход 20 кода логических условий, 1142834выход 21 модифицируемого разряда адреса очередной микрокоманды, выход 22 немодифицируемых разрядов адреса очередной микрокоманды блока 1 памяти микрокоманд, выходы признака 5 конца работы 23 и признака конца команды 23 регистра микроопераций, первый 24 и второй 24 выходы гене-ратора 10 тактовых импульсов.На фиг. 2 и 3 использованы следующие обозначения: А, А, А 1, А, А - микроподпрограммы, х - логическое условие; ш ш ш- разрядности адресной и операционной частей и поля логических условий; М, и М - метки, соответствующие выходам 17 и 18 блока 1 соответственно,Рассмотрим функциональное назначение элементов и связей предлагаемого микропрограммного устройства управления (фиг, 1).Блок 1 памяти микрокоманд предназначен для хранения кодов микрокоманд.Коммутатор 5 осуществляет передачу на информационный вход регистра 2 адреса либо кода команды, поступающего с входа 13 устройства, либо модифицированного адреса очередной микрокоманды по второму информационному вхоцу при единичном или нулевом 30 значении сигнала "Конец команды" на выходе 23 соответственно.Регистр 2 адреса микрокоманд предназначен для приема, хренения и выдачи кодов адресов микрокоманд в 35 блок 1 памяти микрокоманд. Запись кода адреса очередной микрокоманды в регистр 2 адреса микрокоманд производится с выхода 5 коммутатора при поступлении на синхровход импульса с 40 выхода 24 генератора 10 тактовых импульсов.Регистр 3 микроопераций предназначен для приема, хранения и выдачи кодов микроопераций на выход 16 уст ройства. Запись информации в регистр 3 микроопераций осуществляется при наличии на его синхровходе сигнала, формируемого на выходе 24 генератора 10 тактовых импульсов. 50Генератор 10 тактовых импульсов на первом 24, и втором 24 выходах формирует последовательности тактовых импульсов, сдвинутых один относительного другого на время записи 55 в регистр 2 адреса очередной микро- команды и выборки микрокоманды из блока 1 памяти микрокоманд и обеспечивающих синхронизацию работы устройства. Формирование последовательностей импульсов на выходах ген".ратора 10 тактовых импульсов производится только при наличии единичного сигнала на его управляющем входе.Триггер 9 пуска управляет работой генератора 10 тактовых импульсов.Он устанавливается в единичное состояние при поступлении единичного сигнала на вход 14 пуска устройства, который соединен с его входом установки в единицу, Единичный сигнал на выходе триггера 9 пуска разрешает функционирование генератора 10 тактовых импульсов. Триггер 9 пуска устанавливается в нулевое состояние при поступлении на его вход установки в ноль сигнала "Конец работы",который формируется на выходе 23, регистра 3 микроопераций.Коммутатор 7 внешних логических условий осуществляет выделение значения проверяемого внешнего логического условия и выдачу его на элемент ИЛИ 12.Элемент ИЛИ 12 осуществляет формирование значения младшего разряда адреса очередной микрокоманды и выдачу его на один из информационных входов коммутатора 5 адреса. Формирование младшего разряда адреса , очередной микрокоманды осуществляется путем реализации функции1 11е(,(,= Ы хх где Ы, - значение модифицируемогоразряда адреса очередноймикрокоманды на выходе 21блока 1 памяти микрокоманд;х. - значение проверяемого внут)реннего логического условияна выходе коммутатора бвнутренних логических условий;йх- значение проверяемого внешнего логического условияна выходе коммутатора 7,внешних логических условий.Элемент И 11 предназначен для управления записью проверяемого внутреннего логического условия в регистр 4 внутренних логических условий.Регистр 4 внутренних логических условий служит для записи, хранения и выдачи значений внутренних логических условий на информационныевходы коммутатора 6 внутренних логических условий.Коммутатор 6 внутренних логических условий осуществляет выделениезначения проверяемого внутреннегологического условия и выдачи его наэлемент ИЛИ 12 для модификации адреса очередной микрокоманды.Микропрограммное устройство управления работает следующим образом.В исходном состоянии все элементысхемы находятся в нулевом состоянии,а в разряде регистра 3 микрооперации,соответствующему признаку конца команды (выход 23), записана единица(цепи начальной установки условно непоказаны).По сигналу "Пуск", поступающемучерез вход 14 устройства на вход Оустановки в единицу триггера 9, последний устанавливается в единичноесостояние. При этом на выходах 24и 24 генератора 1.0 возбуждаютсяпоследовательности тактовых импульсов, фПо первому тактовому импульсу, поступающему на синхровход регистра 2адреса, последний открызается, Приэтом код команды, являющийся адресомпервой микрокоманды выполняемой 30микропрограммы, через коммутатор 5поступает на информационный вход регистра 2 адреса. По записанному адресу в регистре 2 адреса, в блоке 1памяти микрокоманд выбирается соответствующая микрокоманда и поступаетна его выходы 17-22. При наличиисигнала на синхровходе регистра 3,микроопераций операционная частьмикрокоманды с выхода 19 микроопераций поступает на информационный входрегистра 3 микроопераций. Сигналымикроопераций с регистра 3 поступаютна выход 16 устройства.43При Формировании адреса очередноймикрокоманды возможны три режима работы устройства: 1) Формирование адреса очередной микрокоманды при выполнении линейных участков микропрограмм (проверка внутренних и внешних логических условий не осуществля.ется); 2) формирование адреса очередной микрокоманды при проверке внешних логических условий; 3) Формирова ние адреса очередной микрокомандыпри проверке внутренних логическихусловий,Рассмотрим работу устройства в этих режимах.Первый режим. При считывании микрокоманды из блока 1 памяти микро- команд адрес очередной микрокоманды формируется следующим образом. Немодифицируемая часть адреса очередной микрокоманды с выхода 22 поступает на информационные входы второй группы коммутатора 5 адреса. Значение модифицируемого разряда адреса очередной микрокоманды поступает с выхода 21 блока 1 памяти микрокоманд через элемент ИЛИ 12 на один из информационных входов второй группы коммутатора 5 адреса. Поскольку сигнал признака конца команды отсутствует, адрес очередной микрокоманды через коммутатор 5 адреса поступает на информационный вход регистра 2 адреса. При Формировании на выходе 24 генератора 10 очередного тактового импульса адрес микрокоманды записывается в регистр 2 адреса. Далее устройство функционирует в этом режиме аналогичным образом.Второй режим. Если при выполнении текущей микрокоманды необходимо проверить значение внешнего логического условия и произвести ветвление микропрограммы, то на выходе 2 Г блока 1 памяти микрокоманд считывается код этого логического условия. Этот код поступает на дешифратор 8 и возбуждает соответствующий проверяемому логическому условию выход первой группы выходов дешифратора 8, Значение проверяемого внешнего логического условия с входа 15 через коммутатор 7 внешних логических условий поступает на элемент ИЛИ 12Формирование значения модифицированного разряда адреса очередной микрокомгнды. осуществляется на элементе ИЛИ 12 путем реализации логической Функции с,= - у- ы + х , значение которой поступа 1)ет на один из информационных входов второй группы коммутатора 5 адреса. Далее устройство функционирует аналогичным образом.Третий режим. Запись значения внутреннего логического условия х в регистр 4 осуществляется следующим образом. При считывании последней микрокоманды фрагмента микропрограммы, после выполнения которого должен выполняться повторяемый участок микропрограммы, на выходе блока 1 памя 1142834 10ти микрокоманд сигнал отсутствует. Значение проверяемого после выполне-. ния повторяемого участка микропрограммы внутреннего логического условия х" с выхода 17 блока 1 памяти 5 микрокоманд поступает на инАормационные входы регистра 4. Код этого логического условия с выхода 20 блока 1 памяти микрокоманд поступает на дешиАратор 8 и возбуждает соответствующий проверяемому логическому условию выход второй группы выходов дешифратора 8. При Аормировании очередного тактового импульса на выходе 242 генератора 10 соответствующий проверяемому внутреннему логическому условию разряд регистра 4 открывается и в него записывается значениепроверяемого внутреннего логического условия, Далее при Аормировании о микрокоманд повторяемого участка микропрограммы устройство Аункционирует так же, как и в первом режиме.При Аормировании последней микро- команды повторяемого участка микропрограммы, после выполнения которой необходимо проверить значение внутреннего логического условия и произвести ветвление микропрограммы, кодлогического условия с выхода 20 бло ка 1 памяти поступает на дешифратор 8, а на выходе 18 блока 1 памяти появляется единичный сигнал. При этом коммутатор 6 внутренних логических условий открывается по соответствующему управляющему входу и значение проверяемого внутреннего логического условия через коммутатор 6 поступает на элемент ИЛИ 12,. При этом формирование значения моди фицированного разряда адреса очередной микрокоманды осуществляется аналогично его Аормированию при Аункционировании устройства во втором режиме работы, 45Работа устройства заканчивается при формировании на выходе 23 регистра 3 признака конца работы, который, поступив на вход установки в ноль триггера 9, устанавливает 50 его в исходное состояние, в результате чего генератор 10 прекращаетформирование тактовых импульсов.Принцип сокращения объема оборудования блока 1 памяти поясняется 55на фиг, 2 и 3.Использование предлагаемого устройства позволяет уменьшить объем оборудования блока 1 памяти микро- команд, а следовательно, и микропрограммного устройства управления в целом на величину1 2где У и У - объем оборудования,гблока 1 памяти микро- команд прототипа (базового объекта) и предлагаемого устройства соответственно.Объем оборудования Ч определяется выражениемй;-М (Ъ+Ь+11 )М 1 Ь 9-1)Ъ+ 1 о Д Я)где . М, - число микрокоманд, хранящихся в блоке 1 памятимикрокоманд;Ь , Ь, Ь- разрядность поля логических условий, полямикрооперации и поляадреса микрокоманд соответственно;- число линейных последовательностей.микрокоманд. формируемых устройст.вом;Й 1- среднее число микрокомандв линейной последовательности микрокоманд, формируемых устройством.Оценку объема оборудования И прог ведем при следующих допущениях: в каждой линейной последовательности микрокоманд имеется с вероятностью рф повторяющийся участок микрокоманд; среднее число микрокоманд в повторянющемся участке равно И2С учетом сделанных допущений число ячеек памяти Иг, необходимых для хранения микрокоманд в предлагаемом устройстве, и разрядность поля адреса Ь и поля логических условий Ь мик" 1м йрокоманд, формируемых устройством, определяется выражениямиР УМ =И- - Й2% М (Ъ 8 +% +9 фиЯЙ - ).Р ям 2 й Х У о 1 - )"2Ь Д Ъ9 Мфяю,) ) 10 где 4 1"=2) - разрядность дополнительно введенного вФормат микрокоманд поля, используемого для15реализации провероквнутренних логическихусловий.Относительный выигрыш в оборудовании предлагаемого устройства по отношению к прототипу (базовому объекту) определяется выражением1 тгМ = ---- 1007Вычислим значение Уи при следующих исходных данных полученных при кодировании микропрограмм:=20; Й= 10; М = 8; р = 0,8;Ь= 60.В этом случае4400Ь 1 = --- 100 ж = З 0,6 Х.14600Следовательно, использование изобретения позволяет существенно уменьшить объем оборудования памяти микрокоманд.1142834 г.д Составитель Ю.Ланцоор Л.Алексеенко Техред С.Мигунова Корректо Самборская 0 писн 4 илиал .ППП "Патентф, г.ухгород, ул.Проектная Заказ 738/42 Тирак 7 ВНИИПИ Государств по делам изобрет 113035, Иосква, Ж-.Зого комитета ССний и открытий Раушская наб.,

СмотретьЗаявка

3655615, 24.10.1983

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, МАЛАХОВ ВИКТОР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 28.02.1985

Код ссылки

<a href="https://patents.su/9-1142834-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство с динамическим измерением приоритета

Случайный патент: Самонастраивающаяся система автоматического цифрового управления ректификационной колонной