Многопрограммный регулятор температуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1136123

Авторы: Алферов, Губайдуллин, Дешков, Самохвалов

Текст

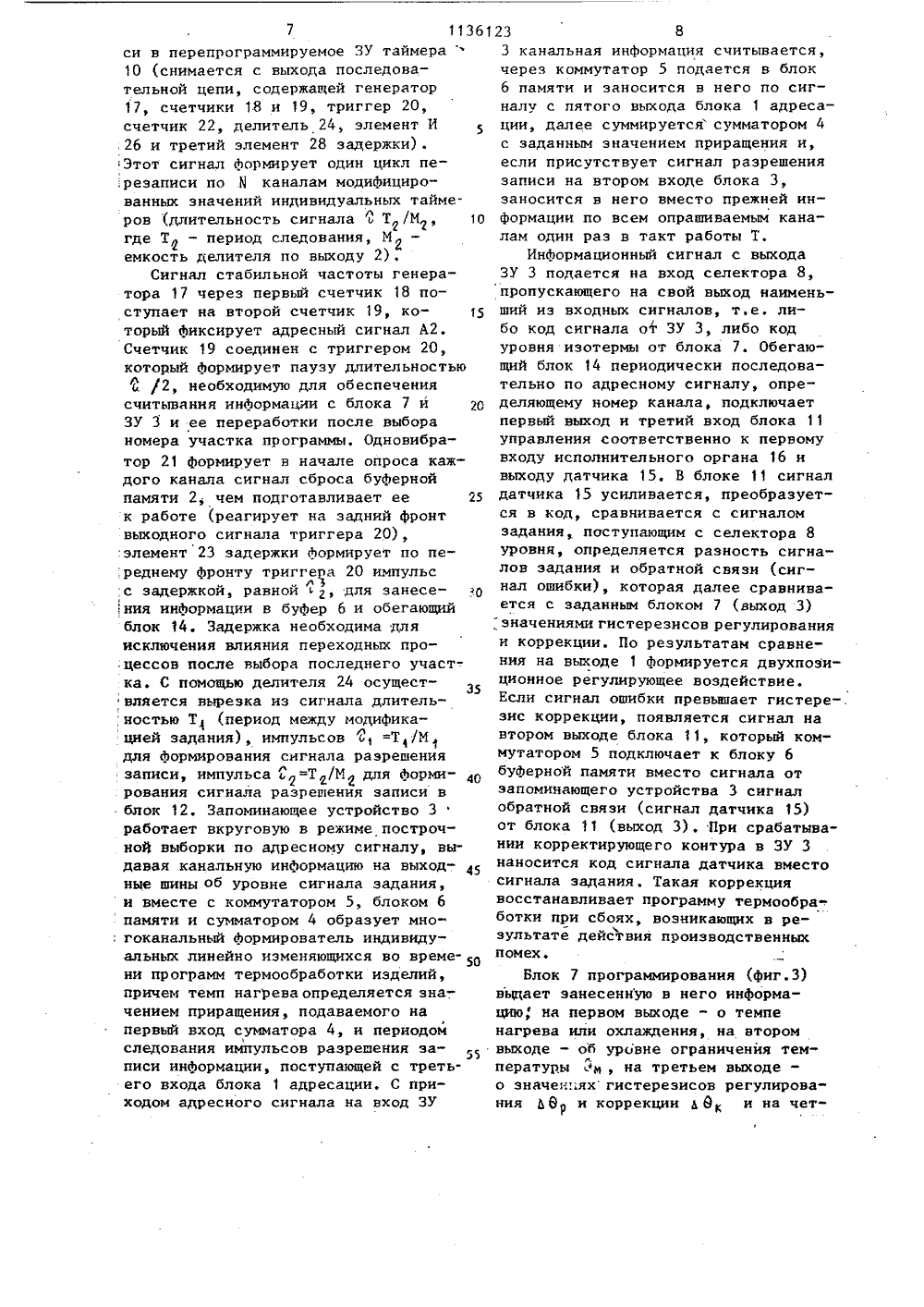

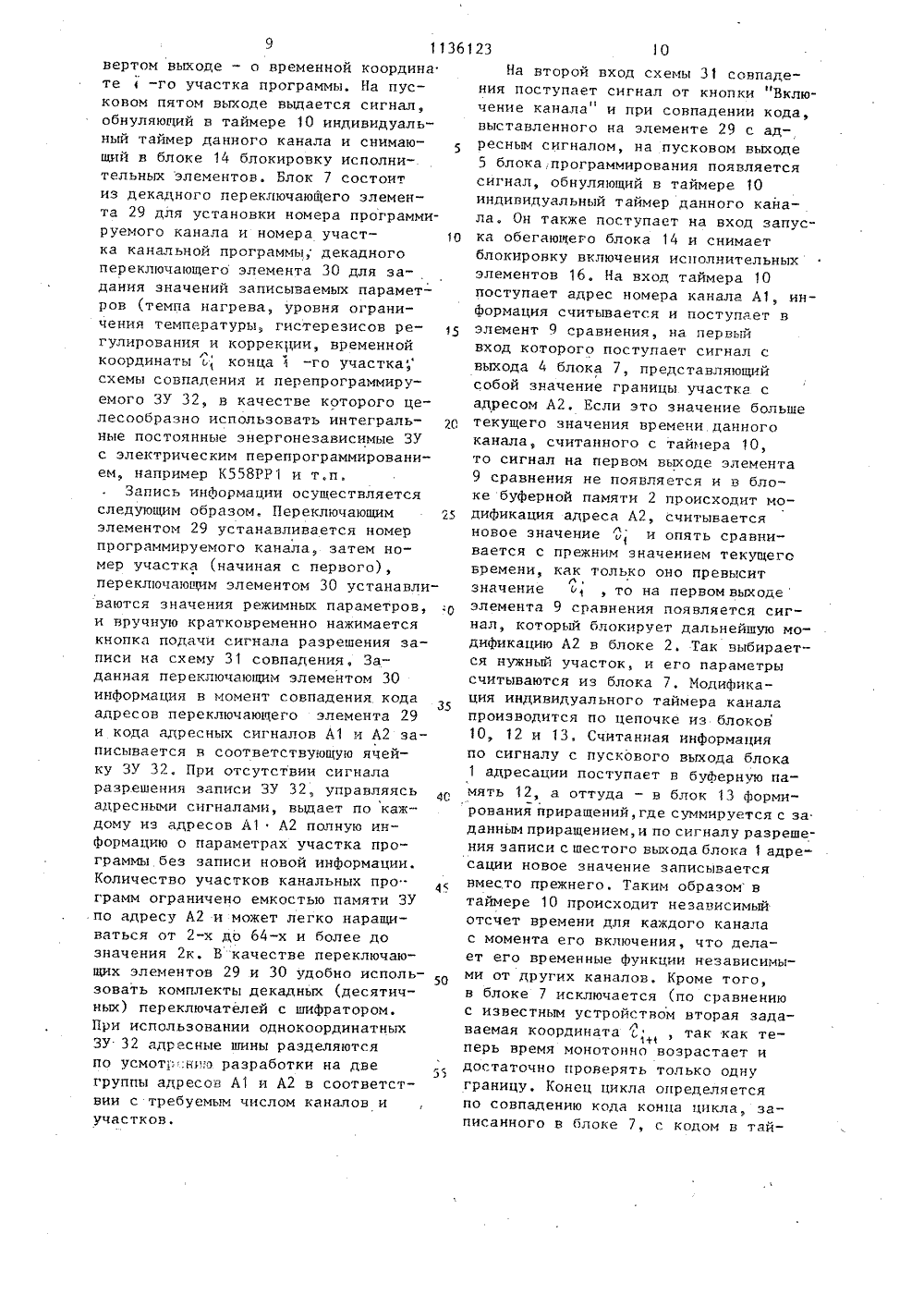

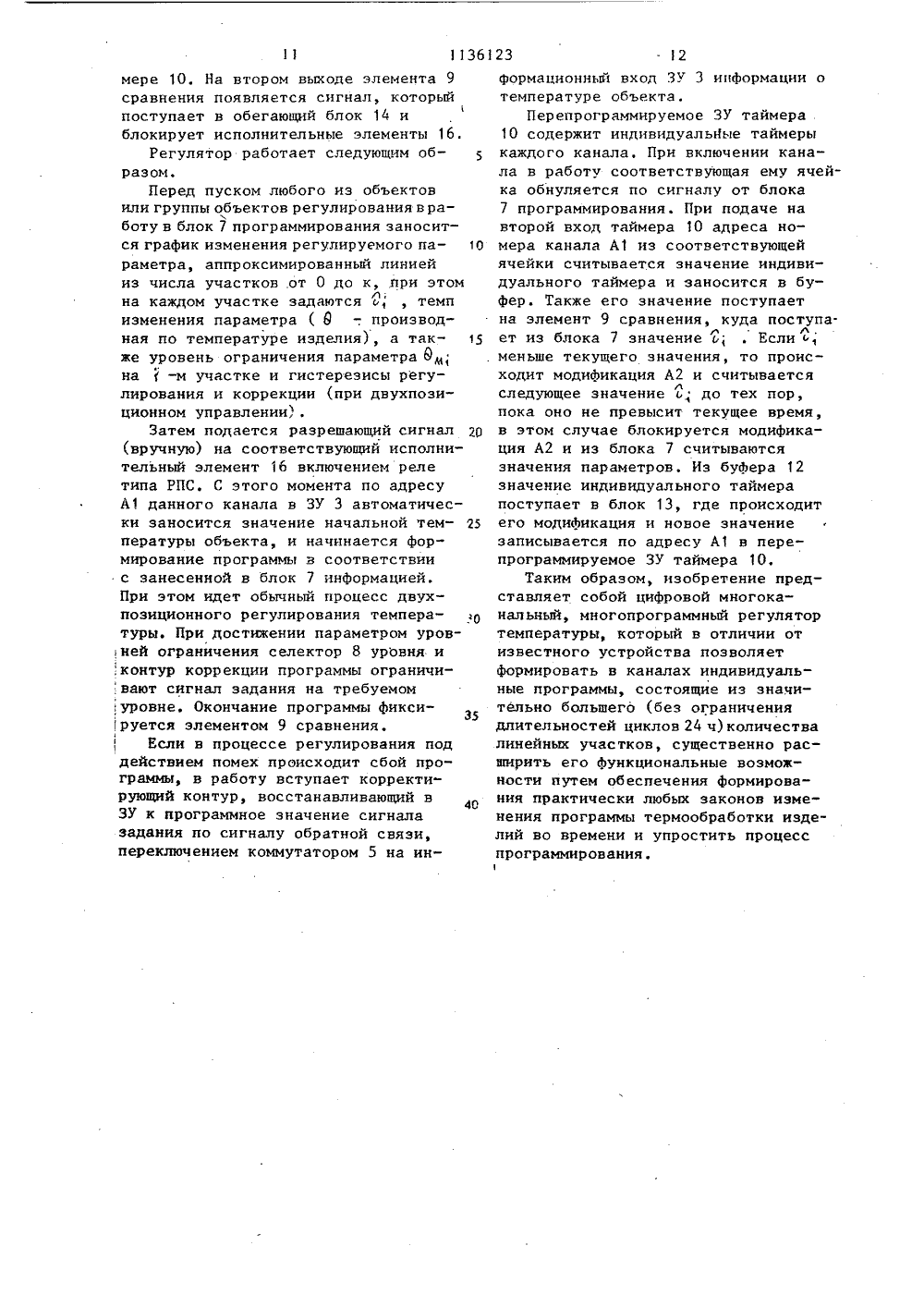

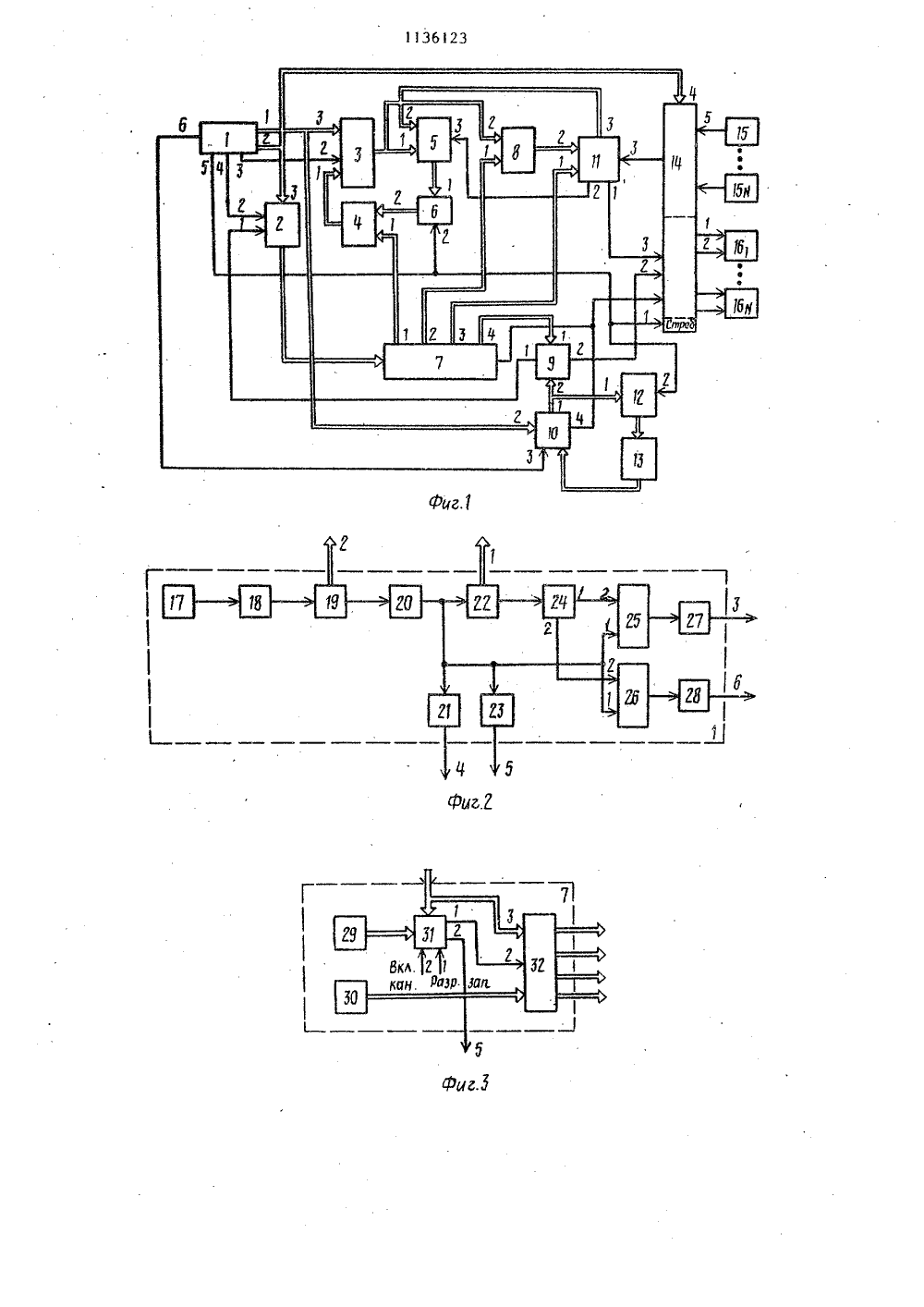

(19) (И) А 1) (:05 Р входометвертыйинены соФдами блотоьм ельн вания, в буФерной приращен де переп го устро жен шест рованиякнций блопервый ика буфер одом таим лока адрыход чер щения ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ ИЗОБРЕ К ДВТОРСИОМУ СВИДЕТЕЛЬСТВ(56) 1. Авторское свидетельство СССР )Р 943667, кл. С 05 1) 23/19, 1982.2, Авторское свидетельство СССР по заявке 1( 3544713/24(15093), кл, С 05 1) 23/19, 21.01.83 (прототип),(54) (57) 1, МНОГОПРОГРАММНЦЙ РЕГУЛЯТОРТЕМПЕРАТУР 11, содержащий блок адресации, первый и второй блоки буфернойпамяти, запоминающее устройство,сумматор, коммутатор, блок программирования, селектор уровня, элементсравнения, таймер, блок управления,обегающий блок, датчики температурыи исполнительные элементы, по одномуна каждый канал регулирования, причем первый и второй выходы блока адресации связаны между собой и подключены к третьим входам запоминающего устройства и второго блока буферной памяти, к вторым входам которых подключены соответственно третийи четвертый выходы блока адресации,выход запоминающего устройства соединен с вторым входом селектора уровня, третьим выходом блока управления, первым и вторым входами коммутатора, выход которого подключен кпервому входу первого блока буфернойпамяти, второй вход которого связанс пятым выходом блока адресации ивходом стробирования обегающего блока, а выход - с первым входом запоминающего устройства через сумматор,другой вход которого связан с первым выходом блока программирования,второй, третий и четвертый выходыкоторого соединены соответственно с первыми входами селектора уровня,блока управления и элемента сравнения, а вход - с выходом второго блока буферной памяти, первый вход ко-.торого подключен к первому выходуэлемента сравнения, вторые вход и выход которого связаны соответственно с выходом таймера и вторымобегающего блока, третий, чи пятый входы которого,соедответственно с первыми выхо ка управления, адресации и выходамидатчиков температуры, а выходы - свходами исполнительных элементови третьим входом блока управления соответственно, второй выход которогосоединен с третьим входом коммутатора, о т л и ч а ю щ и й с я тем,ч , с целью расширения функциональн возможностей путем увеличения сти циклов терморегулиронего введены третий блокпамяти и блок формированияя, а таймер выполнен в вирограммируемого запоминающеиства, блок адресации снабм выходом, блок программи - пусковым выходом, а обегак - входом запуска, причем второй входы третьего блоной памчти соединены с выера и пусковым вьмодом с ации соответственно, а ез блок формирования прирапервым входом таймера,1136123 второй и третий входы которого связаны соответственно с первым и шестымвыходами блока адресации, а четвертый вход - с пусковым выходом блока программирования и входом запуска обегающего блока. 2. Регулятор по п.1, о т л и ч а ю щ и й с я тем, что блок адресации содержит последовательно соединенные генератор, первый и второй счетчики, триггер, третий счетчик, делитель частоты, первый выход которого подключен к одному из входов Изобретение относится к автоматике и может быть использовано для программного регулирования процессов термообработки изделий в группе технологических установок.Известно устройство для программного регулирования температуры, содержащее последовательно соединенный блок адресации, запоминающее устройство, селектор, блок управления, обегающий блок, выходы которого подключены к исполнительным органам и третьему входу блока управления, а выходы - к первому и пятому выходам блока адресации, связанных также с вторым входом блока буферной памяти, . к выходам термодатчиков и второму выходу блока сравнения, коммутатор, входами соединенный с двумя выходами блока управления и выходом запоминающего устройства, а выходом через последовательно соединенные блок буферной памяти и сумматор - с первым входом запоминающего устройства, блок программирования, связанный с . первыми входами сумматора, селектора, блока управления и блока сравнения и с вторым входом обегающего блока, подключенного к таймеру. Блок адресации состоит из генератора, счетчика, элемента И. Блок программирования содержит блок переключателей и перепрограммируемое запоминающее устройство Я .Однако это устройство реализует программу, состоящую только из трех первого элемента И, второй выход - кодному из входов второго элементаИ, другие входы элементов И связанымежду собой, с выходом триггера ичерез одновибратор и второй элемент.задержки - с четвертым и пятым выходами блока адресации соответственно,выходы элементов И соединены соответственно через первый и третийэлементы задержки с третьим и шестымвыходами блока адресации, первыми вторым выходами которого являютсявторые выходы третьего и второгосчетчиков соответственно,линейных участков, что ограничиваетобласть его примененияИзвестен также многоканальныйрегулятор температур, содержащий последовательно соединенные блок адресации, запоминающее устройство, селектор, блок управления, сбегающийблок, выходы которого подключены кисполнительным органам и третьемувходу блока управления, а входы -к первому и пятому выходам блокаадресации, связанных также с вторымвходом блока буферной памяти, к выводам термодатчика и второму выходуэлемента сравнения, коммутатор, входами соединенный с двумя выходамиблока управления и выходом запоминающего устройства, а выходом - черезпоследовательно соединенные блокбуферной памяти и первый сумматор спервым входом запоминающего устройства, блок программирования, связанный с первыми входами первого сумматора, селектора, блока управления,элемента сравнения, второй блок буферной памяти, выход которого соединен с входом блока программирования,первый вход связан с первым выходомэлемента сравнения, второй вход - счетвертым выходом блока адресации,первый и второй выходы которого подключены к третьему входу второгоблока буферной памяти. Блок адресации содержит последовательно соединенные генератор, два счетчика, триггер, третич счетчик, делитель,3 1136элемент И, элемент задержки, а такжеодновибратор. Блок программированиясодержит последовательно. соединенные первый блок переключателей, элемент совпадения и перепрограммируемое запоминающее устройство и второй блок переключателей, подключенный к информационному входу перепрограммируемого запоминающего устройства, адресный вход которого связан с вто О рым входом схемы совпадения 21 .Однако на практике требуется формирование сложньм законов управления, обладающих длиннопериодическими цик.лами. 15Кроме того, устройство имеет общий таймер, не позволяет реализовать программы длительностью более 24 ч, так как в этом случае возможно совпадение числовых значений задан О ных временных интервалов, относящихся к разным суткам, что приводит к ложному отключению каналов регулятора или нарушению программы (ошибка в выборе участка программы), а 25 также усложняет программирование временных координат, так как в начале каждого цикла работы для всех каналов приходится пересчитывать вГ .менные.координаты относительно начала времени запуска данного канала, кроме того, приходится Задавать две временные координаты для каждого участка, что обусловлено сложностью реализации функции выбора участка программы (проверка нескольких логических условий).Цель изобретения - расширение функциональных возможностей путем увеличения длительности циклов термоО регулирования.Указанная цель достигается тем, что в многопрограммньп регулятор температуры, содержащий блок адресации, первый и второй блоки буферной памяти, запоминающее устройство, сумматор, коммутатор, блок программирования, селектор уровня, элемент сравнения, таймер, блок управления, обегающий блок, датчики температуры и исполнительные элементы, но одному на каждый канал регулирования, причем первый и второй выходы блока адресации связаны между собой и под- ключены к третьим входам запоминаю 55 щего устройства и второго блока буферной памяти, к вторым входам которых подключены соответственно тре 123 4тий и четвертый выходы блока адресации, выход запоминающего устройства соединен вторым входом селектора уровня, с третьим вьмодом блока управления, первым и вторым входами коммутатора, выход которого подключен к первому входу первого блока буферно памяти, второй вход которого связай с пятым выходом блока адресации и входом стробирования обегающего блока, а выход - с первым входом запоминающего устройства через сумматор, другой вход которого связан с первым выходом блока программирования, второй, третий и четвертый вьмоды которого соединены соответственно с первыми входами селектора уровня, блока управления и эле" мента сравнения, а вход - с выходом второго блока буферной памяти, первый вход которого подключен к первому выходу элемента сравнения, вторые вход и выход которого связаны соответственно с выходом таймера и вторым входом обегающего блока, третий, четвертый и пятьн 1 входы которого соединены соответственно с первыми выходами блоков управления, адресации и выходами датчиков температуры, а выходы - с входами исполнительных элементов и третьим входом блока управления соответственно, второй выход которого соединен с третьим входом коммутатора, введены третий блок буферной памяти и блок формирования приращения, а таймер выполнен в виде перепрограммируемого запоминающего устройства; блок адресации снабжен шестым выходом, блок программирования- пусковым выходом, а обегающий блок входом запуска, причем первый ивторой входы третьего блока буферной памяти соедчнены с выходом таймера и пусковым вьмодом блока адресации соответственно, а выхсд через блок формирования приращения - с первым входом таймера, второй и третий входы которого связаны соответственно с первым и шестым выходами блока адресации, а четвертый входс пусковым выходом блока программирования н входом запуска обегающего блока.Кроме ".,го, блок адресации содержит последовательно соединенные генератор, первый и второй счетчики, триггер, третий счетчик, делительчастоты, первый выход которого подключен к одному из входов первогоэлемента И, второй выход - к одномуиз входов второго элемента И, другиевходы элементов И связаны между 5собой, с выходом триггера и черезодновибратор и второй элемент задержки " с четвертым и пятым выходамиблока адресации соответственно, выходы элемента И соединены соответственно через первый и третий элементы задержки с третьим и шестым выходами блока адресации, первым ивторым выходами которого являютсявторые выходы третьего и второгосчетчиков соответственно.На фиг.1-3 приведены структурныесхемы соответственно многопрограммного регулятора температуры, блокаадресации и блока программирования,на Фиг,4 - временные диаграммы работы регулятора.Регулятор содержит блок 1 адресации, второй блок 2 буферной памяти,запоминающее устройство (ЗУ) 3,сумматор 4, коммутатор 5, первыйблок 6 буферной памяти, блок 7 программирования, селектор 8 уровня,элемент 9 сравнения, таймер 10, блок11 управления, третий блок 12 буфер-, 30ной памяти, блок 13 формированияприращения, обегающий блок 14, датчики 15 температуры, исполнительныеэлементы 16, генератор 17, первый 1.8и второй 19 счетчики, триггер 20, Зодновибратор 21, третий счетчик 22,второй элемент 23 задержки, делитель24 частоты, первый 25 и второй 26элементы И первый элемент 27 задержки, третий элемент 28 задержки, 40блоки 29 и 30 переключателей, схему31 совпадения, перепрограммируемоезапоминающее устройство 32.Блоки и узлы регулятора выполня"ют следующие функции. 45Блок адресации служит для формирования по временной диаграмме(Фиг.4) сигналов на выходах 1-6,блок 2 буферной памяти предназначендля временного хранения и выдачи в 0блок 7 программирования адреса номера участка А 2, ЗУ 3 - для формирования индивидуальных программ по каждому каналу, сумматор 4 - для модиФикации индищщуальных программ в уЗУ Зф коммутатор 5 управляет занесением в блок 6 буферной памяти либо сигнала задания, либо сигнала коррекции; блок 7 программирования задает индивидуальчые параметры программ по каждому каналу и каждому участку в канале; селектор 8 уровня служит ограничителем максимального значения программ, элемент 9 сравнения выбирает номер участка, на котором находится данный канал таймер 10, выполненный в виде перепрограммируемого запоминающего устройства, предназначен для запоминания индивидуальных времен работы каналов, блок 11 управляет работой коммутатора и обегающего блока 14; блок 12 буферной памяти и блок 13 формирования приращений предназначены для модификации индивидуальных времен в таймере 10, обегающий блок 14 коммутирует соответствующие данному каналу датчики 15 температуры и исполнительные элементы 16.Блок 1 адресации (фиг.2) формирует по временной диаграмме (фиг.4) следующие сигналы на выходах 1-6: адресный сигнал А 1 (выход 1), снимаемый с разрядных выходов счетчика 22, имеющего емкость Д , равную числу каналов регулирования (этот сигнал служит для управления ЗУ 3, обегающим блоком 14, блоком 7 программирования и программируемым ЗУ таймером 10; адресный сигнал А 2 (выход 2), снимаемый со счетчика 19 с емкостью К, равной максимальному числу участков программы термообработки каждого канала (этот сигнал служит для управления считыванием информации с блока 7); сигнал разрешения записи ЗУ 3 информации, поступающей с сумматора 4 (снимается с выхода последовательной цепи, содержащей генератор 17, счетчики 18 и 19, трит. гер 20, счетчик 22, делитель 24, элемент И 25 и первый элемент 27 задержки, и формирует через каждый период Т=К 2 Й М, один цикл перезаписи по Й каналам, где ь и М емкости счетчика 18 и делителя 24 по выходу 1); импульс на сброс памяти блока 2 в начальный момент опроса каждого. канала (выход 4), стробирующий импульс на выходе 5 для записи информации в блок 6 памяти и записи логического уровня управляющего сигнала от блока 11, поступающего через блок 14 в фиксаторы нулевого порядка исполнительных элементов 16, сигнал разрешения запи,26 и третий элемент 28 задержки).Этот сигнал Формирует один цикл перезаписи по я каналам модифицированных значений индивидуальных тайме.ров (длительность сигнала ь Т 2 /М , 1 Огде Т - период следования, Мемкость делителя по выходу 2).Сигнал стабильной частоты генератора 17 через первый счетчик 18 поступает на второй счетчик 19, который Фиксирует адресный сигнал А 2.Счетчик 19 соединен с триггером 20,который Формирует паузу длительностьюь. /2, необходимую для обеспечениясчитывания информации с блока 7 и 20ЗУ 3 и ее переработки после выбораномера участка программы. Одновибратор 21 Формирует в начале опроса каждого канала сигнал сброса буфернойпамяти 2, чем подготавливает ее 25к работе (реагирует на задний фронтвыходного сигнала триггера 20),:элемент 23 задержки Формирует по переднему Фронту триггера 20 импульсс задержкой, равной, для занесе,ния информации в буфер б и обегающийблок 14. Задержка необходима дляисключения влияния переходных процессов после выбора последнего участ-.ка. С помощью делителя 24 осуществляется вырезка из сигнала длительностью Т 1 (период между модифика цией задания), импульсов о 1 =Т/Мдля Формирования сигнала разрешениязаписи, импульса о 2 =Т/М для Формирования сигнала разрешения записи вблок 12Запоминающее устройство 3работает вкруговую в режиме построчной выборки по адресному сигналу, выдавая канальную информацию на выход"ные шины об уровне сигнала задания,и вместе с коммутатором 5, блоком 6памяти и сумматором 4 образует мно; гоканальный Формирователь индивидуальных линейно изменяющихся во време- они программ термообработки изделий,причем темп нагреваопределяется значением приращения, подаваемого напервый вход сумматора 4, и периодомследования импульсов разрешения записи информации, поступающей с третьего входа блока 1 адресации, С приходом адресного сигнала на вход ЗУ 123 83 канальная информация считывается, через коммутатор 5 подается в блок 6 памяти и заносится в него по сигналу с пятого выхода блока 1 адресации, далее суммируется сумматором 4 с заданным значением приращения и, если присутствует сигнал разрешения записи на втором входе блока 3, заносится в него вместо прежней информации по всем опрашиваемым каналам один раэ в такт работы Т.Информационный сигнал с выхода ЗУ 3 подается на вход селектора 8, пропускающего на свой выход наименьший иэ входных сигналов, т.е, либо код сигнала от ЗУ 3, либо код уровня изотермы от блока 7. Обегающий блок 4 периодически последовательно по адресному сигналу, определяющему номер канала, подключает первый выход и третий вход блока 11 управления соответственно к первому входу исполнительного органа 16 и выходу датчика 15. В блоке 11 сигнал датчика 15 усиливается, преобразуется в код, сравнивается с сигналом задания, поступающим с селектора 8 уровня, определяется разность сигналов задания и обратной связи (сигнал ошибки), которая далее сравнивается с заданным блоком 7 (выход 3)значениями гистерезисов регулирования н коррекции. По результатам сравнения на выходе 1 Формируется двухпозиционное регулирующее воздействие. Если сигнал ошибки превышает гистере-. зис коррекции, появляется сигнал на втором выходе блока1, который коммутатором 5 подключает к блоку 6 буферной памяти вместо сигнала от запоминающего устройства 3 сигнал обратной связи (сигнал датчика 15) от блока 11 (выход 3), При срабатывании корректирующего контура в ЗУ 3 наносится код сигнала датчика вместо сигнала заданияТакая коррекция восстанавливает программу термообработки при сбоях, возникающих в результате действия производственныхпомех,Блок 7 программирования (фиг 3) выдает занесенную в него информацию, на первом выходе - о темпенагрева или охлаждения, на втором выходе - об уровне ограничения температуры .фн, на третьем выходео значен.ях гистерезисов регулирования ь 9 р и коррекции ь Ок и на чет 1136123 10вертом выходе - о временной координа те-го участка программы. На пусковом пятом выходе выдается сигнал, обнуляющий н таймере 10 индивидуальный таймер данного канала и снимающий в блоке 14 блокировку исполнительных элементов. Блок 7 состоит из декадного переключающего элемента 29 для установки номера программируемого канала и номера участ О ка канальной программы; декадного переключающего элемента 30 для задания значений записываемых параметров (темпа нагрева, уровня ограничения температуры, гистерезисов регулирования и коррекции, временной координаты ь, конца 1 -го участка", схемы совпадения и перепрограммируемого ЗУ 32, в качестве которого целесообразно использовать интеграль- О ные постоянные энергонезависимые ЗУ с электрическим перепрограммированием, например К 558 РР 1 и т,п.Запись информации осуществляется следующим образом, Переключающим д элементом 29 устанавливается номер программируемого канала, затем номер участка (начиная с первого), переключающим элементом 30 устанавлинаются значения режимных параметров, и нручную кратковременно нажимается кнопка подачи сигнала разрешения записи на схему 31 совпадения, Заданная переключающим элементом 30 информация н момент совпадения кода 35 адресов переключающего элемента 29 и кода адресных сигналов А 1 и А 2 записывается н соответствующую ячейку ЗУ 32, При отсутствии сигнала разрешения записи ЗУ 32, управляясь адресными сигналами, выдает по каждому из адресов А 1А 2 полную инФормацию о параметрах участка программы без записи новой информации. Количество участков канальных программ ограничено емкостью памяти ЗУ по адресу А 2 и может легко наращиваться от 2-х до 64-х и более до значения 2 к. В качестве переключающих элементов 29 и 30 удобно использовать комплекты декадных (десятичных) переключателей с шифратором. При использовании однокоординатных ЗУ 32 адресные шины разделяются по усмотр .нию разработки на две группы адресов А 1 и А 2 в соответствии с требуемым числом каналов и участков. На второй вход схемы 31 совпадения поступает сигнал от кнопки "Включение канала" и при совпадении кода,выставленного на элементе 29 с адресным сигналом, на пусковом выходе5 блокапрограммирования появляетсясигнал, обнуляющий н таймере 10индивидуальный таймер данного канала. Он также поступает на вход запуска обегающего блока 14 и снимаетблокировку включения исполнительныхэлементов 16. На вход таймера 10поступает адрес номера канала А 1, инФормация считывается и поступает вэлемент 9 сравнения, на первыйвход которого поступает сигнал свыхода 4 блока 7, представляющийсобой значение границы участка садресом А 2, Если это значение большетекущего значения времени данногоканала, считанного с таймера 10,то сигнал на первом выходе элемента9 сравнения не появляется и в блоке буферной памяти 2 происходит модификация адреса А 2, считываетсяновое значение " и опять сравнивается с прежним значением текущеговремени, как только оно превыситл,значение ь, то на первом выходеэлемента 9 сраннения появляется сигнал, который блокирует дальнейшую модификацию А 2 в блоке 2. Так выбирается нужный участок, и его параметрысчитываются из блока 7. Модификация индивидуального таймера каналапроизнодится по цепочке из блоков10, 12 и 13, Считанная информацияпо сигналу с пускового выхода блока1 адресации поступает в буферную память 12, а оттуда - н блок 13 формирования приращений, где суммируется с заданным приращением, и по сигналу разрешения записи с шестого выхода блока 1 адресации новое значение записываетсявместо прежнего, Таким образом втаймере 10 происходит независимыйотсчет времени для каждого каналас момента его включения, что делает его временные функции независимыми от других каналов, Кроме того,в блоке 7 исключается (по сравнениюс известным устройством вторая задаваемая координататак как теперь время монотонно возрастает идостаточно проверять только однуграницу, Конец цикла определяетсяпо совпадению кода конца цикла, записанного в блоке 7, с кодом в таймере 10, На втором выходе элемента 9 сравнения появляется сигнал, который поступает в обегающий блок 14 и блокирует исполнительные элементы 16.Регулятор работает следующим образом.Перед пуском любого из объектов или группы объектов регулирования в работу в блок 7 программирования заносится график изменения регулируемого па раметра, аппроксимированный линией из числа участков .от 0 до к, при этомл; на каждом участке задаются темп изменения параметра ( Ц в , производная по температуре изделия), а так же уровень ограничения параметра 9 А на-м участке и гистереэисы регулирования и коррекции (при двухпозиционном управлении) .Затем подается разрешающий сигнал 2 р (вручную) на соответствующий исполнительный элемент 16 включением реле типа РПС, С этого момента по адресу А 1 данного канала в ЗУ 3 автоматически заносится значение начальной тем пературы объекта, и начинается формирование программы в соответствии с занесенной в блок 7 информацией. При этом идет обычный процесс двух- позиционного регулирования температуры, При достижении параметром уров,ней ограничения селектор 8 уровня и ,контур коррекции программы ограничи,вают сигнал задания на требуемом :уровне. Окончание программы фиксируется элементом 9 сравнения.Если в процессе регулирования под действием помех происходит сбой программы, в работу вступает корректи" рующий контур, восстанавливающий в ЗУ к программное значение сигнала задания по сигналу обратной связи, переключением коммутатором 5 на информационный вход ЗУ 3 информации о температуре объекта.Перепрограммируемое ЗУ таймера 10 содержит индивидуальные таймеры каждого канала, При включении канала в работу соответствующая ему ячейка обнуляется по сигналу от блока 7 программирования. При подаче на второй вход таймера 10 адреса номера канала А 1 из соответствующей ячейки считывается значение индивидуального таймера и заносится в буфер. Также его значение поступает на элемент 9 сравнения, куда поступа.л, л. ет из блока 7 значение о; . Еслименьше текущего значения, то происходит модификация А 2 и считываетсялследующее значение о; до тех пор, пока оно не превысит текущее время, в этом случае блокируется модификация А 2 и из блока 7 считываются значения параметров, Из буфера 12 значение индивидуального таймера поступает в блок 13, где происходит его модификация и новое значение записывается по адресу А 1 в перепрограммируемое ЗУ таймера 10.Таким образом, изобретение представляет собой цифровой многоканальный, многопрограммный регулятор температуры, который в отличии от известного устройства позволяет формировать в каналах индивидуальные программы, состоящие из значительно большего (без ограничения длительностей циклов 24 ч) количества линейных участков, существенно расширить его функциональные возможности путем обеспечения формирования практически любых законов изменения программы термообработки изделий во времени и упростить процесс программирования.11136123 Составитегь Г.КреймРедактор С.Саенко Теехред,З.Палий Коррек Сирохман 0609 Тираа 863 ВНИИПИ Государственного комитета СС по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., Зека пиское 5 Филиал ППП "Патент", г. Уагород, ул. Проектная, 4

СмотретьЗаявка

3643798, 16.09.1983

ГОСУДАРСТВЕННЫЙ ПРОЕКТНЫЙ И НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ "ЧЕЛЯБИНСКИЙ ПРОМСТРОЙНИИПРОЕКТ"

ГУБАЙДУЛЛИН ГЕРМАН АСФОВИЧ, АЛФЕРОВ ГЕРМАН ДМИТРИЕВИЧ, ДЕШКОВ АЛЕКСАНДР ТИМОНОВИЧ, САМОХВАЛОВ БОРИС МИХАЙЛОВИЧ

МПК / Метки

МПК: G05D 23/19

Метки: многопрограммный, регулятор, температуры

Опубликовано: 23.01.1985

Код ссылки

<a href="https://patents.su/9-1136123-mnogoprogrammnyjj-regulyator-temperatury.html" target="_blank" rel="follow" title="База патентов СССР">Многопрограммный регулятор температуры</a>

Предыдущий патент: Регулятор температуры

Следующий патент: Термогигростат

Случайный патент: Устройство для контроля магнитных сердечников