Система передачи дискретной информации с решающей обратной связью

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1111258

Авторы: Захарченко, Киреев

Текст

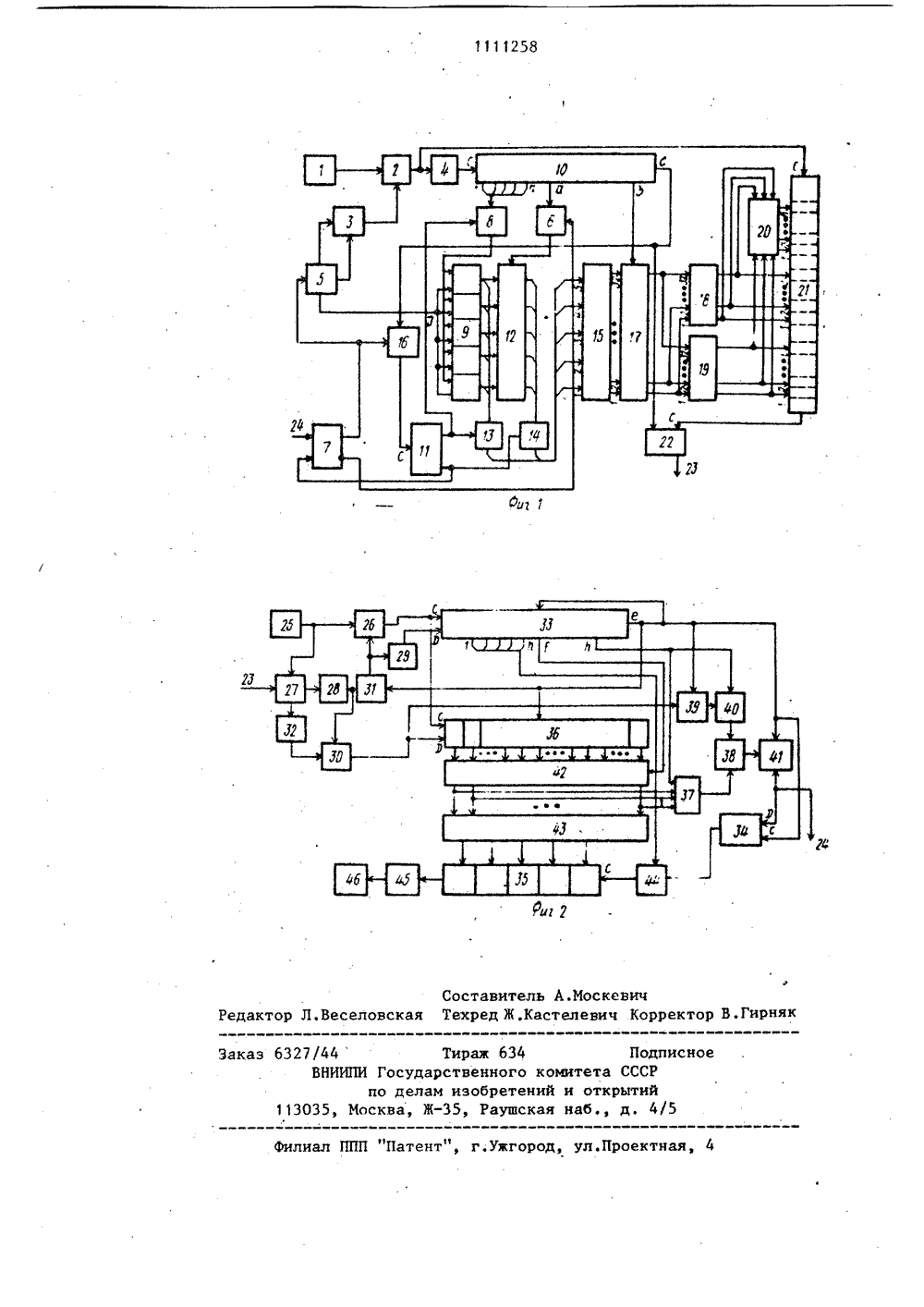

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК Н 04 1 1/12 ИЕ ИЗОБРЕТЕНИЯУ СВИДЕТЕЛЬСТВУ ОПИСА ГОСУДАРСТВЕНМЬ 1 Й КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ(21) 3610276/18-09(46) 30.08.84. Бюл. В 32 (72) Н,В.Захарченко и И.А.Киреев (71) Одесский электротехнический институт связи им. А.С.Попова (53) 621.394.6(088.8)(56) 1. Авторское свидетельство СССР У 517174, кл. Н 04 1 1/12, 1974.2. Пуртов Л.П, и др. Элементы теории передачи дискретной информации. М., "Связь", 1972, с. 167-181 (прототип).(54)(57) СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ . ИНФОРМАЦИИ С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ, содержащая на передающей стороне последовательно соединенные генератор и первый элемент И, к второму входу которого подключен выход триггера управления, входы которого соединены с одними выходами источника информации, другой выход которого подключен к сигнальным входам регистрирующего блока, управляющие входы которого соединены с выходом первого коммутатора, к первому входу которого подключены одни выходы пер-. вого регистра сдвига, другие выходы которого соединены соответственно с первым входом выходного триггера, выход которого подключен к входу прямого канала, и с первым входом второго элемента И, выход которого соединен с управляющим входом блока накопителей, сигнальные входы которого соединены с выходами регистрирующего блока и с первым входом второго коммутатора, второй вход которого соединен с вторым входом первого коммутатора и с первым выходом второго ре 80;, 113 1258 А гистра сдвига, выходы блока накопи- . телей подключены к первому входу третьего коммутатора, второй вход которого соединен с вторым выходом второго регистра сдвига и с первым входом триггера блокировки, первый и второй выходы которого соединены соответственно с входом источника информации и с вторым входом второго элемента И, второй вход триггера блокировки соединен с выходом обратного канала, а на приемной .стороне - генератор, выход которого подключен к первым входам первого элемента И И входного триггера, второй вход и первый выход которого соединены со- Сфе ответственно с выходом прямого канала и со входом первого дифференцирующего блока, выход которо о подключен к первому входу триггера управления, выход которого соединен с вторым входом первого элемен та И и с входом второго дифферен- файф цирующего блока, выход которого под- эффаа ключен к первому входу первого ре" )ива гистра сдвига, один выход которого ры соединен с установочным входом пер- фр вого регистра сдвига, с вторым входом р триггера управления, с первым входом триггера блокировки и с первым входом второго регистра сдвига, второй вход которого соединен с выходом триг гера блокировки и с входом обратного канала, выход второго регистра сдвигаподключен к первому входу коммутатора, второй вход и выход которого соединены соответственно с другими выходами первого регистра сдвига и с одним входом третьего регистра сдвига, выход которого через выходной согласующий блок подключен к входу1111258 потребителя информации, о т л и -ч а ю щ а я с я тем, что, с цельюповышения помехоустойчивости, на передающей стороне введены третий регистр сдвига, решающий блок, двашифратора, четвертью коммутатор, преобразователь кода, третий элемент Ии делитель частоты, выход которогоподключен к входу первого регистрасдвига, другой выход которого соединен с .первым входом третьего элемен-та И, второй вход и выход которогосоединены соответственно с первымвыходом триггера блокировки и с входом второго регистра сдвига, а дополнительный выход первого регистрасдвига подключен к управляющему входу четвертого коммутатора, сигнальныевходы которого соединены с выходамипреобразователя кода, ко входам которого подключены выходы второго итретьего коммутаторов, при этом выходпервого элемента И соединен с входомделителя частоты и с управляющим входом третьего регистра сдвига, к сигнальным входам которого подключенывыходы шифраторов и решающего блока,к входам которого. подключены выходышифраторов, входы которых соединеныс выходами четвертого коммутатора,выход третьего регистра сдвига подключен к второму входу выходноготриггера, а на приемной стороне введены третий дифференцирующий блок,два элемента ИЛИ, счетчик, второй итретий элементы И, решающий блок,четвертый регистр сдвига и преобразоИзобретение относится к технике- телеграфной связи и может использоваться в. системах йередачи дискретной информации с.решающей обратной связью, 5Известна система передачи дискретной информации с решающей обратной связью, содержащая на передающей стороне генератор, элементы И, регистрирующий. блок, регистры сдвига, триггеры, накопитель, коммутаторы, а на приемной стороне - генератор, регистры сдвига, логические схемы, триггеры и дифференцирующие цепочки С 13,15 ватель кода, входы которого соединены с одними входами второго элемента И и с выходами решающего блока,к входам которого подключены выходычетвертого регистра сдвига, первыйвход которого соединен с первым входом счетчика, к второму входу которого подключен один выход первогорегистра сдвига, и с выходом первогоэлемента ИЛИ, к входам которого подключены выход третьего дифференцирующего блока, вход которого соединенс торым выходом входного триггера,и первый вход триггера управления,второй вход которого соединен с однимвыходом первого регистра сдвига и сустановочным входом четвертого регистра сдвига, второй вход которого соединен с выходом первого элемента Ии с вторым входом первого регистрасдвига, первый дополнительный выходкоторого подключен к другому входувторого элемента И, выход которогосоединен с первым входом второго элемента ИЛИ,и к первому входу третьегоэлемента И, второй вход и выход которого соединены соответственно с выходомсчетчика и с вторым входом второгоэлемента ИЛИ, выход которого подключен к второму входу триггера блокировки, причем второй дополнительный выход первого регистра сдвигаподключен к соЬтветствующему входурешающего блока, выходы преобразователя кода соединены с другими входами третьего регистрасдвига. Однако известная система имеет низкую скорость передачи информации,обусловленную необходимостью передачиизбыточной информации для обнаруженияошибок,Наиболее близкой к предложеннойпо техническому решению является система передачи дискретной информациис решающей обратной связью, содержащая на передающей стороне последовательно соединенные генератор и первый элемент И, к второму входу которого подключен выход триггера управления, входыкоторого соединены с3 , 11112 одними выходами источника информации, другой выход которого подключен к сигнальным входам регистрирующего блока, управляющие входы которого соединены с выходом первого коммутатора, к первому входу которогоподключены одни выходы первого регистра сдвига, другие выходы которого,соединены соответственно с первым входом выходного триггера, выход ко" торого. подключен к входу прямого канала, и с первым входом второго элементч И, выход которого соединен .с управляющим входом блока накопителей, сигнальные входы которого соединены с выходами регистрирующего блока и с первым входом второго коммутатора, второй вход которого соединен с вторым входом первого коммутатора и с первым выходом второго регистра сдви га, выходы блока накопителей подключены к первому входу третьего коммутатора, второй вход которого соединен с вторым выходом второго регистра сдвига и с первым входом триггера 25 блокировки, первый и второй выходы которого соединены соответственно с входом источника информации и с вторым входом второго элемента И, второй вход триггера блокировки соединен З 0 с выходом обратного канала, а на приемной стороне - генератор, выход которого подключен к первым входам первого элемента И и входного триггера, второй вход и первый выход кото 35 рого соединены соответственно с выхо,цом прямого канала и с входом первого дифференцирующего блока, выход которого подключен к первому входу триггера управления, выход. которого сое- динен с вторым входом первого элемента И н с входом втоРого дифференцирующего блока, выход которого подключен к первому входу первого регистра сдвига, один выход которого соединен с установочным входом первого регистра сдвига, с вторым входом триггера управления, с первым входом триггера блокировки и с первым входом второго регистра сдвига, второй вход которого50 соединен с выходом триггера блокировки и с входом обратного канала, выход второго регистра сдвига подключен к первому входу коммутатора, второй вход и выход которого соединеньГ соот" ветственно с другими выходами перво"55 го регистра сдвига и с одним входом третьего регистра сдвига, выход которого через выходной согласующий блок 58 4подключен к входу потребителя информации Г 23.Однако известная система имеет низкую помехоустойчивость.Цель изобретения - повышение помехоустойчивости.Поставленная цель достигается тем, что в системе передачи дискретной информации с решающей обратной связью, содержащей на передающей стороне последовательно соединенные генератор и первый элемент И, к второму входу которого подключен выход триггера управления, входы которого соединены с одними выходами источника информации, другой выход которого подключенк сигнальным входам регистрирующего блока, управляющие входы которого соединены с выходом первого коммутатора, к первому входу которого подключены одни выходы первого регистра сдвига, другие выходы которого соединены соответственно с первым входом выходного триггера, выход которого подключен к входу прямого канала, и с первым входом второго элемента И, выход которого соединен с управляющим входом блока накопителей, сигнальные входы которого соединены с выходами регистрирующего блока и с первым входом второго коммутатора, второй вход которого соединен с вторым входом первого коммутатора и с первым выходом второго регистра сдви га, выходы блока накопителей подключены к первому входу третьего коммутатора, второй вход которого соединен с вторым выходом второго регистра сдвига и с первым входом триггера блокировки, первый и второй выходы которого соединены соответственнос входом источника информации и с вторым входом второго элемента И, второй вход триггера блокировки соединен с выходом обратного канала, а на приемной стороне - генератор, выход которого подключен к первым входам первого элемента И и входного триггера, второй вход и первый выход которого соединены соответственно с выходом прямого канала и с входом первого дифференцирующего блока, выход которого подключен к первому входу триггера. управления, выход которо-,го соединен с вторым входом первогоэлемента И и с входом второго диф"ференцирующего блока, выход которогоподключен к .первому входу первогорегистра сдвига, один выход которого11112соединен с установочным входом первого регистра сдвига, с вторым входомтриггера. управления, с первым входомтриггера блокировки и с первым входом второго регистра сдвига, второйФвход которого соедичен с выходомтриггера блокировки и с входом обрат ого канала, выход второго регистрадвига подключен к первому входуоммутатора, второй вход и выход коорого соединены соответственнос другими выходами первого регистрасдвига и с одним входом третьего регистра сдвига, выход которого черезвьмодной согласующий блок подключенк входу потребителя информации, напередающей стороне введены третийрегистр сдвига, решающий блок, двашифратора, четвертый коммутатор,преобразователь кода, третий элемент И и делитель частоты, выход которого подключен к входу первогорегистра сдвига, другой выход которого соединен с первым входом третьего элемента И, второй вход и выходкоторого соединены соответственнос первымвыходом триггера блокировкии с входом второго регистра сдвига,а дополнительный выход первого регистра сдвига подключен к управляющему входу четвертого коммутатора сигнальные входы которого соединены свыходами преобразователя кода, к входам которого подключены выходы вто=рого и третьего коммутаторов, приэтом выход первого элемента И соеди 35нен с входом делителя частоты и с.управляющим входом третьего регистрасдвига, к сигнальным входам которогоподключены выходы шифраторов и ре 40шающего блока, к входам которого подключены выходы шифраторов, входыкоторых соединены.с выходами четвертого коммутатора, выход третьего регистра сдвига подключен к второму45входу выходного триггера, а на приемной стороне введень 1 третий дифференцирующий блок, два элемента ИЛИ,счетчик, второй и третий элементы И,решакиций блок, четвертый регистрсдвига и преобразователь кода, входы которого соединены с одними входами второго элемента И и с выходамирешающего блока, к входам которогоподключены выходы четвертого регистра сдвига, первый вход которого соединен с первым входом счетчика,к второму входу которого подключенодин выход первого регистра сдвига и с выходом первого элемента ИЛИ,к входам которого подключены выходтретьего дифференцирующего блока,вход которого соединен с вторым выходом.входного триггера, и первый входтриггера управления, второй входкоторого соединен с одним выходомпервого регистра сдвига и с установочным входом четвертого регистрасдвига, второй вход которого соеди-нен с выходом первого элемента Ии с вторым входом первого регистрас;.лига, первый дополнительный выходкоторого подключен к другому входувторого элемента И, выход которогосоединен с первым входом второго элемента ИЛИ, и к первому входу третьего элемента И, второй вход и выходкоторого соединены соответственнос выходом счетчика и с вторым входом второго элемента ИЛИ, выход которого подключен к второму входутриггера блокировки, причем второйдополнительный выход первого регистра сдвига подключен к соответствующему входу решающего блока, выходыпреобразователя кода соединены с другими входами третьего регистра сдвига,На фиг, 1 представлена структурная электрическая схема передающейстороны предложенной системы; наФиг. 2 - то же, приемной стороны.Система передачи дискретной информации .с решающей обратной связьюсодержит (Фиг. 1) генератор 1, первыйэлемент И 2, триггер 3 управления,делитель 4 частоты, источник 5 информации, второй элемент И 6, триггер 7 блокировки, первый коммутатор 8, регистрирующий блок 9, первый 10 и второй 11 регистры сдвига,блок 12 накопителей, второй 13 итретий 14 коммутаторы, преобразователь 15 кода, третий элемент И 16,четвертый коммутатор 17, первый 18и второй 19 шифраторы, решающийблок 20, третий регистр 21 сдвига,выходной триггер 22, прямой 23 иобратный 24 каналы.На приемной стороне (фиг. 2) система содержит генератор 25, первыйэлемент И 26, входной триггер 27,первый 28 и второй 29 дифференцирующие блоки, первый элемент ИЛИ 30,триггер 31 управления, третий дифференцирующий блок 32, первый - четвертый регистры одвига 33 - 36, второй,элемент И 37, второй элемент ИЛИ 38,111127счетчик 39, третий элемент И 40, триггер 41 блокировки, решающий блок 42, преобразователь 43 кода, коммутатор 44, выходной согласующий блок 45 и потребитель информации 46.Система работает следующим образом.Источник 5 информации на передающей стороне (фиг. 1) определяет начало и конец передаваемого блока 10 данных. С момента формирования источником 5 информации сигнала "Начало" стартстопной комбинации формируется сигнал, разрешающий запуск триггера 3 управления. При этом раз- .15 решается прохождение импульсов с генератора 1 через. открытый первый элемент И 2 и.делитель 4 частоты на вход первого регистра 10 сдвига. Частота поступающих импульсов выбрана равной Г =1/ ь, (где 1, - длительность единичного элемента простого кода), Информация, вырабатываемая источником 5 информации в, последовательном виде, поступает на регистрирующий блок 9, который выполняет одновременно две функции: регистрацию элементов кодовой комбинации: и преобразование последовательного кода в параллельный. Преобразование осуществляется с помощью импульсов, вырабатываемых распределителем передачи - первым регистром 10 сдвига.Сообщение в виде стартстопных комбинаций от источника 5 информации поступает на входы П ячеек регистрирующего блока 9, выполняющего еще и функцию накопителя. За время цикла работы первого регистра 10 сдвига на п-х его выходах формируются импульсы регистрации, соответствующие сред 40 ней части принимаемых от источника 5 информации единичных элементов, которые через открытый первый коммутатор 8 поступают на другие входы ячеек регистрирующего блока 9, где и производится регистрация и запоминание элементов исходного простого пятиэлементного кода МТК, После момента приема последнего элемента кода очередным тактовым импульсом с соответствующего выхода первого регистра 10 сдвига через открытый второй элемент И 6 информация переписывается из регистрирующего блока 9 в блок 12. На передающей стороне выбраны три регистра сдвига 10, 11 и 21, первый из которых служит для регистрации и накопления элементов 58 8 .кодовой комбинации, а два других - для хранения кодовых комбинаций, подлежащих повторной передаче при обнаружении ошибок на приемной стороне и переспросе по обратному каналу 24.При отсутствии сигнала "Запрос", формирующегося на приемной стороне для повторения ошибочно принятых комбинаций, триггер блокировки 7 находится в нулевом исходном состоянии, при этом разрешается работа второго элемента И 6 и запрещается работа третьего элемента И 16. Работой бло- . ка 12 накопителей управляет второй регистр 11 сдвига, поочередно подключая выходы. соответствующего накопителя кодовой комбинации через второй 13 и третий 14 коммутаторы на вход преобразователя 15 кода. При условии отсутствия сигнала "Запрос" по обратному каналу 24 второй регистр 11 сдвига разрешает работу первого 8 и второго 13 коммутаторов и запрещает работу третьего коммутатора 14,При запросе приемной стороны по обратному каналу 24 триггер 7 блокировки переводится в единичное состояние и происходит запрет работы первого 8 и второго 13 коммутаторов и разрешение работы третьего коммутатора 14. Управление работой второго регистра 11 сдвига осуществляется импульсами, соответствующими окончанию стартстопного цикла, вырабатываемыми первым регистром сдвига 10, которые поступают через открытый третий элемент И 16, что. соответствует повторной передаче информации по прямому каналу 23.При поступлении очередной кодовой комбинации простого пятиэлементного кода в конце стартстопного цикла информация с блока 12 накопителей в параллельном виде через соответствующие второй 13 и третий 14 коммутаторы проключается на вход преобразователя 15 кода, Каждой кодовой комбинации исходного простого пяти- элементного кода присваивают свой номер. С помощью преобразователя 15 кода происходит дешифрация накопленной комбинации в блоке 12 накопителей в одну из 33 возможных (преобразователь из пяти в тридцать две) .Проключение выходов преобразователя 15 кода по входам первого 18 и второго 19 шифраторов производится импульсом считывания, снимаемым с9 . 111выхода первого регистра 10 сдвига.При наличии на одном из выходов преобразователя 15 кода сигнала информациячерез четвертый коммутатор 17 поступает в параллельном виде в первый 18и второй 19 шифраторы.С помощью первого 18 и второго 19шифраторов производится преобразование в двухпозиционный 1,код, гдеместоположение 11 перехода определяет передаваемый кодовый символ,Для обнаружения ошибок в каналевводится третий К-й переход, которыйвычисляется в решакщем блоке 20 последующему алгоритму=1 А 1+А 1) по тоА Аее, 11),1где коеЯнцненты А, АА, А определяются параметрами ошибок в канале связи и требуемой верностьюпередачи.Номер, соответствующий 1-смене полярности, полученный в результате вычисления по (1) в решающем блоке 20,определяет номер ячейки третьегорегистра 21 сдвига, в которую следуетзаписать единицу.lФормирование местоположения нереходов , 3 р К можно пРоизводить также с помощью соответствующей кодовойтаблицы н шифраторов. Информацияо номере комбинации источникаинформации 5, подлежащей передаче,закладывается в комбинации местоположения трех информационных переходов (хр р Е) на интервале временистартстопного цикла Т 11.С выхода первого элемента И 2 тактовые импульсы с частотой следованияРе =1/д, где а - единичный элемент,используемый при формировании сигналов в кодовых словах, число возможных кодовых слов при этом составляет2 1) , но выбираются только те, которые удовлетворяют условию (1),поступают на управляющий вход С третьего регистра 21 сдвига, и информа"ция в виде переходов последовательносчитывается с его выхода на входвыходного триггера 22. С помощьюимпульса, снимаемого с выхода первого регистра 10 сдвига, соответствующего началу стартстопного цикла, иимпульсов с выхода третьего регистрасдвига 21 непрерывно формируются ипередаются в прямой канал трехэлементные многопозиционные кодовыекомбинации. Длительность элемента,соответствующего пусковому элементустартстопной комбинации определяется 1258 10расстоянием от сигнала "Конец-начало"стартстопного цикла до момента появления ч -го перехода с выхода третьего регистра 21 сдвига. РасстояниемеждУи 3 р 1 и Е пеРеходами, Е-мпереходом и сигналом "Конец-начало"цикла выбрано не менее Следовательно, в прямой канал 23непрерывно поступают сформированныестартстопные кодовые комбинации спостоянным числом перех.)дов ХММ -(характеристических моментов модуляции), Из общего числа возможных реализаций отбираются только сигналы,в которых число переходов равно четырем, местоположение переходов удовлетворяет условию (1), и расстояние между р,1, 1 переходами не меньше чем А,на интервале стартстопного цикла исходного кода. С выхода выходноготриггера 22 сигнал поступает впрямой канал 23.Информация с прямого канала 23связи поступает на входной триггер 27,25 где осуществляется временная привязка фронтов принимаемых единичныхэлементов к генератору 25. С помощьюпервого 28 и третьего 32 дифференцирующих блоков производится выделение Фронтов принимаемого сигнала"старт" и переходы из ноля в единицу) . Стартовый переход, пройдя первый дифференцирующий блок 28, уста 35навливает триггер 31 управления вединичное состояние, тем самым разрешая прохождение тактовых импульсовс генератора 25 на входы с первогорегистра 33 сдвига. Цикл работы пер 4 ного регистра 33 сдвига выбран равным Т =Н ь р где Ю - количество ячеЦ,ек первого регистра 33 сдвига, равноечислу возможного местоположенияхарактеристических моментов восста 45,новления (ХИВ) в принимаемой кодовойкомбинации, а ь - длительность единичного элемента преобразованногокода. С помощью второго дифференцирующего блока 29 выделяется переход,записывающий единицу в первую ячейку первого регистра сдвига 33 по1.)-входу.Под действием управляющих импульсов по входу С первого регистра 33сдвига на его выходах поочереднопоявляются импульсы, управляющиеприемной стороной системы в целом.Выходы первого 28 и третьего 32дифференцирующих блоков объединены11 111125 первым элементом ИЛИ 30, с выхода которого стартовый и 1, 1, К информационные переходы принимаемой кодовой комбинации записываются по входу 0 четвертого регистра 36 сдвига. Одновременно с работой первого регистра 33 сдвига начинает работу и четвертый регистр Зб сдвига от импульсов, поступающих по С-входу. Четвертый регистр 36 сдвига выраба О тывает зоны величиной Ь с таким расчетом, чтобы принимаемые , 1 и 1 переходы находились в середине зон анализа й . Номера зон 6, в которых принимаются 1,. 1 и к переходы, запо минаются в ячейках четвертого регистра Зб.сдвига, который является накопителем. Параллельно номера этих зон (ячеек) поступают на решающий блок 42, в котором проверяется условие (1). 20 При невыполнении этого условия фор мируется сигнал запроса (сигнал "Ошибка"), т.е. решающий блок 42 преобразует номера , 1, Е ячеек четвертого регистра 36 сдвига в номер кодовой 25 комбинации простого пятиэлементного кода. На выходе решающего блока 42 появляется сигнал, соответствующий номеру кодовой комбинации кода МТК, вырабатываемой источником 5 информа- З 0 ции. Проключение входов и выходов решающего блока 42 производится импульсом считывания, снимаемым с первого регистра сдвига 33 с выхода Г после записи в четвертый регистр 3635 последнего К-момента смены полярности в принимаемой кодовой комбинации преобразованного кода.Выходы преобразователя кода 43 подключены к 8-входам ячеек третьего ре 40 гистра сдвига 35. Преобразование производится в очередном стартстопном цикле с помощью пяти управляющих импульсов, вырабатываемых первым регистром 33 сдвига с выходов и, кото 45 рые соответствуют моментам смен полярностей единичных элементов в комбинации пятиэлементного кода, выдаваемого потребителю информации 46, через выходной согласующий бЛок 45, Импульсы поступают по С-входам третьего50 регистра 35 сдвига через коммутатор 44 при отсутствии сигнала блокировки, снимаемого с выхода второго регистра 34 сдвига. С выхода последней ячейки третьего регистра 35 сдвига информа.ция в виде единичных переходов, соответствующих ХМВ простого кода МТК, поступает на вход выходного согласую 8 12щего блока 45, с помощью которогоформируется стартстопная кодоваякомбинация, выдаваемая потребителю 41информации,В конце стартстопного цикла первыйрегистр сдвига 33 вырабатывает импульс по выходу е, сбрасывающийтриггер 31 и первый 33 и четвертый 36регистры сдвига в исходное состояние.Если же во время считывания информации ни на одном из выходов решающего блока 42 не появляется сигнал,что соответствует приему неразрешенной комбинации (которая не соответствует кодовой таблице на передаче),то импульс с выхода Ь первого регистра сдвига 33, пройдя второй элемент И 37 и второй элемент ИЛИ 38,устанавливает триггер 41 блокировкив единичное состояние. Триггер 41 блокировки формирует сигнал запросадля передающей стороны по обратномуканалу 24. Выход триггера 41 блокировки также подключен к входу второго регистра сдвига 34, формирующегосигнал блокировки по входу коммута"тора 44. При этом на время повторениякодовых комбинаций по прямому каналу 23 запрещается считывание информации потребителю 46 информации.Установка триггера 41 блокировкив исходное состояние производится импульсом, соответствующим, концу приема стартстопной кодовой комбинации,Так как на передающей стороне формируются комбинации с постояннымчислом (равно четырем) ХММ, то наприемной стороне производится анализколичества ХМВ в пределах стартстопного цикла Тч,. Для этого служитсчетчик 39, емкость которого равначетырем и на вход которого поступаютфронты единичных элементов, формируемые первым 28 и третьим 32 дифференцирующими блоками. В конце стартстопного цикла счетчик 39 устанавливаетсяв исходное состояние. Если же за время приема стартстопного цикла количества ХМВ отличается от четырех, тоимпульс, снимаемый с выхода Ь первогорегистра сдвига 38, пройдя третий элемент И 40 и второй элемент ИЛИ 38,также устанавливает триггер 41 блокировки в единичное состояние, чтосоответствует формированию сигналазапроса и блокировки приемной сторонысистемы.Известно, что эффективная скоростьпередачи К в системах передачи дискретной информации с обратной связью (по прототипу, использующих для обнаружения ошибок избыточные коды, определяется избыточностью применяемого кодаи потерями на переспросыу1 с 1Кж, и жщвт тв тщета (2)фо" и И Р .Раью.которые, в свою очередь, определяются вероятностью ошибочного приема кодового слова Рш,ц .При использовании предложенной системы эффективная скорость передачи определяется только лишь потерями В выражении (2) К - число информационных, а и - общее число элементов кодового слона избыточного кода, И - число повторяемых кодовых слов при перепросе. Для уменьшения потерь достовернос-, ти и снижения потерь пропускной способности канала в предложенной системе вводится трехэлементный многопозиционный бинарный код.При этом на передающей стороне формируются кодовые слова с постоянным числом. ХМИ, равным четырем (одного стартового и трех ,1,К информационнькпереходов), При приеме кодового слова проверяется условие (1) и условие постоянства числа ХИВ в кодовой комбинации, что позволяет обнаФруживать ошибки любой кратности либоисправлять однократные ошибки.Под однократной ошибкой в данномслучае следует понимать смещениев результате искажений любого одногоиз , 1, Е переходов на величину,кратную д.Так как в.предложенной системеК=ф,то даже при вероятности ошибочного приема на знак 10(т.е. накаждые 100 переданных знаков одинпринимается с ошибкой) эффективнаяскорость передачи К=983 при И=2.Если учесть, что при уменьшении 15длительности кодового сигнала дчисло временных позиций на интервалевремени То простого кодового словаувеличивается, то объем кодового 20словаря И можно передать за времяН ТцЯ Ч . Коэффициент использованиявремени для передачи одного кодовогослова представляет собой отношениеТ Оь"-;-, при этом пропускная способ 2 э Т,Тность определяется выражением - уТ. Юи может быть Ъ 1, что соответствуетприросту объема передаваемой информации.ЗО Таким образом, применение предложенной системы позволяет повыситьэффективность использования каналовсвгзи, а следовательно, и помехоустойчивость передачи.1111258 Тираж 634 ИПИ Государственного по делам изобретен Москва, Ж, Раушскаказ 6327В ое 13035,Патент", г од, ул.Проектная,лиал едактор Л,Веселовск Составитель А,МоскевичТехред Ж,Кастелевич Корректор В.Гирня Подл омитета СССР й и открытий я наб., д. 4/

СмотретьЗаявка

3610276, 22.06.1983

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

ЗАХАРЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КИРЕЕВ ИГОРЬ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04L 1/12

Метки: дискретной, информации, обратной, передачи, решающей, связью

Опубликовано: 30.08.1984

Код ссылки

<a href="https://patents.su/9-1111258-sistema-peredachi-diskretnojj-informacii-s-reshayushhejj-obratnojj-svyazyu.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи дискретной информации с решающей обратной связью</a>

Предыдущий патент: Устройство асинхронного сопряжения цифровых сигналов

Следующий патент: Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов

Случайный патент: Привод ленточного конвейера