Устройство управления сортировкой лесоматериалов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1068894

Автор: Киляков

Текст

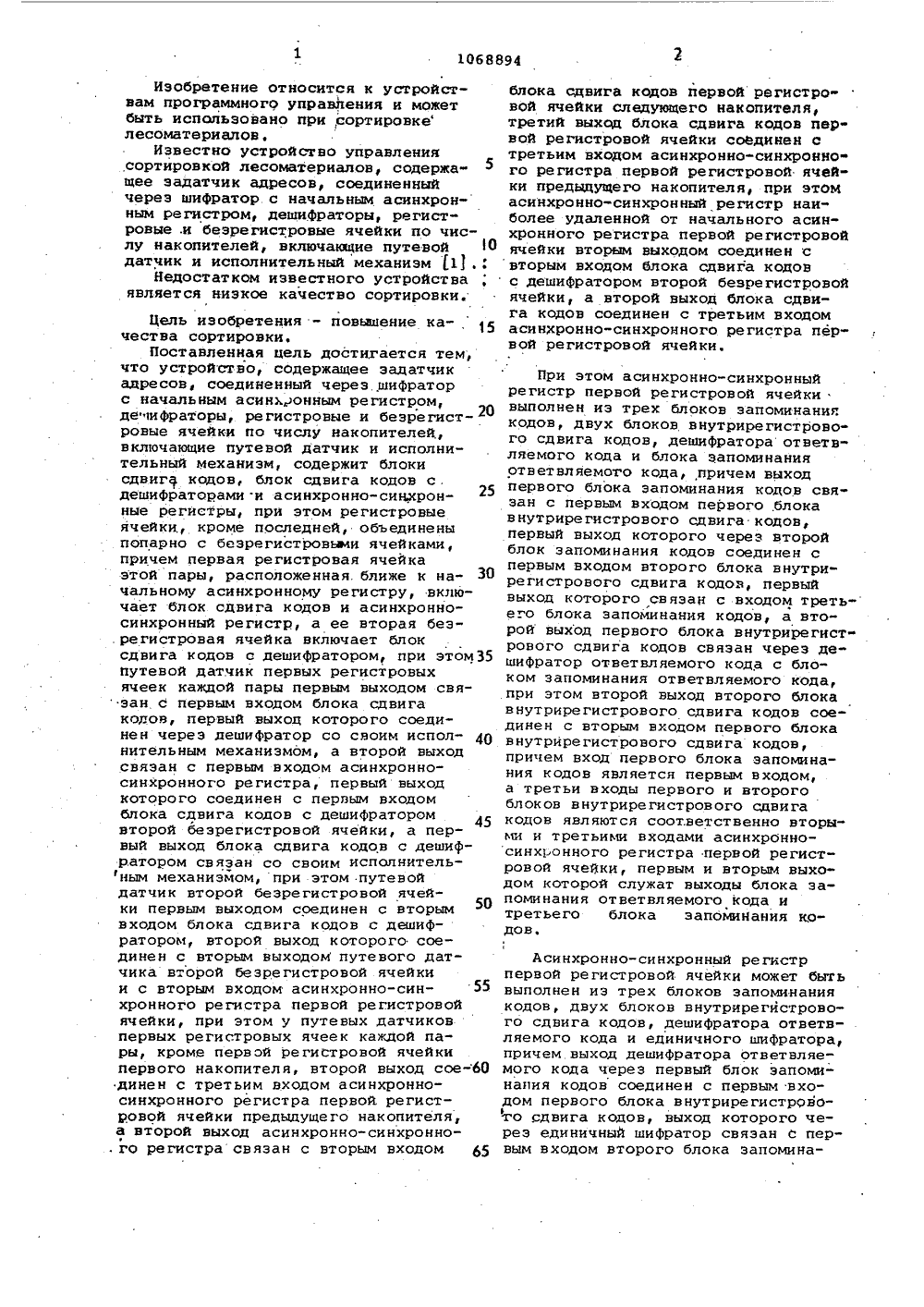

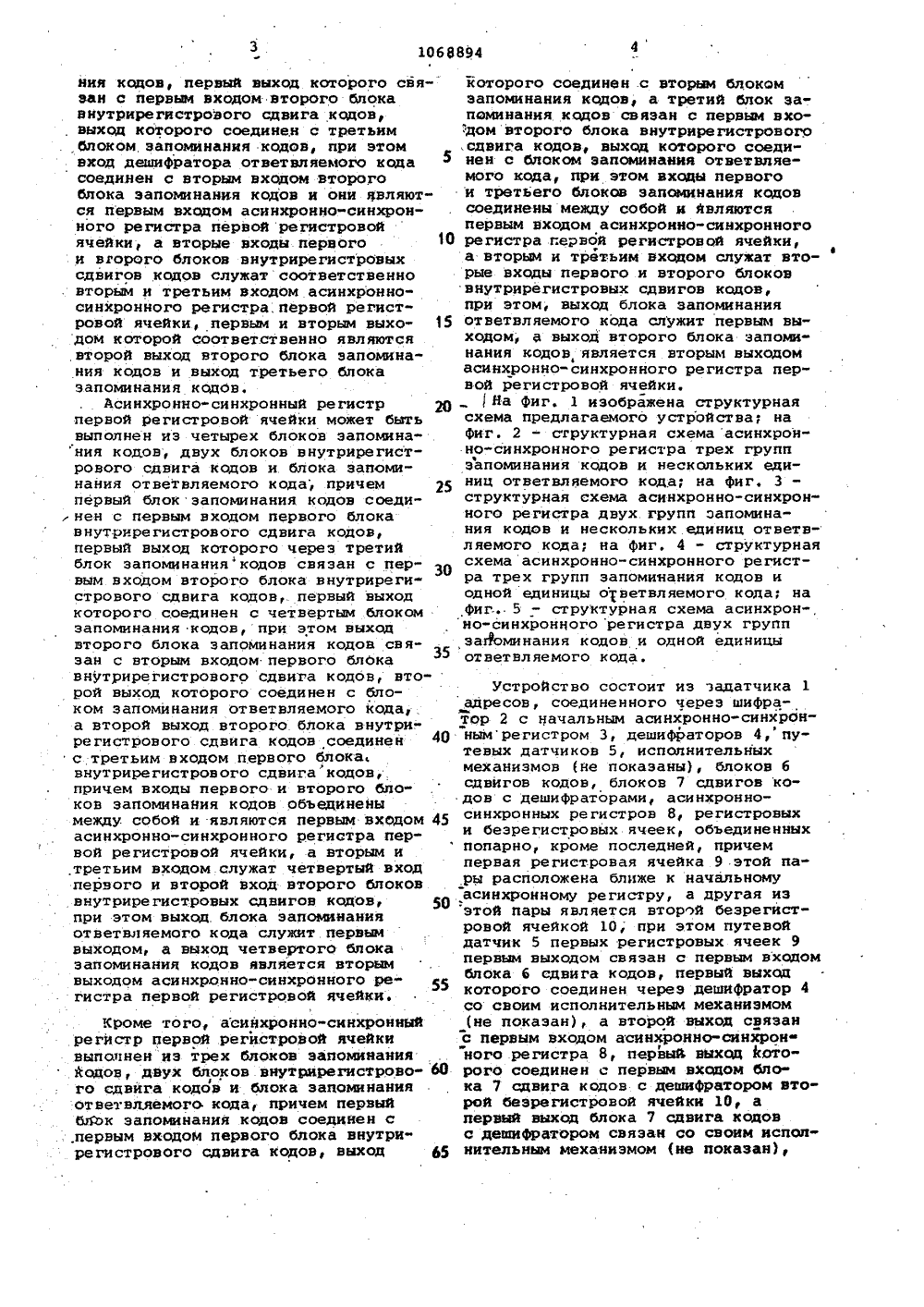

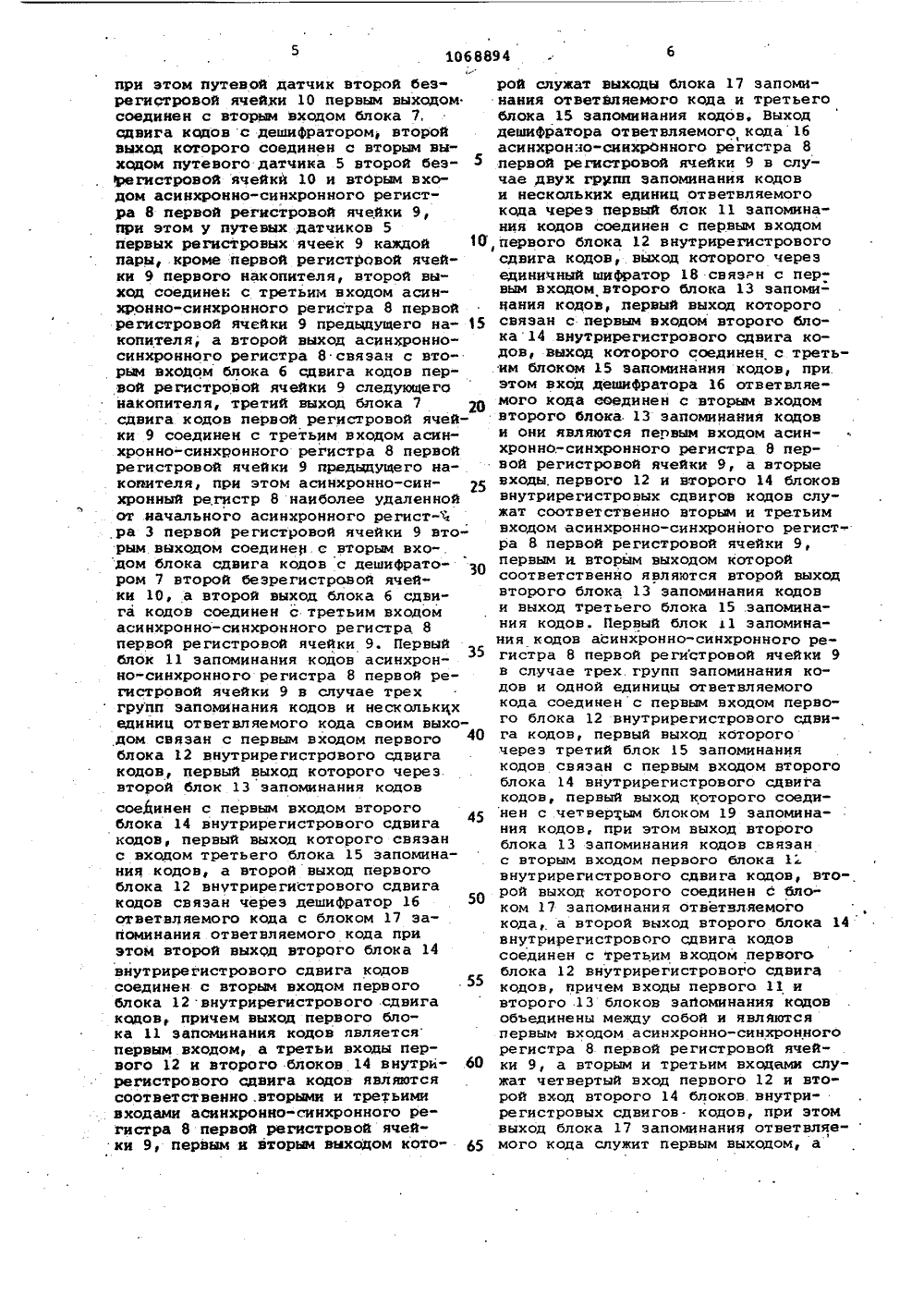

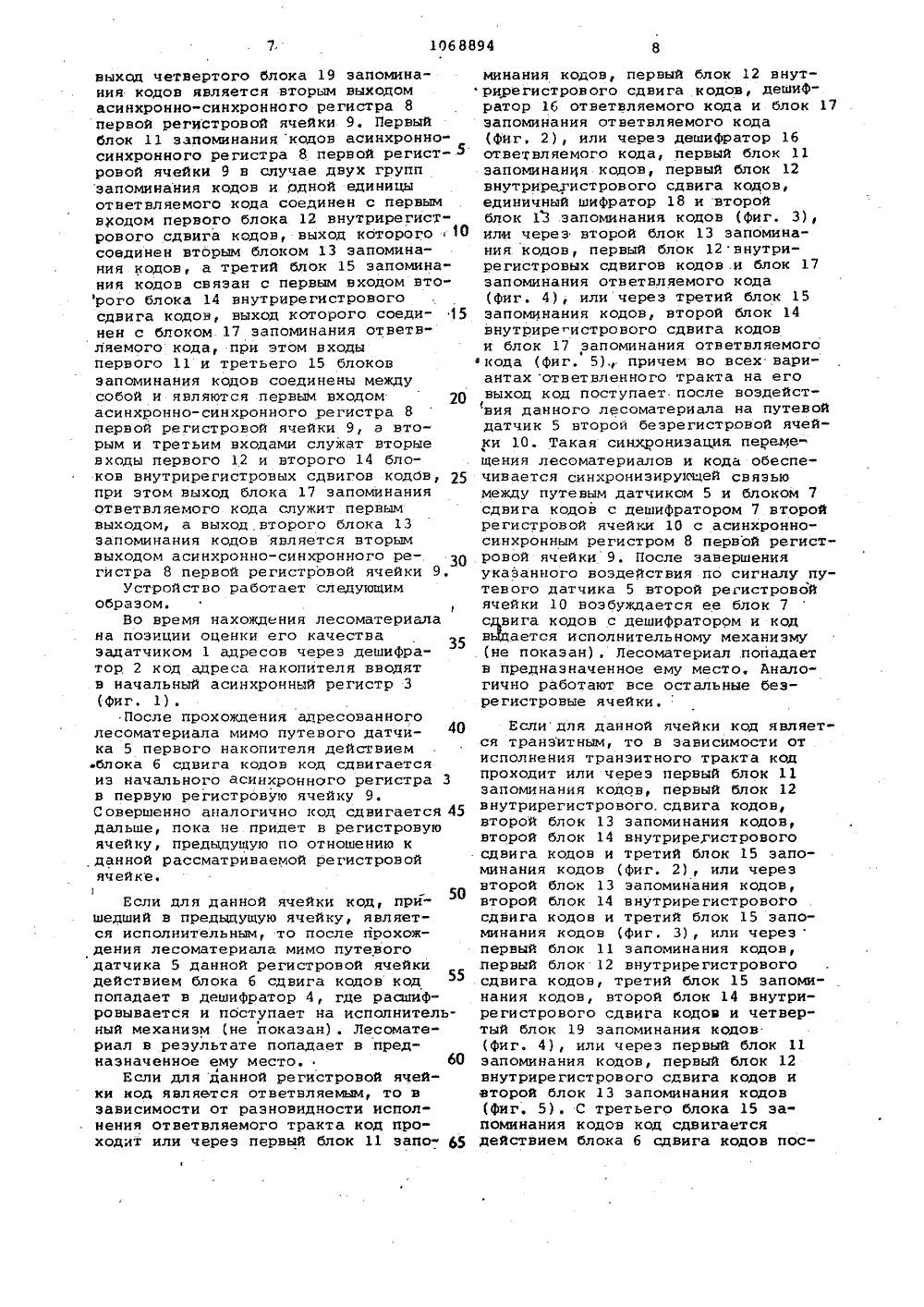

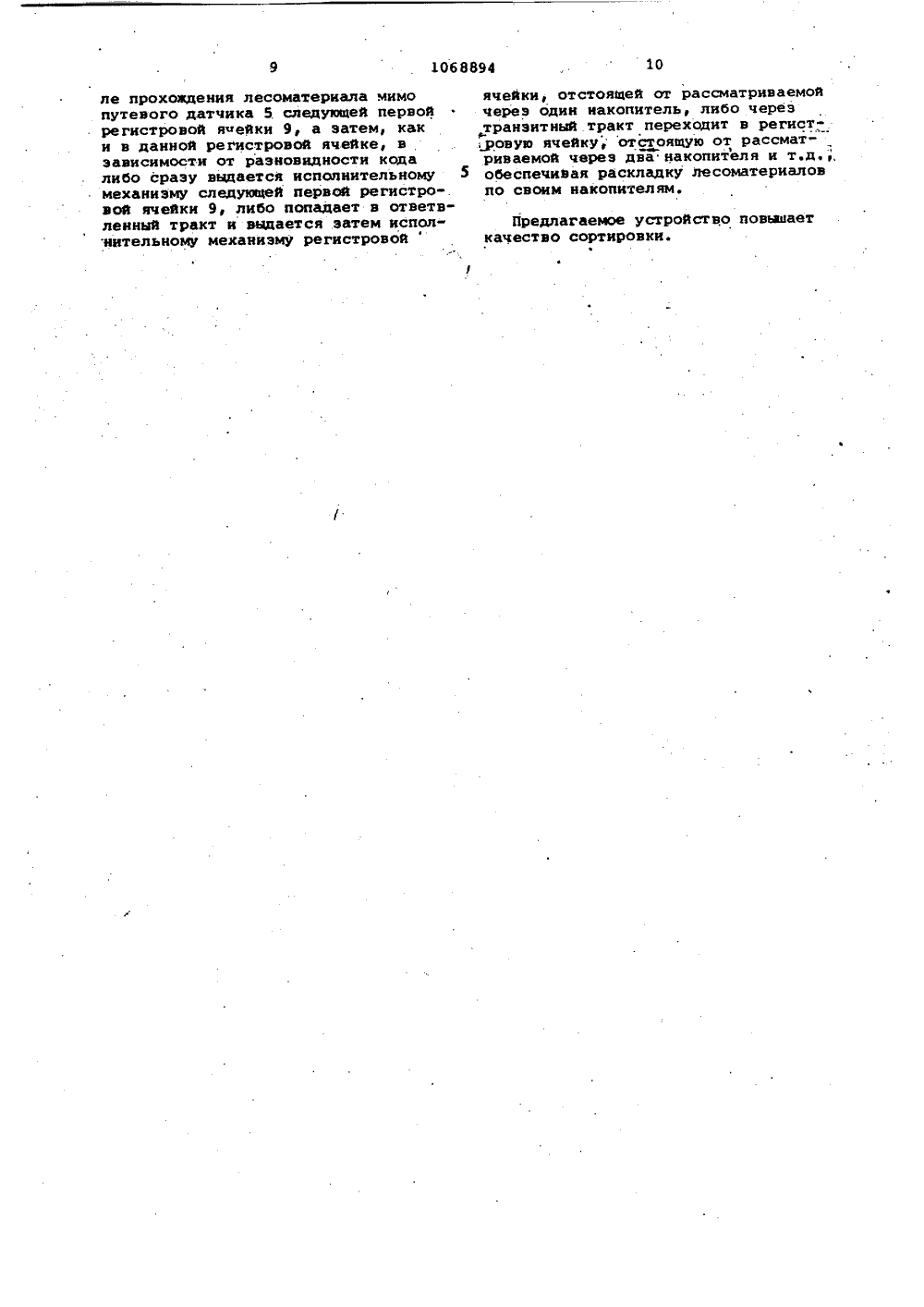

(71 ски (53 ьтро- .оков Ф зачем оСОЮЗ СОВЕТСКИХИЧЕСКИХРЕ ЛИК ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО Е 3 ПЗ з 4(56) 1. Запольский Б.А. и Серов Б .В. Цифровая вычислительная техника для автоматизации лесозаготовительных предприятий, М., фЛесная промшленность, 1966, с. 120, рис, 47.(54 ) (57) 1, УСТРОЙСТВО УПРАВЛЕНИЯСОРТИРОВКОЙ ЛЕСОМАТЕРИАЛОВ, содержа-щее задатчик адресов, соединенный.через шифратор с начальным асинхронным регистром, дешифраторы, регистровые и. безрегистровые ячейки по числу накопителей, включающие путевойдатчик и исполнительный механизм,о т л и ч а ю щ е е с я тем, что, сцелью повьавения качества сортировки,оио содержит блоки сдвига кодов,блок сдвига кодов с дешифраторамии асинхронно-синхронные регистры,при этом регистровые ячейки, кромепоследней, объединены попарно сбеэрегистрс вьми ячейками, причем первая регистровая ячейка этой пары,расположенная ближе к начальномуасинхронному регистру, включает блоксдвига кодов и асинх 1 шнно-синхрон-,ный регистр, а ее вторая без 15 егист- .ровая ячейка включает блок сдвигакодов с дешифратором, при этом путевой датчик первых регистровых ячееккаждой пары первым выходом связанс первым входом блока сдвига кодов,первый выход которого соединен черездешифратор со своим исполнительныммеханиэмом, а второй выход связанс первым входом асинхронно-аинхроиного регистра, первый выхсщ которого соединен с первым входом блокасдвига кодов с дешифратором второйбеэрегистровой ячейки, а первый 369 Ф 05 В 19 181 В 07 С 5/14 выход блока сдвига кодов с дешнфратором связан со своим исполнительным механизмом, при этом путевойдатчик второй безрегистровой ячейкипервым выходом соединен с вторымвходом- блока сдвига кодов с дешифратором, второй выход которого соединен с вторым выходом путевого датчи"ка второй безрегистровой ячейки нвторым входом асинхронно-синхронного регистра первой регистровой ячей"ки, при этом у путевых датчиковпервых регистровых ячеек каждой пары, кроме первой регистровой ячейкипервого накопителя, второй выхсдсоединен с третьим входом асинхронно-синХронного регистра первой регистровой ячейки предыдущего накопителя, а второй выход асинхронно-син.хронного регистра связан с вторымвходом блока сдвига кодов первойрегистровой ячейки следующего накотеля, третий выход блока сдвига ф дов первой регистровой ячейки соенен с третьим входом асинхронно- синхронного. регистра первой регнстро. вой ячейки предыдущего,накопителя, при этом асинхронно"синхронный регистр наиболее удаленной от начал ного асинхронного регистра первой регистровой ячейки вторым выходом соединен"с вторым входом блока сдвига кодов с дешифратором второй ре-. .гистровой ячейки, а второй выход бло ка сдвига кодов соединен с третьим входом асинхронно-синхронного регист ра первой регистровой ячейки,2. Устройство по и, 1, о т л ич а ю щ е е с я тем, что.асинхронно- синхронный регистр первой регнс вой ячейки выполнен иэ трех бло запоминания кодов, двух блоков внутрирегистрового сдвига кодов, деширатора ответвляемого кода н блокапоминания ответвляемого кода, прн выход первого блока запоминания кдов связан с первым входом первогоблока внутрирегистрового сдвига. кодов, первый выход которого через второй блок запоминания кодов соединенс первым входом второго блока внутрирегистрового сдвига кодов, первыйвыход которого связан с входом третьего блока запоминания кодов, а второй выход первого блока внутрирегист.рового сдвига кодов связан черездешифратор ответвляемого кода с блоком запоминания ответвляемого кода,при этом второй выход второго блокавнутрирегистрового сдвига кодов сое"динен с вторым входом первого блока. внутрирегистрового сдвига кодов,причем вход первого блока запоминания кодов является первым входом, а .третьи входы первого и второго блоков внутрирегистрового сдвига кодовявляются соответственно вторыми итретьими входами асинхронно-синхронного регистра первой регистровойячейки, первым и вторым выходом которой служат выходы блока запоминанияответвляемого кода и третьего блоказапоминания кодов.3. Устройство по и, 1, о т л ич а ю щ е е с я тем, что асинхронносинхронный регистр первой регистровой ячейки выполнен иэ трех блоковзапоминания кодов, двух блоков внут". рирегистрового сдвига кодов, дешифратора ответвляемого кода и единичного шифратора, причем выход дешифратора ответвляемого кода через первый блок запоминания кодов соединенс первым входом первого блока внутрирегистрового сдвига кодов, выход которогочерез единичный шифратор свя"эан с первым входом второго блока запоминания кодов, первый выход которо. го связан с первым входом второго блока внутрирегистрового сдвига кодов,выход которого соединен с третьимблоком запоминания кодов, при этомвход дешифратора ответвляемого кодасоединен с вторым входом второгоблока запоминания кодов и они являются первым входом асинхронносинхронного регистра первой регистровой ячейки, а вторые входы первого и второго блоков внутрирегистровых сдвигов кодов служат соответст"венно вторым и третьим входом асинхронно-синхронного регистра первойрегистровой ячейки, первым и вторымвыходом которой соответственно яв" .ляются второй выход второго блоказапоминания кодов,и выход третьегоблока запоминания кодов,4. Устройство по п. 1, о т л ич а ю щ е е с,я тем, что асинхронносинхронный регистр первой регистровой ячейки выполнен из четырех блоко запоминания кодов,. двух блоков внутрирегистрового сдвига кодов . и блока запоминания ответвляемого кода, причем первый блок запоминания кодов соединен с первым входом первого блока внутрирегистрового сдвига кодов, первый выход которого че"реэ третий блок запоминания кодов связан с первым входом второго бло" ка внутрирегистрового сдвига кодов, первый выход которого соединен с четвертым блоком эапоиинания кодов, при этом выход второго блока запоминания кодов связан с вторым входом первого блока внутрирегистрового сдвига кодов, второй выход которого соединен с блоком запоминания ответвляемого кода, а второй выход второго блока внутрирегистрового сдвига кодов соединен с третьим входом перво"го блока внутрирегистрового сдвига.кодов, причем входы первого и второго блоков запоминания кодов .объединены между собой и являются первым входом асинхронно-синхронного регистра первой регистровой ячейки, а вто-.рым и третьим входом, служат четвертый вход первого и второй вход второго блоков внутрирегистрэвых сдвигов кодов, при этом выход блока запоминания ответвляемого кода служит первым выходом, а выход четвертого блока запоминания кодов является вторым выходом асинхронно-синхронного регистра первой регистровой ячейКие5. Устройство по п. 1, о т л и- ч а ю щ е е с я тем, что асинхронно- синхронный регистр первой регистровой ячейки выполнен иэ трех блоков запоминания кодов, двух блоков внутрирегистрового сдвига кодов и блока запоминания ответвляемого кода, причем первый блок запоминания кодовсоединен с первым входом первого блока внутрирегистрового сдвига кодов, выход которого соединен с вторым блоком запоминания кодов, а третий блок запоминания кодов связан с первым входом второго блока внутрирегистрового сдвига кодов, выход которого соединен с блоком запоминания ответвляемого кода, приэтом входы первого и третьего блоков запоминания кодов соединены между собой и являются первым входом асинхронно-синхронного регистра первой регистровой ячейки, а вторым и третьим входом служат вторые входы первого и второго блоков внутрире гистровых сдвигов кодов, при этом выход блока запоминания ответвляе-. мого кода служит первым выходом, а зыход второго блока запоминания кодов является вторым выходом асинхрон- иЬ-синхронного регистра первой регистровой ячейки.Изобретение относится к устройствам программного управления и может быть использовано при,сортировке лесоматериалов,Известно устройство управления сортировкой лесоматериалов, содержащее эадатчик адресов, соединенный через шифратор с начальным асинхронным регистром, дешифраторы, регист" ровые .и безрегистровые ячейки по числу накопителей, включающие путевой 0 датчик и исполнительный механизм 11 .:Недостатком известного устройства является низкое качество сортировки.Цель изобретения - повышение ка-, чества сортировки.Поставленная цель достигается тем, что устройство, содержащее эадатчик адресов, соединенный через шифратор с начальным асин.,бронным регистром, де"1 ифраторы, регистровые и безрегистровые ячейки по числу накопителей., включающие путевой датчик и исполнительный механизм, содержит блоки сдвига кодов, блок сдвига кодов с. дешифраторами .и асинхронно-синхронные регистры, при этом регистровые ячейки, кроме последней, объединены попарно с безрегистровьаки ячейками, причем первая регистровая ячейка этой пары, расположенная. ближе к на чальному асинхронному регистру, включает блок сдвига кодов и асинхронно- синхронный регистр, а ее вторая беэрегистровая ячейка включает блок сдвига кодов с дешифратором, при этом 35 путевой датчик первых регистровых ячеек каждой пары первым выходом связан с первым входом блока сдвига кодов, первый выход которого соединен через дешиФратор со своим испол нительным механизмом, а второй выход связан с первым входом асинхронно- синхронного регистра, первый выход которого соединен с первым входом блока сдвига кодов с дешифратором второй беэрегистровой ячейки, а первый выход блока сдвига кодов с дешифратором связан со своим исполнительным механизмом,при этом путевой датчик второй безрегистровой ячейки первым выходом соединен с вторым входом блока сдвига кодов с дешифратором, второй выход которого соединен с вторым выходом путевого датчика второй беэрегистровой ячейки и с вторым входом асинхронно-син хронного регистра первой регистровой ячейки, при этом у путевых датчиков первых регистровых ячеек каждой пары, кроме первой регистровой ячейки первого накопителя, второй выход соединен с третьим входом асинхронно- синхронного регистра первой регистровой ячейки предыдущего накопителя, а второй выход асинхронно-синхронно. Го регистра связан с втоРым входом 65 блока сдвига кодов первой регистровой ячейки следующего накопителя, третий выход блока сдвига кодов первой регистровой ячейки соединен с третьим входом асинхронно-синхронного регистра первой регистровой ячейки предыдущего накопителя, при этом асинхронно-синхронный регистр наиболее удаленной от начального асинхронного регистра первой регистровой ячейки вторым выходом соединен с вторым входом блока сдвига кодов с дешифратором второй безрегистровой ячейки, а второй выход блока сдвига кодов соединен с третьим входом асинхронно-синхронного регистра первой регистровой ячейки.При этом асинхронно-синхронный регистр первой регистровой ячейки выполнен из трех блоков запоминания кодов, двух блоков внутрирегистрового сдвига кодов, дешифратора ответвляемого кода и блока запоминания ответвляемого кода, причем выход первого блока запоминания кодов связан с первым входом первого, блока внутрирегнстрового сдвига кодов, первый выход которого через второй блок запоминания кодов соединен с первым входом второго блока внутри- регистрового сдвига кодов, первый выход которого связан с входом третьего блока запоминания кодов, а второй выход первого блока внутрирегист" рового сдвига кодов связан через дешифратор ответвляемого кода с блоком запоминания ответвляемого кода, при этом второй выход второго блока внутрирегистрового сдвига кодов соединен с вторым входом первого блока внутрирегистрового сдвига кодов, причем вход первого блока запоминания кодов является первым входом, а третьи входы первого и второго блоков внутрирегистрового сдвига кодов являются соответственно вторымн и третьими входами асинхронно- синхронного регистра первой регистровой ячейки, первым и вторым выхо дом которой служат выходы блока запоминания ответвляемого кода и третьего блока запомииания КО- дов. Асинхронно-синхронный регистр первой регистровой ячейки может быть выполнен иэ трех блоков запоминания кодов, двух блоков внутрирегистрового сдвига кодов, дешифратора ответвляемого кода и единичного шифратора, причем выход дешифратора ответвляемого кода через первый блок запоминания кодов соединен с первым входом первого блока внутрирегистррвого сдвига кодов, выход которого через единичный шифратор связан С первым входом второго блока запомина 1068894ния кодов, первый выход которого свя зан с первым входом второго блока внутрирегистрового сдвига кодов, выход которого соединен с третьим блоком запоминания кодов, при этом вход дешифратора ответвляемого иода соединен с вторым входом второго блока запоминания кодов и они являют ся первым входом асинхронно-синхронного регистра первой регистровой ячейки, а вторые входы первого и вгорого блоков внутрирегистровых сдвигов кодов служат соответственно вторым и третьим входом асинхронно- синхронного регистра. первой регистровой ячейки, первым и вторым выходом которой соответственно являются ,второй выход второго блока запоминания кодов и выход третьего блока запоминания кодов.Асинхронно-синхронный регистр первой регистровой ячейки может быть выполнен из четырех блоков эапомина" ния кодов, двух блоков внутрирегистрового сдвига ксдов и блока запоминания ответвляемого кода; причем первый блок запоминания кодов соеди-нен с первым входом первого блока внутрнрегистрового сдвига кодов, первый выход которого через третий блок запоминаниякодов связан с первым входом второго блока внутриреги стрового сдвига кодов, первый выход которого соединен с четвертым блоком запоминания кодов,при этом выход второго блока запоминания кодов связан с вторым входом первого блока внутрирегистрового сдвига кодов, вто рой выход которого соединен с блоком запоминания ответвляемого кода, а второй выход второго блока внутри- регистрового сдвига кодов соединен с третьим входом первого блока, внутрирегистрового сдвига кодов, причем входы первого и второго блоков запоминания кодов объединены между собой и являются первым входом асинхронно-синхронного регистра первой регистровой ячейки, а вторым и .третьим входом служат четвертый вход первого и второй вход второго блоков внутрирегистровых сдвигов кодов, при этом выход. блока запоминания ответвляемого кода служит первым выходом, а выход четвертого блока запоминания кодов является вторым выходом асинхронно-синхронного ре" гистра первой регистровой ячейки.Кроме того, ааинхронно"синхронный регистр первой регистровой ячейки выполнен иэ трех блоков запоминания одов, двух блоков внутрирегистрового сдвига кодов и блока запоминания ответвляемого кода, причем первый байк запоминания коцов соединен с .первым входом первого блока внутри- регистрового сдвига кодов, выход которого соединен с вторым блокомзапоминания кодов, а третий блох запоминания кодов связан с первым входом второго блока внутрирегистрового,сдвига кодов, выход которого соеди иен с блоком запоминания ответвляемого хода, при этом входы первогои третьего блоков запоминания кодовсоединены между собой и являютсяпервым входом асинхронно-синхронного О регистра гервой регистровой ячейки,а вторым и третьим входом служат вторые входы первого и второго блоковвнутрирегистровых сдвигов кодов,при этом, выход блока запоминания 15 ответвляемого кода служит первым выходом, а выход второго блока запоми"нания кодов является вторым выходомасинхронно-синхронного регистра первой регистровой ячейки.На Фиг. 1 изображена структурнаясхема предлагаемого устройства 1 наФиг. 2 - структурная схема асинхронно-синхронного регистра трех группзапоминания кодов и нескольких единиц ответвляемого кода; на Фнг, 3 структурная схема асинхронно-синхронного регистра двух групп запоминания кодов и нескольких единиц ответвляемого кода; на Фиг. 4 - структурнаясхема асинхронно-синхронного регистра трех групп запоминания кодов иодной единицы ответвляемого кода; наФиг 5 - структурная схема асинхронно-синхронного регистра двух группзапоминания кодов и одной единицы З 5 ответвляемого кода. Устройство состоит иэ задатчика 1адресов, соединенного через шиФратор 2 с начальным асинхронно-синхрон нымрегистром 3, дешифраторов 4, путевых датчиков 5, исполнительныхмеханизмов (не показаны), блоков 6сдвигов кодов, блоков 7 сдвигов кодов с дешифраторами, асинхронносинхронных регистров 8, регистровыхи безрегистровых ячеек, объединенныхпопарно, кроме последней, причемпервая регистровая ячейка 9 этой пары расположена ближе к начальномуасинхронному регистру, а другая изэтой пары является вторй безрегистровой ячейкой 10; прн этом путевойдатчик 5 первых регистровых ячеек 9первым выходом связан с первым входомблока 6 сдвига кодов, первый выходкоторого соединен через дешиФратор 4со своим исполнительным механизмом(не показан), а второй выход связанс первым входом асинхронно-синхронного регистра 8, первыВ выход Йото рого соединен с первым входом блока 7 сдвига кодов с дешифратором второй безрегистровой ячейки 10, апервый выход блока 7 сдвига кодовс дещиФратором связан со своим исполу 5 нительиым механизмом (не показан),рой служат выходы блока 17 запоминания ответвляемого кода и третьего блока 15 запоминания кодов, Выход дешифратора ответвляемого кода 16 асинхронно-синхронного регистра 8 первой регистровой ячейки 9 в случае двух групп запоминания кодов и нескольких единиц ответвляемого кода через первый блок 11 запоминания кодов соединен с первым входом ,первого блока 12 внутрирегистрового 510688 при этом путевой датчик второй безрегистровой ячейки 10 первым выходом соединен с вторым входом блока 7, сдвига кодов с дешифратором, второй выход которого соединен с вторым выходом путевого датчика 5 второй безрегистровой ячейки 10 и вторым входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9, при этом у путевых датчиков 5 первых регистровых ячеек 9 каждой 10 пары, кроме первой регистровой ячейки 9 первого накопителя, второй выход соединен с третьим входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9 предыдущего на копителя, а второй выход асинхронно- синхронного регистра 8 связан с вторым входом блока 6 сдвига кодов первой регистровой ячейки 9 следующего накопителя, третий выход блока 7 сдвига кодов первой регистровой ячейки 9 соединен с третьим входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9 предыдущего на" коиителя, при этом асннхронно-синхронный ре,гистр 8 наиболее удаленной от начального асинхронного регист- ра 3 первой регистровой ячейки 9 вторым.выхоцом соединен е вторым вхо-. дом блока сдвига кодов с дешифрато ром 7 второй безрегистровой ячейки 10, а второй выход блока 6 сдвига кодов соединен с третьим входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9. Первый блок 11 запоминания кодов асинхронно-синхронного регистра 8 первой регистровой ячейки 9 в случае трех групп запоминания кодов и нескольких единиц ответвляемого кода своим выходом связан с первым входом первого 40 блока 12 внутрирегистрового сдвига кодов, первый выход которого через. второй блок 13 запоминания кодов соединен с первым входом второго блока 14 внутрирегистрового сдвига кодов, первый выход которого связан с входом третьего блока 15 запоминания кодов, а второй выход первого блока 12 внутрирегистрового сдвига кодов связан через дешиФратор 16 50 ответвляемого кода с блоком 17 запоминания ответвляемого кода при этом второй выхОд второго блока 14 внутрирегистрового сдвига кодов соединен с вторым входом первого блока 12 внутрирегистрового сдвига кодов, причем выход первого блока 11 запоминания кодов является первым входом, а третьи входы первого 12 и второго блоков 14 внутри регистрового сдвига кодов являются соответственно .вторыми и третьими входами асинхронно-сиихронного регистра 8 первой регистровой ячейки 9, первым и вторым выходом кото сдвига кодов, выход которого черезединичный шифратор 18 связали с первым входом второго блока 13 запоминания кодов, первый выход которогосвязан с первым входом второго блока 14 виутрирегистрового сдвига кодов, выход которого соединен с ретьим блоком 15 запоминания кодов, прн. этом вход дешифратора 16 ответвляемого кода соединен с вторым входом второго блока. 13 запоминания кодови они являются первым входом асинхронно.-синхронного регистра 8 первой регистровой ячейки 9, а вторыевходы, первого 12 и второго 14 блоковвнутрирегистровых сдвигов кодов служат соответственно вторым и третьимвходом асинхронно-синхронного регистра 8 первой регистровой ячейки 9,первым и вторым выходом которойсоответственно являются второй выходвторого блока 13 запоминания кодови выход третьего блока 15 .запоминания кодов. Первый блок 1 эапомина" ния кодов асинхронно-синхронного регистра 8 первой регистровой ячейки 9в случае трех. групп запоминания кодов и одной единицы ответвляемогокода соединен с первым входом первого блока 12 внутрирегистрового сдвига кодов, первый выход которогочерез третий блок 15 запоминаниякодов связан с первым входом второгоблока 14 внутрирегистрового сдвигакодов, первый выход которого соединен с четвертым блоком 19 запоминания кодов, при этом выход второгоблока 13 запоминания кодов связанс вторым входом первого блока 1.внутрирегистрового сдвига кодов, второй выход которого соединен с бло"ком 17 запоминания ответвляемогокода, а второй выход второго блока 14внутрирегистрового сдвига кодовсоединен с третьим входом первогоблока 12 внутрнрегнстровоГо сдвигакодов, иричем входы первого 11 ивторого .13 блоков запоминания кодовобъединены между собой и являютсяпервым входом асинхронно-синхронногорегистра 8 первой регистровой ячейки 9, а вторым и третьим входами служат четвертый вход первого 12 и второй вход второго 14 блоков. внутрирегнстровых сдвигов. кодов, при этомвыход блока 17 запоминания ответвляе-мого кода служит первым выходом, авыход четвертого блока 19 запоминания кодов является вторым выходомасинхронно-синхронного регистра 8первой регистровой ячейки 9, Первыйблок 11 запоминания кодон асинхронно"синхронного регистра 8 первой регистроной ячейки 9 в случае двух группзапоминания кодов и одной единицыответвляемого кода соединен с первымвходом первого блока 12 внутрирегистрового сдвига кодон, выход кОторого 0соединен вторым блоком 13 запоминания кодов, а третий блок 15 запоминания кодов связан с первым входом второго блока 14 внутрирегистровогосдвига кодов, выход которого соединен с блоком 17 запоминания ответвляемого кода, при этом входыперного 11 и третьего 15 блоковзапоминания кодов соединены междусобой и являются первым входом Щасинхронно-синхронного регистра 8первой регистровой ячейки 9, а вторым и третьим входами служат вторыевходы первого 12 и второго 14 блоков внутрирегистровых сдвигов кодОв, 25при этом выход блока 17 запоминанияответвляемого кода служит первымвыходом, а выход второго блока 13запоминания кодов является вторымвыходом асинхронно-синхронного регистра 8 первой регистровой ячейки 9.Устройство работает следующимобразом.Во время нахождения лесоматериалана позиции оценки его качестваэадатчиком 1 адресов через дешифратор 2 код адреса накопителя вводятв начальный асинхронный регистр 3(фиг. 1),После прохождения ацресованноголесоматериала мимо путевого датчика 5 первого накопителя действием.блока 6 сдвига кодов код сдвигаетсяиэ начального асинхронного регистра 3в первую регистровую ячейку 9,Совершенно аналогично код сдвигается 45дальше, пока не придет н регистровуюячейку, предыдущую по отношению кданной рассматриваемой регистровойячейке.Если для данной ячейки код, пришедший в предыдущую ячейку, являет" ся исполнительным, то после прохождения лесоматериала мимо путевого датчика 5 данной регистроной ячейки действием блока 6 сдвига кодой код попадает в дешифратор 4, где расшифровывается и поступает на исполнительный механизм (не показан), Лесоматериал в результате попадает в предназначенное ему место, 60Если для данной регистровой ячейки код является ответвляемым, то в зависимости от разновидности исполнения ответвляемого тракта код проходит или через первый блок 11 запо минания кодов, первый блок 12 внут рирегистрового сдвига кодов, дешифратор 16 ответвляемого кода и блок 17 запоминания атнетвляемого кода (Фнг. 2), или через дешифратор 16 ответвляемого кода, первый блок 11 запоминания кодов, первый блок 12 внут рире,гистрового сдвига кодов, единичный шифратор 18 и второй блок 13 запоминания кодов (Фиг. 3), или через второй блок 13 запоминания кодов, первый блок 12 ннутрирегистровых сдвигов кодов .и блок 17 запоминания ответвляемого кода (Фиг. 4), иличерез третий блок 15 запоминания кодов, второй блок 14 внутриреистрового сдвига кодов и блок 17 запоминания ответвляемого 4 кода (Фиг. 5) причем во всех вариантах ответнленного тракта на его выход код поступает после воздействия данного лесоматериала на путевой датчик 5 второй беэрегистровой ячейки 10. Такая синхронизация перемещения лесоматериалов и кода обеспечивается синхронизирующей связью между путевым датчиком 5 и блоком 7 сдвига кодов с дешифратором 7 второй регистровой ячейки 10 с асинхронно- синхронным регистром 8 первой регистровой ячейки 9. После завершения указанного воздействия по сигналу путевого датчика 5 второй регистровой ячейки 10 возбуждается ее блок 7 сдвига кодов с дешифратором и код вьцается исполнительному механизму (не показан), Лесоматериал .попадает в предназначенное ему место, Аналогично работают все остальные беэрегистровые ячейки.Еслидля данной ячейки код является транзитным, то в зависимости от исполнения транзитного тракта код проходит или через первый блок 11 запоминания кодов, первый блок 12 внутрирегистроного.сдвига кодов, второй блок 13 запоминания кодов, второй блок 14 внутрирегистрового сдвига кодов и третий блок 15 запоминания кодов (фиг. 2), или через второй блок 13 запоминания кодов, второй блок 14 ннутрирегистрового сдвига кодов и третий блок 15 запоминания кодов (Фнг. 3), или черезпервый блок 11 запоминания кодов, первый блок 12 внутрнрегистрового сдвига кодов, третий блок 15 запоминания кодов, второй блок 14 внутри- регистрового сдвига кодов и четвер" тый блок 19 запоминания кодов(Фиг. 4), или через первый блок 11 запоминания кодов, первый блок 12 внутрирегистроного сдвига кодов и второй блок 13 запоминания кодов (Фиг. 5). С третьего блока 15 запоминания кодов код сдвигается действием блока 6 сдвига кодов после прохождения лесоматериала мимопутевого датчика 5 следующей первойрегистровой ячейки 9, а затем, каки в данной регистровой ячейке, взависимости от разновидности кодалибо сразу выдается исполнительному 5механизму следующей первой регистро-.вой ячейки 9, либо попадает в ответвленный тракт и выдается затем исполнительному механизму регистровойячейки, отстоящей от рассматриваемойчерез один накопитель, либо черезтранзитный тракт переходит в регист,ровую ячейку, отстоящую от рассматриваемой через два накопителя и т.д,обеспечивая раскладку лесоматериаловпо своим накопителям. Предлагаемое устройство повьаааеткачество сортировки.

СмотретьЗаявка

3472931, 21.07.1982

СЕВЕРНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРОМЫШЛЕННОСТИ

КИЛЯКОВ АЛЕКСЕЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: B07C 5/14, G05B 19/18

Метки: лесоматериалов, сортировкой

Опубликовано: 23.01.1984

Код ссылки

<a href="https://patents.su/9-1068894-ustrojjstvo-upravleniya-sortirovkojj-lesomaterialov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления сортировкой лесоматериалов</a>

Предыдущий патент: Устройство для программного управления

Следующий патент: Устройство для позиционного программного управления

Случайный патент: Устройство для вычисления преобразования фурье