Декодер сверточного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 769736

Авторы: Немировский, Четверик

Текст

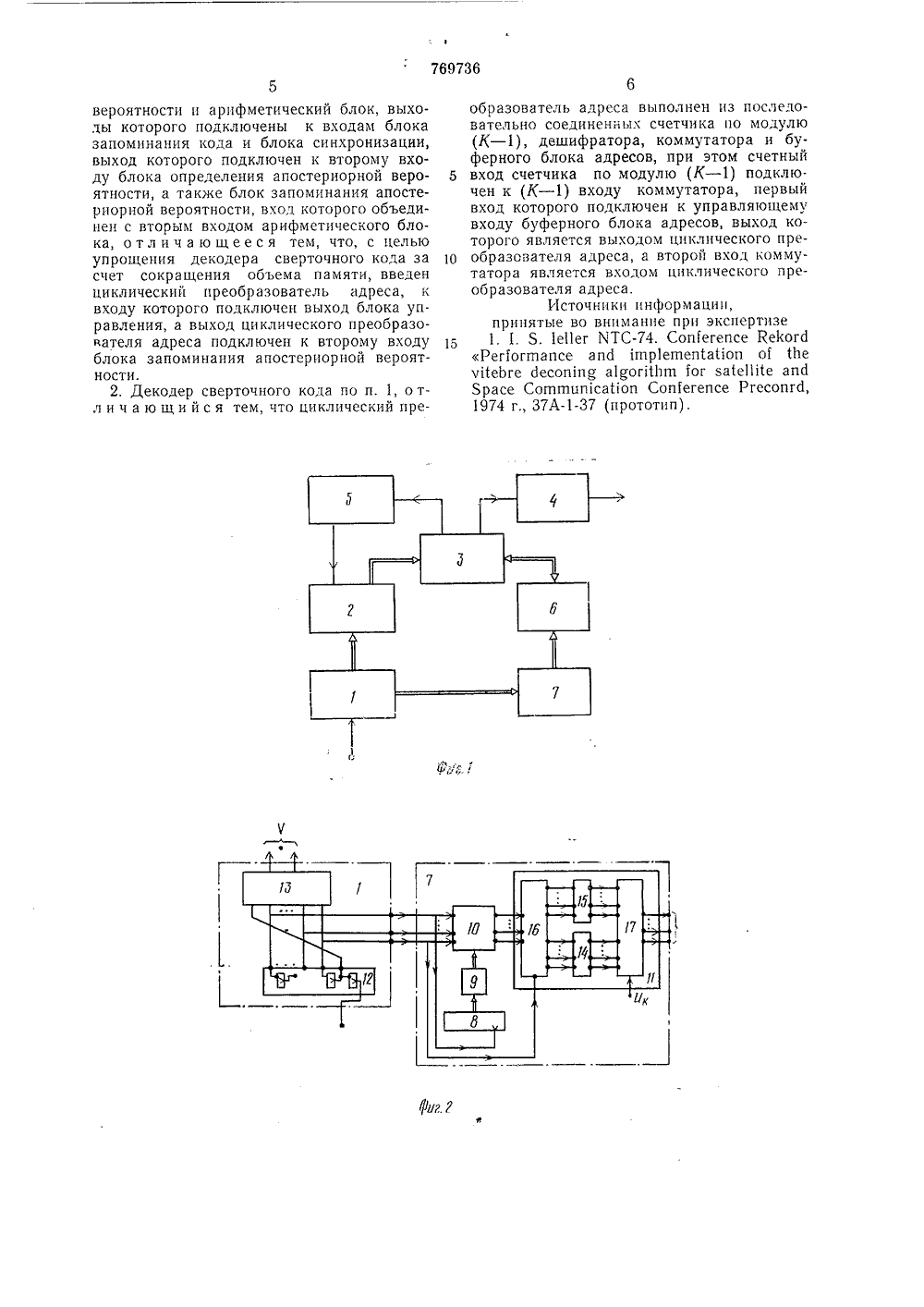

ОБРЕТЕН н 1 7697 оюз Советских Социалистическ Республик ОР СКОМУ СВ ИДЕТ К(45) Дата опубликования описания 53) УД 1( 621.394.. Э. Немировский и В. Н, Четверик 71) Заявитель РТОЧНОГО КОД 4) ДЕКОДЕ Изобретениежет использнных. 15меет сложную и з сударственнын комитет (23) Приоритет тносится к технике связи и аться в системах передачи Известен декодер сверточного кода, содержащий последовательно соединенные блок управления, блок определения апостериорной вероятности и арифметический блок, выходы которого подключены к входам блока запоминания кода и блока синхронизации, выход которого подключен к второму входу блока определения апостериорной вероятности, а также блок запоминания апостериорной вероятности, вход которого объединен с вторым входом арифметического блока 11.Однако такой декодерсхему,Цель изобретен я - упрощение декодера сверточного кода а счет сокращения объема памяти.Для этого в декодер сверточного кода, содержащий последовательно соединенные блок управления, блок определения апостериорной вероятности и арифметический блок, выходы которого подключены к входам блока запоминания кода и блока синхронизации, выход которого подключен к второму входу блока определения апостернорной вероятности, а также блок запоминания апостериорной вероятности, вход которого объединен с вторым входом арифметического блока, введен циклический преобразователь адреса, к входу которого подключен выход блока управления, а выход циклического преобразователя адреса подключен к второму входу блока запоминания апостер нор ной вероятности, причем циклический преобразователь адреса выполнен из последовательно соединенных счетчика по модулю (К - 1), дешифратора, коммутатора и буферного блока адресов, при этом счетный вход счетчика по модулю (К - 1) подключен к (К - 1) входу коммутатора, первый вход которого подключен к управляющему входу буферного блока адресов, выход которого является выходом циклического преобразователя адреса, а второй вход коммутатора является входом циклического преобразователя адреса.На фиг, 1 дана структурная электрическая схема предложенного декодера; на фиг. 2 - схема циклического преобразователя адреса; на фиг. 3 - временные диаграммы, поясняющие работу циклического преобразователя адреса.Декодер содержит блок 1 управления, блок 2 определения апостериорной вероятности, арифметический блок 3, блок 4 запоминания кода, блок 5 синхронизации, блок б запоминания апостериорной вероятности,циклический преобразователь 7 адреса, который состоит из счетчика 8 по модулю(К - 1), дешифратора 9, коммутатора 10 ибуферного блока 11 адресов,Декодер работает следующим образом.В начальном состоянии все блоки 4, 6 обнулены. На вход блока 2 поступаетотсчетов сигнала. В блоке 2 вычисляются 2 ъ алгебраических сумм и разностей - ветвевых метрик.По окончании вычислений в блоке 2 навход блока 1 подаются импульсы с частотой Я 2". Каждое состояние счетчика 12(блок 1, фиг. Зб) К параллельных разрядовпередается на вход кодера 13, а младшие(К - 1) разрядов одновременно подаются навход циклического преобразователя 7. В кодере 13 вырабатывается код адреса ветвевой метрики 1, совпадающий с двоичнымобозначением соответствующих канальныхсигналов, По этому адресу в блоке 2 выбирается ветвевая метрика и передается навход арифметического блока 3. Одновременно адрес преобразуется в исполнительныйадрес. При этом коммутатор 10 соединяетразрядные шины. При начальном (нулевом)состоянии счетчика 8 соединяются одноименные разрядные шины. При каждом изменении состояния У счетчика 8 состояниекоммутатора 10 циклически изменяется так,что всегда выполняется следующее правилосоединения входных шин (1 ) с выходными шинами (1 1):- 1 =- 1 + М (пкн 1 К - 1).Выходной адрес коммутатора 10 передается на регистр 14 или 15 через переключатель 16 по следующему правилу: все четные по порядку поступления адреса (нулевой, второй и т. д.) передаются в регистр14, все нечетные - в регистр 15, Переключатель 16 устанавливает соответствующиесоединения в зависимости от значения(фиг. За) младшего разряда входного адреса, которое подается на управляющийвход переключателя 16. Содержимое одного из регистров 14 или 15 передается навыход циклического преобразователя 7 через переключатель 17 в зависимости от значения управляющего сигнала (фиг. Зв). Поадресу производится выборка метрик и пересылка в блок 3 старых значений метриксостояний и запись в блок 6 из блока 3 новых значений метрик.Период Т от момента 1 о до 1 время обработки информации, относящейся к однойпаре состояний кодера 13. В момент 1, производится выборка из блока 6 метрики, относящейся к состоянию кодера 13 (аь,а, О), В интервале 1 о + 1, в арифметическом блоке 3 вычисляется новое значениеметрики при переходе к состоянию О,ак а т, е. при а= О. В моментзначение аменяется с О на 1 и в арифметическом блоке 3 вычисляется новое значе 5 10 15 20 25 ЗО 35 40 45 50 55 60 65 ние метрики при переходе в состояние 1, а,; ь,а,.В момент 1 изменяется значение разрядов (фиг, За, б) счетчика 12, Производится выборка метрик по адресу, соответствующему состоянию кодера 13 (аь, а ) и счет в арифметическом блоке 3 (на интервале 1 - .1,) нового значения метрики для перехода в состояние О, а, - ъ а, (а=О). Второй адрес считывания, преобразованный в преобразователь 7, запоминается в регистре 15, соответствующее перключение переключателя 16 выполняется в момент 1 управляющим сигналом (фиг. За). В последующие два момента времени г 4 и г 5 производится запись (фиг. Зд) новых значений метрик по тем же адресам, по которым ранее была сделана выборка и которые хранятся в регистрах 14, 15. Для этой цели в момент 1, управляющий сигнал (фиг. Зв) подготавливает переключатель 17 для соединения регистра 14 с выходом преобразователя 7. К моменту записи г 4 в арифметическом блоке 3 сравниваются два значения метрик (фиг. Зг) для состояния О, аь, а,: значение, полученное на пути, ведущему из состояния с а, = О и значение, полученное на пути, ведущему из состояния с а, 1. Наибольшее значение записывается в блок 6 в момент 14 по адресу, выдаваемому на вход блока 6 из регистра 14, а соответствующее выигравшее значение (фиг. За) выдается из арифметического блока 3 в блок 4. Аналогичное сравнение двух метрик для состояния 1, аь, а, и путей а, - О и а, - 1 выполняется в арифметическом блоке 3 на отрезке 14 - :1 ь. К моменту записи 15 переключатель 17, управляемый напряжением (фиг. Зв), подключает к выходу преобразователя 7 регистр 15, где хранится второй адрес записи.Описанный цикл повторяется 2" враз, после чего счетчик 13 переполняется и сбрасывается. В этот момент обновлены и пере- упорядочены все 2" взначений метрик состояний в блоке 6. Счетчик 8 увеличивает свое значение на 1 и тем самым изменяет соединения разрядов входного и выходного адресов в преобразователе 7, приводя его в соответствие с новым упорядочением результатов в блоке 6.Введенный циклический преобразователь адреса 7 обеспечивает .автоматическое согласование периодически изменяющегося порядка метрик в блоке 6 с неизменным лексикографическим упорядочением перебираемых счетчиком 12 состояний кодера 13.Предложенный декодер имеет более простую схему за счет сокращения объема памяти,Формула изобретения 1. Декодер сверточного кода, содержащий последовательно соединенные блок управления, блок определения апостериорнойвероятности н арифметический блок, выходы которого подключены к входам блоказапоминания кода и блока синхронизации,выход которого подключен к второму входу блока определения апостериорной вероятности, а также блок запоминания апостериорной вероятности, вход которого объединен с вторым входом арифметического блока, отличающееся тем, что, с цельюупрощения декодера сверточного кода за 10счет сокращения объема памяти, введенциклический преобразователь адреса, квходу которого подключен выход блока управления, а выход циклического преобразователя адреса подключен к второму входу 15блока запоминания апостериорной вероятности,2. Декодер сверточного кода по п. 1, о тл и ч а ю щ и й с я тем, что циклический преобразователь адреса выполнен из последовательно соединенных счетчика по модулю (К - 1), дешифратора, коммутатора и буферного блока адресов, при этом счетный вход счетчика по модулю (К - 1) подключен к (К - 1) входу коммутатора, первый вход которого подключен к управляющему входу буферного блока адресов, выход которого является выходом циклического преобразователя адреса, а второй вход коммутатора является входом циклического преобразователя адреса.Источники информации,принятые во внимание при экспертизе 1, 1. 5, 1 е 1 ег ХТС. Соп 1 егепсе Ке 1 согд Рег 1 оппапсе апс 1 1 гпр 1 егпеп 1 айоп о 1 Йе и 1 еЬге с 1 есоп 1 пд а 1 догН 1 пп 1 ог за 1 е 1111 е апд Ьрасе Сопппцп 1 саИоп Соп 1 егепсе Ргесопгд, 1974 г., 37 А-37 (прототип)., ч 4769736 . 1 озаСоставитель Т. Маркина Редактор Н. Тимонииа Техред И. Пеичко Корректор М. Гаврило Заказ 2412/12 Изд,504 Тираж 995 Подписное НПО Поиск Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж.35, Раугпская наб., д. 4/5ипография, пр. Сапунова, 2

СмотретьЗаявка

2677487, 23.10.1978

ПРЕДПРИЯТИЕ ПЯ В-8466

НЕМИРОВСКИЙ ЭРНСТ ЭДУАРДОВИЧ, ЧЕТВЕРИК ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 13/23

Метки: декодер, кода, сверточного

Опубликовано: 07.10.1980

Код ссылки

<a href="https://patents.su/4-769736-dekoder-svertochnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Декодер сверточного кода</a>

Предыдущий патент: Преобразователь напряжения в частоту

Следующий патент: Коммутатор

Случайный патент: Устройство для контроля положения изделий