Устройство для арифметической и логической обработки двоичных и двоично-десятичных -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 962922

Авторы: Гурьянов, Козюминский, Мищенко, Семашко

Текст

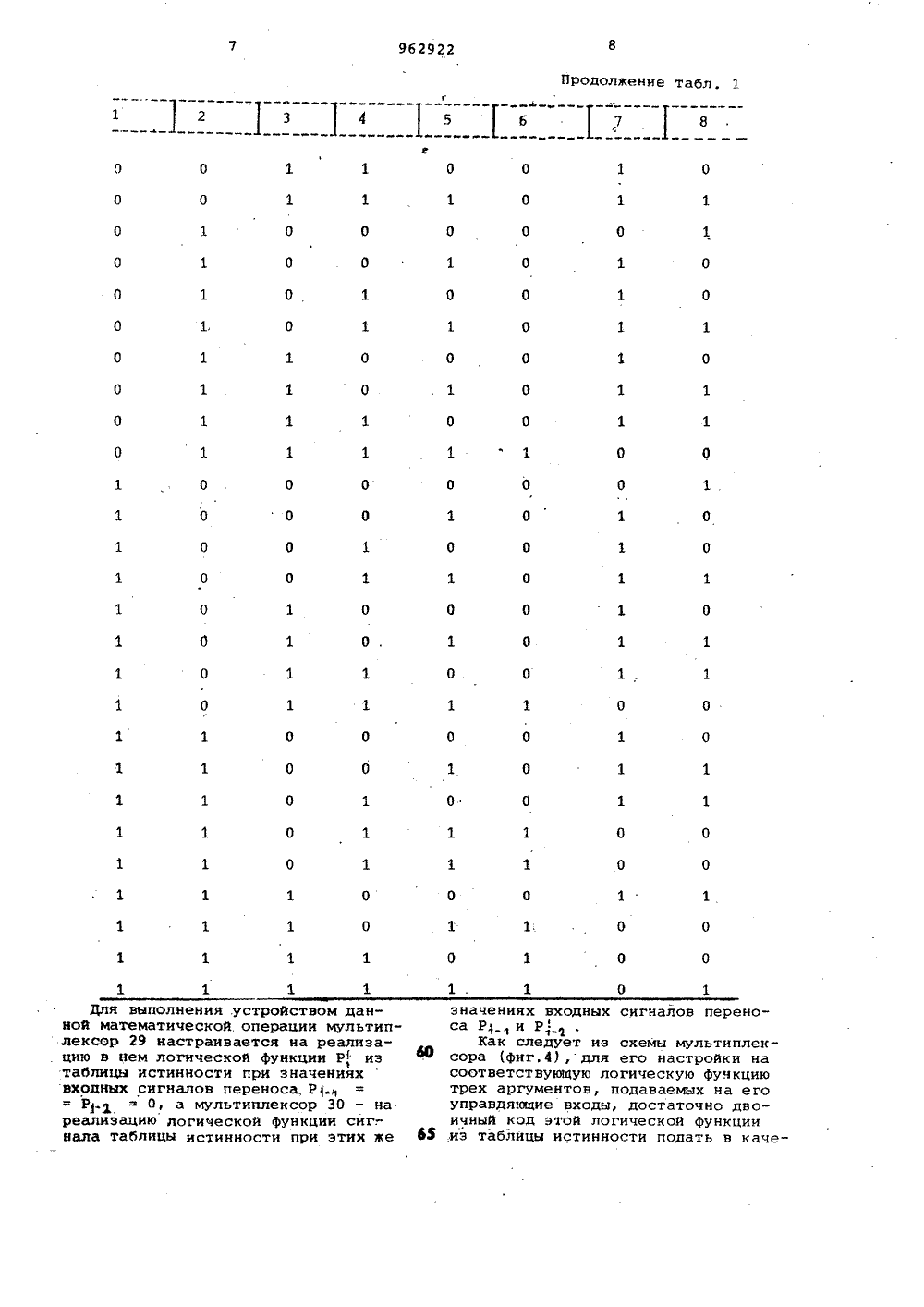

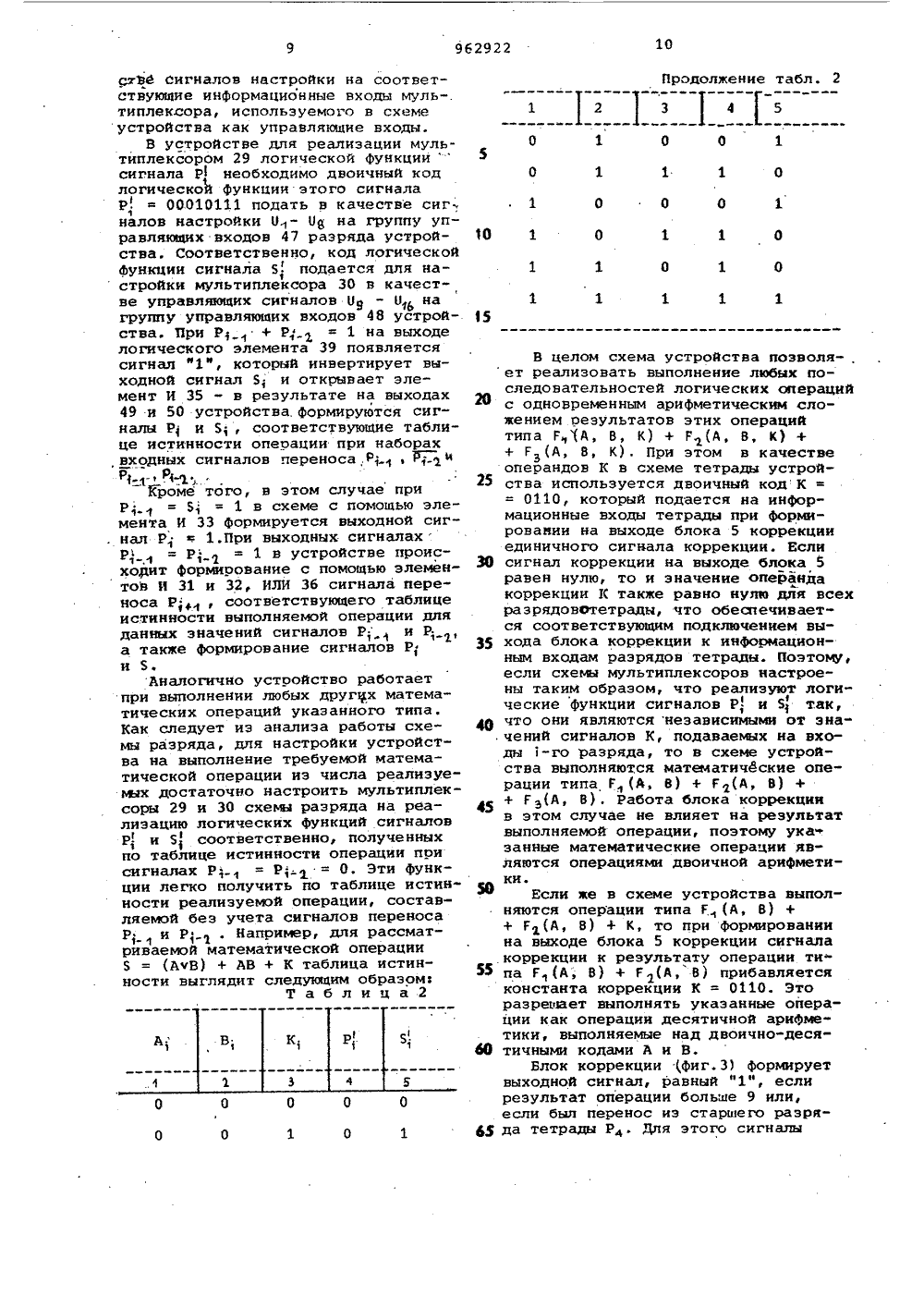

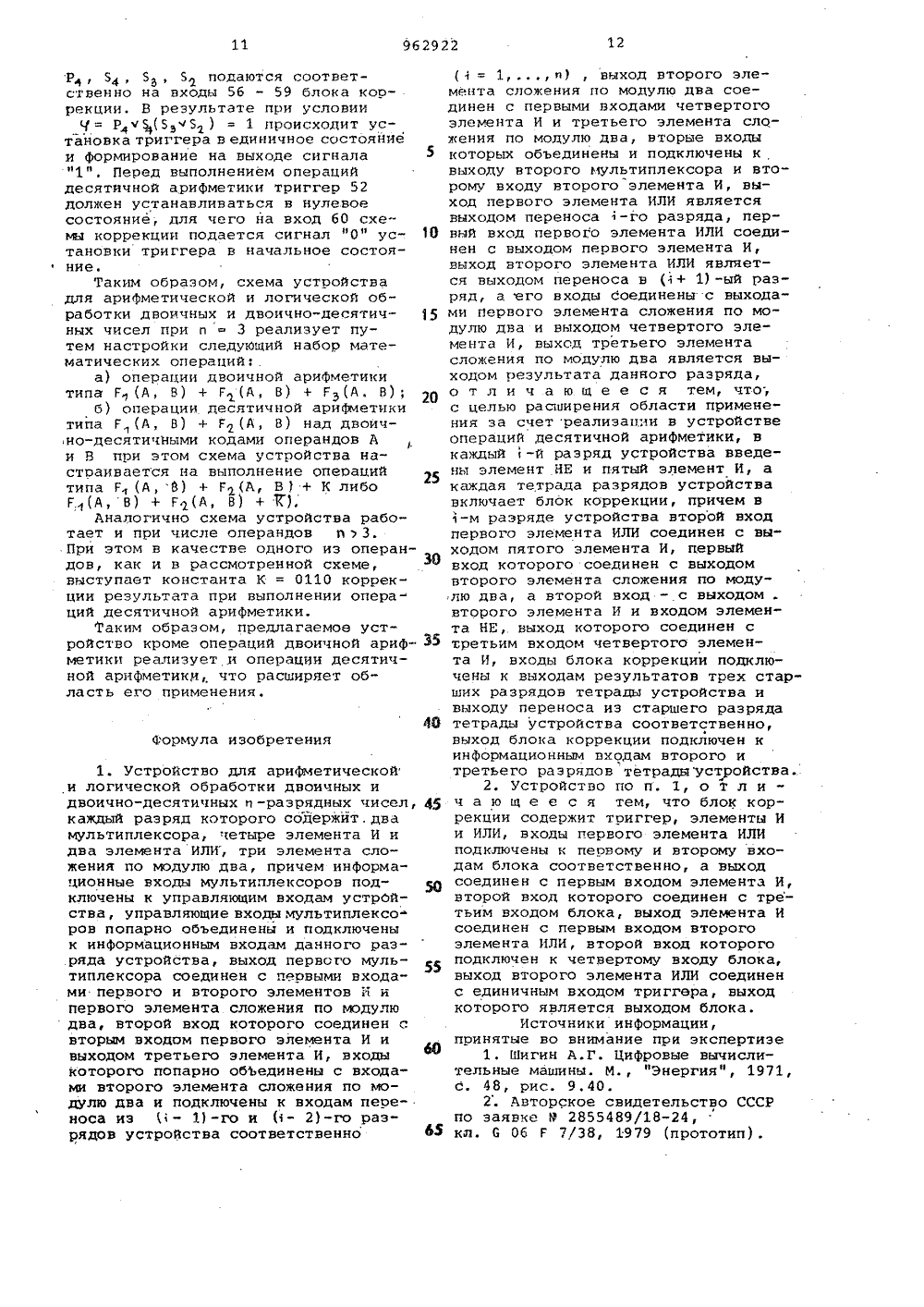

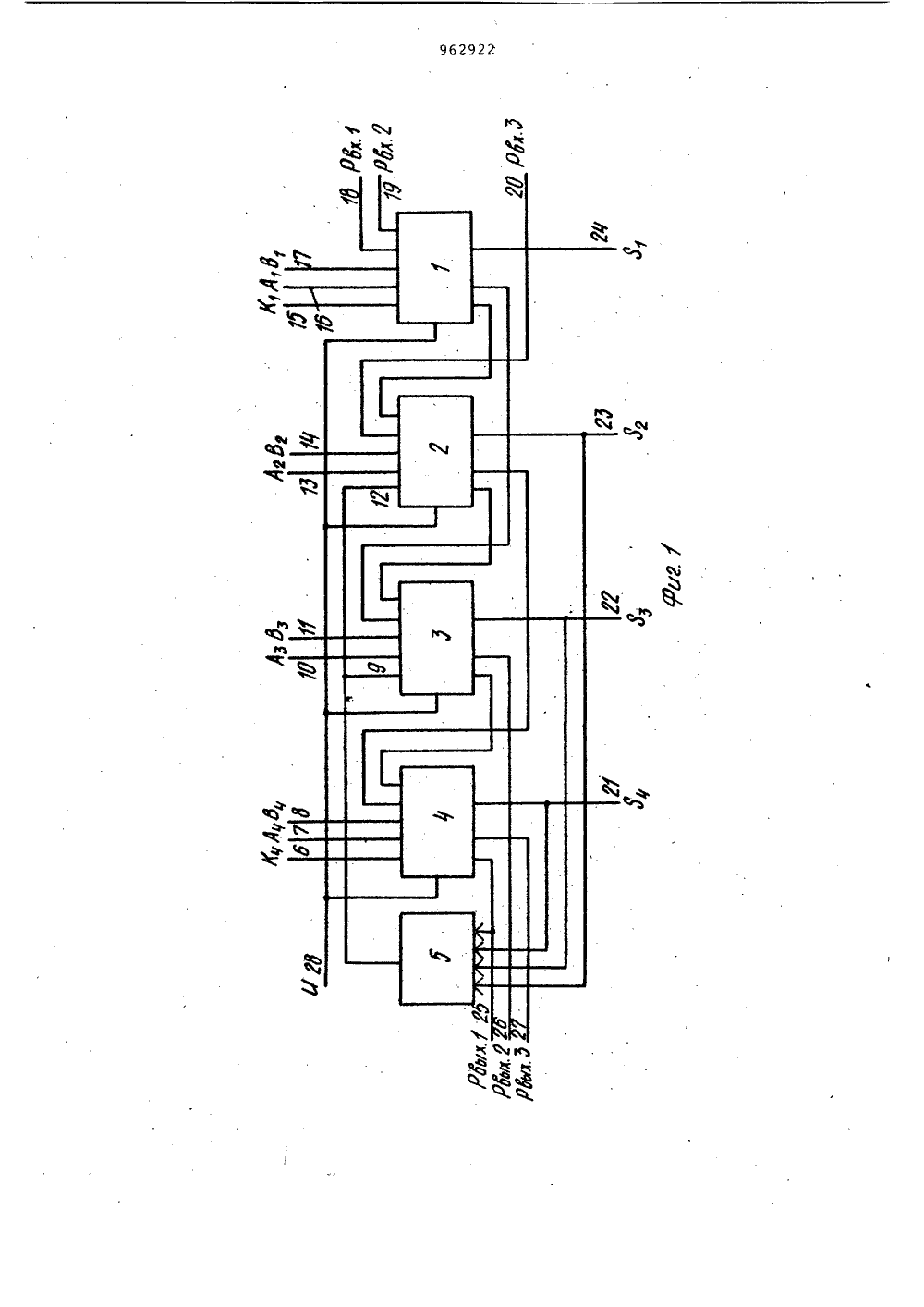

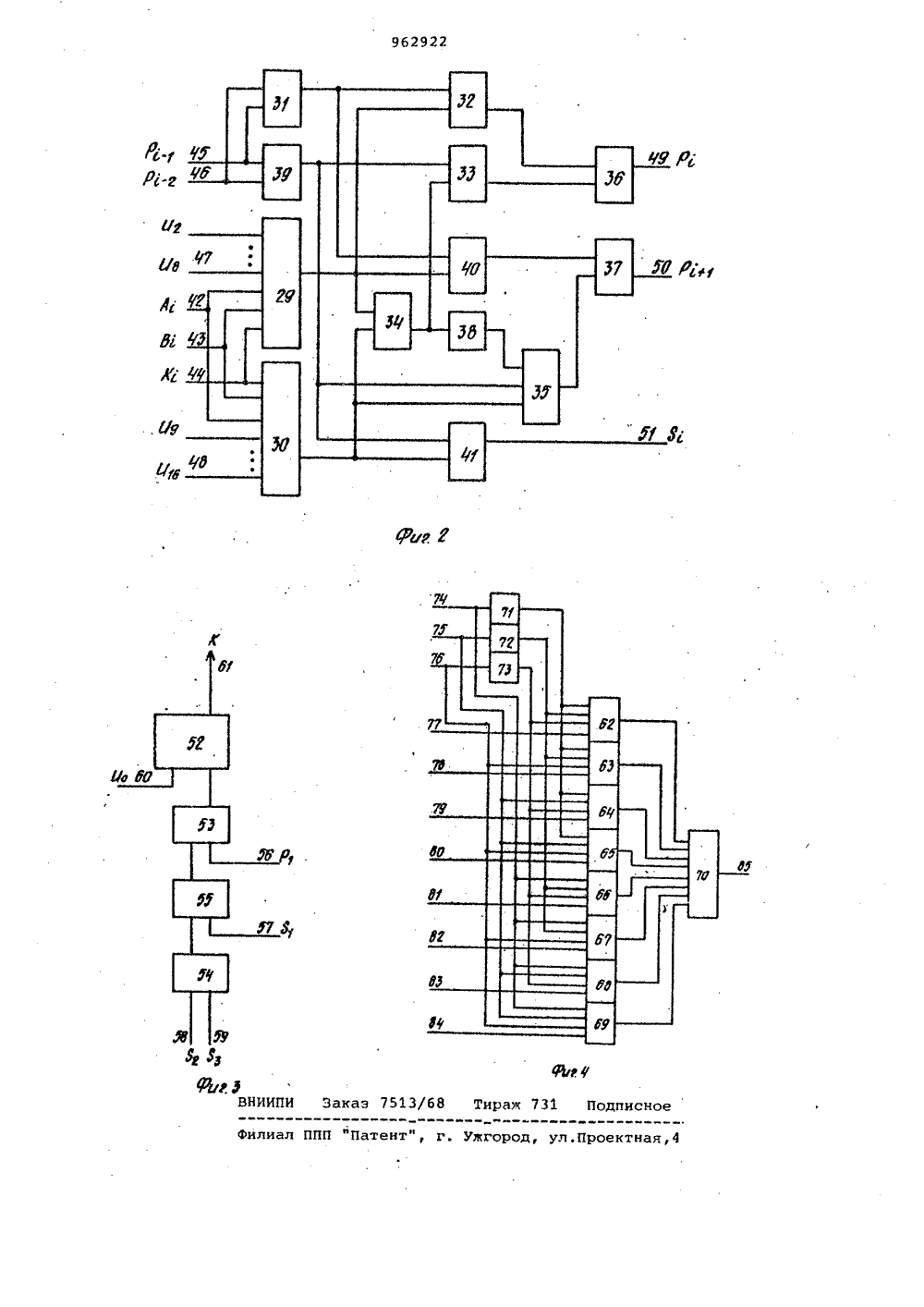

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик рщ 962922(22) Заявлено 16.06,80 (2 ) 2942870/18-24 Р 1 М Кп 3 С 06 Г 7/38 с присоединением заявки Нов Государственный комитет СССР по делаю изобретений и открытий(088,8) Опубликовано 30.09,82 Бюллетень М 36 Дата опубликования описания 30. 09. 82 В.Д. Козюминский, В.А. Мищенко, А.Н. Семаш и А.В. Гурьянов(54) УСТРОЙСТВО ДЛЯ АРИФМЕТИЧЕСКОЙ И ЛОГИЧЕСКОЙ ОБРАБОТКИ ДВОИЧНЫХ И ДВОИЧНО-ДЕСЯТИЧНЫХ и-РАЗРЯДНЫХ ЧИСЕЛИзобретение относится к вычислительной технике и может использоваться припостроении устройств обработки цифровой информации в ЭВМ.Известно устройство для сложения двоично-десятичных кодов, содержащее сумматоры, схемы переноса и коррекции 1,).Недостатком устройства является то, что оно не реализует операций сложения двоичных кодов и логических операций.Наиболее близким по технической сущности к предлагаемому является устройство для арифметической и логической обработки двоичныхчисел, каждый разряд которого содержит инФормационные входы и два входа переноса, выход результата и два выхода переноса, управляющие входы, элементы И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ - выходва мультиплексора, управляющие входы которых попаоно объединены и подключены к информационным входам уст.ройства, информационные входы муль-. 25 типлексоров являются управляющими входами устройства. Выход первого мультиплексора соединен с первыми входами первого и второго элементов И и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и 30 второй вход которого соединен с.вторьм входом первого элемента И и выходом третьего элемента И, входы которого попарно объединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ т и подключены к входам переноса разряда. Выход второго элемента ИСКЛЮЧАЮЩЕЕ ,ИЛИ соединен с вторым входом второго элемента И и первым входом четвертого элемента И и третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых объединены и подключены к выходу второго мультиплексора и третьему входу второго элемента И, выход которого соединен с третьим входом первого элемента ИСКЛЮ-, ЧАЮЩЕЕ ИЛИ соединен с вторым вхо-. входом первого элемента ИЛИ,другой вход которого соединен с выходом четвертого элемента И. Выходы вто" рого элемента ИЛИ подключены к выходам первого и второго элементов И. Выходы элементов ИЛИ являются выходами переноса, а выход третьего элемента ИСКЛЮЧАПЩИЕ ИЛИ - выходом результата устройства 2).Устройство путем настройки реализует любые математические операции обработки двоична чисел типа г(х- х) + г(х, - . х) + г (х 962922Х), где Г(Х- Х) - произволь"ные логические операции функции ипеременных над операндами Х 1, ХХпНедостатком устройства являетсято, что оно не реализует операцийдесятичной арифметики над двоичнодесятичными кодами,Цель изобретения - расширение области применения путем реализации вустройстве операций десятичной арифметики.,Поставленная цель достигаетсятем, что устройство для арифметической и логической обработки двоичных и двоично-десятичных и-разрядных чисел, каждый разряд которогосодержит два мультиплексора, четыреэлемента И и.два элемента ИЛИ, триэлемента сложения по модулю два,причем информационные входы мультиплексоров подключены к управляющимвходам устройства, управляющие входымультиплексоров попарно объединеныи подключены к информационным входамданного разряда устройства, выходпервого мультиплексора соединен спервыми входами первого и второгоэлементов И и первого элемента сложения по модулю два, второй вход которого соединен с вторым входом первого элемента И и выходом третьегоэлемента И, входы .которого попарнообъединены с входами второго элемента сложения по модулю два и подключены к входам переноса из (1 - 1)-гои (1 - 2)-го разрядов устройства соответственно ( = 1, , и), выходвторого элемента сложения по модулюдва соединен с первыми .входами четвертого элемента И и третьего элемента сложения по модулю два, вторыевходы которых объединены и подключены к выходу второго мультиплексораи второму входу второго элемента И,выход первого элемента ИЛИ являетсявыходом переноса -го разряда, первый вход первого элемента ИЛИ соединен с выходом первого элемента И,выход второго элемента ИЛИ являетсявыходом переноса в ( + 1)-ый разряд, а его входы соединены с выходами первого элемента сложения по модулю два и выходом четвертого элемента И, выход третьего элемента сложения по модулю два является выходомрезультата данного разряда, в каждый л -й разряд устройства введеныэлемент НЕ и пятый элемент И, а каждая тетрада разрядов устройствавключает блок коррекции, причем в1-м разряде устройства второй входпервого элемента ИЛИ соединен с выходом пятого элемента И, первый.вход которого соединен с.выходомвторого элемента сложения по модулюдва, а второй вход - с выходом второго элемента И и входом элемента НЕ, выход которого соединен стретьим входом четвертого элемента И,входы блока коррекции подключены квыходам результатов трех старших разрядов тетрады устройства и выходупереноса из старшего разряда тетрадыустройства соответственно, выход блока коррекции подключен к информационным входам второго и третьего разрядов тетрады устройства,Кроме того, блок коррекции содержит триггер, элементы И и ИЛИ, входы первого элемента ИЛИ подключены кпервому и второму входам блока соответственно, а выход соединен с первым входом элемента И, второй вход которого соединен с третьим входом блока, выход элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого подклюнен к четвертому входу блока, выход второго элемента ИЛИ соединен с единичным входом триггера, выход которого яв;ляется выходом блока962922 Таблица 1 А; 5 0 0 разряды обрабатываемых чисел А и В, а также сигнал с выхода схемы блока коррекции, для чего выход блока коррекции подключен к третьим информационных входам 2-го и 3-го разрядов, а на соответствующие входы 1-го и 4-го разрядов тетрады подается нулевой сигнал, в результате чего в качестве третьего операнда в тетраде является код 0110.Входы настроек каждого разряда подключены к группам управлякзаих вхо дов 28 устройства.В схеме разряда устройства (фиг.2) информационные входы мультиплексоров 29 и 30 подключены к группам управляющих входов 47, и 48, а их управляющие входы попарно объединены и подключены к информационным входам 42 - 44 разряда. Выход мультиплексора 29 соединен с входами элементов И 32 и 34 и входом элемента 40 сложения по модулю два. Вторые входы элементов 32 и 40 подключены к выходу элемента И 31, входы которого попарно объединены с входами элемента 39 сложения по модулю два и подключены к входам,45 и 46 переноса. разряда. Выход элемента 39 соединен с входами элементов И 33 и 35 и входом элемента 41 сложения по модулю два, выход которого является выходом 51 результата разряда, Вто рой вход элемента 41 подключен к входам элементов 34 и 35 и выходу мультиплексора 30. Выход элемента И 3 соединен с входом элемента И 33 и входом элемента НЕ 38, выход которого соединен с входом элемента И . 35. Входы элементов ИЛИ 36 и 37 подключены соответственно к выходам элементов 32, 33 и 35, 40, а выяоды элементов 36 и 37 являются выходами 49 и 50 пепеносов из схем разряда. В блоке коррекции (фиг.З) входустановки триггера 52 в единичноесостояние соединен с выходом элемента ИЛИ 53, один вход которого является входом 46 блока операции, адругой его вход соединен с выходомэлемента И 55, первый вход которогоявляется входом 57 блока, а его другой вход соединен с выходом элемента ИЛИ 54, входы которого являются 10 входами 58 и 59 блока коррекции. Выход триггера является выходом 61блока коррекции, а его вход установки в нуль является входом 60 блокакоррекции.15 Устройство для арифметической илогической обработки двоичных и двоично-десятичных чисел работает сле.дующим образом. 33 На информационные входы 42 - 44разряда устройства (фиг.2) подаются одноименные разряды А, В.и К операндов А, В к К, а на входы 45 и46 - сигналы переноса Р; и Р .1 соот ветственно из ( - 2)-го и (1- 1)-горазрядов устройства. С выхода 51разряда устройства снимается сигнал5; результата выполняемой математической операции, а с выходов 49 и50 - сигналы Р; и Р;1 переноссв в(1 + 1)-й и ( + 2)-й разряды устройства соответственно. Настройка устройства на выполнение требуемой математической операции типа Р(А, В, К) Ф Г(А,В,К)ф+ Е(А, В; К) осуществляется с помощью сигналов настройки О 1 - Ое иО 9 - О 16 . подаваемых на группы управляющих входов 47 и 48 мультиплексоров 29 и 30 соответственно.Рассмотрим работу устройства на ф .примере выполнения операции 5(АчВ) + (А В) + К, таблица истинности для которой приведена в962922 1 О О 0 О О О О О О О О О а О О О О 0 О Для выполнения .устройством данной математической. операции мультиплексор 29 настраивается на реализа. цию в нем логической функции Р, иэ таблицы истинности при значениях входных сигналов переноса, Р.РО, а мультиплексор 30 - на реализацию логической функции сиг.- нала таблицы истинности при этих же Продолжение табл. 1г значениях входных сигналов переноса Ри РКак следует из схемы мультиплек- Ж сора (фиг.41, для его настройки насоответствуваую логическую фучкцию трех аргументов, подаваемых на его управдяющие входы, достаточно двоичный код этой логической функции 6 ,иэ таблицы истинности подать в качедхве сигналов настройки на соответствующие информационные входы муль-.типлексора, используемого в схеме устройства как управляющие входы.В устройстве для реализации мультиплексором 29 логической Функциисигнала Р необходимо двоичный кодлогической функции этого сигналаР00010111 подать в качестве сигвалов настройки О- Ов на группу управляющих входов 47 разряда устройства. Соответственно, код логической функции сигнала 5,. подается для настройки мультиплексора 30 в качестве управляющих сигналов ОВ - О нагруппу управляющих входов 48 устройства. При Р+ Р, 1 = 1 на выходе логического элемента 39 появляетсясигнал ф 1 ф, который инвертирует выходной сигнал 5; и открывает элемент И 35 - в результате на выходах49 и 50 устройства. формируются сигналы Р( и 5;, соответствующие таблице истинности операции при наборах входных сигналов переноса,Р5:"1 ф фйКроме того, в этом случае при Р= 5, = 1 в схеме с помощью элемента И 33 формируется выходной сиг. нал Р1.При выходных сигналах Р= Р; 1 = 1 в устройстве происходит формирование с помощью элементов И 31 и 32, ИЛИ 36 сигнала переноса Р , соответствующего таблице истинности выполняемой операции для данных значений сигналов Р . и Р; а также Формирование сигналов Р; и 5.Аналогично устройство работает при выполнении любых других математических операций указанного типа. Как следует из анализа работы схемы разряда, для настройки устройства на выполнение требуемой математической операции иэ числа реализуеьих достаточно настроить мультиплексоры 29 и 30 схемы разряда на реализацию логических функций сигналов Р и 5 соответственно, полученных3по таблице истинности операции при сигналах Р;= Р 1 = О. Эти Функции легко получить по таблице истинности реализуемой операции, составляемой без учета сигналов переноса Р и Р,. Например, для рассматриваемой математической операции 5 = (ймВ) + АВ + К таблица истинности выглядит следующим образомТаблица 2Продолжение табл. 2 1:Г. 1 10 1 1 1 0 О 0 1 0 1 О 1 1 В целом схема устройства позволя-,ет реализовать выполнение любых последовательностей логических операцийс одновременным арифметическим сложением результатов этих операцийтипа Г(А, В, К) + Г (А, В, К ++ Г (А, В, К). При этом в качествеоперандов К в схеме тетрады устройства используется двоичный код К =0110, который подается на информационные входы тетради при формировании на выходе блока 5 коррекцииединичного сигнала коррекции. Если30 сигнал коррекции на выходе блока 5равен нулю, то и значение операндакоррекции К также равно нулю для всехразрядовотетрады, что обеспечивается соответствующим подключением вы хода блока коррекции к информационным входам разрядов тетрады. Поэтому,если схемы мультиплексоров настроены таким образом, что реализуют логические функции сигналов Р, и 5 так, ,щ что они являются независимыми от зна. чений сигналов К, подаваемых на входы 1-го разряда, то в схеме устройства выполняются математические операции типа Г(А, В) + Г(А, В) ++ Гз(А, В). Работа блока коррекциив этом случае не влияет на результатвыполняемой операции, поэтому указанные математические операции являются операциями двоичной арифметики.Если же в схеме устройства выполняются операции типа Г(А, В) ++ Г(А, 8) + К, то при формированиина выходе блока 5 коррекции сигналакоррекции к результату операции ти"па Г(А, В) + Г 1(А, В) прибавляетсяконстанта коррекции К = 0110. Эторазрешает выполнять указанные операции как операции десятичной арифметики, выполняемые над двоично-деся тичными кодамн й и В.Блок коррекции (Фиг.3) формируетвыходной сигнал, равный П 1", еслирезультат операции больше 9 или,если был перенос из старшего разря да тетрады Рд. Для этого сигналыР, 54, 5 Э, 52 подаются соответственно на входы 56 - 59 блока коррекции, В результате при условииЧ = Р ч (5 ч 52 ) = 1 происходит установка триггера в единичное состояние и формирование на выходе сигнала "1". Перед выполнением операций десятичной арифметики триггер 52 должен устанавливаться в нулевое состояние, для чего на вход 60 схемы коррекции подается сигнал "0" установки триггера в начальное состояние.Таким образом, схема устройства для арифметической и логической обработки двоичных и дноично-десятичных чисел при п3 реализует путем настройки следующий набор математических операций:а) операции двоичной арифметики типа Г (А, В) + Г 2(д, В) + Г(А, В);б) операции десятичной арифметики типа Г(А, В) + Г 2(А, В) над двоично-десятичйыми кодами операндов А и В при этом схема устройстна настраивается на выполнение операций типа Г (А, В) + Г 2(А, В ) + К либо Г(Д, В) + Г 2(Д, В) + К).Аналогично схема устройства работает и при числе операндов п3. При этом в качестне одного из операндов, как и н рассмотренной схеме, выступает константа К = 0110 коррек" ции результата при выполнении операций десятичной арифметики.1 аким образом, предлагаемое устройство кроме операций двоичной арифметики реализует и операцни десятичной арифметики, что расширяет об" ласть его применения.Формула изобретения1. Устройство для арифметической и логической обработки двоичных и двоично-десятичных и -разрядных чисел, каждый разряд которого содержит. дна мультиплексора, четыре элемента И и два элемента ИЛИ, три элемента сложения по модулю дна, причем информационные входы мультиплексоров подключены к управляющим входам устрОЙ- ства, управляющие входы мультиплексоров попарно объединены и подключены к информационным входам данного разряда устройства, выход первого мультиплексора соединен с первыми входами первого и второго элементов И и первого элемента сложения по модулю два, второй вход которого соединен с вторым входом первого элемента И и выходом третьего элемента И, входы которого попарно обЪединены с входами второго элемента сложения по модулю два и подключены к входам пеоеноса из (- 1)-го и (- 2)-го разрядов устройства соответственно(1 = 1 и), выход второго элемента сложения по модулю два соединен с первыми входами четвертогоэлемента И и третьего элемента сложения по модулю два, вторые входы которых объединены и подключены к выходу второго мультиплексора и второму входу второго элемента И, выход первого элемента ИЛИ является выходом переноса 1-го разряда, первый вход первого элемента ИЛИ соединен с выходом первого элемента И, выход второго элемента ИЛИ является выходом переноса н (1+ 1) -ый разряд, а его входы соединены с выходами первого элемента сложения по модулю два и выходом четвертого элемента И, ныхсд третьего элементасложения по модулю дна является выходом результата данного разряда,о т л и ч а ю щ е е с я тем, что;с целью расширения области применения за счет реализации в устройствеопераций десятичной арифметики, вкаждый-й разряд устройства введены элемент НЕ и пятый элемент И, акаждая тетрада разрядов устройстванключает блок коррекции, причем в1-м разряде устройства второй входпервого элемента ИЛИ соединен с выходом пятого элемента И, первый ЗО вход которого соединен с выходомвторого элемента сложения по модулю два, а второй вход - с выходом .второго элемента И и входом элемента НЕ, выход которого соединен стретьим входом четвертого элемента И, входы блока коррекции подключены к выходам результатов трех старших разрядов тетрады устройства ивыходу переноса иэ старшего разряда46 тетрады устройства соответственно,выход блока коррекции подключен кинформационным входам второго итретьего раэрядон тетрадиустуойства.2. Устройство по п, 1, о т л ичающее с я тем, что блок коррекции содержит триггер, элементы Ии ИЛИ, входы первого элемента ИЛИподключены к первому и второму входам блока соответственно, а выходсоединен с первым входом элемента И,второй вход которого соединен с тре- тьим входом блока, выход элЕмента Исоединен с первым входом второгоэлемента ИЛИ, второй вход которогоподключен к четвертому входу блока,выход второго элемента ИЛИ соединенс единичным входом триггера, выходкоторого является выходом блока.Источники информации,принятые во внимание при экспертизе1. Шигин А.Г. Цифровые вычислительные машины. М., "Энергия", 1971,с. 48, рис. 9.40.2Авторское свидетельство СССРпо заявке Р 2855489/18-24,65 кд, С 06 Г 7/38, 1979 (прототип).гЯ ВНИИПИ Закаэ 7513/68 Тираж 731 ПодписноеЮ 6 в Е Шилиал ППП "Патент", г, Ужгород, ул.Проектная,4

СмотретьЗаявка

2942870, 16.06.1980

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, СЕМАШКО АЛЕКСАНДР НИКОЛАЕВИЧ, ГУРЬЯНОВ АНАТОЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: арифметической, двоично-десятичных, двоичных, логической, разрядных, чисел

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/8-962922-ustrojjstvo-dlya-arifmeticheskojj-i-logicheskojj-obrabotki-dvoichnykh-i-dvoichno-desyatichnykh-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для арифметической и логической обработки двоичных и двоично-десятичных -разрядных чисел</a>

Предыдущий патент: Устройство для анализа и обработки знаковых разрядов

Следующий патент: Управляемый логический модуль

Случайный патент: Устройство для защиты от импульсных помех