Генератор испытательных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

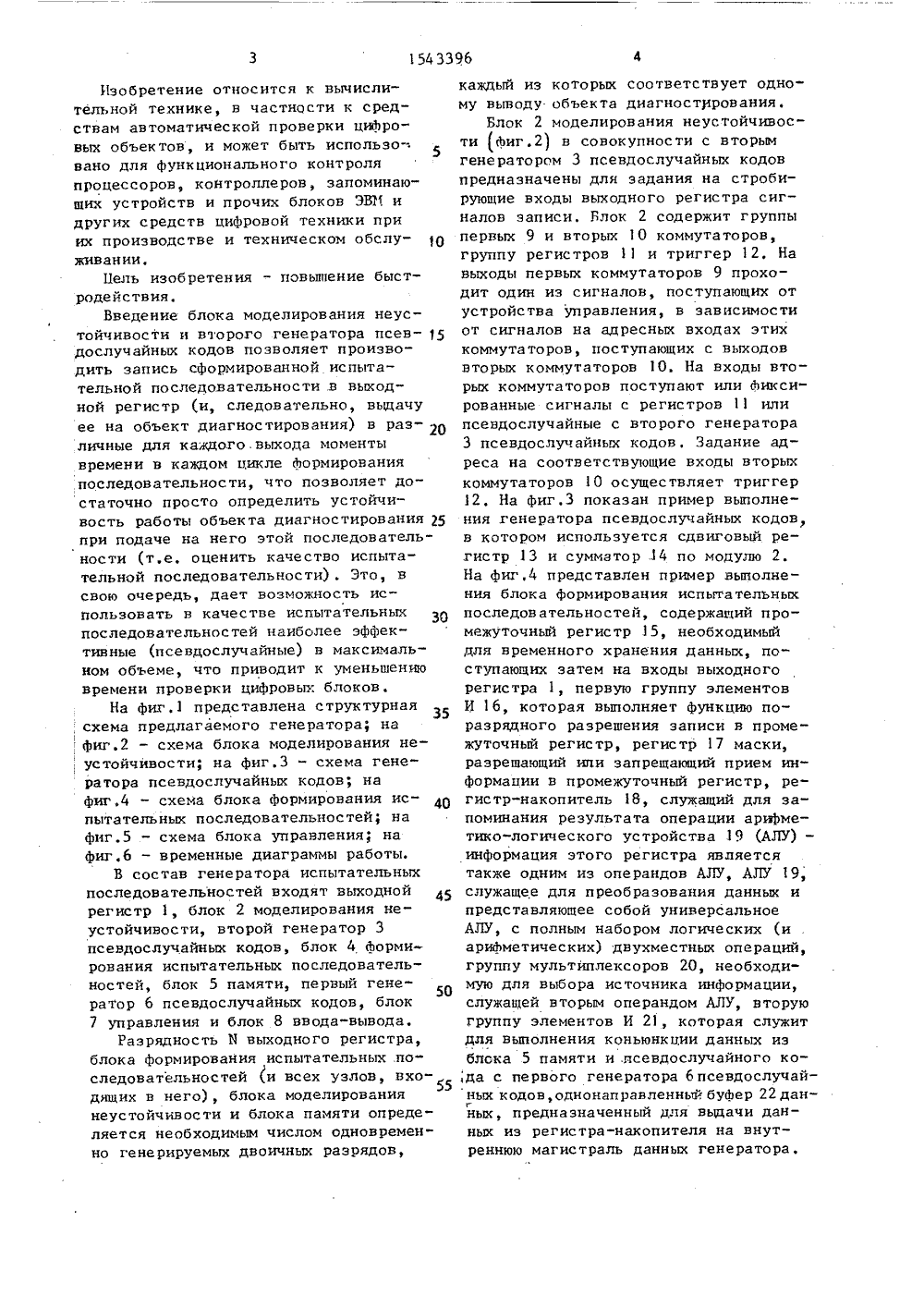

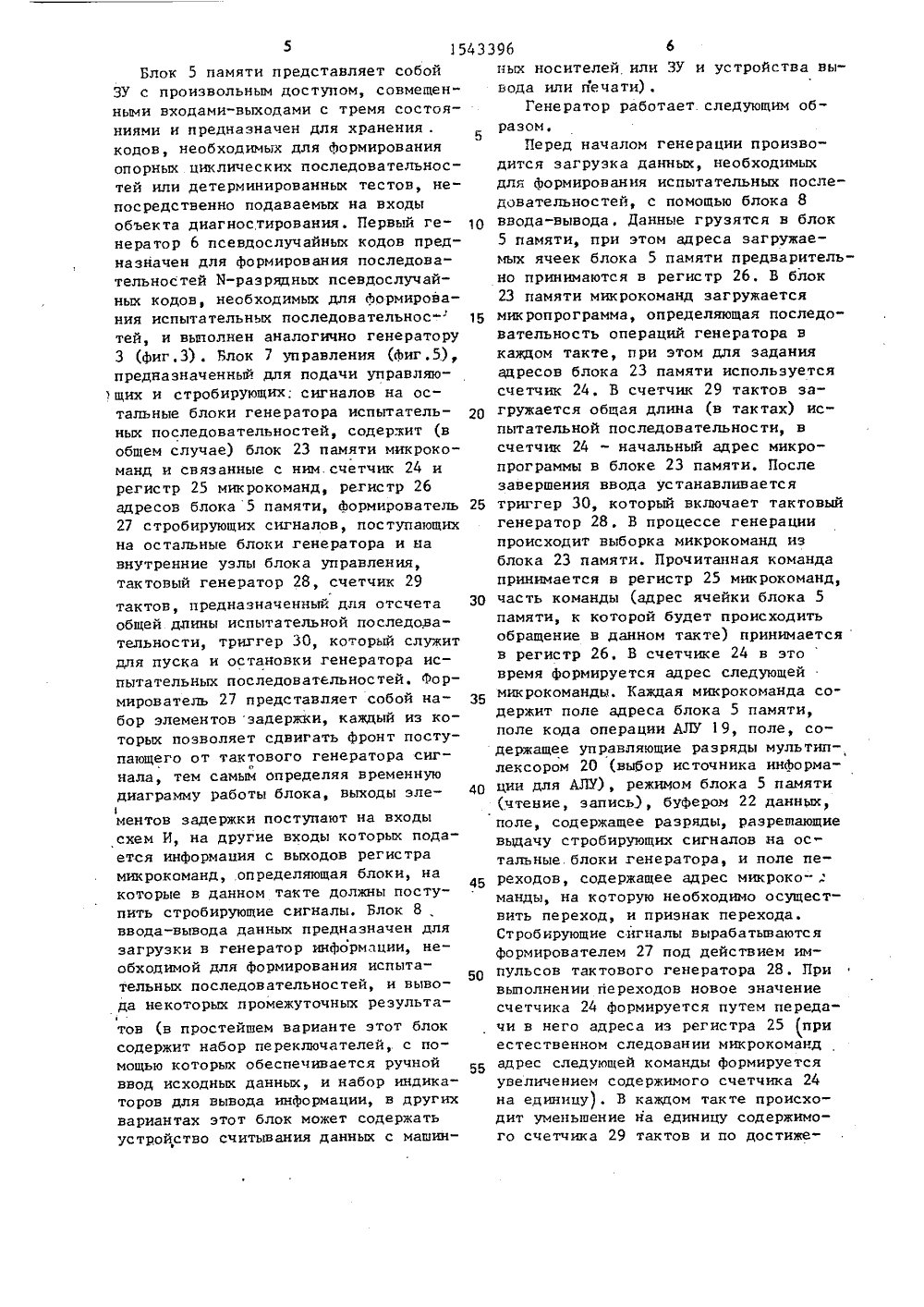

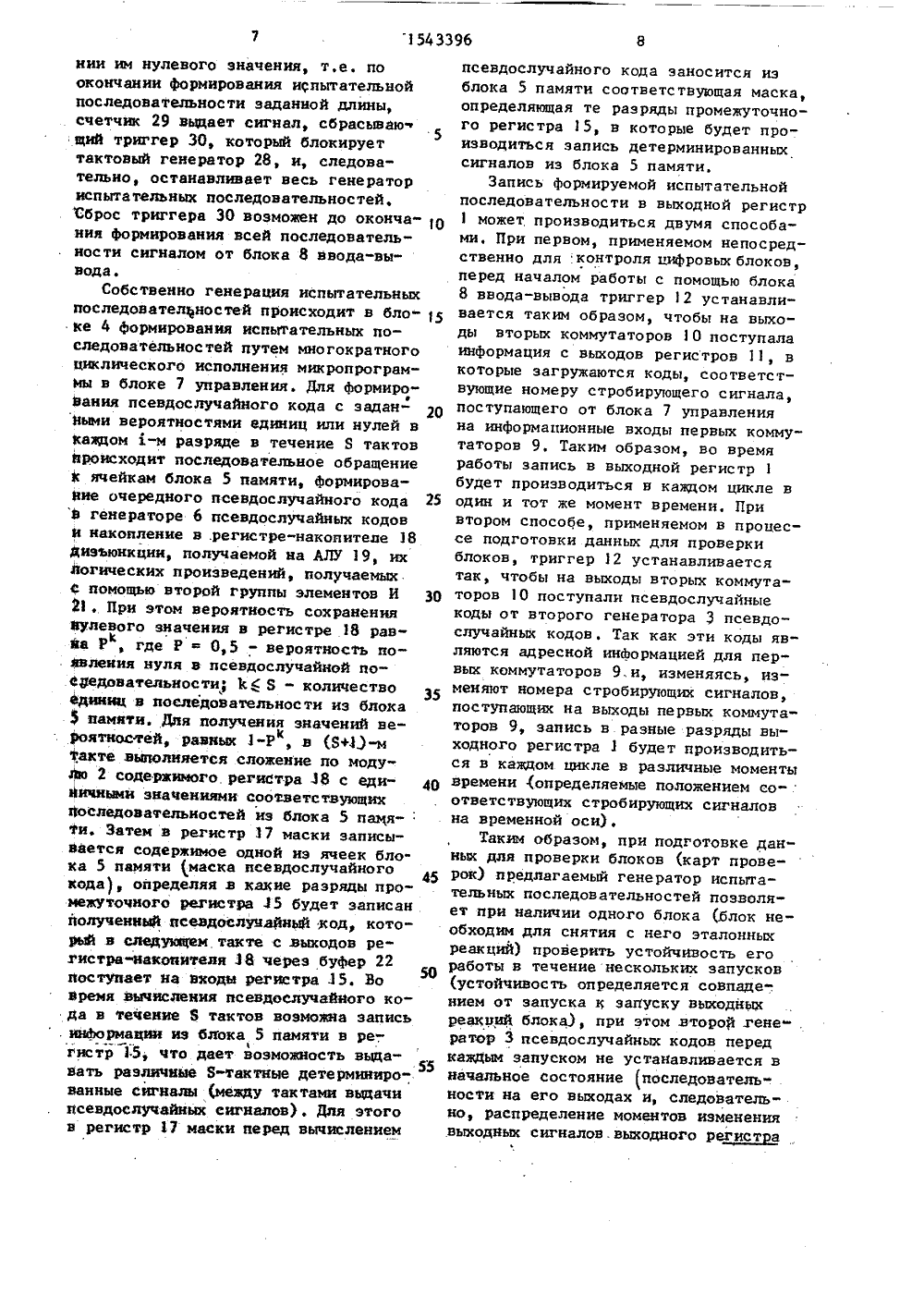

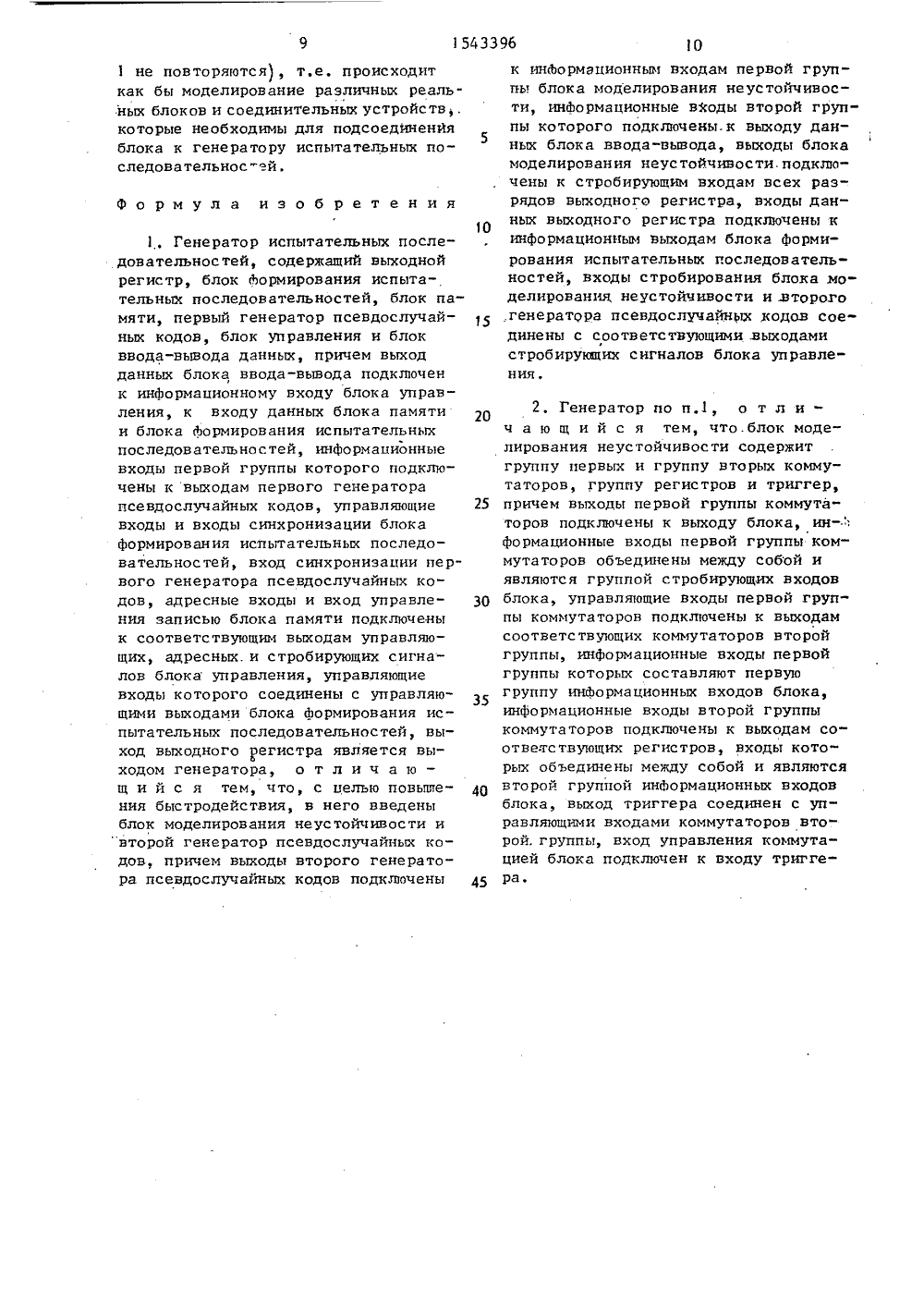

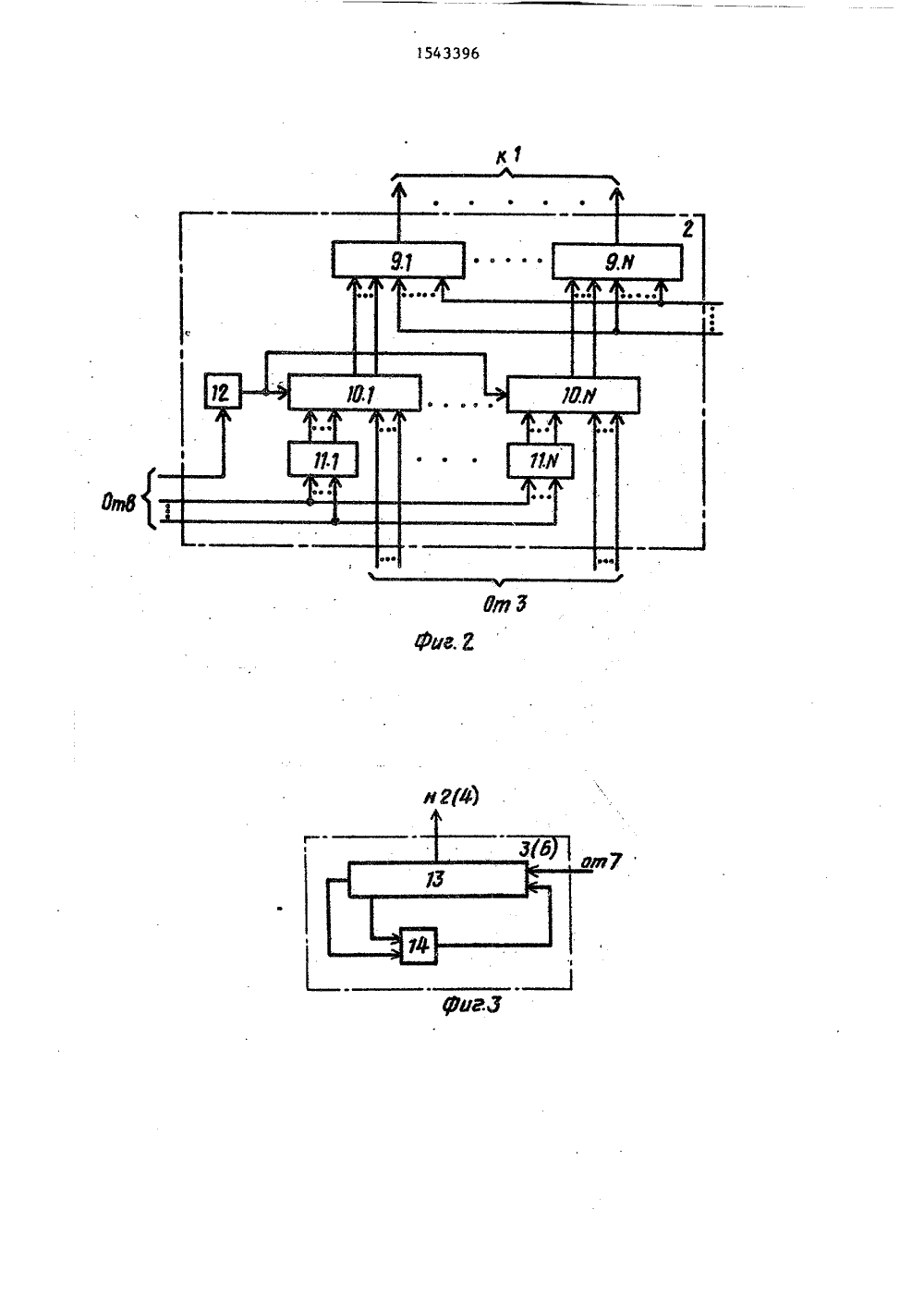

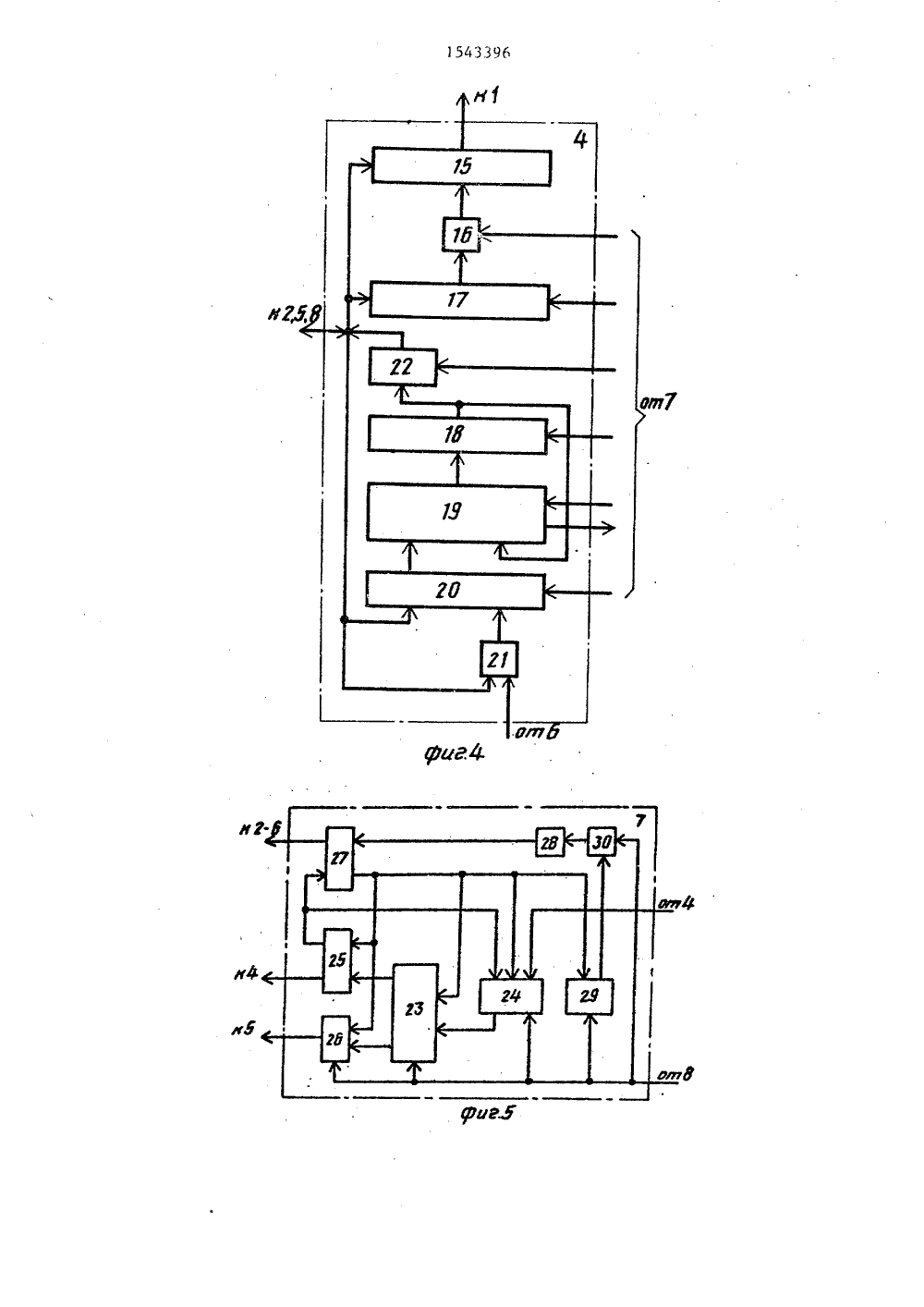

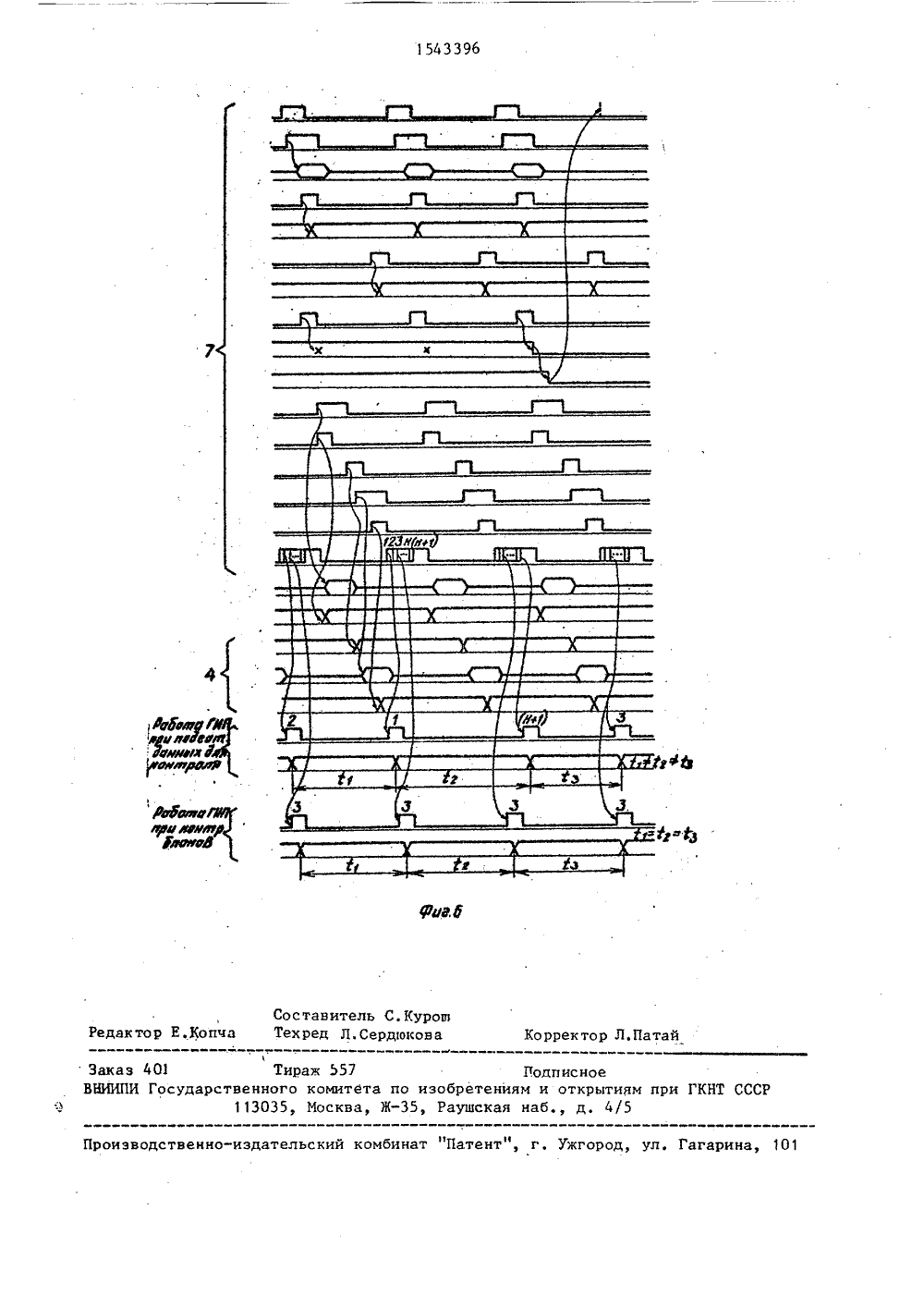

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 51)5 С 06 Р 1/О ОБРЕТЕН АВТОРСКОМУ ТЕПЬСТВ тель ери(5 (5 СССР 80. СР ыстро- содермодеой 3 и ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР 42915 99/24-2428, 07,8715.02.90. Бюл.6Киевский научно-исследоваи конструкторский институт пф ного оборудования(54) ГЕНЕРАТОР ИСПЫТАТЕЛЬНЫХ ПОСЛЕДОВАТЕЛЬНОС ТЕИ(57) Изобретение относится к средвам автоматического контроля и диностики цифровых объектов при ихизводстве и техническом обслуживаЦель изобретения - повьппение бдействия генератора. Генераторжит выходной регистр 1, блок 2лирования неустойчивости, втор гйервый 6 генераторы псевдослучайных кодов, блок 4 формирования испытательных последовательностей, блок 5 памяти, блок 7 управления и блок 8 ввода-вывода, В состав блока 2 входят группа первых и группа вторых коммутаторов, группа регистров и триггер, Испытательная последовательность, сформированная в блоке 4 из данных блока 5 и псевдослучайных ко;, дов генератора 6, под управлением сигналов, формируемых блоком 7, поступает на информационные входы регистра 1, на стробирующие входы которого могут поступать импульсы от блока 2 в каждом цикле в один и тот же или в различные моменты времени, определяемые генератором 3. Загрузка генератора и установка режимов происходит через блок 8. Поставленная цель достигается за счет введения блока моделирования неустойчивости и второго генератора псевдослучайных кодов. 1 з.п. ф-лы, 6 ил.Изобретение относится к вычислительной технике, в частности к средствам автоматической проверки цифровых объектов, и может быть использо-.вано для функционального контроляпроцессоров, контроллеров, запоминающих устройств и прочих блоков ЭВИ идругих средств цифровой техники приих производстве и техническом обслуживании.Цель изобретения - повьппение быстродействия,Введение блока моделирования неустойчивости и второго генератора псевдослучайных кодов позволяет производить запись сформированной испытательной последовательности .в выходной регистр (и, следовательно, выдачуее на объект диагностирования) в различные для каждого. выхода моментывремени в каждом цикле Формированияпоследовательности, что позволяет достаточно просто определить устойчивость работы объекта диагностирования 25при подаче на него этой последовательности (т,е, оценить качество испытательной последовательности) . Это, всвою очередь, дает возможность использовать в качестве испытательныхпоследовательностей наиболее эффективные (псевдослучайные) в максимальном объеме, что приводит к уменьшениювремени проверки цифровых блоков.На фиг,1 представлена структурная; схема предлагаемого генератора; наФиг.2 - схема блока моделирования не, устойчивости; на фиг,3 - схема генератора псевдослучайных кодов; нафиг,4 - схема блока Формирования испытательных последовательностей; наФиг.5 - схема блока управления; нафиг,б - временные диаграммы работы.В состав генератора испытательныхпоследовательностей входят выходнойрегистр 1, блок 2 моделирования неустойчивости, второй генератор 3псевдослучайных кодов, блок 4 Формирования испытательных последовательностей, блок 5 памяти, первый генератор б псевдослучайных кодов, блок7 управления и блок 8 ввода-вывода,Разрядность Н выходного регистра,блока формирования испытательных .последовательностей и всех узлов, входящих в него), блока моделированиянеустойчивости и блока памяти определяется необходимым числом одновремен"но генерируемых двоичных разрядов,каждый из которых соответствует одному выводу объекта диагностИрования.Блок 2 моделирования неустойчивости фиг.2) в совокупности с вторым генератором 3 псевдослучайных кодов предназначены для задания на стробирующие входы выходного регистра сигналов записи. Блок 2 содержит группы первых 9 и вторых 1 О коммутаторов, группу регистров 11 и триггер 12, На выходы первых коммутаторов 9 проходит один из сигналов, поступающих от устройства управления, в зависимости от сигналов на адресных входах этих коммутаторов, поступающих с выходов вторых коммутаторов 10, На входы вторых коммутаторов поступают или Фиксированные сигналы с регистров 11 или псевдослучайные с второго генератора 3 псевдослучайных кодов. Задание адреса на соответствующие входы вторых коммутаторов 10 осуществляет триггер 12. На фиг.3 показан пример выполнения генератора псевдослучайных кодов, в котором используется сдвиговый регистр 13 и сумматор 14 по модулю 2, На Фиг,4 представлен пример выполнения блока формирования испытательных последовательностей, содержащий промежуточный регистр 15, необходимый для временного хранения данных, поступающих затем на входы выходного регистра 1, первую группу элементов И 1 б, которая выполняет функцию поразрядного разрешения записи в промежуточный регистр, регистр 17 маски, разрешающий ипи запрещающий прием информации в промежуточный регистр, регистр-накопитель 18, служащий для запоминания результата операции арифметико-логического устройства 19 (АЛУ) - информация этого регистра является также одним из операндов АЛУ, АЛУ 19, служащее для преобразования данных и представляющее собой универсальное АЛУ, с полным набором логических (и арифметических) двухместных операций, группу мультиплексоров 20, необходимую для выбора источника информации, служащей вторым операндом АЛУ, вторую группу элементов И 21, которая служит для выполнения коньюнкции данных из блска 5 памяти и .псевдослучайного ко,да с первого генератора бпсевдослучайных кодов, однонаправленный буфер 22 данГных, предназначенный для выдачи данных из регистра-накопителя на внутреннюю магистраль данных генератора.5 1543Блок 5 памяти представляет собой ЗУ с произвольным доступом, совмещенными входами-выходами с тремя состояниями и предназначен для хранения . кодов, необходимых для формирования опорньк циклических последовательностей или детерминированных тестов, непосредственно подаваемых на входы объекта диагностирования. Первый генератор 6 псевдослучайных кодов предназначен для формирования последовательностей Н-разрядньк псевдослучайных кодов, необходимых для Формирования испытательных последовательнос тей, и выполнен аналогично генератору 3 (фиг,3), Блок 7 управления (фиг,5), предназначенный для подачи управляю) щих и стробирующих. сигналов на остальные блоки генератора испытатель ных последовательностей, содержит (в общем случае) блок 23 памяти микрокоманд и связанные с ним.счетчик 24 и регистр 25 микрокоманд, регистр 26 адресов блока 5 памяти, Формирователь 25 27 стробирующих сигналов, поступающих на остальные блоки генератора и на внутренние узлы блока управления, тактовый генератор 28, счетчик 29 тактов, предназначенный для отсчета 30 общей длины испытательной последовательности, триггер 30, который служит для пуска и остановки генератора испытательных последовательностей. Формирователь 27 представляет собой на- ЗБ бор элементов задержки, каждый из которьк позволяет сдвигать фронт поступающего от тактового генератора сигенала, тем самым определяя временную диаграмму работы блока, выходы злементов задержки поступают на входы схем И, на другие входы которых подается информация с выходов регистра микрокоманд, определяющая блоки, на45 которые в данном такте должны поступить стробирующие сигналы. Блок 8, ввода-вывода данных предназначен для загрузки в генератор информации, необхоцимой для формирования испытательных последовательностей, и выво 50 да некоторых промежуточных результатов (в простейшем варианте этот блок содержит набор переключателей,. с помощью которых обеспечивается ручной ввод исходньк данных, и набор индикаторов для вывода информации, в других вариантах этот блок может содержать устройство считывания данных с машин 396 6ных носителей или ЗУ и устройства вывода или иечати) .Генератор работает. следующим образом,Перед началом генерации производится загрузка данных, необходимыхдля Формирования испытательных последовательностей, с помощью блока 8ввода-вывода, Данные грузятся в блок5 памяти, при этом адреса загружаемых ячеек блока 5 памяти предварительно принимаются в регистр 26. В блок23 памяти микрокоманд загружаетсямикропрограмма, определяющая последовательность операций генератора вкаждом такте, при этом для заданияадресов блока 23 памяти используетсясчетчик 24. В счетчик 29 тактов загружается общая длина (в тактах) испытательной последовательности, всчетчик 24 - начальный адрес микропрограммы в блоке 23 памяти, Послезавершения ввода устанавливаетсятриггер 30, который включает тактовыйгенератор 28 . В процессе генерациипроисходит выборка микрокоманд изблока 23 памяти. Прочитанная командапринимается в регистр 25 микрокоманд,часть команды (адрес ячейки блока 5памяти, к которой будет происходитьобращение в данном такте) принимаетсяв регистр 26. В счетчике 24 в этовремя формируется адрес следующеймикрокоманды. Каждая микрокоманда содержит поле адреса блока 5 памяти,поле кода операции АЛУ 19, поле, содержащее управляющие разряды мультиплексором 20 (выбор источника информации для АЛУ), режимом блока 5 памяти(чтение, запись), буфером 22 данныхполе, содержащее разряды, разрешающиевьдачу стробирующих сигналов на остальные блоки генератора, и поле переходов, содержащее адрес микроко-;манды, на которую необходимо осуществить переход, и признак перехода.Стробирующие сигналы вырабатываютсяформирователем 27 под действием импульсов тактового генератора 28 . Привыполнении переходов новое значениесчетчика 24 формируется путем передачи в него адреса из регистра 25 приестественном следовании микрокомандадрес следующей команды формируетсяувеличением содержимого счетчика 24на единицу). В каждом такте происходит уменьшение на единицу содержимого счетчика 29 тактов и по достиже 1543396нии им нулевого значения, т.е. поокончании формирования испытательнойпоследовательности заданной длины,счетчик 29 выдает сигнал, сбрасывающий триггер 30, который блокирует5тактовый генератор 28, и, следовательно, останавливает весь генераториспытательных последовательностей,Сброс триггера 30 возможен до окончания формирования всей последовательности сигналом от блока 8 ввода-вывода.Собственно генерация испытательныхпоследовательностей происходит в блоке 4 формирования испытательных носледовательностей путем многократногоциклического исполнения микропрограммы в блоке 7 управления. Для формирования псевдослучайного кода с заданйыми вероятностями единиц ипи нулей вкаждом 1-м разряде в течение Я тактовироисходит последовательное обращениек ячейкам блока 5 памяти, формирование очередного псевдослучайного кода 25Э генераторе 6 псевдослучайных кодови накопление в .регистре-накопителе 18Дизъюнкции, получаемой на АЛУ 19, ихЙогических произведений, получаемыхФ помощью второй группы элементов И 3021, При этом вероятность сохраненияВулевого значения в регистре 18 ранкжв Р , где Р вв 0,5 - вероятность ноелеиия нуля в псевдослучайной поФ 3 едовательности; Е С 8 - количествоЕдиинц в последовательности из блоха3 памяти. Для получения значений вероятностей, равиьщ 1-Р", в (8+13-иФакте выполняется сложение по модулю 2 содержимого. регистра 16 с едиМичиыми значениями соответствующихпоследовательностей из блока 5 памяти, Затем в регистр 17 маски записывается содержимое одной иэ ячеек бло"ка 5 памяти маска псевдослучайного 45кода), определяя в хвхне разряды промежуточного регистра 15 будет записанполученный асеэдоелуив 9 ный ход, которьй в следующем такте с выходов регистра-иакоаителя 18 через буфер 22поступает на входы регистра 15. Вовремя вычисления псевдослучайного кода в течение 8 тактов возможна запись. информации из блока 5 памяти в ре-,гистр 15, что дает возможность вьдавать различные 3-тактные детермиииро"ванные сигналы (между тактами выдачипсевдослучайных сигналов), Для этогов регистр 17 маски перед вычислением псевдослучайного кода заносится из блока 5 памяти соответствующая маска, определяющая те разряды промежуточного регистра 15, в которые будет производиться запись детерминированных сигналов из блока 5 памяти.Запись формируемой испытательной последовательности в выходной регистрможет производиться двумя способамн, При первом, применяемом непосредственно для контроля цифровых блоков, перед началом работы с помощью блока 8 ввода-вывода триггер 12 устанавливается таким образом, чтобы на выходы вторых коммутаторов 1 О поступала информация с выходов регистров 11, в которые загружаются коды, соответствующие номеру стробирующего сигнала, поступающего от блока 7 управления на информационные входы первых коммутаторов 9. Таким образом, во время работы запись в выходной регистр 1 будет проиэводиться в каждом цикле в один и тот же момент времени. Прн втором способе, применяемом в процессе подготовки данных для проверки блоков, триггер 12 устанавливается твк, чтобы на выходы вторых коммутаторов 10 поступали псевдослучайные коды от второго генератора 3 псевдослучайных кодов . Так как эти коды являются адресной информацией для первых коммутаторов 9,и, изменяясь, изменяют номера стробнрующих сигналов, поступающих на выходы первых коммутаторов 9, запись в разные разряды выходного регистра 1 будет производиться в каждом цикле в различные моменты времени (определяемые положением со-ответствующих стробирующнх сигналов на временной оси).Таким образом, при подготовке данных для проверки блоков (карт проверок) предлагаемый генератор испытательных последовательностей позволяет при наличии одного блока (блок не" обходим для снятия с него эталонных реакций) проверить устойчивость его работы в течение нескольких запусков (устойчивость определяется совпвде". нием от запуска к запуску выходных ревкпи блока), при этом второЯ гене- . ратор 3 псевдослучайных кодов перед каждым запуском не устанавливается в начальное состояние (последователь" ности на его выходах и, следовательно, распределение моментов изменения выволньн сигналов. внволвого ввгнстов1 не повторяются), т,е. происходит как бы моделирование различных реальных блоков и соединительных устройств, . которые необходимы для подсоединения блока к генератору испытательных по 5 следовательнос-зй. Формула изобретения101, Генератор испытательных последовательностей, содержащий выходной регистр, блок формирования испытательных последовательностей, блок памяти, первый генератор псевдослучайных кодов, блок управления и блок ввода-вывода данных, причем выход данных блока ввода-вывода подключен к информационному входу блока управления, к входу данных блока памяти и блока формирования испытательных последовательностей, инФормационные входы первой группы которого подключены к выходам первого генератора псевдослучайных кодов, управляющие 25 входы и входы синхронизации блока формирования испытательных последовательностей, вход синхронизации первого генератора псевдослучайных кодов, адресные входы и вход управле ния записью блока памяти подключены к соответствующим выходам управляющих, адресных.и стробирующих сигналов блока управления, управляющие входы которого соединены с управляющими выходами блока формирования испытательных последовательностей, выход выходного регистра является выходом генератора, о т л и ч а ю - щ и й с я тем, что, с целью повьппе ния быстродействия, в него введены блок моделирования неустойчивости и "второй генератор псевдослучайных кодов, причем выходы второго генератора псевдослучайных кодов подключены 45 к информационным входам первой группь 1 блока моделирования неустойчивости, информационные входы второй группы которого подключены.к выходу даннь 1 х блока ввода-вывода, выходы блокамоделирования неустойчивости. подключены к стробирующим входам всех разрядов выходного регистра, входы данных выходного регистра подключены кинформационным выходам блока формирования испытательных госледовательностей, входы стробирования блока моделирования, неустойчивости и .второгогенератора псевдослучайных, кодов соединены с соответствующими .выходамистробирующих сигналов блока управления,2, Генератор по п.1, о т л ич а ю щ и й с я тем, что.блок моделирования неустойчивости содержит группу первых и группу вторых коммутаторов, группу регистров и триггер, причем выходы первой группы коммутаторов подключены к выходу блока, ин-: формационные входы первой группы коммутаторов объединены между собой и являются группой стробирующих входов блока, управляющие входы первой группы коммутаторов подключены к выходам соответствующих коммутаторов второй группы, информационные входы первой группы которых составляют первую группу информационных входов блока, информационные входы второй группы коммутаторов подключены к выходам соответствующих регистров, входы которых объединены между собой и являются второй группой информационных входов блока, выход триггера соединен с управляющжи входами коммутаторов второй,группы, вход управления коммутацией блока подключен к входу триггера..Патаи Зака НИИП иям при ГКНТ ССС я наб роиэводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1

СмотретьЗаявка

4291599, 28.07.1987

КИЕВСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ И КОНСТРУКТОРСКИЙ ИНСТИТУТ ПЕРИФЕРИЙНОГО ОБОРУДОВАНИЯ

КАДАНСКИЙ АЛЕКСАНДР АБРАМОВИЧ, КОРОЛЕВ ВЛАДИМИР НИКОЛАЕВИЧ, РУККАС ОЛЕГ ДМИТРИЕВИЧ, СИДОРЕНКО ВАСИЛИЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генератор, испытательных, последовательностей

Опубликовано: 15.02.1990

Код ссылки

<a href="https://patents.su/8-1543396-generator-ispytatelnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор испытательных последовательностей</a>

Предыдущий патент: Устройство регулирования -фазного напряжения

Следующий патент: Генератор последовательности избыточной системы счисления

Случайный патент: Ламельный контакт