Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1354192

Автор: Самошин

Текст

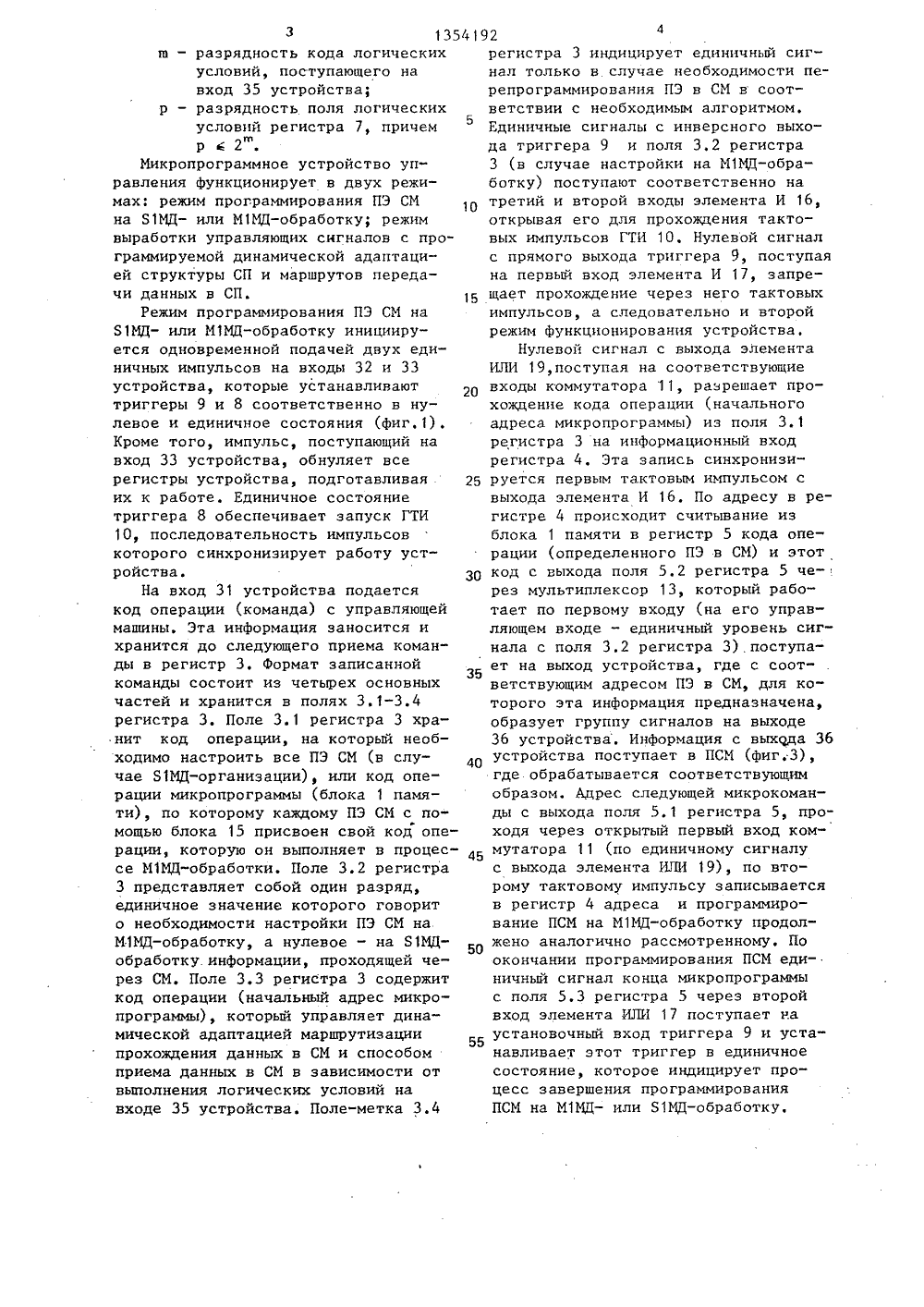

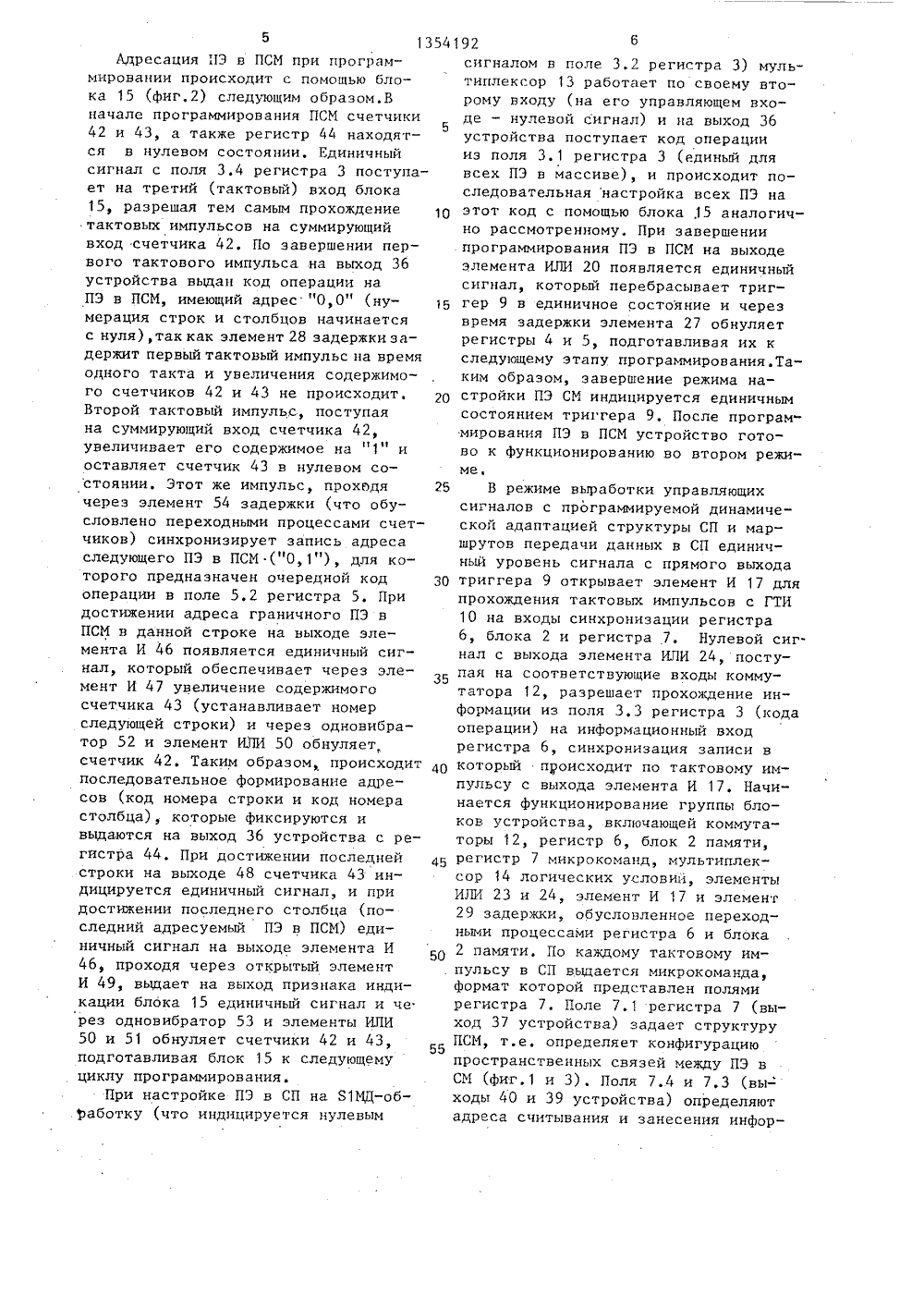

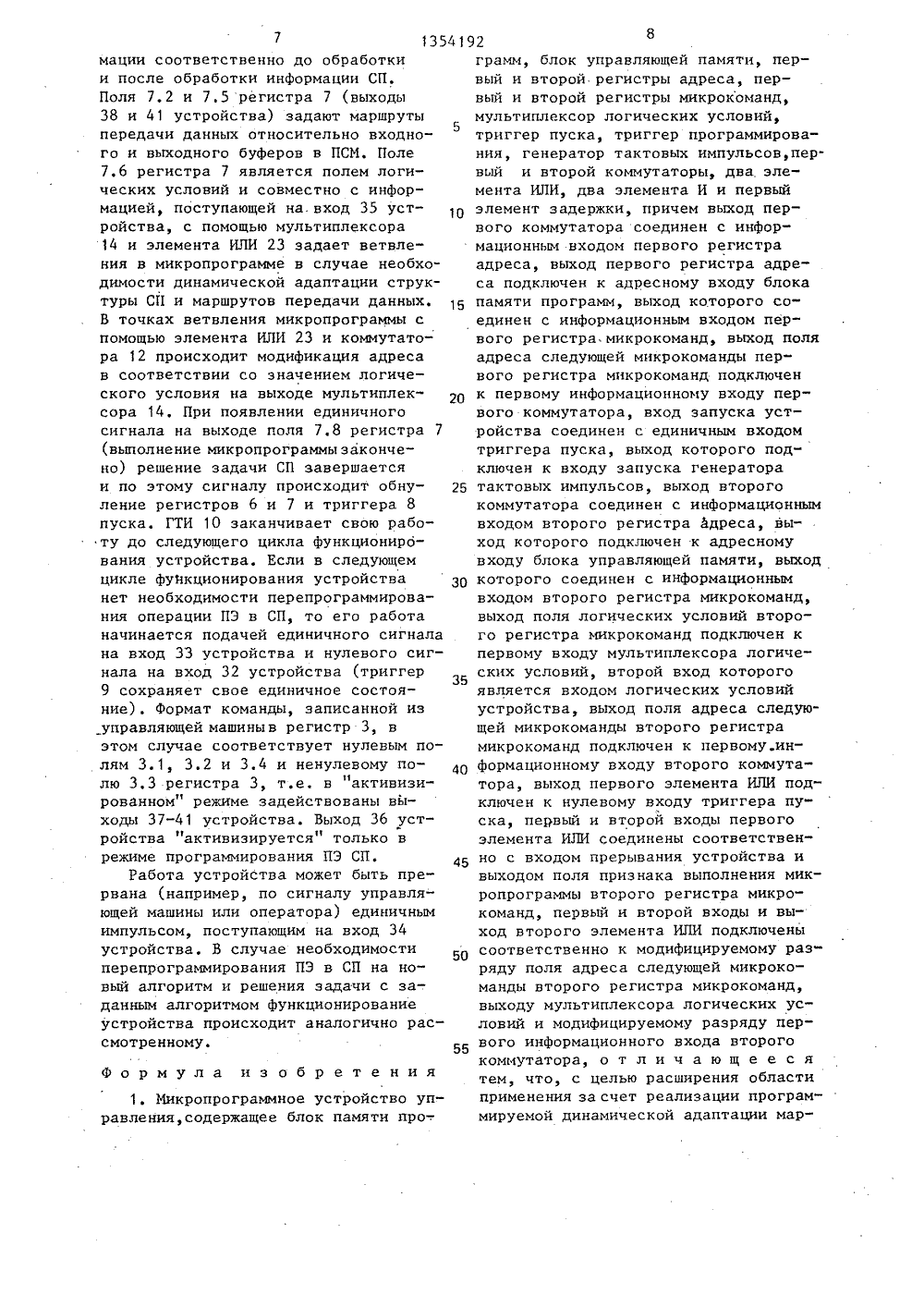

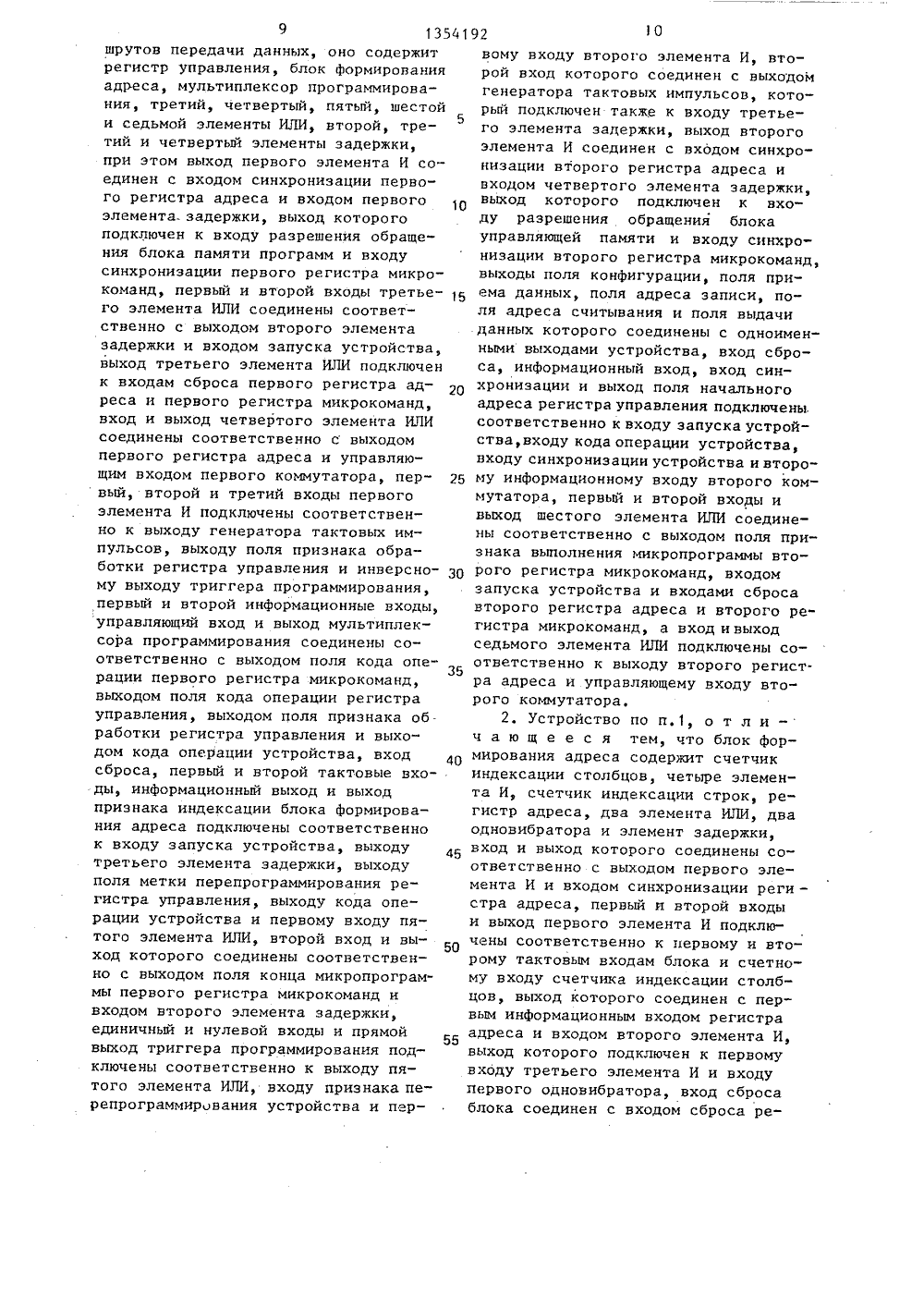

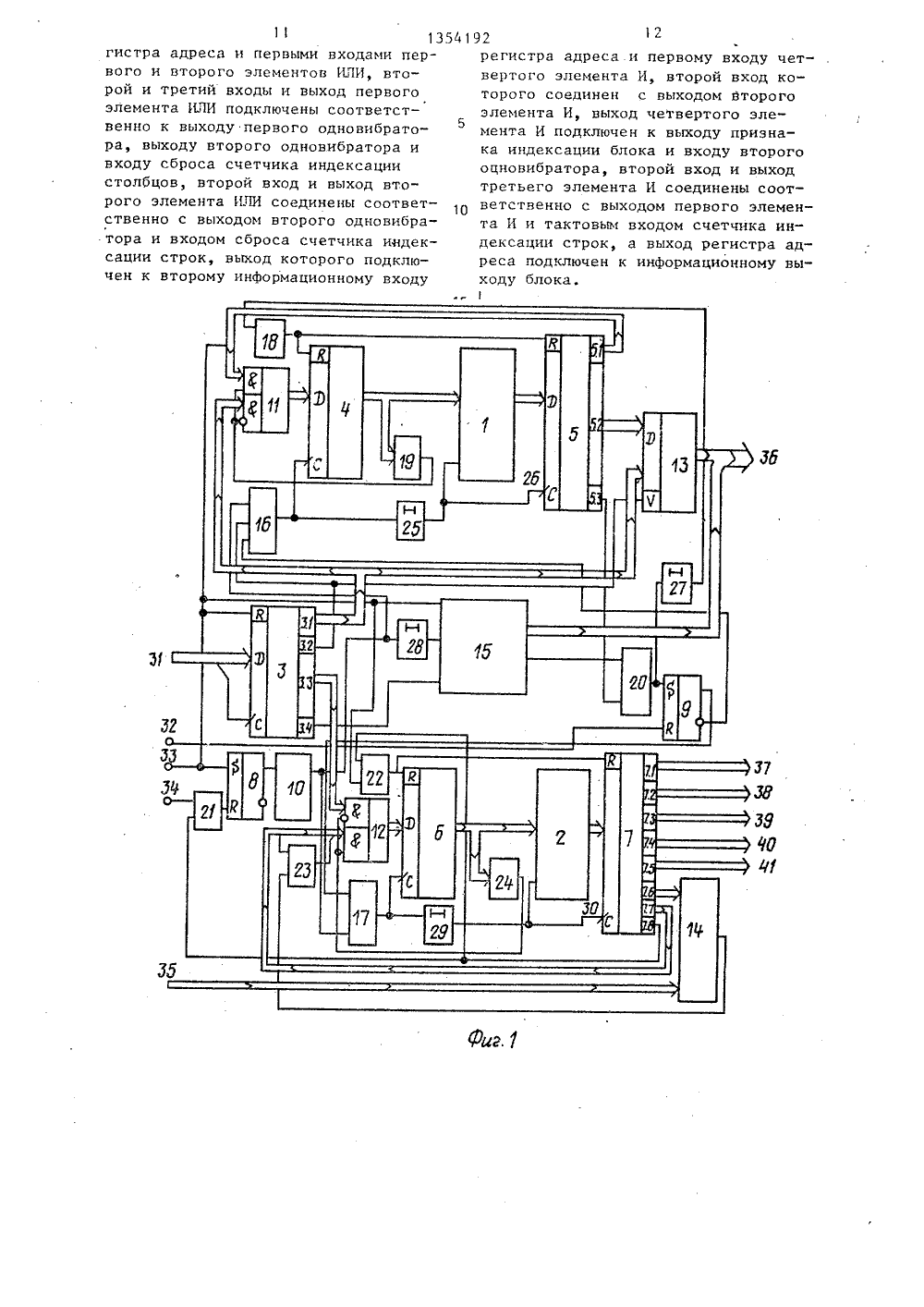

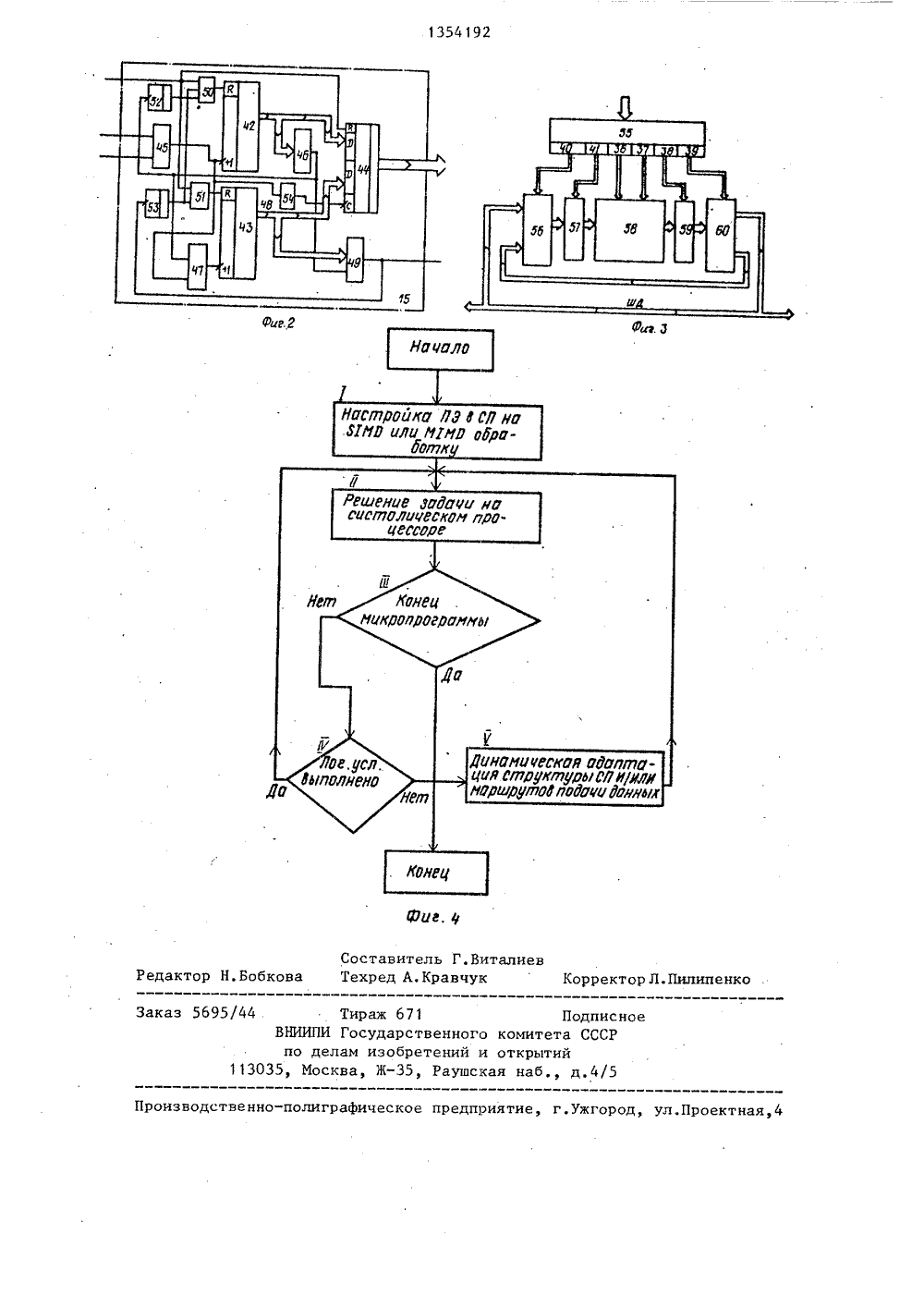

135 1Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления систолических, матричных,г конвейерных и других мультипроцессорных систем, использующих параллельную обработку информации..Цель изобретения - расширение области применения устройства за счет реализации программируемой динамической адаптации маршрутов передачи данных.На фиг.1 приведена функциональная схема устройства; на фиг.2 - функцио нальная схема блока Формирования адреса; на фиг.З - устройство в составе систолического процессора; на Фиг.4 - блок-схема алгоритма Функционирования устройства. 20Микропрограммное устройство управления (Фиг,1) содержит блок 1 памяти программ, блок 2 управляющей памяти, регистр 3 управления, первый регистр 4 адреса, первый регистр 5бмикрокоманд, второй регистр 6 адреса, второй регистр 7 микрокомандтриггер8 пуска ВБ-типа, триггер 9 программирования 28-типа, генератор 10 тактовых импульсов (ГТИ), первый 11 и 30 второй 12 коммутаторы, первый мультинлексор 13, мультиплексор 14 логических условий, блок 15 Формирования адреса, первый 16 и второй 17 элементы И, первый 18, второй 19, третий 20, четвертый 21, пятый 22 шестой23 и седьмой 24 элементы И 31 И, первый элемент 25 задержки, синхровход26 регистра 5, второй 2, третий 28 и четвертый 29 элементы задержки.Так же показаны синхровход 30 регистра 7, вход 31 кода операции, вход 32 признака перепрограммирования вход 33 запуска, вход 34 прерывания и вход 35 логических условий устройства, выход 36 кода операции, выход 37 по. ля конфигурации, выход 38 поля приема данных, выход 39 поля адреса занесения информации, выход 40 поля адреса считывания, выход 41 поля вьадачи данных устройства.Блок 15 формирования адреса (Фиг.2) содержит счетчик 42 индексации столбцов, счетчик 43 индексации строк,регистр 44 адреса, первый 45, второй46 и третий 47 элементы И, счетчик 43 имеет выход 48. Кроме того, блок 15 содержит четвертый элемент И 49, первый 50 и второй 51 элементы ИЛИ,92 2первый 52 и второй 53 одновибраторыпо фронту импульса с задержкой и элемент 54 задержки,Микропрограммное устройство управления на фиг.3 показано в структуресистолического процессора, Систолический процессор в общем случае содержит микропрограммное устройство 55управления, входной буфер 56, входной коммутатор 57 (К 1), программируемую систолическую матрицу 58(ПСМ), выхоцной коммутатор 59 (К 2)и выходной буфер 60, которые осуществляют связь с управляющей машиной через шину данных (ЩЦ), Это позволяетдобиться гибкости в функционировании сис.толического процессора и получении результата вычислений в программируемой систолической матрице (СМ),в которой возможно как программирование каждого процессорного элемента(ПЭ) в массиве, так и конфигурациисвязей между ними (маршрутов прохождения данных), что позволяет использовать в устройстве преимущества программируемой динамической адаптации:гибкость, высокое быстродействие, относительную универсальность при решении определенного класса задач,Функционирование устройства основано на двух основных режимах: настройка ПЭ в систолическом процессоре (СП) на 81 аЯ- или М 1 МД-обработку (блок 1); решения задачи на СПс использованием динамической адаптации структуры процессора и маршрутов передачи данных в процессоре(блоки 11-7),Мультиплексор 14 логических усОловий предназначен для реализациилогической функцииР- Я х; у;1=1где х - значейие ).-го логического1условия на входе 35 устройства;у; =1 сс5если в соответствующемразряде поля 7,6 регистра 7записана "1";( Г если в соответствующем разряде поля 7.6 регис ра 7 записан "0",5419 10 20 25 30 35 40 45 50 55 3 13в - разрядность кода логическихусловий, поступающего навход 35 устройства;р - разрядность поля логическихусловий регистра 7, причемр й 2Микропрограммное устройство управления функционирует в двух режимах: режим программирования ПЭ СМна 81 МД- или М 1 МД-обработку; режимвыработки управляющих сигналов с программируемой динамической адаптацией структуры СП и маршрутов передачи данных в СП.Режим программирования ПЭ СМ на31 МД- или М 1 МД-обработку инициируется одновременной подачей двух единичных импульсов на входы 32 и 33устройства, которые устанавливаюттриггеры 9 и 8 соответственно в нулевое и единичное состояния (фиг,1),Кроме того, импульс, поступающий навход 33 устройства, обнуляет всерегистры устройства, подготавливаяих к работе. Единичное состояниетриггера 8 обеспечивает запуск ГТИ10, последовательность импульсовкоторого синхронизирует работу устройства,На вход 31 устройства подаетсякод операции (команда) с управляющеймашины, Эта информация заносится ихранится до следующего приема команды в регистр 3. Формат записаннойкоманды состоит из четырех основныхчастей и хранится в полях 3.1-3,4регистра 3. Поле 3.1 регистра 3 хранит код операции, на который необходимо настроить все ПЭ СМ (в случае 31 МД-организации), или код операции микропрограммы (блока 1 памяти), по которому каждому ПЭ СМ с помощью блока 15 присвоен свой код операции, которую он выполняет в процессе М 1 МД-обработки. Поле 3.2 регистра3 представляет собой один разряд,единичное значение которого говорито необходимости настройки ПЭ СМ наМ 1 МД-обработку, а нулевое - на 81 МДобработку. информации, проходящей через СМ. Поле 3.3 регистра 3 содержиткод операции (начальный адрес микропрограммы), который управляет динамической адаптацией маршрутизациипрохождения данных в СМ и способомприема данных в СМ в зависимости отвыполнения логических условий навходе 35 устройства. Поле-метка 3,4 24регистра 3 индицирует единичный сигнал только в случае необходимости перепрограммирования ПЭ в СМ в соответствии с необходимым алгоритмом, Единичные сигналы с инверсного выхода триггера 9 и поля 3,2 регистра 3 (в случае настройки на М 1 МД-обработку) поступают соответственно на третий и второй входы элемента И 16, открывая его для прохождения тактовых импульсов ГТИ 10, Нулевой сигнал с прямого выхода триггера 9, поступая на первый вход элемента И 17, запрещает прохождение через него тактовых импульсов, а следовательно и второй режим функционирования устройстваНулевой сигнал с выхода элемента ИЛИ 19,поступая на соответствующие входы коммутатора 11, разрешает прохождение кода операции (начального адреса микропрограммы) из поля 3.1 регистра 3 на информационный вход регистра 4. Эта запись синхронизируется первым тактовым импульсом с выхода элемента И 16. По адресу в регистре 4 происходит считывание из блока 1 памяти в регистр 5 кода операции (определенного ПЭ в СМ) и этот код с выхода поля 5.2 регистра 5 через мультиплексор 13, который работает по первому входу (на его управляющем входе - единичный уровень сигнала с поля 3,2 регистра 3).поступает на выход устройства, где с соответствующим адресом ПЭ в СМ, для которого эта информация предназначена, образует группу сигналов на выходе 36 устройства, Информация с выхода 36 устройства поступает в ПСМ (фиг;3), где обрабатывается соответствующим образом. Адрес следующей микрокоманды с выхода поля 5.1 регистра 5, проходя через открытый первый вход коммутатора 11 (по единичному сигналу с выхода элемента ИЛИ 19), по второму тактовому импульсу записывается в регистр 4 адреса и программирование ПСМ на М 1 МД-обработку продолжено аналогично рассмотренному. По окончании программирования ПСМ единичный сигнал конца микропрограммы с поля 5,3 регистра 5 через второй вход элемента ИЛИ 17 поступает на установочный вход триггера 9 и устанавливает этот триггер в единичное состояние, которое индицирует процесс завершения программирования ПСМ на М 1 МП- или 51 МД-обработку,5 10 15 20 25 30 35 40 45 50 55 5 13Адресация ПЭ в ПСМ при программировании происходит с помощью блока 15 (фиг 2) следующим образом.В начале программирования ПСМ счетчики 42 и 43, а также регистр 44 находятся в нулевом состоянии, Единичный сигнал с поля 3.4 регистра 3 поступает на третий (тактовый) вход блока 15, разрешая тем самым прохождение тактовых импульсов на суммирующий вход счетчика 42. По завершении первого тактового импульса на выход 36 устройства выдан код операции на ПЭ в ПСМ, имеющий адрес "0,0" (нумерация строк и столбцов начинается с нуля),так как элемент 28 задержки задержит первый тактовый импульс на время одного такта и увеличения содержимого счетчиков 42 и 43 не происходит. Второй тактовый импульс, поступая на суммирующий вход счетчика 42, увеличивает его содержимое на "1" и оставляет счетчик 43 в нулевом состоянии, Этот же импульс, проходя через элемент 54 задержки (что обусловлено переходными процессами счетчиков) синхронизирует запись адреса следующего ПЭ в ПСМ ("0,1"), для которого предназначен очередной код операции в поле 5.2 регистра 5. При достижении адреса граничного ПЭ в ПСМ в данной строке на выходе элемента И 46 появляется единичный сигнал, который обеспечивает через элемент И 47 увеличение содержимого счетчика 43 (устанавливает номер следующей строки) и через одновибратор 52 и элемент ИЛИ 50 обнуляет, счетчик 42, Таким образом, происходит последовательное формирование адресов (код номера строки и код номера столбца), которые фиксируются и выдаются на выход 36 устройства с регистра 44. При достижении последней строки на выходе 48 счетчика 43 индицируется единичный сигнал и при достижении последнего столбца (последний адресуемый ПЭ в ПСМ) единичный сигнал на выходе элемента И 46, проходя через открытый элемент И 49, выдает на выход признака индикации блока 15 единичный сигнал и че рез одновибратор 53 и элементы ИЛИ 50 и 51 обнуляет счетчики 42 и 43, подготавливая блок 15 к следующему циклу программирования.При настройке ПЭ в СП на 81 Щ-обРаботку (что индицируется нулевым 54192б сигналом в поле 3,2 регистра 3) мультиплексор 13 работает по своему второму входу (на его управляющем входе - нулевой сигнал) и на выход 36 устройства поступает код операции из поля 3,1 регистра 3 (единый для всех ПЭ в массиве), и происходит последовательная настройка всех ПЭ на этот код с помощью блока .15 аналогично рассмотренному, При завершении программирования ПЭ в ПСМ на выходе элемента ИЛИ 20 появляется единичный сигнал, который перебрасывает триггер 9 в единичное состояние и через время задержки элемента 27 обнуляет регистры 4 и 5, подготавливая их к следующему этапу программирования.Таким образом, завершение режима настройки ПЭ СМ индицируется единичным состоянием триггера 9. После программирования ПЭ в ПСМ устройство готово к функционированию во втором режимеВ режиме выработки управляющих сигналов с программируемой динамической адаптацией структуры СП и маршрутов передачи данных в СП единичный уровень сигнала с прямого выхода триггера 9 открывает элемент И 17 для прохождения тактовых импульсов с ГТИ 10 на входы синхронизации регистра 6, блока 2 и регистра 7. Нулевой сиг. нал с выхода элемента ИЛИ 24, поступая на соответствующие входы коммутатора 12, разрешает прохождение информации из поля 3.3 регистра 3 (кода операции) на информационный вход регистра 6, синхронизация записи в который происходит по тактовому импульсу с выхода элемента И 17. Начинается функционирование группы блоков устройства, включающей коммутаторы 12, регистр 6, блок 2 памяти,регистр 7 микрокоманд, мультиплексор 14 логических условий, элементыИЛИ 23 и 24, элемент И 17 и элемент29 задержки, обусловленное переходными процессами регистра 6 и блока2 памяти, По каждому тактовому импульсу в СП выдается микрокоманда,формат которой представлен полямирегистра 7, Поле 7,1 регистра 7 (выход 37 устройства) задает структуру ПСМ, т.е, определяет конфигурациюпространственных связей между ПЭ вСМ (фиг.1 и 3). Поля 74 и 7.3 (вы-ходы 40 и 39 устройства) определяютадреса считывания и занесения инфор30 7 1354 19 мации соответственно до обработки и после обработки информации СП. Ноля 7.2 и 7.5 регистра 7 (выходы 38 и 41 устройства) задают маршруты передачи данных относительно входно 5 го и выходного буферов в ПСМ. Поле 7,6 регистра 7 является полем логических условий и совместно с информацией, поступающей на. вход 35 устройства, с помощью мультиплексора 14 и элемента ИЛИ 23 задает ветвления в микропрограмме в случае необходимости динамической адаптации структуры СП и маршрутов передачи данных, В точках ветвления микропрограммы с помощью элемента ИЛИ 23 и коммутатора 12 происходит модификация адреса в соответствии со значением логического условия на выходе мультиплексора 14. При появлении единичного сигнала на выходе поля 7,8 регистра 7 (выполнение микропрограммы закончено) решение задачи СП завершается и по этому сигналу происходит обну ление регистров 6 и 7 и триггера 8 пуска. ГТИ 10 заканчивает свою работу до следующего цикла функционирбвания устройства. Если в следующем цикле функционирования устройства нет необходимости перепрограммирования операции ПЭ в СП, то его работа начинается подачей единичного сигнала на вход 33 устройства и нулевого сигнала на вход 32 устройства (триггер 9 сохраняет свое единичное состояние), Формат команды, записанной из управляющей машины в регистр 3, в этом случае соответствует нулевым полям 3.1, 3.2 и 3.4 и ненулевому по лю 3.3 регистра 3, т.е, в "активизированном режиме задействованы выходы 37-41 устройства, Выход 36 устройства "активизируется" только в режиме программирования ПЭ СП. 45Работа устройства может быть прервана (например, по сигналу управляющей машины или оператора) единичным импульсом, поступающим на вход 34 устройства. В случае необходимости перепрограммирования ПЭ в СП на новый алгоритм и решения задачи с заданным алгоритмом функционирование устройства происходит аналогично рассмотренному. 55 Формула изобретения 1. Микропрограммное устройство управления,содержащее блок памяти про-. 28грамм, блок управляющей памяти, первый и второй регистры адреса, первый и второй регистры микрокоманд, мультиплексор логических условий, триггер пуска, триггер программирования, генератор тактовых импульсов,первый и второй коммутаторы, два элемента ИЛИ, два элемента И и первый элемент задержки, причем выход первого коммутатора соединен с информационным входом первого регистра адреса, выход первого регистра адреса подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом первого регистра микрокоманд, выход поля адреса следующей микрокоманды первого регистра микрокоманд подключен к первому информационному входу первого коммутатора, вход запуска устройства соединен с единичным входом триггера пуска, выход которого подключен к входу запуска генератора тактовых импульсов, выход второго коммутатора соединен с информационным входом второго регистра Адреса, выход которого подключен к адресному входу блока управляющей памяти, выход которого соединен с информационным входом второго регистра микрокоманд, выход поля логических условий второго регистра микрокоманд подключен к первому входу мультиплексора логических условий, второй вход которого является входом логических условий устройства, выход поля адреса следующей микрокоманды второго регистра микрокоманд подключен к первому информационному входу второго коммутатора, выход первого элемента ИЛИ подключен к нулевому входу триггера пуска, первый и второй входы первого элемента ИЛИ соединены соответственно с входом прерывания устройства и выходом поля признака выполнения микропрограммы второго регистра микро- команд, первый и второй входы и выход второго элемента ИЛИ подключены соответственно к модифицируемому разряду поля адреса следующей микрокоманды второго регистра микрокоманд, выходу мультиплексора логических условий и модифицируемому разряду первого информационного входа второго коммутатора, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет реализации программируемой динамической адаптации мар 13541925 10 15 20 25 30 35 40 45 50 55 шрутов передачи данных, оно содержит регистр управления, блок формирования адреса, мультиплексор программирования, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, второй, третий и четвертый элементы задержки, при этом выход первого элемента И соединен с входом синхронизации первого регистра адреса и входом первого элемента, задержки, выход которого подключен к входу разрешения обращения блока памяти программ и входу синхронизации первого регистра микро- команд, первый и второй входы третьего элемента ИЛИ соединены соответственно с выходом второго элемента задержки и входом запуска устройства, выход третьего элемента ИЛИ подключен к входам сброса первого регистра адреса и первого регистра микрокоманд, вход и выход четвертого элемента ИЛИ соединены соответственно с выходом первого регистра адреса и управляющим входом первого коммутатора, пер вый, второй и третий входы первого элемента И подключены соответственно к выходу генератора тактовых импульсов, выходу поля признака обработки регистра управления и инверсному выходу триггера программирования, первый и второй информационные входы, управляющий вход и выход мультиплексора программирования соединены соответственно с выходом поля кода операции первого регистра микрокоманд, выходом поля кода операции регистра управления, выходом поля признака об. работки регистра управления и выходом кода операции устройства, вход сброса, первый и второй тактовые входы, информационный выход и выход признака индексации блока формирования адреса подключены соответственно к входу запуска устройства, выходу третьего элемента задержки, выходу поля метки перепрограммирования регистра управления, выходу кода операции устройства и первому входу пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом поля конца микропрограммы первого регистра микрокоманд и входом второго элемента задержки, единичный и нулевой входы и прямой выход триггера программирования подключены соответственно к выходу пятого элемента ИЛИ, входу признака перепрограммирования устройства и первому входу второго элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, который подключен также к входу третьего элемента задержки, выход второго элемента И соединен с входом синхронизации второго регистра адреса и входом четвертого элемента задержки, выход которого подключен к входу разрешения обращения блока управляющей памяти и входу синхронизации второго регистра микрокоманд, выходы поля конфигурации, поля приема данных, поля адреса записи, поля адреса считывания и поля выдачи данных которого соединены с одноименными выходами устройства, вход сброса, информационный вход, вход синхронизации и выход поля начального адреса регистра управления подключены. соответственно к входу запуска устройства,входу кода операции устройства, входу синхронизации устройства и второму информационному входу второго коммутатора, первый и второй входы и выход шестого элемента ИЛИ соединены соответственно с выходом поля признака выполнения микропрограммы второго регистра микрокоманд, входом запуска устройства и входами сброса второго регистра адреса и второго ре" тистра микрокоманд, а вход и выход седьмого элемента ИЛИ подключены соответственно к выходу второго регистра адреса и управляющему входу второго коммутатора.2. Устройство по п.1, о т л и -ч а ю щ е е с я тем, что блок формирования адреса содержит счетчик индексации столбцов, четыре элемента И, счетчик индексации строк, регистр адреса, два элемента ИЛИ, два оцновибратора и элемент задержки, вход и выход которого соединены соответственно с выходом первого элемента И и входом синхронизации реги - стра адреса, первый и второй входы и выход первого элемента И подключены соответственно к первому и второму тактовым входам блока и счетному входу счетчика индексации столбцов, выход которого соединен с первым информационным входом регистра адреса и входом второго элемента И, выход которого подключен к первому входу третьего элемента И и входу первого одновибратора, вход сброса блока соединен с входом сброса ре 11 1 З гистра адреса и первыми входами первого и второго элементов ИЛИ, второй и третий входы и выход первого элемента ИЛИ подключены соответственно к выходу первого одновибратора, выходу второго одновибратора и входу сброса счетчика индексации столбцов, второй вход и выход второго элемента ИЛИ соединены соответственно с выходом второго одновибратора и входом сброса счетчика индексации строк, выход которого подключен к второму информационному входу 54192регистра адреса.и первому входу четвертого элемента И, второй вход которого соединен с выходом второгоэлемента И, выход четвертого элемента И подключен к выходу приэнака индексации блока и входу второгооцновибратора, второй вход и выходтретьего элемента И соединены соот ветственно с выходом первого элемента И и тактовым входом счетчика индексации строк, а выход регистра адреса подключен к информационному выходу блока.г1354192 ктор Н.Бобкова исноеСР аказ Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,95/44 ВНИИПИ по де 1130359 Мосоставитель Г.Виталиевехред А.Кравчук Корректор Л.Пилипенк ираж 671 Подл осударственного комитета СС м изобретений и открытий а, Ж, Раушская наб., д,4/5

СмотретьЗаявка

3971319, 28.10.1985

ЛЕНИНГРАДСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

САМОШИН ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/46

Метки: микропрограммное

Опубликовано: 23.11.1987

Код ссылки

<a href="https://patents.su/8-1354192-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство управления очередностью подключения источников информации к магистрали

Случайный патент: Цифровой измеритель угловой скорости