Управляющий процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1290341

Авторы: Алексенко, Балашов, Бжезинский, Колесников, Куприянов, Пантелеев

Текст

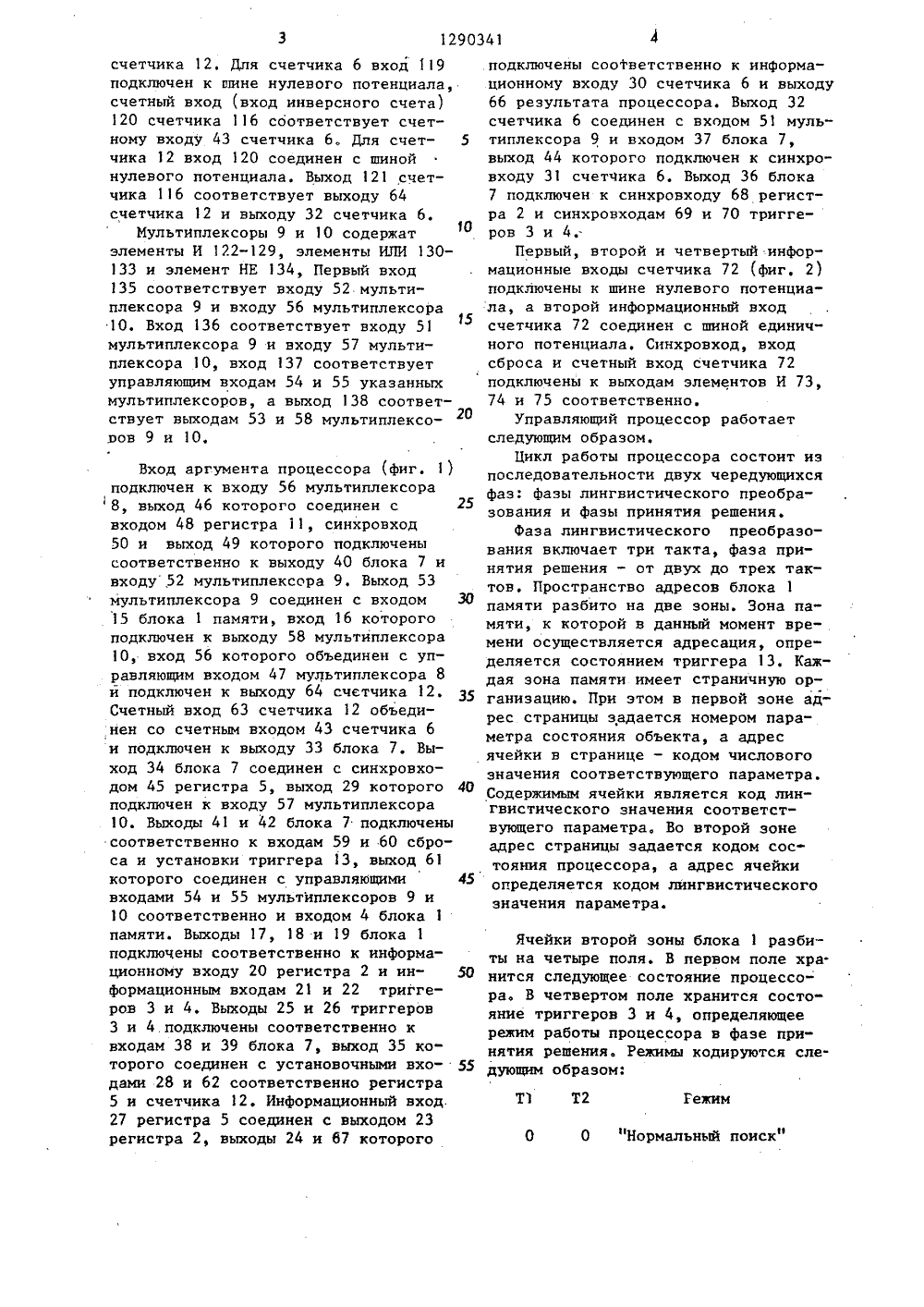

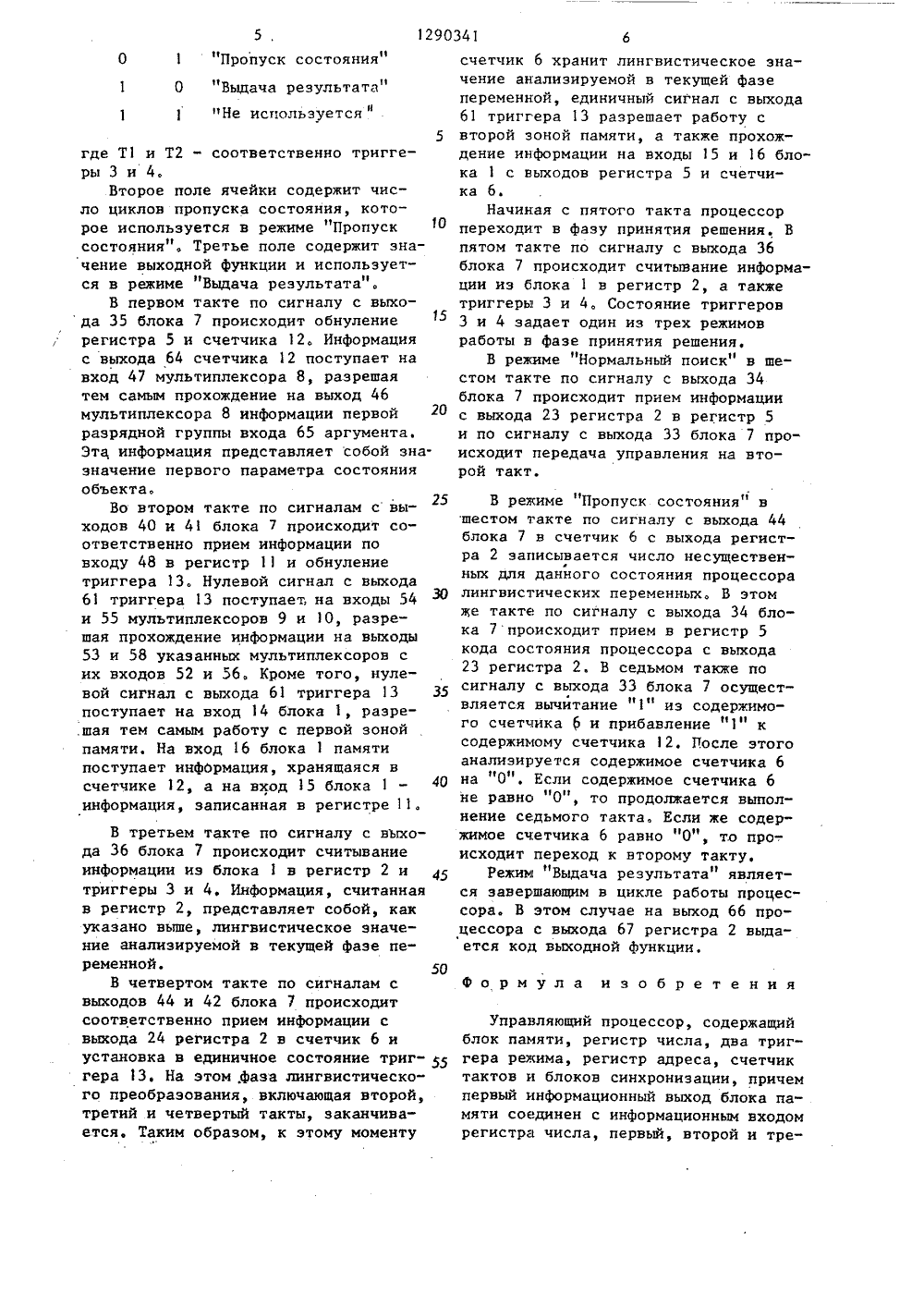

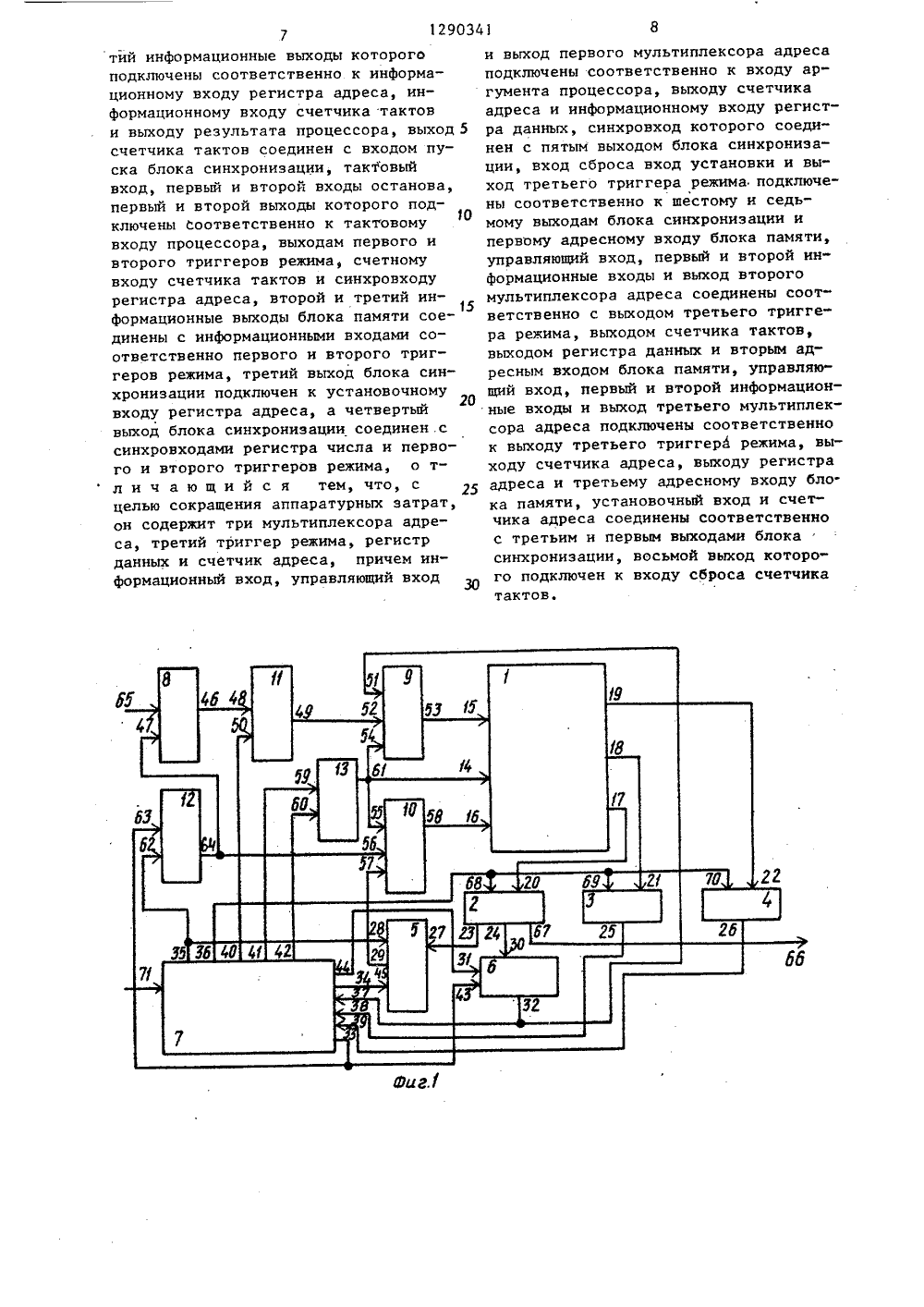

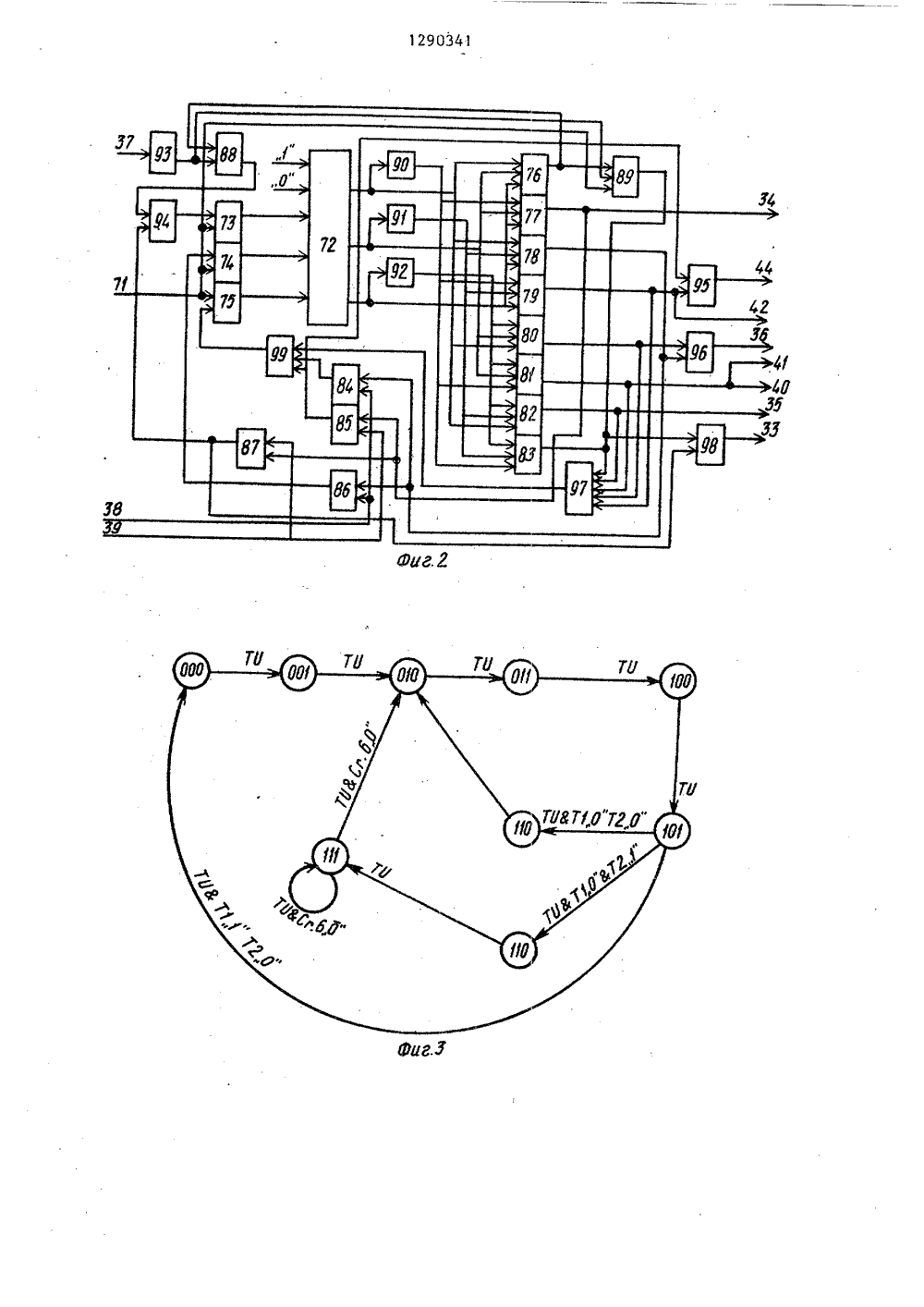

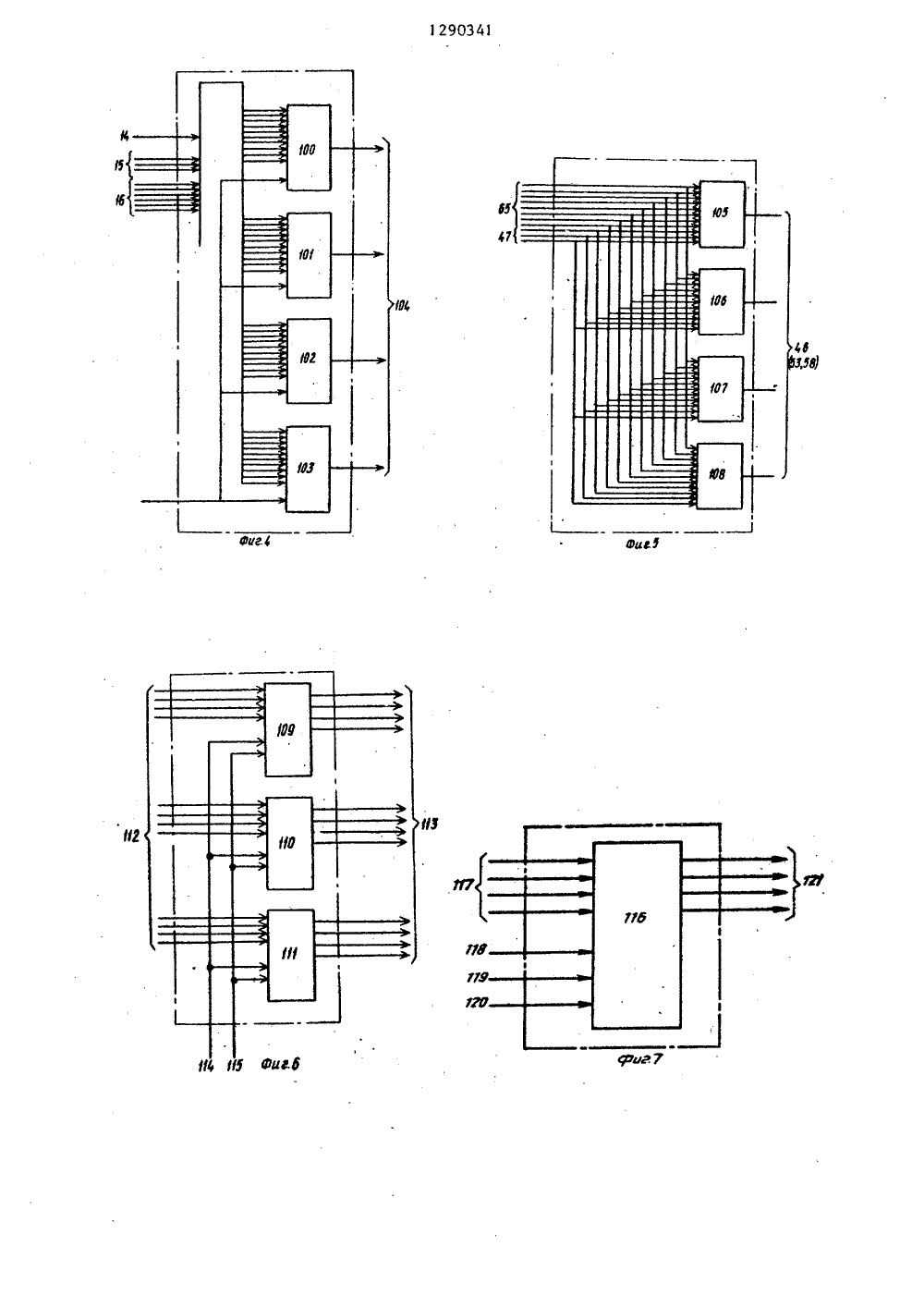

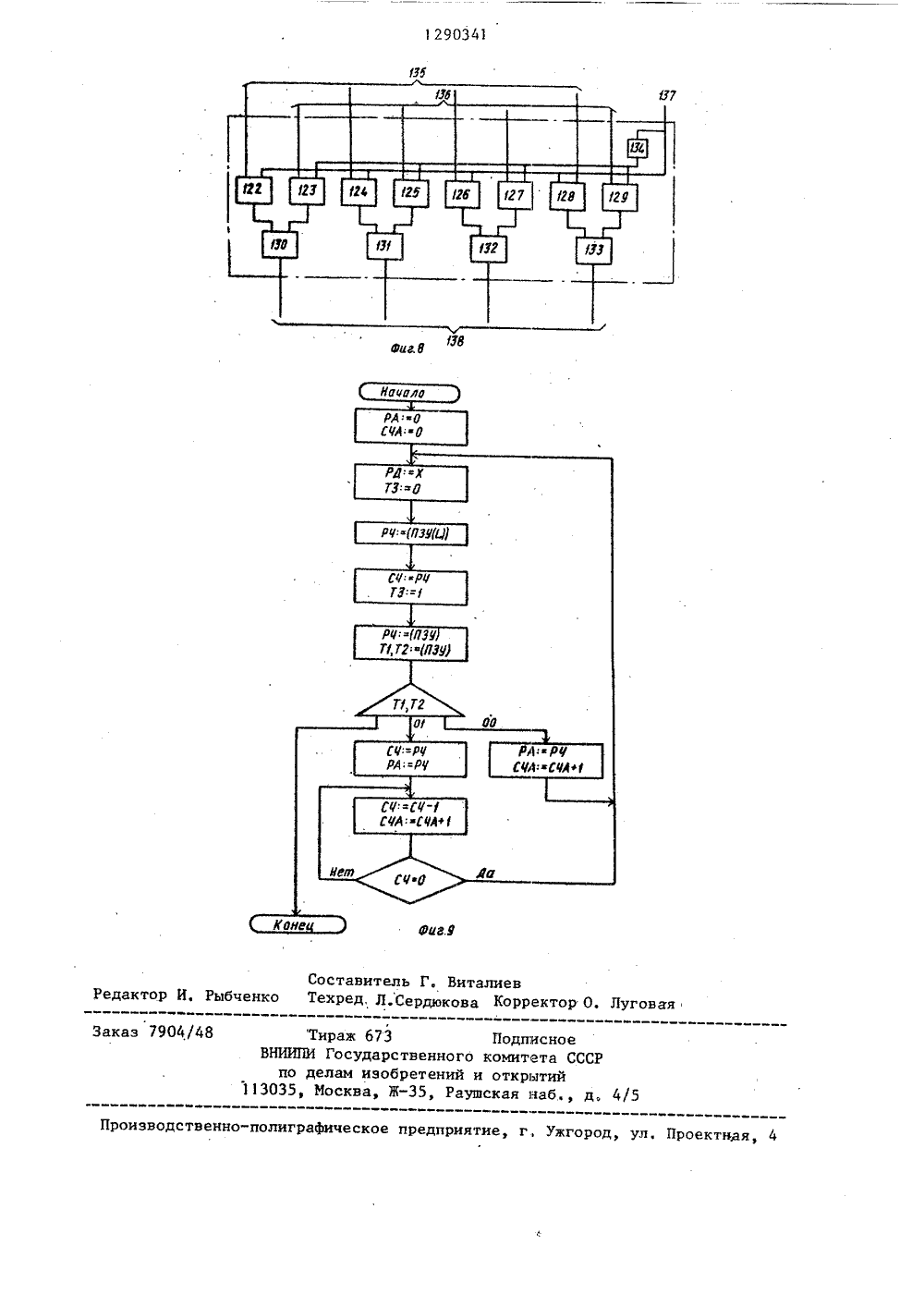

90341 СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 51)4 О 06 Р 15/20 ОБРЕЕЛЬСТВ ЕНИЯ Балашов,есников,реализации - Управ 1974, В 6,веде ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ ИК АВТОРСКОМУ СВИ(57) Изобретение относится к областицифровой вычислительной техники иможет быть использовано при созданиисистем, реализующих алгоритмы управления, контроля и диагностики объектов, не имеющих точной математичес"кой модели. Целью изобретения является сокращение аппаратурных затратпроцессора, в том числе аппаратурныхзатрат блока постоянной памяти, приреализации алгоритмов управления,заданных в лингвистической форме. Сэтой целью в процессор, содержащийблок памяти, регистр числа, два триггера режима, регистр адреса, счетчиктактов и блок синхронизации, в нытри мультиплексора адреса, третийтриггер режима, регистр данных исчетчик адреса. 9 ил.Изобретение относится к цифровойвычислительной технике и может бытьиспользовано при создании систем, реализующих алгоритмы управления, контроля и диагностики объектов, не имеющих точной математической модели,т.е. в системах, неотъемлемым звеномкоторых является человек, оценивающийинформацию и принимающий решение влингвистической форме.Целью изобретения является сокращение аппаратурных затрат процессора,в том числе аппаратурных затрат блокапостоянной памяти, при реализации алгоритмов управления, заданных в математической форме,На фиг. 1 представлена функциональная схема процессора; на фиг, 2 - припример реализации блока синхронизации; на фиг. 3 - граф переходов счетчика блока синхронизации; на фиг, 4 -пример реализации блока памяти; нафиг. 5 - пример реализации первогомультиплексора адреса; на фиг, 6 в , 25пример реализации регистра данных,регистра адреса и регистра числа;на фиг, 7 - пример реализации счетчика тактов и счетчика адреса; нафиг. 8 - пример реализации второгои третьего мультиплексоров адреса;нафиг. 9 - пример реализации алгоритмаработы процессора,Процессор содержит блок 1 памяти,регистр 2 числа, первый триггер 3 режима, второй триггер 4 режима, регистр 5 адреса, счетчик 6 тактов,блок 7 синхронизации с первого потретий мультиплексоры 8-10 адреса,регистр 11 данных, счетчик 12 адреса, третий триггер 13 режима, первыйвторой и третий адресные входы 14-16блока 1, первый, второй и третий ин. формационные выходы 17, 18 и 19 блока 1, информационный вход 20 регистра 2, информационный вход 21 триггера 3, информационный вход 22 триггера4, первый и второй выходы 23 и 24регистра 2, выход 25 триггера 3, выход 26 триггера 4, информационныйвход 27 регистра 5, установочный вход28 регистра 5, выход 29 регистра 5,информационный вход 30 и вход 31сброса счетчика 6, выход 32 счетчика6, выходы 33-36 блока 7, вход 37 пуска блока 7, первый и второй входы 38и 39 останова блока 7, выходы 40, 41и 42 блока 7, счетный вход 43 счетчика 6, выход 44 блока 7, синхровход 45 регистра 5, выход 46 мультиплексора 8, управляющий вход 47 мультиплексора 8, информационный вход 48 регистра 11 выход 49 регистра 11, синхровход 50 регистра 11, первый и второй информационные входы 51 и 52 мультиплексора 9, выход 53 мультиплексора 9, управляющие входы 54 и 55 мультиплексоров 9 и 1 О, первый и второй информационные входы 56 и 57 мультиплексора 10, выход 58 мультиплексора 1 О, вход 59 сброса триггера 13, вход 60 установки триггера 13, выход 61 триггера 13, установочный вход 62 счетчика 12, счетный вход 63 счетчика 12, выход 64 счетчика 12, информационный вход 65 мультиплексора 8, выход 66 результата процессора, третий выход 67 регистра 2, синхровход 68 регистра 2, синхровход 69 триггера 3, синхровход 70 триггера 4, тактовый вход 71 блока 7.Блок 7 синхронизации содержит счетчик 72, элементы И 3-89, элементы НЕ 90-92, элементы ИЛИ 93-99.Блок 1 памяти содержит одноразрядные модули 100-103 и выход 104 соответствующий первому, второму и третьему информационным выходам 17, 18 и 19 блока 1.Мультиплексор 8 содержит одноразрядные мультиплексоры 105-108.Регистры 11, 5 и 2 содержат четырехразрядные регистры 109-111,информационный вход 112, соответствующий информационным входам 48, 27 и 20 ре" гистров 11, 5 и 2, и выход 113, соответствующий выходам 49 и 29 регистров 11 и 5. Для регистра 2 выход 113 разбит на три группы выходов 23, 24 и 67, Вход 114 на фиг. 6 соответствует синхровходам 50, 45 и 68 регистров 11, 5 и 2, а вход 115 соответствует установочному входу 28 регистра 5. Для регистра 11 и регистра 2 установочный вход 115 подключен к шине нулевого потенциала.Счетчики 6 и 12 содержат четырех- разрядный счетчик 116, информационный вход 117, соответствующий информационному входу 30 счетчика 6. Для счетчика 12:вход 117 подключен к шине нулевого потенциала. Синхровход 118 счетчика 116 соответствует синхровходу 31 счетчика 6 и установочному входу 62 счетчика 12, Счетный вход (вход прямого счета) 119 счетчика 116 соответствует счетному входу 63,1290341 Вход аргумента процессора (фиг. 1) подключен к входу 56 мультиплексора8, выход 46 которого соединен с 25 входом 48 регистра 11, синхровход 50 и выход 49 которого подключены соответственно к выходу 40 блока 7 и входу 52 мультиплексора 9. Выход 53 мультиплексора 9 соединен с входом 30 15 блока 1 памяти, вход 16 которого подключен к выходу 58 мультиплексора 10, вход 56 которого объединен с управляющим входом 47 мультиплексора 8 и подключен к выходу 64 счетчика 12. Счетный вход 63 счетчика 12 объединен со счетным входом 43 счетчика 6 и подключен к выходу 33 блока 7. Выход 34 блока 7 соединен с синхровходом 45 регистра 5, выход 29 которого 40 подключен к входу 57 мультиплексора 10. Выходы 41 и 42 блока 7 подключены соответственно к входам 59 и 60 сброса и установки триггера 13, выход 61 которого соединен с управляющими 45 входами 54 и 55 мультиплексоров 9 и 10 соответственно и входом 4 блока 1 памяти. Выходы 17, 18 и 19 блока 1 подключены соответственно к информационному входу 20 регистра 2 и ин формационным входам 21 и 22 триггеров 3 и 4, Выходы 25 и 26 триггеров 3 и 4.подключены соответственно к входам 38 и 39 блока 7, выход 35 которого соединен с установочными вхо дами 28 и 62 соответственно регистра 5 и счетчика 12. Информационный вход.27 регистра 5 соединен с выходом 23 регистра 2, выходы 24 и 67 которого Ячейки второй зоны блока 1 разбиты на четыре поля. В первом поле хранится следующее состояние процессора. В четвертом поле хранится состояние триггеров 3 и 4, определяющее режим работы процессора в фазе принятия решения. Режимы кодируются следующим образом: Т 3 Т 2 Режим счетчика 12, Для счетчика 6 вход 119подключен к шине нулевого потенциала,счетный вход (вход инверсного счета)120 счетчика 116 соответствует счетному входу 43 счетчика 6. Для счетчика 12 вход 120 соединен с шинойнулевого потенциала. Выход 12 счетчика 116 соответствует выходу 64счетчика 12 и выходу 32 счетчика 6.Мультиплексоры 9 и 10 содержатэлементы И 122-129, элементы ИЛИ 130133 и элемент НЕ 134, Первый вход135 соответствует входу 52 мультиплексора 9 и входу 56 мультиплексора10. Вход 136 соответствует входу 51мультиплексора 9 и входу 57 мультиплексора 1 О, вход 137 соответствуетуправляющим входам 54 и 55 указанныхмультиплексоров, а выход 138 соответствует выходам 53 и 58 мультиплексоров 9 и 10,подключены соо 1 ветственно к информационному входу 30 счетчика 6 и выходу 66 результата процессора. Выход 32 счетчика 6 соединен с входом 51 мультиплексора 9 и входом 37 блока 7, выход 44 которого подключен к синхровходу 31 счетчика 6, Выход 36 блока 7 подключен к синхровходу 68 регистра 2 и синхровходам 69 и 70 триггеров 3 и 4.- Первый, второй и четвертый информационные входы счетчика 72 (фиг. 2) подключены к шине нулевого потенциала, а второй информационный вход счетчика 72 соединен с шиной единичного потенциала. Синхровход, вход сброса и счетный вход счетчика 72 подключены к выходам элементов И 73, 74 и 75 соответственно.Управляющий процессор работает следующим образом.Цикл работы процессора состоит из последовательности двух чередующихся фаз: фазы лингвистического преобразования и фазы принятия решения.Фаза лингвистического преобразования включает три такта, фаза принятия решения - от двух до трех тактов. Пространство адресов блока 1 памяти разбито на две зоны. Зона памяти, к которой в данный момент времени осуществляется адресация, определяется состоянием триггера 13. Каж" дая эона памяти имеет страничную организацию. При этом в первой зоне адрес страницы задается номером параметра состояния объекта, а адрес ячейки в странице - кодом числового значения соответствующего параметра. Содержимым ячейки является код лингвистического значения соответствующего параметра, Во второй зоне адрес страницы задается кодом состояния процессора, а адрес ячейки определяется кодом лингвистического значения параметра. 0 0 "Нормальный поиск"5, 12903411 "Пропуск состояния"сч 0 "Выдача результата"1 "Не используется " где Т и Т 2 - соответственно триггеры 3 и 4,Второе поле ячейки содержит число циклов пропуска состояния, которое используется в режиме "Пропуск состояния". Третье поле содержит значение выходной функции и используется в режиме "Выдача результата".В первом такте по сигналу с выхо да 35 блока 7 происходит обнуление регистра 5 и счетчика 12. Информация с выхода 64 счетчика 2 поступает на вход 47 мультиплексора 8, разрешая тем самым прохождение на выход 46 мультиплексора 8 информации первой разрядной группы входа 65 аргумента. Эта, информация представляет собой зназначение первого параметра состояния объекта.Во втором такте по сигналам с выходов 40 и 41 блока 7 происходит соответственно прием информации по входу 48 в регистр 11 и обнуление триггера 13. Нулевой сигнал с выхода 61 триггера 13 поступает, на входы 54 и 55 мультиплексоров 9 и 10, разрешая прохождение информации на выходы 53 и 58 указанных мультиплексоров с их входов 52 и 56. Кроме того, нулевой сигнал с выхода 61 триггера 13 35 поступает на вход 14 блока 1, разре,шая тем самым работу с первой зоной памяти. На вход 16 блока 1 памяти поступает инфОрмация, хранящаяся в счетчике 12, а на вход 15 блока 1 - 40 информация, записанная в регистре 11. В третьем такте по сигналу с выхода 36 блока 7 происходит считывание информации иэ блока 1 в регистр 2 и 45 триггеры 3 и 4. Информация, считанная в регистр 2, представляет собой, как указано вышее, лингвистическое значение анализируемой в текущей фазе переменной. 50В четвертом такте по сигналам с выходов 44 и 42 блока 7 происходит соответственно прием информации с выхода 24 регистра 2 в счетчик 6 и установка в единичное состояние триг гера 13, На этом, фаза лингвистического преобразования, включающая второй, третий и четвертый такты, заканчивается, Таким образом, к этому моменту етчик 6 хранит лингвистическое значение анализируемой в текущей фазе переменной, единичный сигнал с выхода 61 триггера 13 разрешает работу с второй зоной памяти, а также прохождение информации на входы 15 и 16 блока 1 с выходов регистра 5 и счетчика 6.Начиная с пятого такта процессор переходит в фазу принятия решения. В пятом такте по сигналу с выхода 36 блока 7 происходит считывание информации из блока 1 в регистр 2, а также триггеры 3 и 4. Состояние триггеров 3 и 4 задает один из трех режимов работы в фазе принятия решения.В режиме "Нормальный поиск" в шестом такте по сигналу с выхода 34 блока 7 происходит прием информации с выхода 23 регистра 2 в регистр 5 и по сигналу с выхода 33 блока 7 происходит передача управления на второй такт. В режиме "Пропуск состояния" в шестом такте по сигналу с выхода 44 блока 7 в счетчик б с выхода регистра 2 записывается число несущественных для данного состояния процессора лингвистических переменных. В этом же такте по сигналу с выхода 34 блока 7 происходит прием в регистр 5 кода состояния процессора с выхода 23 регистра 2, В седьмом также по сигналу с выхода 33 блока 7 осуществляется вычитание "1" из содержимого счетчика р и прибавление "1" к содержимому счетчика 12, После этого анализируется содержимое счетчика 6 на "0". Если содержимое счетчика 6 не равно "0", то продолжается выполнение седьмого такта, Если же содержимое счетчика 6 равно "0", то происходит переход к второму такту.Режим "Выдача результата" является завершающим в цикле работы процессора. В этом случае на выход 66 процессора с выхода 67 регистра 2 выдается код выходной функции,Формула изобретения Управляющий процессор, содержащий блок памяти, регистр числа, два триггера режима, регистр адреса, счетчик тактов и блоков синхронизации, причем первый информационный выход блока па" мяти соединен с информационным входом регистра числа, первый, второй и тре7 1290341 тий информационные выходы которого подключены соответственно к информационному входу регистра адреса, информационному входу счетчика тактов и выходу результата процессора, выход счетчика тактов соединен с входом пуска блока синхронизации, тактовый вход, первый и второй входы останова, первый и второй выходы которого подключены соответственно к тактовому входу процессора, выходам первого и второго триггеров режима, счетному входу счетчика тактов и синхровходу регистра адреса, второй и третий информационные выходы блока памяти соединены с информационными входами соответственно первого и второго триггеров режима, третий выход блока синхронизации подключен к установочному входу регистра адреса, а четвертый выход блока синхронизации соединен.с синхровходами регистра числа и первого и второго триггеров режима, о тл и ч а ю щ и й с я тем, что, с целью сокращения аппаратурных затрат, он содержит три мультиплексора адреса, третий триггер режима, регистр данных и счетчик адреса, причем информационный вход, управляющий вход и выход первого мультиплексора адреса подключены соответственно к входу аргумента процессора, выходу счетчика адреса и информационному входу регист ра данных, синхровход которого соединен с пятым выходом блока синхронизации, вход сброса вход установки и выход третьего триггера режима подключены соответственно к шестому и седьмому выходам блока синхронизации и первому адресному входу блока памяти, управляющий вход, первый и второй информационные входы и выход второго 15мультиплексора адреса соединены соответственно с выходом третьего триггера режима, выходом счетчика тактов, выходом регистра данных и вторым адресным входом блока памяти, управляющий вход, первый и второй информационные входы и выход третьего мультиплексора адреса подключены соответственно к выходу третьего триггера режима, выходу счетчика адреса, выходу регистра адреса и третьему адресному входу блока памяти, установочный вход и счетчика адреса соединены соответственно с третьим и первым выходами блока синхронизации, восьмой выход которого подключен к входу сброса счетчика тактов.ираж 673 Государственнелам изобретенМосква, Ж,Подписное го комитета СССР й и открытий аушская наб.,

СмотретьЗаявка

3796552, 03.10.1984

ПРЕДПРИЯТИЕ ПЯ Г-4149

АЛЕКСЕНКО АНДРЕЙ ГЕННАДЬЕВИЧ, БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, БЖЕЗИНСКИЙ АЛЕКСАНДР СЕМЕНОВИЧ, КОЛЕСНИКОВ ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ, КУПРИЯНОВ МИХАИЛ СТЕПАНОВИЧ, ПАНТЕЛЕЕВ МИХАИЛ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 17/28

Метки: процессор, управляющий

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/8-1290341-upravlyayushhijj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Управляющий процессор</a>

Предыдущий патент: Микропроцессор

Следующий патент: Устройство для моделирования систем массового обслуживания

Случайный патент: 310386