Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1290340

Авторы: Генина, Гришин, Ярошевский

Текст

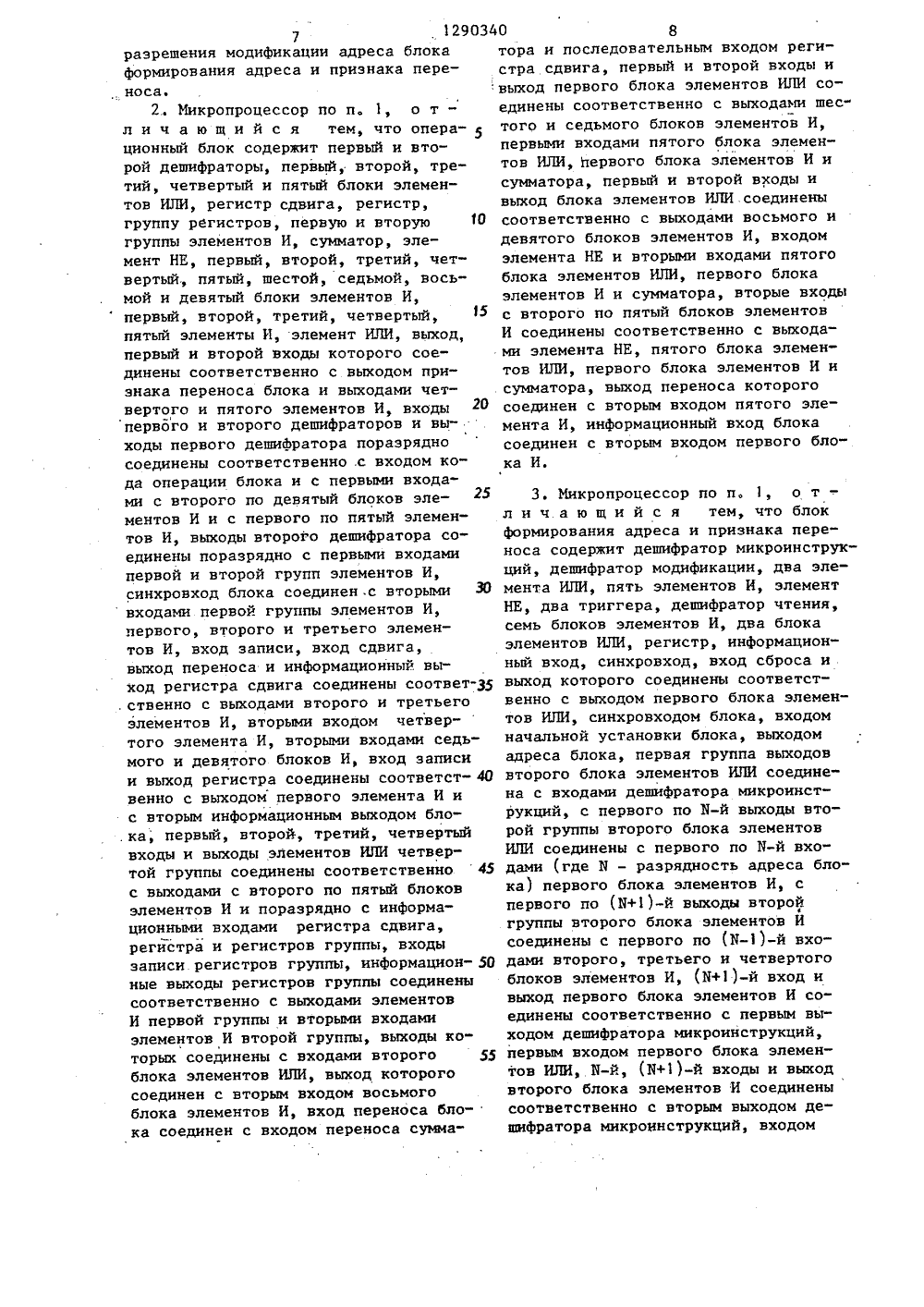

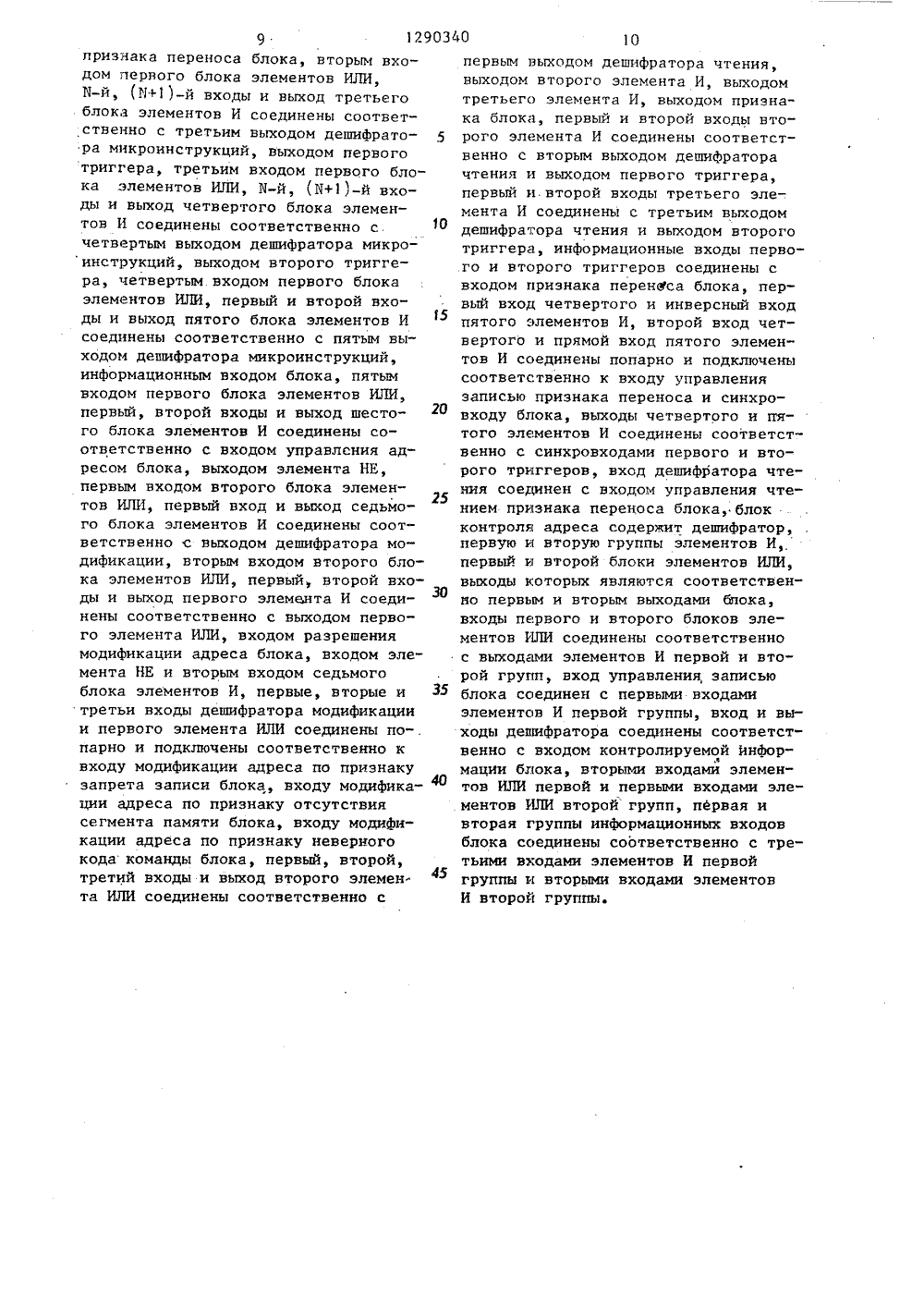

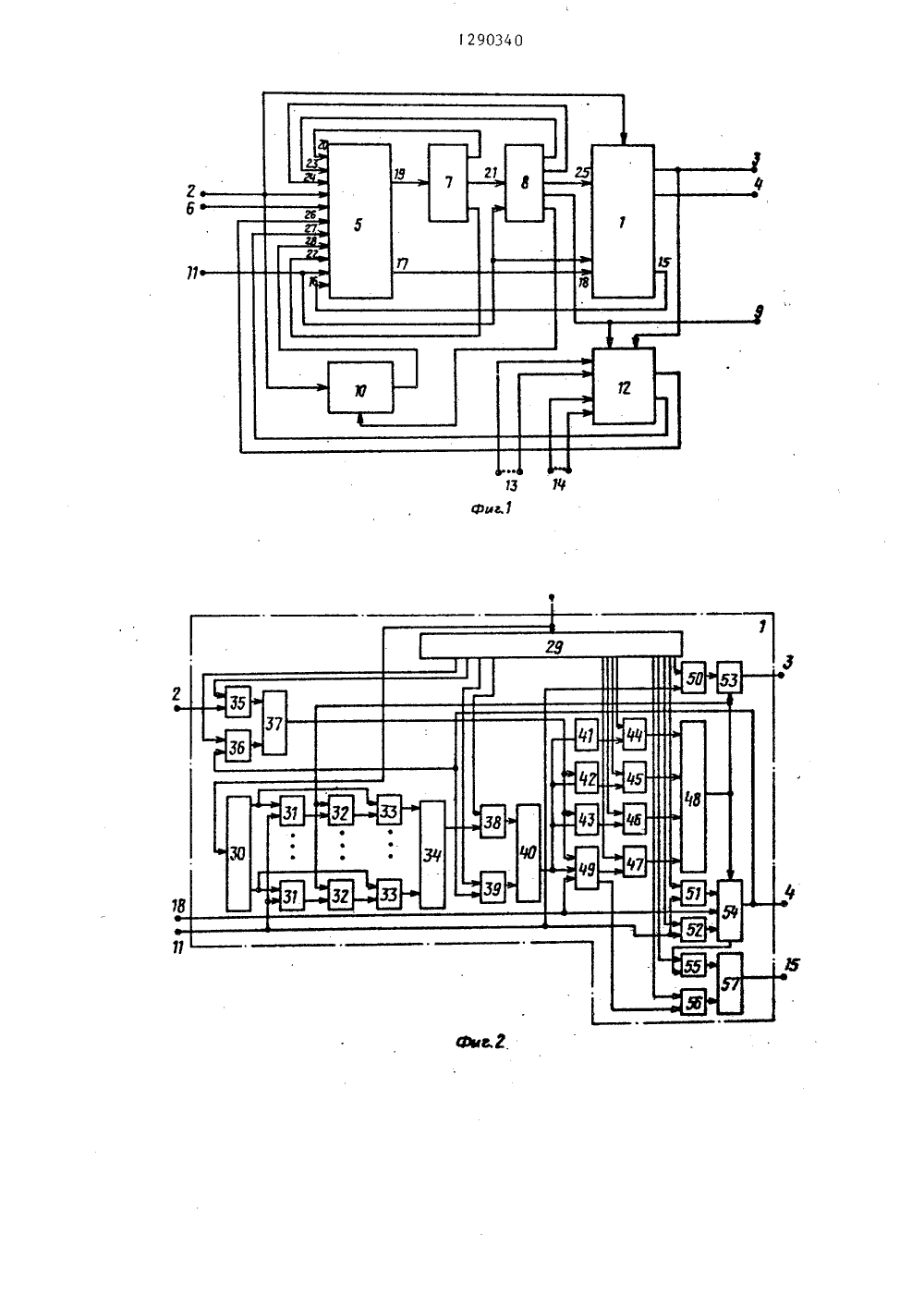

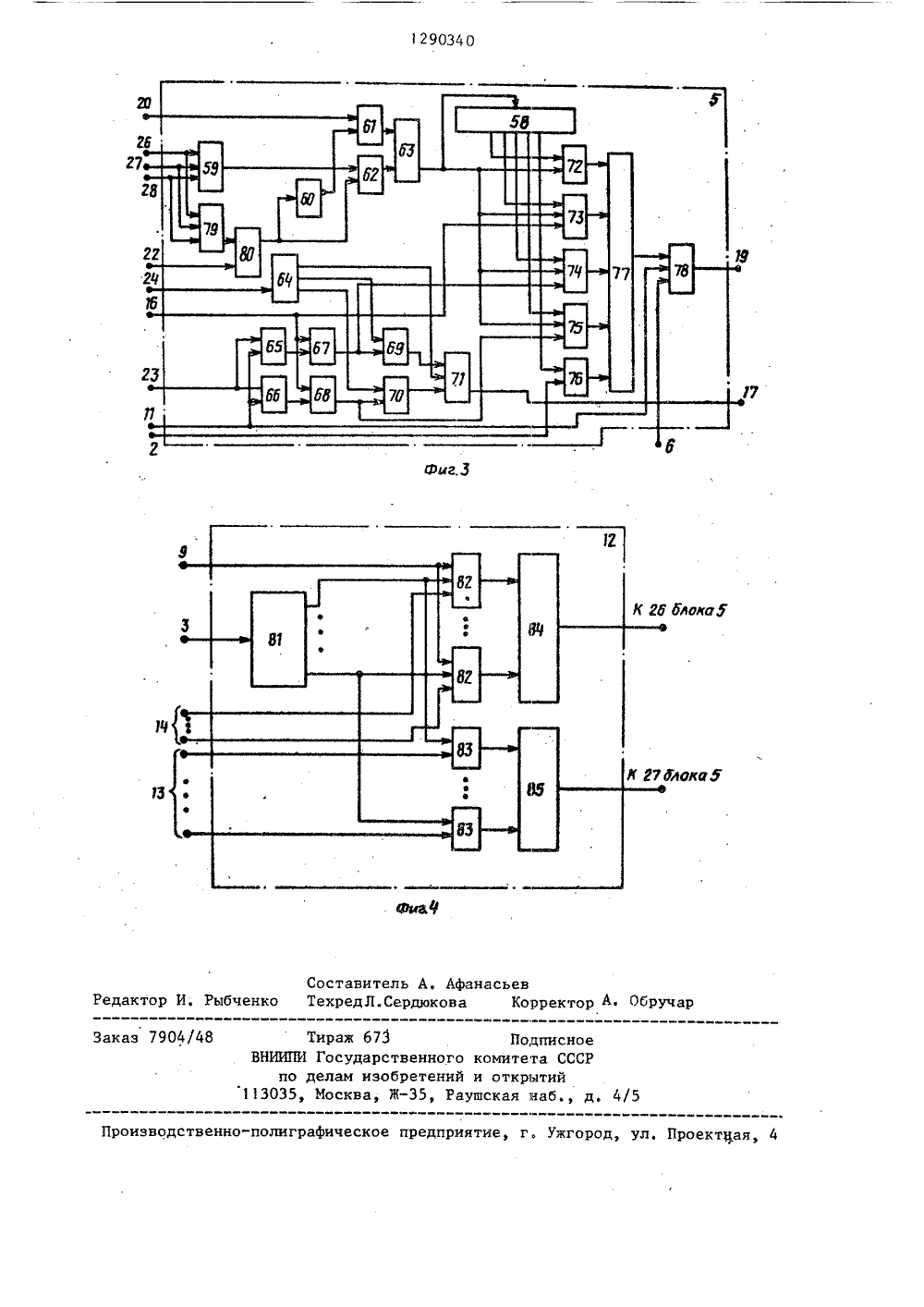

90340 1 12Изобретение относится к вычислительной технике и может быть использовано в информационных, управляющихи вычислительных системах.Цель изобретения - повышение достоверности функционирования,На фиг. 1 изображена функциональная схема микропроцессора; нафиг. 2 - функциональная схема операционного блока; на фиг. 3 - функциональная схема блока формированияадреса и признака переноса; нафиг. 4 - функциональная схема блокаконтроля адреса.Микропроцессор (фиг. 1) содержитоперационный блок 1, информационныйвход которого является информационным входом 2 микропроцессора, а выходы 3 и 4 - соответственно вторыми ипервыми информационными выходами микропроцессора, блок 5 формированияадреса и признака переноса, блок 6начальной установки которого является входом микропроцессора, блок 7микропрограммной памяти, регистр 8микрокоманд, выход 9 которого является выходом управления обращением квнешней памяти микропроцессора, блок10 памяти кодов команд, вход 11 синхронизации, блок 12 контроля адреса,группы входов 13 и 14 которого являются соответственно контрольными входами микропроцессора для указаниясегментов подключенной памятии указания запрещенных для записисегментов памяти, Позициями 15-28обозначены входы и выходы микропроцессора.Блок 1 (фиг, 2) содержит дешифратор 29 микроконструкций дешифратор30 выбора регистра, группу элементовИ 31, группу регистров 32, группу.элементов И 33, блоки элементовИПИ 34, И 35, 36, ИЛИ 37, И 38, 39,ИЛИ 40, НЕ 41, ИЛИ 42, И 43-4, ИЛИ48, сумматор 49, элементы И 50, И 51,52, регистр адреса 53, сдвиговый регистр 54, элементы И 55, 56, ИЛИ 57,Блок 5 (фиг. 3) содержит дешифратор 58 микроинструкций, дешифратор 59 модификации, элемент НЕ 60, группы элементов И 61, 62, блок ИЛИ 63, дешифратор 64 чтения, элементы И 65, 66, триггеры 67, 68, элементы И 69, 70, ИЛИ 71, блоки элементов И 72-76, блок ИЛИ 77, регистр 78 адреса, элементы ИЛИ 79, И 80. 5 10 15 20 25 30 35 40 45 2Блок 12 (фиг, 4) содержит дешнф-ратор 81, две группы элементов И 82,83 и два блока ИЛИ 84, 85,Микропроцессор работает следующимобразом.Для приведения микропроцессора висходное состояние на вход 6 подаетсясигнал начальной установки, при этомрегистр 78 блока 5 устанавливается внулевое состояние. В результате навыходе 19 блока 5 образуется нулевойадрес, который является начальным адресом микропрограммы начальной загрузки. По этому адресу из блока 7выбирается микрокоманда. Каждая микрокоманда состоит из двух частей:адресной и исполнительной. Адреснаячасть поступает на вход 20 блока 5 ичерез группы элементов И 61 и ИЛИ 63поступает на входы дешифратора 58 иблоков элементов И 72-76 групп,Адресная часть состоит из двух частей: в первой указывается тип перехода, а во второй адрес перехода.Сигналы, собтветствующие типу перехода. поступают на вход дешифратора 58.а сигналы адреса перехода поступаютна вторые входы блоков элементов И 7275 групп. В зависимости от того, накаком выходе дешифратора 58 образуется единичный сигнал, адрес следующеймикрокоманды определяется либо безусловно по адресной части микрокоманды, либо с учетом состояния триггеров 67 и 68, либо с учетом сигналана входе 16 блока 5, либо по кодукоманды на входе 2 блока 5, Адрес,образованный одним из вышеперечисленных способов, поступает через блокэлементов ИЛИ 77 на информационныйвход регистра 78 и по синхросигналуна вхоце 11 блока 5 записывается врегистр 8. Одновременно исполнительная часть текущей микрокоманды записывается в регистр 8,Исполнительная часть микрокоманды состоит из пяти полей. Код первого поля, поступающий на вход 23 блока 5, определяет, в какой из триггеров (67 или 68) по синхросигналу записывается значение на входе 16 блока 5. Код повторного поля, поступающий на вход 24 блока 5, определяет функцию. дешифратора 64 чтения, в зависимости от которой на выходе 17 блока 5 образуется либо содержимое триггеров 67 или 68, либо значение логического нуля или единицы.1290340 Код третьего поля, поступающий.на вход 25 блока 1, определяет функцию операционного блока. Часть сигналов этого поля поступает на входдешифратора 29 блока 1 и определяеттип операции, а другая часть поступает на вход дешифратора 30, выбирающего один из регистров 32 группы,который является первым операндомвыполняемой операции. Вторым операндом может быть либо код на входе 2микропроцессора, либо содержимоерегистра 54 блока 1. Над операндамиблок 1 выполняет арифметико-логические и сдвиговые операции. 15Выбранные операнды с выходов блоков элементов ИЛИ 37 и 40 поступаютна входы блоков элементов НЕ 41,ИЛИ 42, И 43, сумматора 49, на выходах которых образуются соответственно результаты логических операций НЕ,ИЛИ, И или сумма операндов с учетомсигнала переноса, поступающего навход 18 блока 1, При переполнениисумматора на его выходе переноса образуется сигнал переноса, поступающийна вход элемента И 56, и при наличииединичного сигнала на втором входеэлемента И 56, поступающего с выходадешифратора 29, сигнал переноса через элементы И 56, ИЛИ 57 поступаетна выход 15 блока 1,В зависимости от того, какие блоки элементов И 44-47 открыты единичным сигналом с выходов дешифратора29, результат, соответствующий операции, поступает через соответствующийблок элементов И и элемент ИЛИ 48 навходы регистров 53, 54 и регистров32 группы. Результат записывается в 40один из этих регистров в зависимостиот наличия единичного сигнала навходах элементов И 50, 51 или элементов И 31 группы, При наличии единичного сигнала на входе элемента И 52 45результат в регистр 54 записываетсясо сдвигом на один разряд вправо,при этом на последовательный информационный вход регистра 54 данные поступают с входа 18 блока 1, а данные 50с последовательного выхода регистра54.через элементы И 55 и ИЛИ 57 поступают на выход 15 блока 1. Код четвертого поля регистра 8 5поступает на.выход 9 микропроцессораи указывает блоку внешней памяти (непоказан), какой тип операции (записьили чтение) выполняется. 4Кроме того, этот сигнал поступаетна вход элементов И 82 группы, обеспечивая разрешение прохождения сигналов через элементы этой группы, привыполнении операции записи в блоквнешней памяти.Работа блока 12 состоит в следующем. На группах входов 13 и 14 любым известным способом формируютсяединичные сигналы, указывающие соответственно сегменты адресного пространства памяти, отсутствующие в данной конфигурации вычислительной памяти, и сегменты подключенной внешнейпамяти, запись в которые запрещена.Изменение номеров сегментов, записьв которые запрещена, может производиться программным способом.При обращении к внешней памятина выходе 3 микропроцессора формируется адрес ячейки памяти, который поступает на вход дешифратора 81 блока12, в результате чего на одном иэвыходов дешифратора 81, номер которого соответствует адресуемому сегменту памяти, образуется единичныйсигнал, поступающий на вход одногоиз элементов И 82, 83 группы. В томслучае, если адресуемый сегмент отсутствует, на втором входе элементаИ 83 группы также будет единичныйсигнал, поступающий с группы входов13 микропроцессора. Таким образом,на выходе блока ИЛИ 85 образуетсяединичный сигнал, сообщающий об отсутствии адресуемой ячейки памяти.В том случае, если адресуемый сегмент памяти запрещен для записи, навтором входе соответствующего элемента И также должен присутствоватьединичный сигнал, поступающий с группвходов 14 микропроцессора, а на третьем входе элементов И 82 группы присутствует сигнал записи, то на выходеблока ИЛИ 83 образуется сигнал о запрете записи,Информация, поступающая на вход 2микропроцессора, представляет собойлибо числовые данные, либо коды команд, В том случае, когда происходитприем кода команды, с пятого выходарегистра 8 на вход разрешения блока10 поступает сигнал, разрешающий работу этого блока, В блок 10 памяти кодов команд по адресам, совпадающим скодами команд, записаны нули, а по всемостальным адресам- единицы. Таким образом, в случае приема нелегальногокода команды на выходе блока 10 об12903 1, Микропроцессор, содержащий операционный блок, блок формирования ад реса и признака переноса, блок микропрограммной памяти, регистр микрокоманд, вход записи, информационный вход, первый выход поля управления, второй выход поля управления, выход 55 поля микрооперации, третий выход поля управления которого соединены соответственно с синхровходом микропроцессора, выходом поля микрокоманды разуется единичный сигнал, поступаю" щий на вход 28 блока 5.Итак, при операциях обмена информацией с внешней памятью на входы 26, 27, 28 блока 5 поступают сведения о легальности или нелегальности операции. Кроме того, с третьего выхода блока 7 на вход 22 блока 5 поступает единичный сигнал, разрешающий анализ поступивших сведений в 10 блок 5. В том случае, если имеет место одно из трех нарушений, на выходе элемента ИЛИ 79 образуется единичный сигнал, который открывает элемент И 80. В результате блокируется 45 блок элементов И 61 и открывается блок элементов И 621Таким образом, в случае ошибки естественный ход выполнения микро программы прерывается и адрес следующей микрокоманды определяется кодом, образующимся на выходе дешифратора 59, поступающего через блоки элементов И 62 и ИЛИ 63 на вход дешифрато ра 58 и блоков элементов И 72-76.Иными словами, при наличии ошибки .происходит переход к началам микропрограмм, выполняющим обработку сообщений о неверном коде команды, абра-. 30 щении к отсутствующему или запрещенному для записи сегменту памяти. Существо работы этих микропрограмм заключается в запоминании слова состояния микропроцессора на данный момент времени, идентификации типа ошибки и передачи управления программам операционной системы для анализа сообщения и принятия соответствующего решения. 40Повьппенная устойчивость к сбоям при операциях обмена информацией позволяет использовать микропроцессор в изделиях, где предъявляются жесткие требования к живучести системы. Формула изобретения 406блока микропрограммной памяти, входом управления признака переноса блока формирсвания адреса и признака переноса, входом управления выдачей признака переноса блока Формирования адреса и признака переноса, входом кода операции операционного блока, выходом управления обращением и памяти микропроцессора, вход начальной установки, выход адреса, вход управления адресом, вход признака переноса, выход признака переноса, синхровход и информационный вход блока формирования адреса и признака переноса.соединены соответственно с входом начальной установки микропроцессора, адресным входом и выходом поля управления формированием адреса микрокоманды блока микропрограммной памяти, выходом переноса и входом переноса операционного блока, синхровходом и информационным входом микропроцессора, синхровход, информационный вход, первый и второй информационные выходы операционного блока соединены соответственно с синхровходом, информационными входом, информационным выходом и выходом адреса внешней памяти микропроцессора, о т л и ч а ю -щ и й с я тем, что, с целью повышения достоверности Функционирования, в него введены блок памяти кодов команд и блок контроля адреса контролируемой информации, вход признака режима записи, первая и вторая группы информационных входов, первый и второй выходы которого соединены соответственно с адресным входом и третьим входом поля управления регистра микрокоманд, группой контрольных вхо" дов указания сегментов подключенной памяти микропроцессора, группой контрольных входов указания запрещенных для записи сегментов памяти микропроцессора, входом модификации адреса по признаку запрета записи и входом модификации адреса по признаку отсутствия сегмента памяти блока формирования адреса и признака переноса, а адресный вход, вход выборки и выход блока памяти кодов команд подключены соответственно к информационному входу микропроцессора, выходу регистра микрокоманд и входу модификации адреса по признаку неверного кода команды блока формирования адреса и признака переноса, выход поля разрешения модификации адреса блока микро-. программной памяти соединен с входом12903разрешения модификации адреса блокаформирования адреса и признака переноса.2 Микропроцессор по п. 1, о т "л и ч а ю щ и й с я тем, что операционный блок содержит первый и второй дешифраторы, первый, второй, третий, четвертый и пятый блоки элементов ИЛИ, регистр сдвига, регистр,группу регистров, первую и вторую 10группы элементов И, сумматор, элемент НЕ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый блоки элементов И,первый, второй, третий, четвертый,пятый элементы И, элемент ИЛИ, выход,первый и второй входы которого соединены соответственно с выходом признака переноса блока и выходами четвертого и пятого элементов И, входыпервого и второго дешифраторов и вы"ходы первого дешифратора поразрядносоединены соответственно .с входом кода операции блока и с первыми входами с второго по девятый блоков элементов И и с первого по пятый элементов И, выходы второго дешифратора соединены поразрядно с первыми входамипервой и второй групп элементов И,синхровход блока соединен .с вторыми З 0входами первой группы элементов И,первого, второго и третьего элементов И, вход записи, вход сдвига,выход переноса и информационный выход регистра сдвига соединены соответ. ственно с выходами второго и третьегоэлементов И, вторыми входом четвертого элемента И, вторыми входами седьмого и девятого блоков И, вход записии выход регистра соединены соответственно с выходом первого элемента И ис вторым информационным выходом бло.ка, первый, второй, третий, четвертыйвходы и выходы элементов ИЛИ четвертой группы соединены соответственно 45с выходами с второго по пятый блоковэлементов И и поразрядно с информационными входами регистра сдвига,регйстра и регистров группы, входызаписи. регистров группы, информационные выходы регистров группы соединенысоответственно с выходами элементовИ первой группы и вторыми входамиэлементов И второй группы, выходы которых соединены с входами второго 55блока элементов ИЛИ, выход которогосоединен с вторым входом восьмогоблока элементов И, вход переноса блока соединен с входом переноса сумча 40 8тора и последовательным входом регистра сдвига, первый и второй входы и выход первого блока элементов ИЛИ соединены соответственно с выходами шестого и седьмого блоков элементов И, первыми входами пятого блока элементов ИЛИ, первого блока элементов И и сумматора, первый и второй входы и выход блока элементов ИЛИ соединены соответственно с выходами восьмого и девятого блоков элементов И, входом элемента НЕ и вторыми входами пятого блока элементов ИЛИ, первого блокаэлементов И и сумматора, вторые входыс второго по пятый блоков элементов И соединены соответственно с выходами элемента НЕ, пятого блока элементов ИЛИ, первого блока элементов И и сумматора, выход переноса которого соединен с вторым входом пятого элемента И, информационный вход блока соединен с вторым входом первого блока И. 3. Микропроцессор по п. 1, о т -л и ч а ю щ и й с я тем, что блокформирования адреса и признака переноса содержит дешифратор микроннструкций, дешифратор модификации, два элемента ИЛИ, пять элементов И, элемент НЕ, два триггера, дешифратор чтения, семь блоков элементов И, два блока элементов ИЛИ, регистр, информационный вход, синхровход, вход сброса и выход которого соединены соответственно с выходом первого блока элементов ИЛИ, синхровходом блока, входом начальной установки блока, выходом адреса блока, первая группа выходов второго блока элементов ИЛИ соединена с входами дешифратора микроинструкций, с первого по Б-й выходы второй группы второго блока элементов ИЛИ соединены с первого по Б-й входами (где Б - разрядность адреса блока) первого блока элементов И, с первого по (Б+1)-й выходы второй группы второго блока элементов Й соединены с первого по (Б)-й входами второго, третьего и четвертого блоков элементов И, (Б+1)-й вход и выход первого блока элементов И соединены соответственно с первым выходом дешифратора микроинструкций, первым входом первого блока элементов ИЛИ, Б-й, (Б+1)-й входы и выход второго блока элементов И соединены соответственно с вторым выходом дешифратора микроинструкций, входом1290340 10 9признака переноса блока, вторым входом первого блока элементов ИЛИ, И-й, (И+1)-й входы и выход третьего блока элементов И соединены соответственно с третьим выходом дешифратора микроинструкций, выходом первого триггера, третьим входом первого блока элементов ИЛИ, Б-Й, (И+1)-й входы и выход четвертого блока элементов И соединены соответственно с четвертым выходом дешифратора микро- инструкций, выходом второго триггера, четвертым входом первого блока элементов ИЛИ, первый и второй входы и выход пятого блока элементов И соединены соответственно с пятым выходом дешифратора микроинструкций, информационным входом блока, пятым входом первого блока элементов ИЛИ, первый, второй входы и выход шестого блока элементов И соединены соответственно с входом управления адресом блока, выходом элемента НЕ, первым входом второго блока элементов ИЛИ, первый вход и выход седьмого блока элементов И соединены соответственно с выходом дешифратора модификации, вторым входом второго блока элементов ИЛИ, первый второй входы и выход первого элемента И соединены соответственно с выходом первого элемента ИЛИ, входом разрешения модификации адреса блока, входом элемента НЕ и вторым входом седьмого блока элементов И, первые, вторые и третьи входы дешифратора модификации и первого элемента ИЛИ соединены по-. парно и подключены соответственно к входу модификации адреса по признаку запрета записи блока, входу модификации адреса по признаку отсутствия сегмента памяти блока, входу модиФикации адреса по признаку неверного кода команды блока, первый, второй, третий входы и выход второго элемента ИЛИ соединены соответственно с первым выходом дешифратора чтения,выходом второго элемента И, выходомтретьего элемента И, выходом признака блока, первый и второй входы вто рого элемента И соединены соответственно с вторым выходом дешифраторачтения и выходом первого триггера,первый и.второй входы третьего эле-.мента И соединены с третьим выходомдешифратора чтения и выходом второготриггера, информационные входы перво.го и второго триггеров соединены свходом признака переноса блока, первый вход четвертого и инверсный входпятого элементов И, второй вход четвертого и прямой вход пятого элементов И соединены попарно и подключенысоответственно к входу управлениязаписью признака переноса и синхровходу блока, выходы четвертого и пятого элементов И соединены соответственно с синхровходами первого и второго триггеров, вход дешифратора чтения соединен с входом управления чтением признака переноса блока, блокконтроля адреса содержит дешифратор,первую и вторую группы элементов И,первый и второй блоки элементов ИЛИ,выходы которых являются соответственно первым и вторым выходами бпока,входы первого и второго блоков элементов ИЛИ соединены соответственнос выходами элементов И первой и второй групп, вход управления, записьюблока соединен с первыми входамиэлементов И первой группы, вход и выходы дешифратора соединены соответственно с входом контролируемой информации блока, вторыми входамй элементов ИЛИ первой и первыми входами элементов ИЛИ второй групп, первая ивторая группы информационных входовблока соединены соответственно с третьими входами элементов И первойгруппы и вторыми входами элементовИ второй группы.290340 окаХ ГлояаХ Составитель А. Афанасьеведактор И. Рыбченко ТехредЛ.Сердюкова Корректор Аю 0 бручар аказ 7904/48 венно-полиграфическое предприятие, г, У оектная, 4 извод Тираж 673 ВНИИПИ Государственно по делам изобретен 13035, Иосква, Ж, к и уш Подписноетета СССРкрытийя наб., д

СмотретьЗаявка

3893972, 02.04.1985

ПРЕДПРИЯТИЕ ПЯ В-8185

ГРИШИН ВЛАДИМИР АЛЕКСЕЕВИЧ, ЯРОШЕВСКИЙ ПАВЕЛ ЮРЬЕВИЧ, ГЕНИНА ЗИНАИДА ЯКОВЛЕВНА

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/8-1290340-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для сопряжения источника и приемника информации

Следующий патент: Управляющий процессор

Случайный патент: 343465