Формирователь тестов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

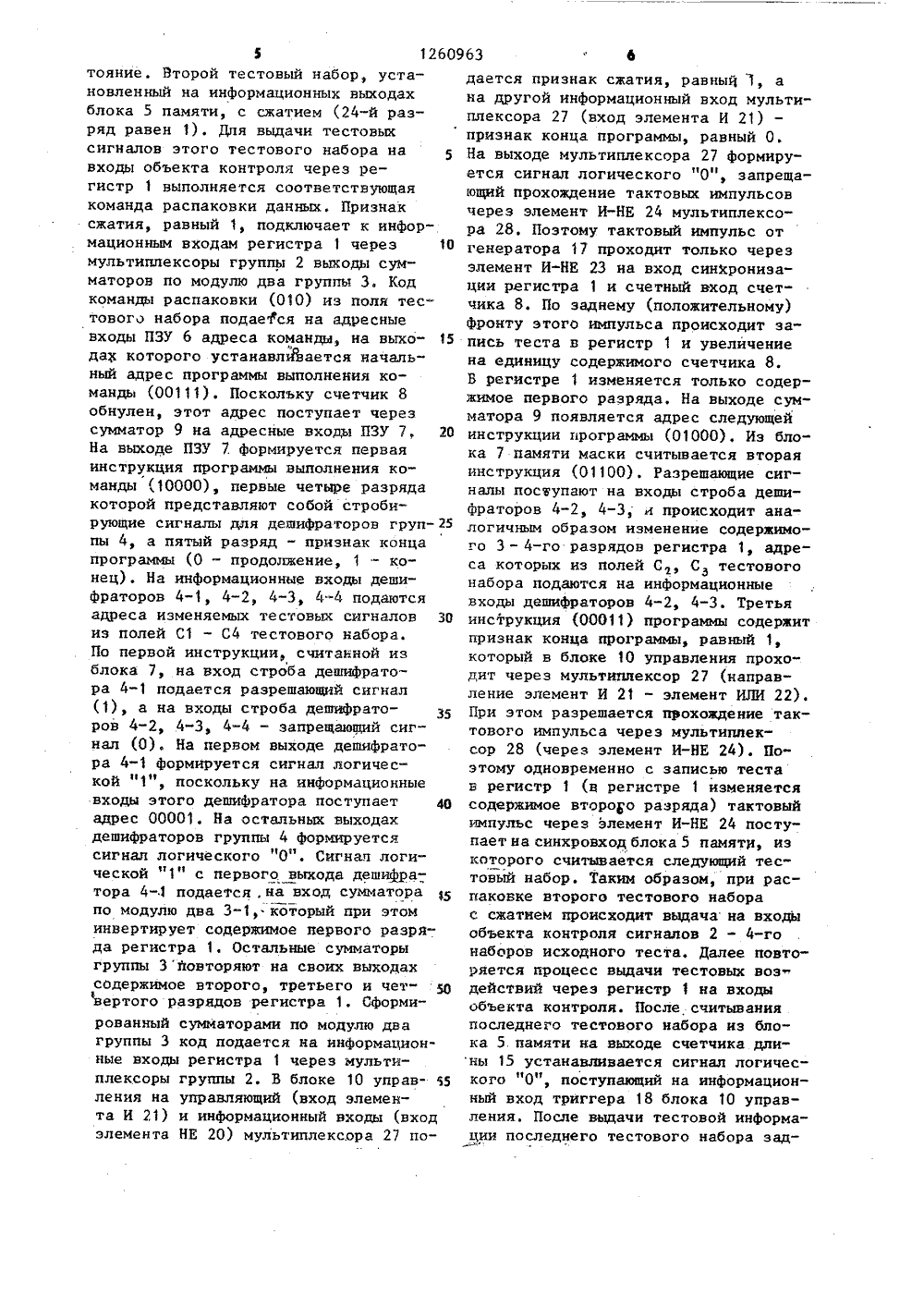

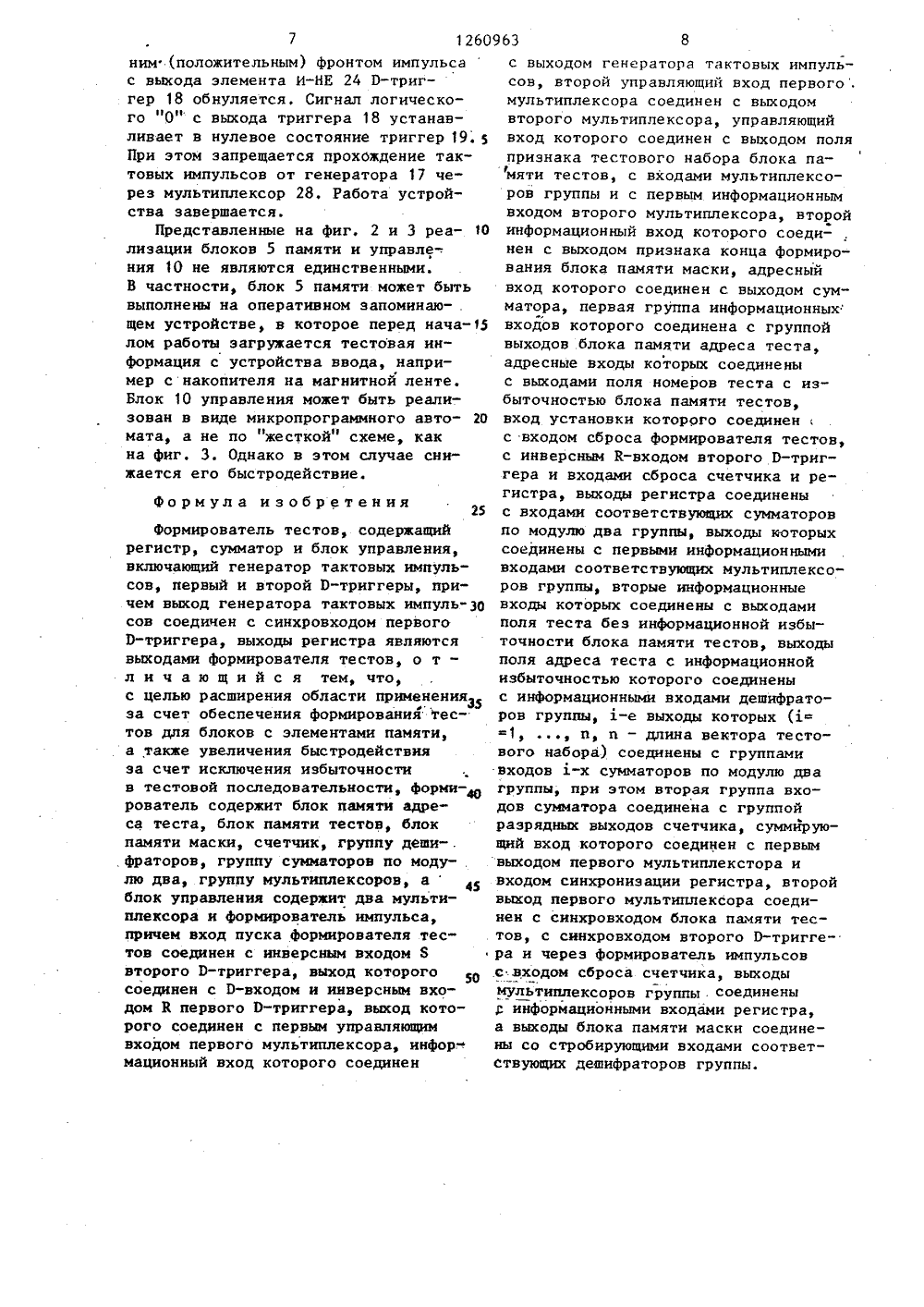

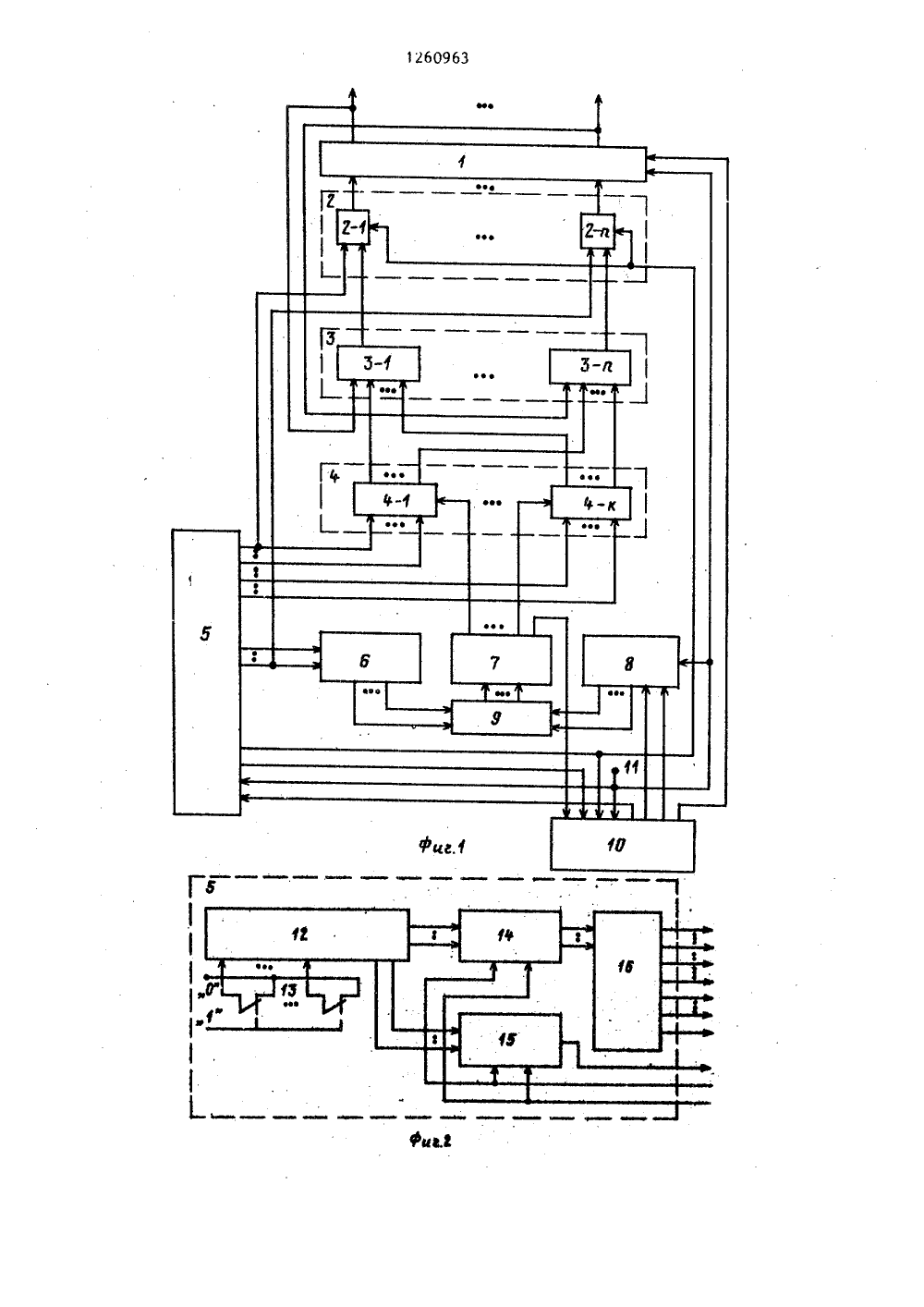

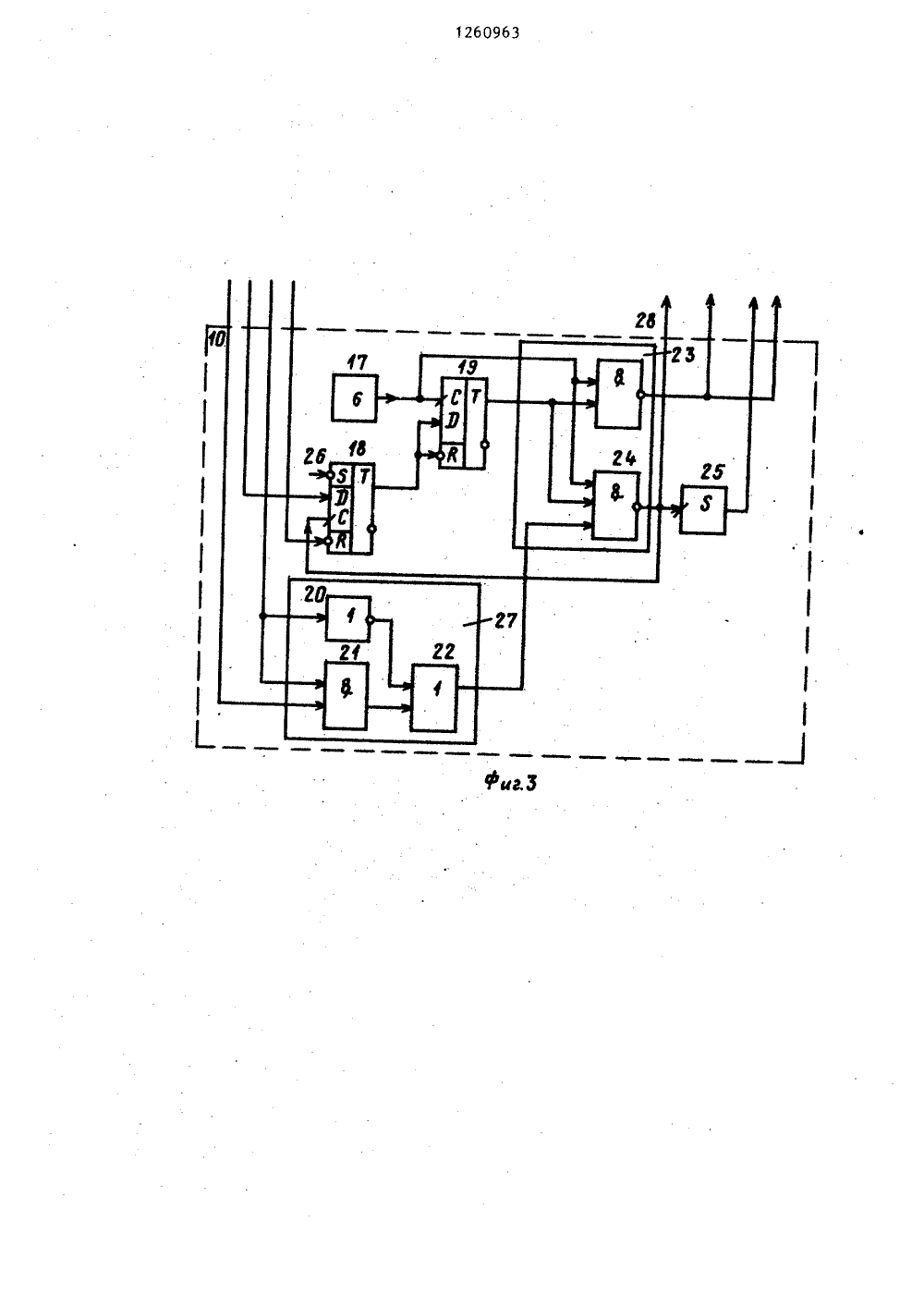

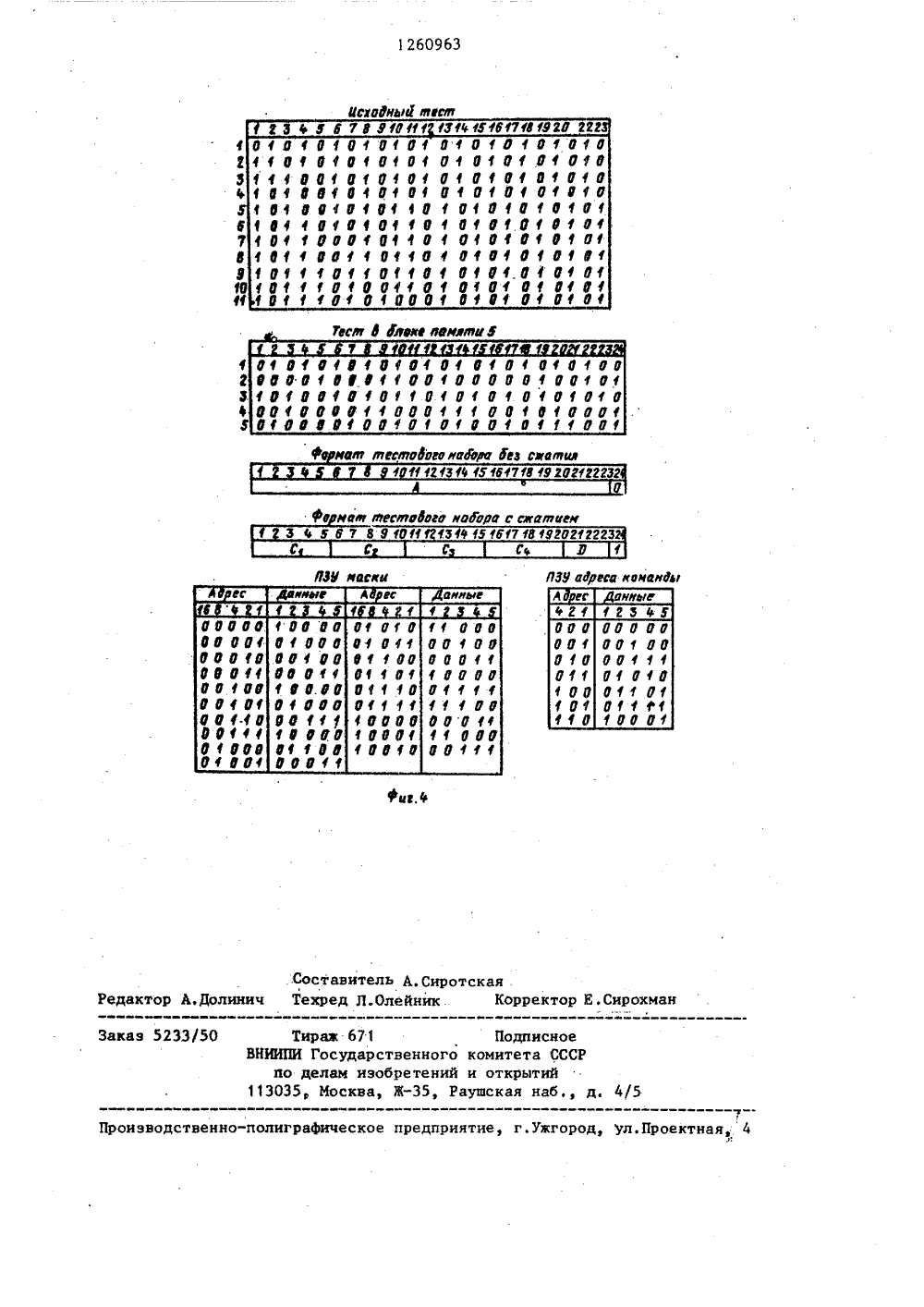

(Ю 4 СО 1 26 ПИСАНИЕ ИЗОБРЕТЕН ЕЛЬС СВ АВТОРСК(56)В 91АвУ 911 ство СССР 14, 1982. во СССР 26, 1980,с ф ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ(57) Изобретение относится к вычислительной технике и может быть использовано для формирования тестовыхвоздействий при контроле функциони"рования и локализации неисправностей цифровых узлов и блоков вычислительных машин. Цель иэобретевия -расширение области применения эасчет обеспечения формирования тестовдля блоков с элементами памяти,а также увеличение быстродействия эа счет исключения "избыточности"в тестовой последовательности. Дляпоследовательностных схем в процессе формирования тестовых воздействий возможно одновременное изменениелишь небольшого числа входных сигналов. Поэтому в тексте один наборвходных сигналов отличается от предыдущего в небольшом числе разрядов.Такие текстовые последовательностимогут быть подвергнуты сжатию, чтопозволяет сократить объем памяти, служащей для хранения тестовой информации. Поэтому в тест входят тестовые наборы двух типов - тестовый набор без информационной избыточности(без сжатия) и тестовый набор с информационной избыточностью (сжатием).формирователь содержит регистр,группу мультиплексоров, группу сумматоров по модулю два, блок управления, счетчик, блок памяти маски,группу дешифраторов. 4 ил.Изобретение относится к вычислительной технике и может быть использовано для формирования тестовых воздействий при контроле функционирования и локализации неисправюостей цифровых узлов и блоков вычислительныхмашин.Цель изобретения - расширениеобласти применения за счет обеспе 10чения формирования тестов для блоков,содержащих элементы памяти, а такжеувеличение быстродействия за счетисключения избыточности тестовой последовательности.На фиг. 1 приведена структурная15схема формирователя тестов; нафиг. 2 - блок памяти; на фиг. 3 -блок управления; на фиг. 4 - примерформирования тестовой последователь 20ности.Формирователь тестов содержитрегистр 1, группу 2 мультиплексоров,включающую мультиплексоры 2-1,2-22-п (и - число входов контролируемого объекта), группу 3 сумматоров по модулю два, включающую сумматоры 3-1, 3-23-и по модулю два,группу 4 дешифраторов, включающуюдешифраторы 4-1, 4-2 4-1 си+1(об - - 1 с+1 где ш - целое числоф Утакое, что шс Год (и+1)ш),блок 5 памяти, блок 6 памяти адресатеста, блок 7 памяти маски, счетчик 8.сумматор 9, блок 10 управления, 35вход 11 сброса (см, фиг. 1).Блок 5 памяти содержит ПЗУ 12 адреса и длины теста, переключатели 13адреса, счетчик 14 адреса, счетчик 15длины и ПЗУ 16 тестов (см, фиг. 2). 40Блок 10 управления содержит генератор 17 тактовых импульсов, триггеры 18 и 19, элемент НЕ 20, элемент И 21, элементы ИЛИ 22, элемен"ты И-НЕ 23 и 24, формирователь 25 импульсов и вход 26 пуска, мультиплексоры 27 и 28 (см. фиг. 3)Все узлы формирователя тестов могут быть выполнены на интегральныхмикросхемах, в частности регистр 1 - 50на К 155 П 8, ПЗУ 6, 7, 12 - на 155 РЕЗ,счетчики 8, 14, 15 - на К 155 ИЕ 7, сумматор 9 - на К 155 ИИЗ, ПЗУ 16 - наК 556 РТ 5, триггеры 18 19 - на К 155 ТМ 2,формирователь 25 импульсов - на 55К 155 АГЗ.Формирователь работает следующимобразом. Тестовые последовательности сигналов, подаваемые на входы объектовконтроля при контроле функционирования и локализации неисправностей,обладают информационной избыточностью.В частности, для наиболее широкогокласса цифровых схем, которыми являются последовательные схемы, в процессе формирования тестовых воздействий возможно одновременное изменение лишь небольшого числа входныхсигналов. Поэтому в тесте один наборвходньы сигналов отличается от преды-дущего в небольшом числе разрядов.Такие тестовые последовательностимогут быть подвергнуты сжатию, чтопозволяет сократить объем памяти запоминающих устройств, служащих дляхранения тестовой информации. В блоке 5 памяти тест хранится в виде последовательности тестовых наборов.Каждый тестовый набор занимает однуячейку памяти в (и+1) бит. В тест вхо-дят тестовые наборы двух типов: тестовый набор без информационной избы"точности (без сжатия) и тестовый набор с информационной избыточностью(с сжатием). Тестовый набор безсжатия имеет следующие функциональные поля:А - и - разрядный код, каждыйразряд которого определяет состояниесоответствующего входного сигналаобъекта контроля;В = 0 - признак отсутствия сжатия.Тестовый набор со сжатием имеетследующие функциональные поля:СтфС ш - Разрядныеадреса изменяемых тестовых сигналов;Р-Ь) - разрядный код команды,выполняемой устройством при распа-ковке сжатого тестового набора;В = 1 - признак сжатия.Для описания работы формирователявведем обозначения:Т; - 1-й тестовый набор в тесте;е; - хэммингово (кодовое) расстояние тестового набора Т; от тестовогонабора Т;, (1.=1, , я, где я - число тестов формирователя),Сжатию может быть подвергнута такая последовательность тестовых наборов Т , Т Тр (р2), для котоффВурррой выполняется условие: Я 1. с 1 с.11=1Будем называть совокупность ее. е структурой последовательности тестовых наборов Т ТвТрРассмотрим последовательность тестовых наборон, для которых выполняетсяРусловие1.=1. Число структур та:1 к- :5ких последовательностей Я=2Например, при =4 0=7 имеются следующие структуры последовательностей:1,1,1,1 1,1,2 1,2,1 2,1,1 1,33,1 2,2. Каждая структура в процессе выдачи тестовых сигналовиз блока 5 памяти нз нходыобъекта контроля распаковываетсяпутем выполнения формирователемсвоей команды, код которой хранится в поле 0 тестового набора с сжатием. Сжатые последовательности тестовых наборов, для которых 2 111,:1распаковываются с помощью этих жекоманд. Например, структура 1,1,1может быть распакована той же командой, что и структура 1, 1,2, толькон последнем поле С тестового наборас сжатием записывается несуществующийадрес изменяемого тестового сигнала.На фиг. 4 приведен пример сжатияисходного теста при п=23 (1=4, ш=5),показаны содержимое блока 5 памяти,форматы тестовых наборов без сжатия 30и с сжатием, содержимое блока 7,ПЗУ 6 адреса команды, Рассмотрим работу формирователя на этом конкретном примере,Перед началом работы в блоке 5 35памяти на переключателях адреса 13устанавливается номер выбираемоготеста, который поступает на адресные,входы ПЗУ 12. На выходах ПЗУ 12 появляются коды начального адреса и 40длины теста, которые поступают соответственно на информационные входысчетчика 14 и счетчика 15. Для приведения в исходное состояние узлови блоков формирователя на вход 11 45сброса подается сигнал логического"0". По этому сигналу в блоке 5 памяти происходит запись начальногоадреса теста в счетчик 14 адресаи кода длины теста в счетчик 15 длины. По адресу, сформированному счетчиком 14, из ПЗУ 16 тестов считается первый тестовый набор, По этомужесигналу сбрасываются в нулевое сос-,тояние регистр 1 и счетчик 8, в кото рый записывается нулевая комбинация.В блоке 10 управления устанавливается в нулевое состояние 0-триггер 18,сигнал логического 0 с прямого выхода которого сбрасывает в нулевоесостояние 0-триггер 19. В свою очередь сигнал логического "0" с прямого выхода 0-триггера 19 запрещаетпрохождение тактовых импульсов от генератора, 17 через элементы И-НЕ 23,24 мультиплексора 28, Начало работыформирователя задается сигналом логического "0", подаваемым на вход 26пуска. Этот сигнал в блоке 10 управления устанавливает Р-триггер 18н единичное состояние. Сигнал логической "1" с прямого выхода Р-триггера 18 поступает на 0-вход Р-триггера 19, который по переднему (положительному) фронту тактового импульса от генератора 17 переводитсяв единичное состояние и разрешаетпрохождение тактовых импульсов от генератора 17 через мультиплексор 28(элементы И-НЕ 23, 24), В выбранномтесте первый тестовый набор без сжатия (см. Фиг. 4). Признак сжатия(24-й разряд тестового набора), равный О, поступает с выхода блока 5памяти на управляющий вход мультиплексора 27 (входы элементов НЕ 20и И 21 блока 10 управления). В результате на выходе мультиплексора 27формируется сигнал логической "1",поступающий на информационный входмультиплексора 28 (вход элемента ИНЕ 24), Признак сжатия поступает также на синхровходи мультиплексоровгруппы 2, обеспечивающих подключениек информационным входам регистра 1информационных выходов блока 5 памяти (разряды 1. - 23 тестового набора).В блоке 10 управления тактовый импульс от генератора 17 проходит через мультиплексор 28 (элемент И-НЕ 23) на вход синхронизации регистра 1 и осуществляют в него записьпервого набора тестовых сигналовЭтот же тактовый импульс проходитчерез элемент И-НЕ 24 на счетныевходы счетчиков 14, 15 и увеличивает содержимое счетчика 14 на единицуи уменьшает содержимое счетчика 15на единицу. На выходе ПЗУ 16 тестовпоявляется второй тестовый набор, Импульс с выхода элемента И-НЕ 24 поступает также на вход формирователя 25 импульсов, на выходе которогопо заднему (положительному) фронтуформируется короткий импульс, устанавливающий счетчик 8 в нулевое сос 5 12609 тояние. Второй тестовый набор, установленный на информационных выходах блока 5 памяти, с сжатием (24-й разряд равен 1). Для выдачи тестовых сигналов этого тестового набора на входы объекта контроля через регистр 1 выполняется соответствующая команда распаковки данных, Признак сжатия, равный 1, подключает к информационным входам регистра 1 через 10 мультиплексоры группы 2 выходы сумматоров по модулю два группы 3. Код команды распаковки (010) из поля тестового набора подается на адресные входы ПЗУ б адреса команды, на выхо дах которого устанавливается начальный адрес программы выполнения командь (00111). Поскольку счетчик 8 обнулен, этот адрес поступает через сумматор 9 на адресные входы ПЗУ 7, 20 На выходе ПЗУ 7 формируется первая инструкция программы выполнения команды (10000), первые четыре разряда которой представляют собой стробирующие сигналы для дешифраторов груп пы 4, а пятый разряд " признак конца программы (О - продолжение, 1 - ко" нец). На информационные входы дешифраторов 4-1, 4-2, 4"3, 4-4 подаются адреса изменяемых тестовых сигналов 30 иэ полей С 1 - С 4 тестового набора. По первой инструкции, считанной из блока 7, на вход строба дешыратора 4-1 подается разрешающий сигнал ( 1), а на входы строба дешифраторов 4-2, 4-3, 4-4 - запрещающий сигнал (0). На первом выходе дешифратора 4-1 Формируется сигнал логической "1", поскольку на информационные входы этого дешифратора поступает 40 адрес 00001. На остальных выходах дешифраторов группы 4 формируется сигнал логического "0", Сигнап логической "1" с первого выхода дешифра" тора 4-.1 подается,на вход сумматора 15 по модулю два 3-1,- который при этом инвертирует содержимое первого разряда регистра 1, Остальные сумматоры группы 3 повторяют на своих выходах содержимое второго, третьего и четвертого разрядов регистра 1. Сформированный сумматорами по модулю два группы 3 код подается на информационные входы регистра 1 через мультиплексоры группы 2. В блоке 10 управ ления на управляющий (вход элемента И 21) и информационный входы (вход элемента НЕ 20) мультиплексора 27 подается признак сжатия, равньщ 1, а на другой информационный вход мультиплексора 27 (вход элемента И 21) признак конца. программы, равный О. На выходе мультиплексора 27 формируется сигнал логического "0", запрещающий прохождение тактовых импульсов через элемент И-НЕ 24 мультиплексора 28. Поэтому тактовый импульс от генератора 17 проходит только через элемент И-НЕ 23 на вход синхронизации регистра 1 и счетный вход счетчика 8. По заднему (положительному) фронту этого импульса происходит запись теста в регистр 1 и увеличение на единицу содержимого счетчика 8. Б регистре 1 изменяется только содержимое первого разряда, На выходе сумматора 9 появляется адрес следующей инструкции программы (01000), Из блока 7 памяти маски считывается вторая инструкция (01100), Разрешающие сигналы поступают на входы строба дешиФраторов 4-2, 4-3, и происходит аналогичным образом изменение содержимого 3 - 4-го разрядов регистра 1, адреса которых из полей С, С тестового набора подаются на информационные входы дешифраторов 4-2, 4-3. Третья инструкция (00011) программы содержит признак конца программы, равный 1, который в блоке 10 управления проходит через мультиплексор 27 (направление элемент И 21 - элемент ИЛИ 22), При этом разрешается прохождение тактового импульса через мультиплексор 28 (через элемент И-НЕ 24), По" этому одновременно с записью теста в регистр 1 (в регистре 1 изменяетсясодержимое второо разряда) тактовый импульс через элемент И-НЕ 24 поступает на синхровход блока 5 памяти, из которого считывается следующий тес" товый набор. Таким образом, при распаковке второго тестового набора с сжатием происходят выдача на входы объекта контроля сигналов 2 - 4-го наборов исходного теста. Далее повторяется процесс выдачи тестовых воз действий через регистр 1 на входы объекта контроля. После считывания последнего тестового набора из блока 5 памяти на выходе счетчика длины 15 устанавливается сигнал логического "0", поступающий на информационный вход триггера 18 блока 10 управления, После выдачи тестовой информации последнего тестового набора зад 7 1260 ним (положительным) фронтом импульса с выхода элемента И-НЕ 24 П-триггер 18 обнуляется. Сигнал логического "О" с выхода триггера 18 устанавливает в нулевое состояние триггер 19. 5 При этом запрещается прохождение тактовых импульсов от генератора 17 через мультиплексор 28, Работа устройства завершается,Представленные на фиг, 2 и 3 реа лизации блоков 5 памяти и управле-.ния 10 не являются единственными.В частности, блок 5 памяти может быть выполнены на оперативном запоминаю- . щем устройстве, в которое перед нача лом работы загружается тестовая информация с устройства ввода, например с накопителя на магнитной ленте. Блок 10 управления может быть реализован в виде микропрограммного авто мата, а не по "жесткой" схеме, как на фиг. 3. Однако в этом случае снижается его быстродействие.формула изобретенияформирователь тестов, содержащийрегистр, сумматор и блок управления,включающий генератор тактовых импульсов, первый и второй Э-триггеры, причем выход генератора тактовых импуль"ЗОсов соединен с синхровходом первогоВ-триггера, выходы регистра являютсявыходами формирователя тестов, о т -л и ч а ю щ и й с я тем, что,с целью расширения области примененияза счет обеспечения формирования тестов для блоков с элементами памяти,а также увеличения быстродействияза счет исключения избыточностив тестовой последовательности, форинОрователь содержит блок памяти адреса теста, блок памяти тестов, блокпамяти маски, счетчик, группу деши- ., фраторов, группу сумматоров по модулю два групду мультиплексорова 45блок управления содержит два мультиплексора и формирователь импульса,причем вход пуска формирователя тестов соединен с инверсным входом 8второго О-триггера, выход которогосоединен с Р-входом и инверсным входом К первого П-триггера, выход которого соединен с первым управлякяцимвходом первого мультиплексора, информационный вход которого соединен 9 бЗс выходом генератора тактовых импульсов, второй управляющий вход первого, мультиплексора соединен с выходом второго мультиплексора, управляющий вход которого соединен с выходом поля признака тестового набора блока памяти тестов, с входами мультиплексоров группы и с первым информационным входом второго мультиплексора, второйв информационный вход которого соединен с выходом признака конца формирования блока памяти маски, адресный вход которого соединен с выходом сумматора, первая группа информационных входов которого соединена с группой выходов блока памяти адреса теста, адресные входы которых соединены с выходами поля номеров теста с избыточностью блока памяти тестов, вход установки которого соединен: с входом сброса формирователя тестов, с инверсньм К-входом второго 0-триггера и входами сброса счетчика и регистра, выходы регистра соединены с входами соответствующих сумматоров по модулю два группы, выходы которых соединены с первыми информационными входами соответствующих мультиплексоров группы, вторые информационные входы которых соединены с выходами поля теста без информационной избыточности блока памяти тестов, выходы поля адреса теста с информационной избыточностью которого соединены с информационными входами дешифраторов группы, 1-е выходы которых (1и, и - длина вектора тестового набора) соединены с группами входов д-х сумматоров по модулю два группы, при этом вторая группа входов сумматора соединена с группой разрядных выходов счетчика, суммйрующий вход которого соединен с первым выходом первого мультиплекстора и входом синхронизации регистра, второй выход первого мультиплексора соединен с синхровходом блока памяти тестов, с синхровходом второго 0-триггера и через формирователь импульсов с входом сброса счетчика, выходы мультиплексоров группы . соединены ,с информационными входами регистра, а выходы блока памяти маски соединены со стробирующими входами соответствующих деаифраторов группы.1 260963 Исеадный ееее ИУ адрееа конандв Составитель А Техред Л.Олей ская Корректор Е.Сирохман Редактор А,Долин Тирам 671 Государс по делам изо 13035, Москва, одписноетета СССРкрытийая наб., д,венного кретений иЖ, Раув ВН КИПИ ул. Проектная,4 изводственно-полиграфическое предприятие, г.ужгор Ф 7 б У 10 41 й 3 Ф 0 8 7 Ю 846444 48444846474 ВИХО йИ 04010104 0404 01040104040 11 04 010104 01 01 0104,01 040 111 ЮО 1010104 04 0401 04010 1 01 В 01 01 01 04 01 04 01 01040 4 б 1 Ю Р 4 0 4 01 1 О 4 01 0 1 Ю 4 О 1 О 4б 11010101101 0101040404 1 01 10001 011 О 1 0101 01 0104 1014 0041 04101 01010104 04 1011101101101 0101.01 04 01 401 4 4 04 О 011 01 0101 01 01 04 1011104 010001 0104 01 0404

СмотретьЗаявка

3891146, 30.04.1985

ПРЕДПРИЯТИЕ ПЯ А-3756

БОГДАНОВ ВЯЧЕСЛАВ ВСЕВОЛОДОВИЧ, ЛУПИКОВ ВИКТОР СЕМЕНОВИЧ, СПИВАКОВ СЕРГЕЙ СТЕПАНОВИЧ

МПК / Метки

МПК: G06F 11/26

Метки: тестов, формирователь

Опубликовано: 30.09.1986

Код ссылки

<a href="https://patents.su/8-1260963-formirovatel-testov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь тестов</a>

Предыдущий патент: Устройство для тестового контроля временных соотношений

Следующий патент: Устройство для визуального контроля исполнения программ

Случайный патент: Устройство для раздачи жидкости, например, горючего, тракторам