Устройство для формирования тестов логических блоков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1388874

Автор: Мазур

Текст

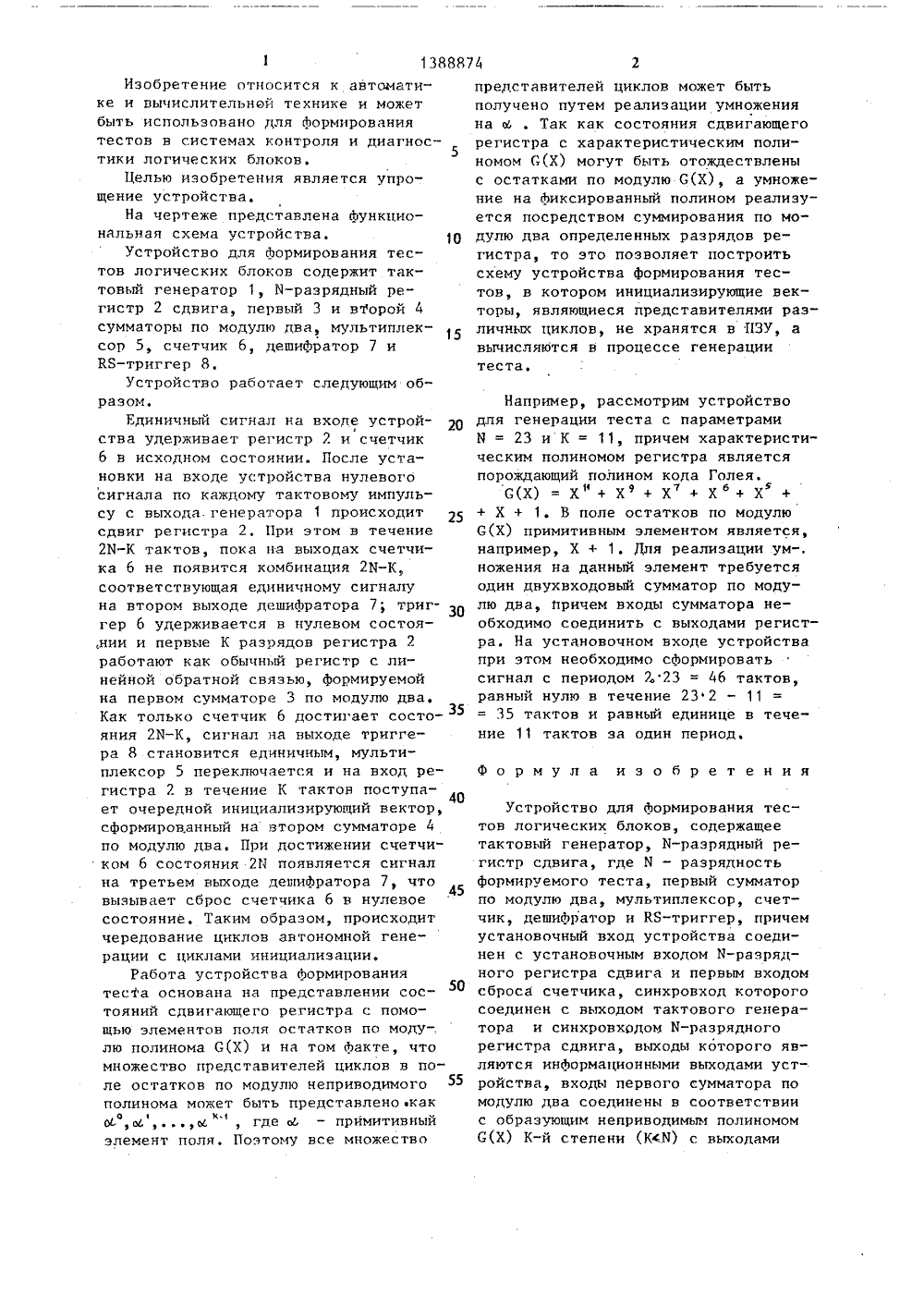

СОЮЗ СОВЕТСНИСОЯИАЛИСТИЧЕСНРЕСПУБЛИК А 1 И 9) (11) 1)4 С 06 Р 1 ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 11/24-24.88. Бюл. )1 14 льное конструктор го и камневого ст е нко азур(088,8)ское свидетельствкл, С Об Р 11/00,апзасС 1 оп оп сотпрР 9, Бер. 1984,СССР 1979. йегз,84554) УСТРОЕСТОВ ЛОГИ57) Изобр ВО ДЛЯ ФОРМИРОВАНИЯСКИХ БЛОКОВ тение относится к авто числительной технике и матике и может бы использовано для Йо ми ования тесто системах контрол ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(21) 41250 (22) 29.0 (46) 15.04 (71) Специ бюро часо строения (72) Е.И.М (53) 681.(56) Авто В 792256,1 ЕЕЕ Т чо 1. С849 и диагностики логических блоков. Пелью изобретения является упрощениеустройства. Устройство содержит тактовый генератор 1, И-разрядный регистр 2 сдвига, где И - разрядностьформируемого теста, первый и второйсумматоры по модулю два 3, 4, мультиплексор 5, счетчик 6, дешифратор 7и КБ-триггер 8, За счет введения второго сумматора по модулю два с соответствующими связями устройство впроцессе формирования очередногофрагмента теста одновременно вычисляет вектор инициализации для следующего фрагмента. После окончанияцикла автономной генерации фрагментатеста производится цикл инициализации, далее указанные циклы чередуются до достижения необходимой полнотысформированного теста. 1 ил,Изобретение относится к автоматике и вычислительной технике и можетбыть использовано для формированиятестов в системах контроля и диагностики логических блоков.5Целью изобретения является упрощение устройства.На чертеже представлена функциональная схема устройства. 1 ОУстройство для формирования тестов логических блоков содержит тактовый генератор 1, Б-разрядный регистр 2 сдвига, первый 3 и вТорой 4сумматоры по модулю два, мультиплексор 5, счетчик 6, дешифратор 7 иКБ-триггер 8,Устройство работает следующим образом.Единичный сигнал на входе устройства удерживает регистр 2 и счетчик6 в исходном состоянии. После установки на входе устройства нулевогосигнала по каждому тактовому импульсу с выхода. генератора 1 происходитсдвиг регистра 2, При этом в течение2 И-К тактов, пока на выходах счетчика 6 не появится комбинация 2 М-К,соответствующая единичному сигналуна втором выходе дешифратора 7; триг Огер 6 удерживается в нулевом состоя,нии и первые К разрядов регистра 2работают как обычный регистр с линейной обратной связью, формируемойна первом сумматоре 3 по модулю два.Как только счетчик 6 достигает состояния 2 И-К, сигнал на выходе триггера 8 становится единичным, мультиплексор 5 переключается и на вход регистра 2 в течение К тактов поступает очередной инициализирующий вектор,сформированный на втором сумматоре 4по модулю два. При достижении счетчиком 6 состояния 2 И появляется сигнална третьем выходе дешифратора 7, чтовызывает сброс счетчика 6 в нулевоесостояние. Таким образом, происходитчередование циклов автономной генерации с циклами инициализации,Работа устройства формированиятеста основана на представлении состояний сдвигающего регистра с помощью элементов поля остатков по моду-.лю полинома С(Х) и на том факте, чтомножество представителей циклов в поле остатков по модулю неприводимогополинома может быть представлено .какЮ ,осюс , где о 6 - примитивныйэлемент поля. Поэтому все множество представителей циклов может быть получено путем реализации умножения на м, . Так как состояния сдвигающего регистра с характеристическим поли- номом С(Х) могут бить отождествлены с остатками по модулю С(Х), а умножение на фиксированный полином реализуется посредством суммирования по модулю два определенных разрядов регистра, то это позволяет построить схему устройства формирования тестов, в котором инициализирующие векторы, являющиеся представителями различных циклов, не хранятся в ПЗУ, а вычисляются в процессе генерации теста.Например, рассмотрим устройство для генерации теста с параметрами В = 23 и К = 11, причем характеристическим полиномом регистра является порождающий полином кода Голея.С(Х) =Х +Х+Х +Хб+Х + + Х + 1. В поле остатков по модулю С(Х) примитивным элементом является, например, Х + 1. Для реализации ум-. ножения на данный элемент требуется один двухвходовый сумматор по модулю два, причем входы сумматора необходимо соединить с выходами регистра. На установочном входе устройства при этом необходимо сформировать сигнал с периодом 2,23 = 46 тактов, равный нулю в течение 232 - 1135 тактов и равный единице в течение 11 тактов за один период.Формула изобретенияУстройство для формирования тестов логических блоков, содержащее тактовый генератор, И-разрядный регистр сдвига, где И - разрядность формируемого теста, первый сумматор по модулю два, мультиплексор, счетчик, дешифратор и КЯ-триггер, причем установочный вход устройства соединен с установочным входом И-разрядного регистра сдвига и перным входом сброса счетчика, синхровход которого соединен с выходом тактового генератора и синхровходом Б-разрядного регистра сдвига, выходы которого являются информационными выходами устройства, входи первого сумматора по модулю два соединены в соответствии с образующим неприводимым полиномом С(Х) К-й степени (КИ) с выходами1388874 Составитель С.СтарчихинТехред А.Кравчук Корректор А.Обручар Редактор Е.Копча Заказ 1581/50 Тираж 704 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Подписное Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 И-разрядного регистра сдвига из числа первых К выходов регистра, в том числе сК-М, выход первого сумматора по модулю два соединен с первым ин 5 формационным входом мультиплексора, выход и управляющий вход которого соединен соответственно с информационным входом И-разрядного регистра сдвига и выходом КЯ-триггера, нуле вой и единичный входы которого соединены соответственно с первым и вторым выходами дешифратора, третий выход и входы которого соединены соответственно с вторым входом сброса иразрядными выходами счетчика, о тл и ч а ю щ е е с я тем, что, сцелью упрощения устройства, оно содержит дополнительно второй сумматорпо модулю два, входы которого соединены в соответствии с примитивнымэлементом поля остатков по модулюС(Х) с выходами Н-разрядного регистра сдвига из числа последних К еговыходов, а выход второго сумматорапо модулю два соединен с вторым информационным входом мультиплексора.,

СмотретьЗаявка

4125011, 29.09.1986

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО ЧАСОВОГО И КАМНЕВОГО СТАНКОСТРОЕНИЯ

МАЗУР ЕФИМ ИЛЬИЧ

МПК / Метки

МПК: G06F 11/26

Метки: блоков, логических, тестов, формирования

Опубликовано: 15.04.1988

Код ссылки

<a href="https://patents.su/3-1388874-ustrojjstvo-dlya-formirovaniya-testov-logicheskikh-blokov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования тестов логических блоков</a>

Предыдущий патент: Устройство для контроля логических блоков

Следующий патент: Устройство для адресации блоков памяти

Случайный патент: Автомобиль-контейнеровоз для перевозки баллонов со сжиженным газом