Устройство для сопряжения процессоров через общую память в многопроцессорной системе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1231508

Авторы: Головин, Денищенко, Ерзаков, Черепьяная

Текст

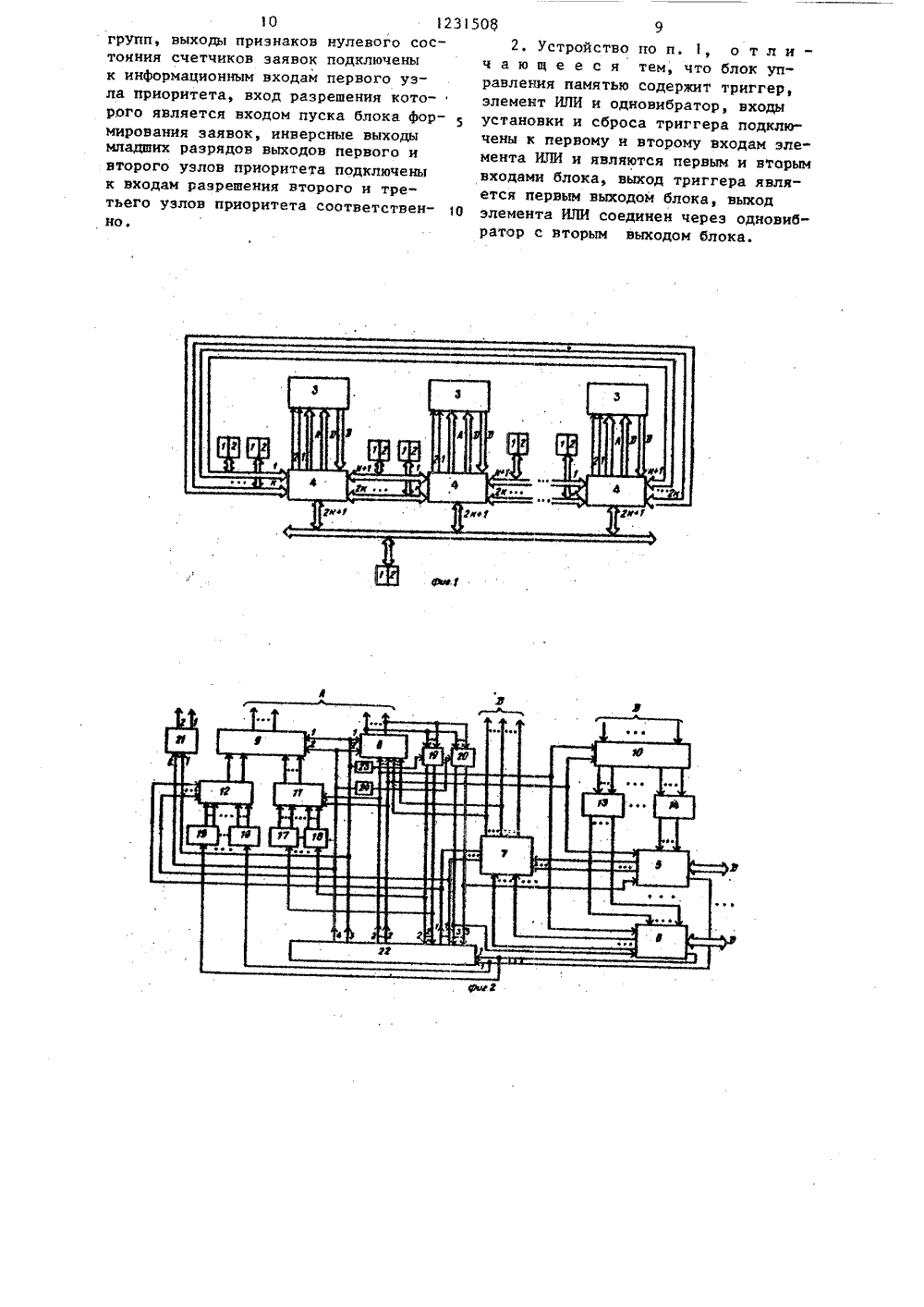

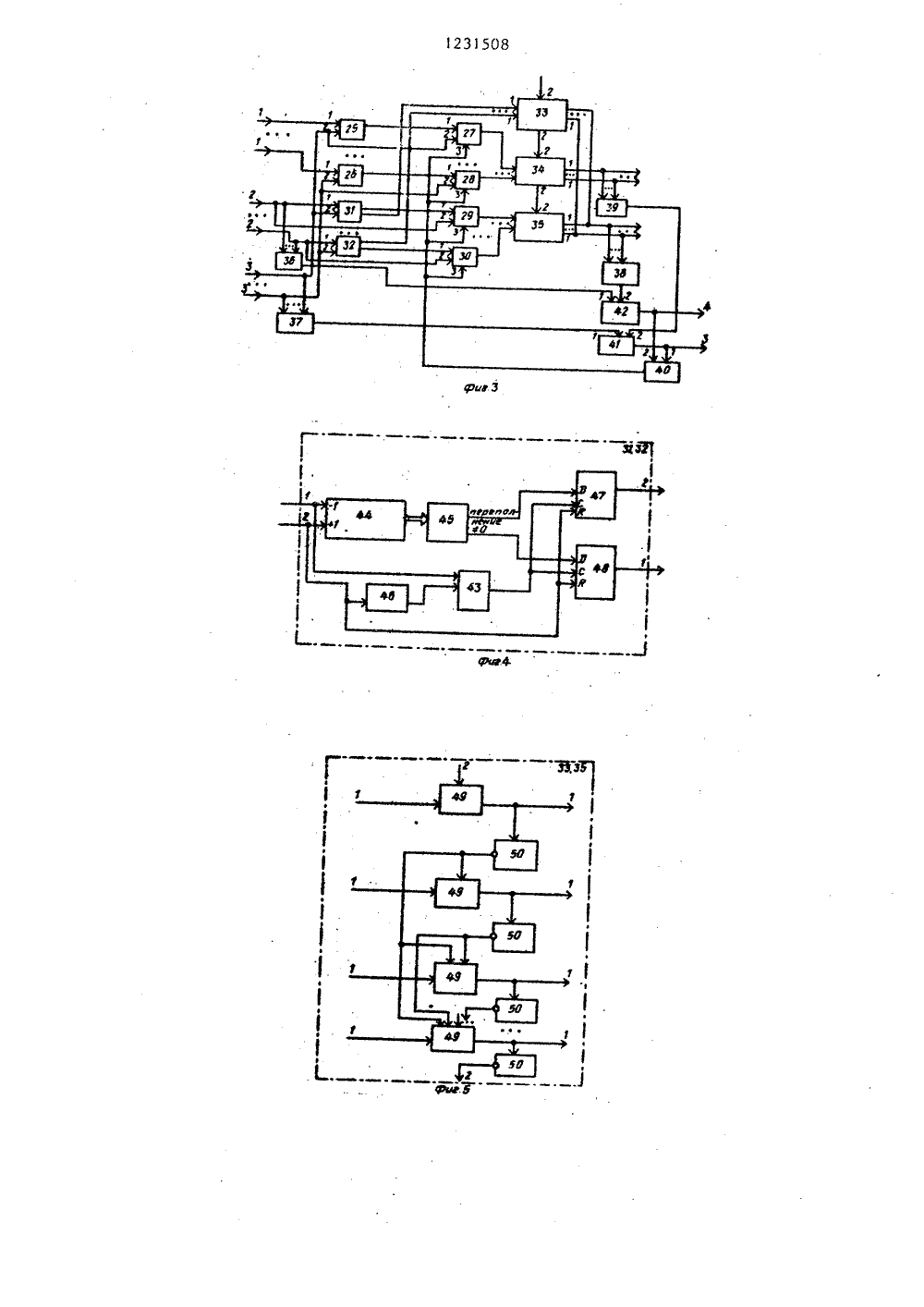

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 09 Ш) 594 С 06 Р 5/1 ГОСУДАРС ПО ДЕЛАМ АНИЕ ИЗОБРЕТЕ ИДЕТЕЛЬСТВ Н АВТОРСКОМ ТНЕННЫЙ НОМИТЕТ СССР ОБРЕТЕНИЙ И ОТКРЫТИЙ(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРО-ЦЕССОРОВ ЧЕРЕЗ ОБЩУЮ ПАМЯТЬ В МНОГОПРОЦЕССОРНОЙ СИСТЕМЕ(57) Изобретение позволяет реализовывать многопроцессорные системы свысоким быстродействием эа счет органиэации асинкронного обращенияпроцессоров через общую памятьКон.струкция предлагаемого устройствасодержит 2 К+ блоков ввода-вывода,где К определяется количеством подключаемых к устройству процессоров,пять мультиплексоров, демультиплексор, 2 К+1 регистров, 2 К+1 счетчиковадреса записи, 2 К+1 счетчиков адресасчитывания, дешифраторы сброса записанной и считанной заявки, блок управления памятью, блок формированиязаявок и два элемента задержки. Работа устройства происходит в двух режимах записи и считывания заявок.1 з.п. ф-лы. 8 ил, 1 табл.123508 Код типа Уф МП информации (5 бит) (3 бита),Информация(8 бит) Запрещена 000 001 РезервнаяДанные (байт Иф 1)Данные (байт У 2)Номер инструкции 010 ф 0 011 100 11 О 50 111 Номер данного Изобретение относится к вычислительной технике и может быть использовано н автоматизированных системах управления для сопряжения процессоров.Целью изобретения является повышение быстродействия.На фиг. 1 приведен пример блоксхемы многопроцессорной системы сиспользованием устройстна для сопряжения процессоров, на фиг, 2функциональная схема устройства длясопряжения процессоров, на Фиг. 3-6 -функциональные схемы блока формировайия заявок, счетчика сообщений, уз-ла приоритета и блока управления памятью соответственно на фиг. 7 и8 - примеры алгоритмов управленияместного и центрального процессоровсоответственно н составе многопроцессорной системы,Многопроцессорная система (Фиг,1)содержит микропроцессоры (МП) 1,одиниз которых центральный, местные оперативные запоминающие устройства(ОЗУ) 2, общие ОЗУ 3, устройства 4для сопряжения процессоров через общую память.Устройство 4 для сопряжения процессоров (фиг. 2) содержит с первого5 по (2 К+1) 6 блоков ввода-вынода,где К определяется количеством подключаемых МП подключенных к устройству 4, с первого по третий мультиплексоры 7-9, демультиплексор 10,четвертый 11 и пятый 12 мультиплексоры, с первого 13 по (2 К+1) 14 регистры, с первого 15 по (2 К+1) 16счетчики адреса записи, с первого17 по (2 К+1) 8 счетчики адреса считывания, дешифраторы 9 и 20 сбросазаписанной и считанной заявки соответственно, блок 21 управления памятью, блок 22 формирования заявок,дна элемента 23 и 24 задержки.Блок 22 Формиронания заявок(фиг. 3) содержит первую, вторую итретью группы триггеров, н которыхсоответственно обозначены первый и2 К+1 триггеры 25 и 26, 27 и 28, 29 и30, с первого по 2 К+ счетчики 31 и32 заявок, три узла 33-35 приоритета,пять элементов ИЛИ 36-40, дна триггера 41 и 42.Каждый счетчик 31 и 32 заявок(фиг, 4) содержит элемент ИЛИ 43,ренерсинный счетчик 44, дешифратор45, элемент 46 задержки, дна триггера 47, 48. ъКаждый узел 33-35 приоритета,(фиг. 5) содержит группу элементовИ 49 и группу элементов НЕ 50.Блок 21 управления памятью 5 (Фиг. 6) содержит однонибратор 51,элемент ИЛИ 52 и триггер 53Вычислительная система (фиг. ), .использующая предложенное устройство, работает следующим образом,С помощью магистрали системы воперативное запоминающее устройство(034)2 центрального МП 1 записываются содержание инструкции, котороенеобходимо выполнить, и исходныеданные, которые необходимы для вы"полнения инструкции. Под управлени"ем центрального МП с помощью устройства 4 для сопряжения производитсяперепись содержания инструкций и исходных,данных к ним в ОЗУ 3 общегопользования, например, следующимисообщениями: Код типа информации определяет назначение информации согласно следу 30 ющей таблицы,Код типа Назначение информацииинформации Программа инструкции(байт У 2) В начале передается номер инструкции, программа выполнения инструкции, а потом номер данных и его значения в ниде байта Ви байта В 2. Обращение центрального МП 1 к соответствующему устройству 4 происходит последовательно н порядке, опредеВ режиме ."Запись" данные, которые необходимо записать в ОЗУ 3, посту,пают в блоки 5, 6 под управлением соответствующего местного МП 1, что сопровождается выработкой сигнала логической "1" по выходу квитирования. С выхода блоков 5, 6 данные поступают иа информационные входы перЭО вого мультиплексора 7. При выполнении заявки на запись сообщения в ОЗУ 3 по одному иэ выходов адреса записываемой заявки блока 22 вырабатывается сигнал логической "1", который разрешает прохожчение требуемых данных на выходы первого мультиплексора 7 и первые информационные входы второй группы второго мультиплексора 8. На выходе признака записи бло"- а 22 формируется сигнал логической "1", который устанавливает второй и третий мультиплексоры 8 и 9 в состояние "Запись" при котором на выход второго мультиплексора 8 поступает ,информация с его информационных вхо дов второй группы, а на выход третьего мультиплексора 9 поступает информация с его первого информационного входа. Код с выходов второго и третьего мультиплексоров 8 и 9 образует 50 адрес, по которому в ОЗУ 3 производится запись данных, которые посту" :пают с выходов первого мультиплексора 7. После цикла записи, который формируется блоком 21 на выходе вто рого дешифратора 20, соответствующего адресу записанного сообщения, вырабатывается сигнал логической "1" 25 1231ленном выполняемой инструкцией Каждое устройство 4 может принимать сообщения одновременно от 2 К+1 местных ОЗУ 2 под управлением соответствующих МП 1. Запись принятых сообщений в соответствующие секции ОЗУ 3 общего пользования происходит последовательно в соответствии с установленным приоритетом. Для каждого МП 1 в ОЗУ 3 отведена отдельная секция па О мяти, которая находится по номеру МП, указанному в сообщении. Далее записанные в ОЗУ 3 сообщения последовательно считываются в устройство 4 в порядке установленного приорите та. Из устройства 4 передача сообщений в необходимые ОЗУ 2 происходит асинхронно под управлением соответствующих МП 1.Устройство 4 работает в режимах 20 "Запись и "Считывание". 508 4который поступает, на соответствующий вход сброса записанной заявки блока 22 и сбрасывает заявку на запись сообщения в ОЗУ 3.В режиме Считывание при выполнении заявки на считывание сообщения из ОЗУ 3 по одному иэ выходов адреса (, жтываемой заявки блока 22 вырабатывается сигнал логической "1 который разрешает передачу требуемых данных на соответствующие выходы демультиплексора 10 для записи в соответствующий регистр 13, 14 и информации со входов четвертого мультиплексора 11 на его выход, а также формирование требования в блоки 5 и б на вывод считанной информации. На выходе признака записи блока 22 формируется сигнал логической "1", который устанавливает второй (8) и третий (9) мультиплексоры в режим Считывание, при котором на выход второго мультиплексора 8 поступает информация с его информационных входов первой группы, а на выход третьего мультиплексора 9 - информация с его второго информационного входа. Код с выходов второго и третьего мультиплексоров 8 и 9 образует адрес, по которому происходит считывание данных иэ ОЗУ 3 на информационные входы демультиплексора 10 и далее в соответствующий регистр 13, 14. После окончания цикла считывания, который формирует блок 21, на выходе первого дешифратора 19, соответствующего адресу считанного сообщения, вырабатывается сигнал логической1 , который поступает на соответствующий вход сброса считанной заявки блока 22 и сбрасывает заявку на считывание сообщения из ОЗУ. В блоках 5, б вырабатывается требование прерывания в унифицированную магистраль для соответствующего МП 1, который в удобное для него время произведет считывание сообщения из соответствующего регистра 13, 14 независимо от работы устройства 4,Блок 22 формирования заявок (фиг, 3) работает следующим образом.Заявки на запись сообщения в ОЗУ 3 поступают по входам заявок на запись и запоминаются в триггерах первой группы 25, 26, Далее при наличии сигнала логической "1" с выхода пятого элемента ИЛИ 40 они переписываются в триггеры второй группы 27, 28, с выходов которых по31508 6 5 10 15 20 30 35 40 15 50 55 В 12 ступают на информационные входы второго узла 34 приоритета. Аналогично поступают заявки на считывание сообщений иэ ОЗУ 3 на информационные входы первого узла 33 приоритета с выходов признаков ненулевого состояния счетчиков 31, 32 заявок и на информационные входы третьего узла 35 приоритета с выходов признаков переполнения счетчиков 31, 32 заявок. С помощью трех узлов 33-35 приоритета определяется заявка., которую необходимо обслужить в данный момент. Если обслуживается заявка на запись, сообщения в ОЗУ 3, то на одном из выходов второго узла 34 вырабатывается сигнал логической "1", по которому Формируется требование прерыва.ния в соответствующую унифицированную магистраль, связанную с устройством 4, и сигнал логической "1" на выходе четвертого элемента ИЛИ 39. Триггер 41 устанавливается в состояние логической "1", с выхода которого через элемент ИЛИ (40) вырабатывается сигнал логической "1", который запрещает последующий ввод информации в триггеры второй и третьей групп 27, 28 и 29, 30,цо окончания цикла записи. После окончания цикла записи по одному из входов сброса записанной заявки блока 22 поступает сигнал логической "1", который сбрасывает указанную заявку на запись сообщения в ОЗУ 3. С выхода второго элемента ИЛИ 37 вырабатывается сигнал логической "1", который . устанавливает триггер 41 в состояние логического "О", разрешая с по-, мощью пятого элемента ИЛИ (40) прием новой информации в триггеры второй и третьей групп 27 28 и 29, 30. Одновременно с заявками на запись сообщения в ОЗУ 3 поступают заявки иа считывание сообщения из ОЗУ 3, выполнение которых менее приоритетно. Количество заявок на считывание сообщений из ОЗУ 3, поступающих на первые входы счетчиков 31, 32 заявок, подсчитывается и если они есть и их количество не превышает допустимой величины, то с выходов признаков неравенства нулю соответствующих счетчиков 31, 32 вырабатывается заявка на считывание (сигнал логической "1"), которая аналогично укаэанному запоминается в триггерах третьей группы 29, 30. С выхода триггеров 29, 30 заявка насчитывание поступает на информационные входы третьего узла 35 приори"тетаПри обслуживании заявки на счи"тывание сообщения из ОЗУ 3 на одномиэ выходов третьего узла 35 приоритета вырабатывается сигнал логичес"кой "1", который поступает навыходы адреса считываемой заявкиблока 22 и формирует на выходе третьего элемента ИЛИ 38 сигнал логической "1", который устанавливаеттриггер 42 в состояние логической"1" и запрещает прием новой информации в триггеры второй и третьейгрупп После окончания цикла считывания по одному иэ входов сброса считанной заявки вырабатывается сигналлогической "1", который уменьшаетна единицу содержание соответствующего счетчика 31-32 заявок. В предлагаемом устройстве обеспе" чена возможность одновременного асинхронного обращения 2 К+1 микропроцессоровк устройству 4 для записи или считывания информации. Формула изобретения Устройство для сопряжения процессоров через общую память в многопроцессорной системе, содержащее с первого по третий мультиплексоры, демультиплексор, 2 К+1 регистров, где К число подключаемых процессоров, два элемента задержки, блок формирования заявок и блок управления памятью, о т л и ч а ю щ е е с я тем, что, с целью повьппения быстродействия, в него введены 2 К+1 блоков вво-, да-вывода, четвертый и пятый мультиплексоры, 2 К+1 счетчиков адреса записи, 2 К+1 счетчиков адреса считыва" ния, первый и второй дешифраторы, входы-выходы сообщений блоков ввода- вывода являются входами-выходами шин обмена устройства, выходы сообщений блоков ввода-вывода подключены к информационным входам первого мультиплексора, выход которого является выходом сообщений, записываемых в общую память устройства, информационньгй вход демультиплексора является входом сообщений, считываемых из общей памяти устройства, выходы демуль.типлексора подключены к информационным входам регистров, выходы которых подключены к входам сообщений231508 соответствующих блоков ввода-вывода,выходы квитирования которых подключены к входам заявок на запись блок 4формирования заявок и к счетньв входам соответствующих счетчиков адреса записи, выходы которых подключены к информационным входам пятогомультиплексора, выход которого подключен к первому информационномувходу третьего мультиплексора, выход 10которого является выходом группы разрядов адреса ячейки общей памяти устройства, выходы второго дешифратораподключены к входам сброса записанной заявки блока формирования заявок 15и к входам разрешения приема соответствующих блоков ввода-вывода, выходы первого дешифратора"подключенык входам сброса считанной заявкиблока формирования заявок и к счетным входам соответствующих счетчийов адреса считывания, выходы которых подключены к информационным входам четвертого мультиплексора, выходкоторого подключен к второму информационному входу третьего мультиплексора, выходы адреса записываемойзаявки блока формирования заявок подключены к входам управления первогои пятого мультиплексоров, выходы ад- Зореса считываемой заявки подключенык входам управления четвертого мультиплексора, к информационным входампервой группы второго мультиплексора и к входам разрешения передачи соответствующих блоков ввода-вывода,выход признака записи блока формирования заявок подключен к первым входам управления второго и третьегомультиплексоров, к первому входу блока управления памятью и через первый элемент задержки - к входу стробирования первого дешифратора, выход признака считывания блока формирования заявок подключен к вторым 45входам управления второго и третьего мультиплексоров, к второму входублока управления памятью и через вто"вой элемент задержки - к входу стробирования второго дешифратора, первый и второй выходы блока управления памятью являются выходами режима й стробирования общей памяти устройства соответственно, выходы разрядов адреса выхода первого мультиплексора подключены к информационным входам второй группы второгомультиплексора, выходы которого подключены к входам первого.и второгодешифраторов и являются выходамигруппы разрядов адреса секции общейпамяти устройства, причем блок формирования заявок содержит три группы триггеров, группу счетчиков заявок, три узла приоритета, пять элементов ИЛИ и два триггера, входыустановки триггеров первой группыявляются входами заявок на записьблока формирования заявок, входысброса триггеров третьей группы соединены с вычитающими входами соответствующих счетчиков заявок группы, с входами первого элемента ИПИи являются входами сброса считанной заявки блока формирования заявок, входы сброса триггеров первойгруппы соединены с входами сбросасоответствующих триггеров второйгруппы, суммирующими входами соответствующих счетчиков заявок группы, свходами второго элемента ИЛИ и являются входами сброса записанной заявки блока формирования заявок, выходы триггеров первой группы подключены к информационным входам соответствующих триггеров второй группы, выходы которых подключены к информационным входам второго узлаприоритета, выходы которого,подключены к входам четвертого элемента ИЛИ и являются выходами адреса записываемой заявки блока формирования заявок, выходы переложения счетчиков заявок группы подключены к информационным входам соответствующих триггеров третьей группы, выходы которых подключены к информационным входам третьего узла приоритета, выходы которого поразрядно объединены через МОНТАЖКОЕ ИЛИ с входами первого узла приоритета и подключены к входам третьего элемента ИЛИ и являются выходами адреса считываемой заявки блока формирования заявок, выходы первого и второго элементов ИЛИ подключены к входам установки первого и второго триггеров соответственно, входы сброса которых подключены к выходам третьего и четвертого элементов ИЛИ соответственно, выходы первого и второго триггеров являются выходами признаков считывания и записи блока формирования заявок н подключены к первому и второму входам пятого элемента ИЛИ, выход которого подключен к входам синхронизации триггеров второй и третьейо гззою 9групп, выходы признаков нулевого сос. Устройство по и. 1, о т л и - тояния счетчиков заявок подключены ч а ю щ е е с я тем, что блок упк информационным входам первого уэ- равления памятью содержит триггер, ла приоритета, вход разрешения кото- элемент ИЛИ и одновибратор, входы рого является входом пуска блока Фор-установки и сброса триггера подклюмирования заявок, инверсные выходы ченц к первому и второму входам элемладших разрядов выходов первого и мента ИЛИ и являются первым и вторым второго узлов приоритета подключены входами блока, выход триггера являк входам разрешения второго и тре- ется первым выходом блока, выход тьего узлов приоритета соответствен О элемента ИЛИ соединен через одновибно. ратор с вторым выходом блока.

СмотретьЗаявка

3744237, 25.05.1984

ПРЕДПРИЯТИЕ ПЯ Г-4746

ЕРЗАКОВ ЕВГЕНИЙ МИХАЙЛОВИЧ, ДЕНИЩЕНКО ИГОРЬ ЯКОВЛЕВИЧ, ГОЛОВИН ВИКТОР ИВАНОВИЧ, ЧЕРЕПЬЯНАЯ ВАЛЕНТИНА ИВАНОВНА

МПК / Метки

МПК: G06F 15/167

Метки: многопроцессорной, общую, память, процессоров, системе, сопряжения

Опубликовано: 15.05.1986

Код ссылки

<a href="https://patents.su/8-1231508-ustrojjstvo-dlya-sopryazheniya-processorov-cherez-obshhuyu-pamyat-v-mnogoprocessornojj-sisteme.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения процессоров через общую память в многопроцессорной системе</a>

Предыдущий патент: Устройство для обмена информацией двух электронно вычислительных машин

Следующий патент: Устройство для моделирования графов

Случайный патент: Способ получения изопропилиден-бис-(п-фениленокси) ди(пропанола-2)