Тестер контроля и диагностики электронных модулей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1396099

Автор: Карлсбрун

Текст

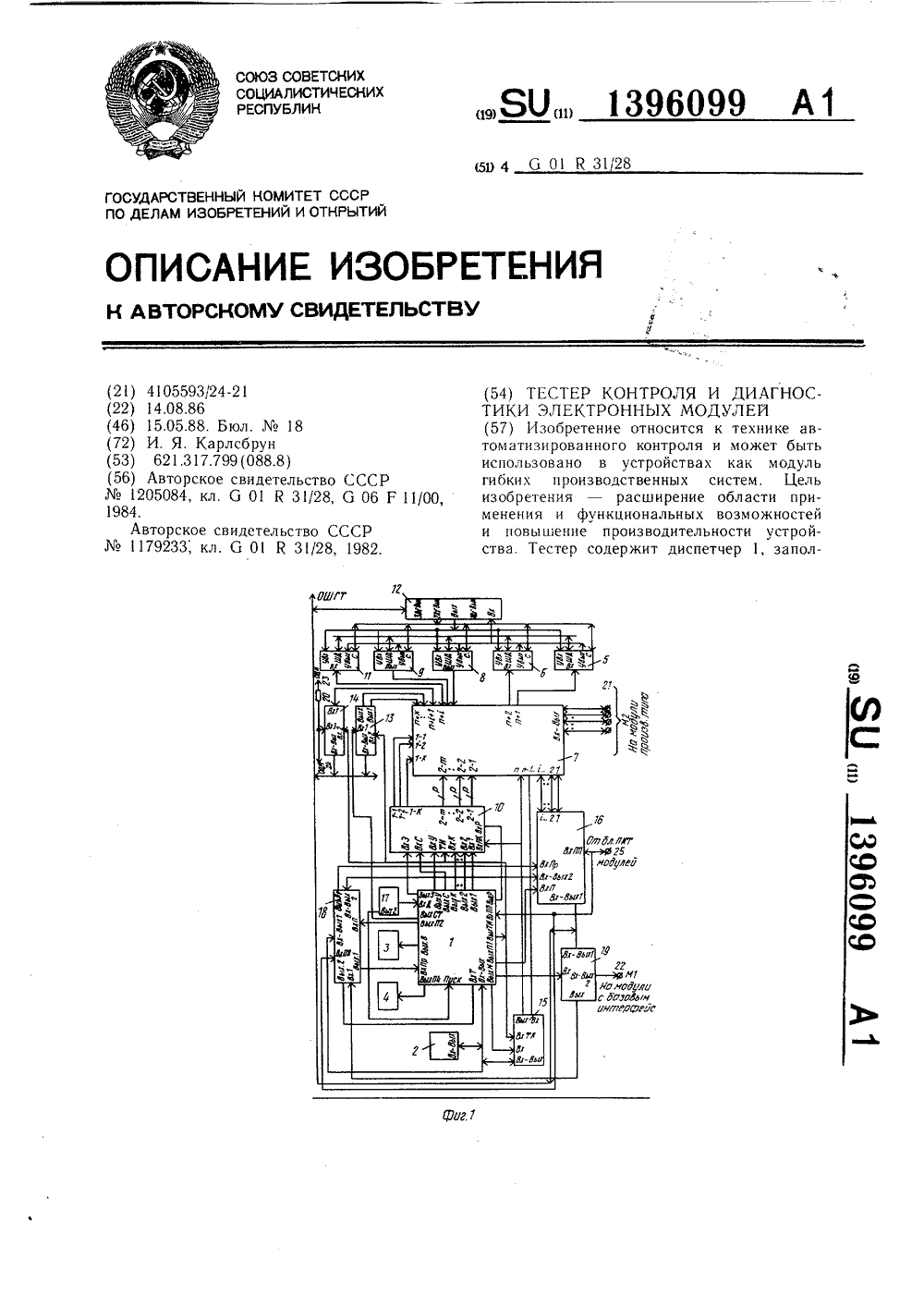

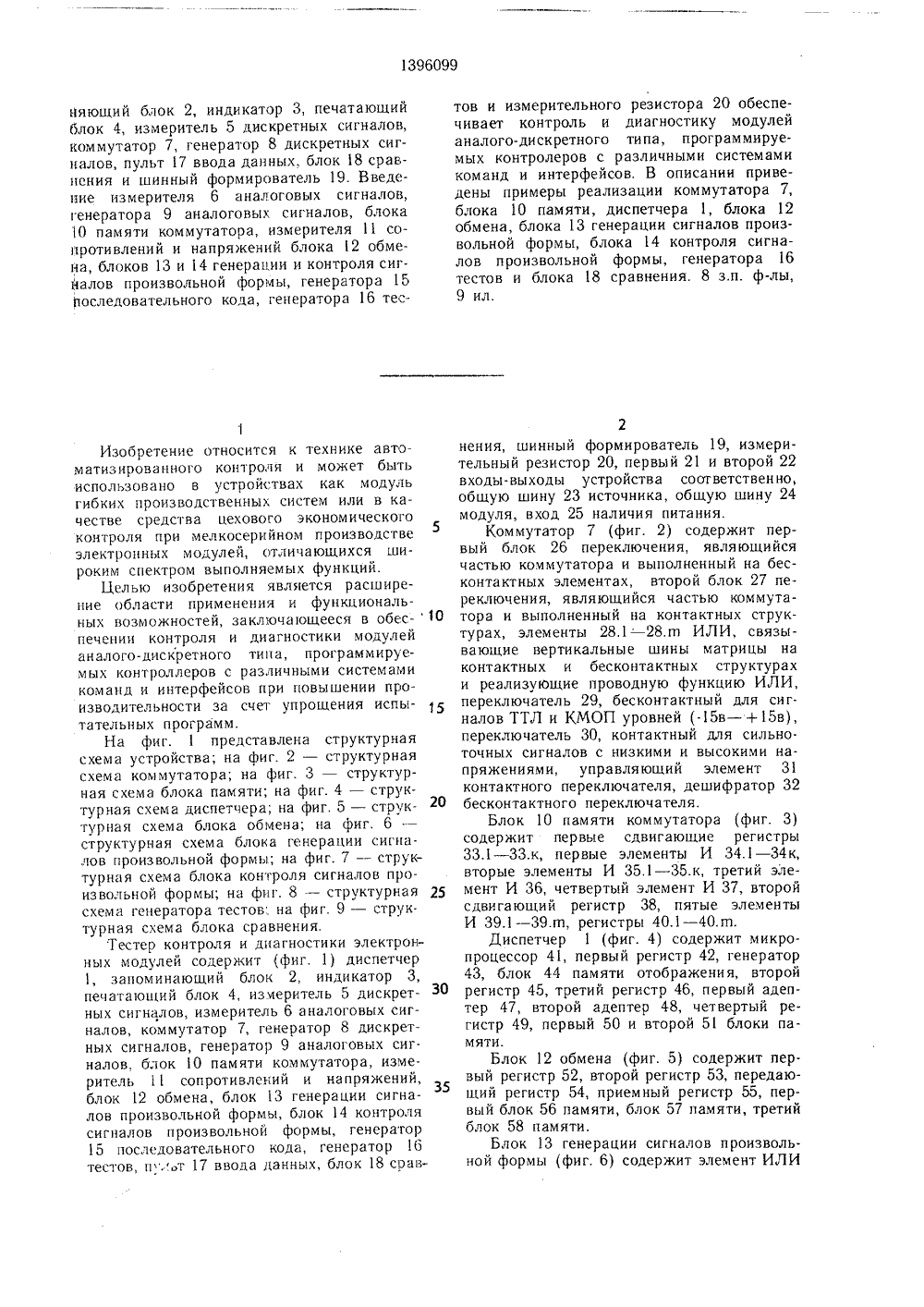

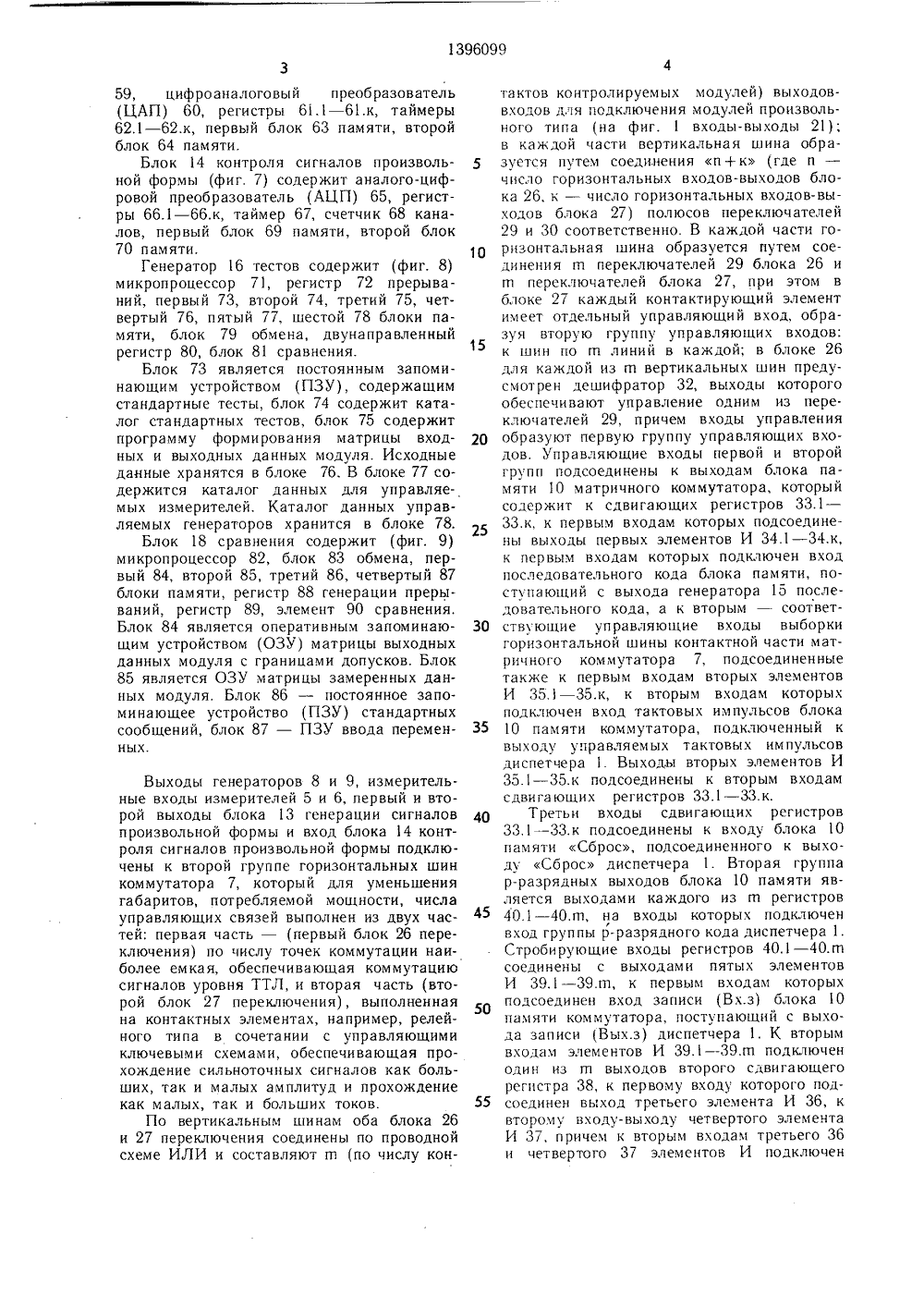

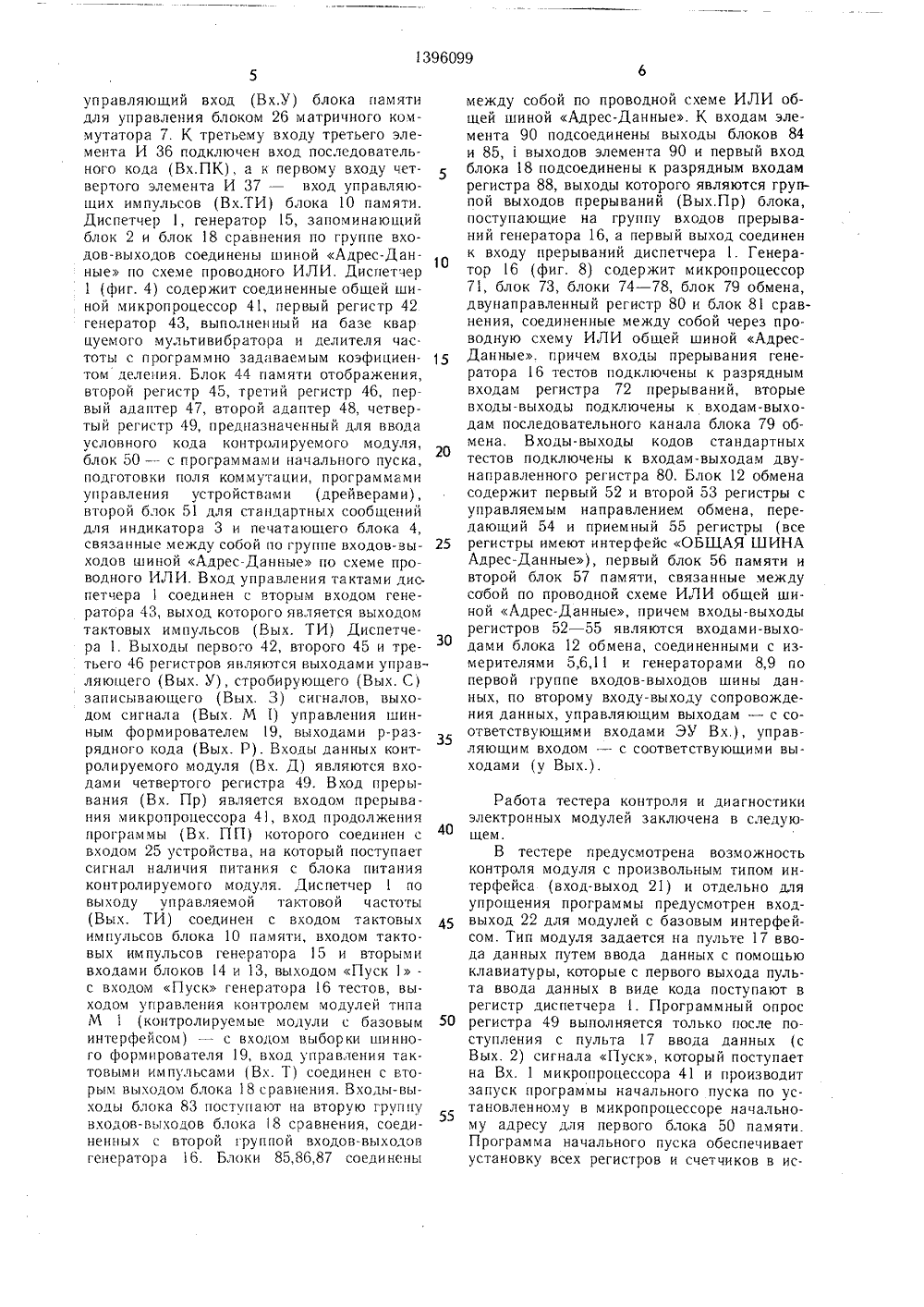

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9 А 1396 О 1 К 31/28 Т СССРОТКРЫТИЙ ОСУДАРСТВЕННЫЙ НОМИ О ДЕЛАМ ИЗОБРЕТЕНИЙ ПИСАНИЕ ИЗОБРЕТЕНИЯВТОРСКОМУ СВИДЕТЕЛЬСТВУ 54) ТИКИ57) И л. 18брун(088.8)видетель01 ЙЗ тво СССР 28, б 06 Р 11/00 тельство СССР 01 К 31/28, 1982.(21) 4105593/24-2 (22) 14,08,86 (46) 15.05.88. Бю (72) И. Я, Карлс (53) 621.317,799 (56) Авторское с1205084, кл. б 1984.Авторское сви1179233; кл, (з том ати исполь гибких изобре менени и повь ства. Т ЕСТЕР КОНТРОЛЯ И ДИАГНОСЭЛЕКТРОННЫХ МОДУЛЕЙ зобретение относится к технике авзированного контроля и может быть овано в устройствах как модульпроизводственных систем. Цель ения - расширение области прия и функциональных возможностейшение производительности устройестер содержит диспетчер 1, запол/Ф упра 3 лениЕ конатанттт ной частью номмутатора 7 асмо такттт имугттаттт орафиг 57/тт й оаслтььо уттраол ол ттитттатга,оюотулей 1 Б т 4,т уль,Уа ген весто 8 Йч диспетчера Яд генерагааро лесгтюР Рб1396099 Рт дл срос нению М Рт Агоева лыг:юлю,с сфлей Хл сройсщюЮ триююгоро T ДЬг о Блок на имущул Ра генератор леетаКМ Пуе,Фа А.тгт 17 слт Ще. Составитель В. СавинТехред И, ВересТираж 772ного комитета СССР по деламосква, )К - 35, Раушская нарафичсское предприятие, г. Уж в едактор Н. Швыдкаяаказ 1974 р 18НИИПИ 1 осударствен113035, МПроизводственно-полиг открытий Ого Ь. лцгпаниямз Рулей Д сосо. устр, У Корректор М. ПожоПодписноеизобретений иб., д. 4/5город, ул. Проектная, 41396099 няющий блок 2, индикатор 3, печатающий блок 4, измеритель 5 дискретных сигналов, коммутатор 7, генератор 8 дискретных сигналов, пульт 17 ввода данных, блок 18 сравнения и шинный формирователь 19. Введение измерителя 6 аналоговых сигналов, генератора 9 аналоговых сигналов, блока 1 О памяти коммутатора, измерителя 11 сопротивлений и напряжений блока 12 обмена, блоков 13 и 14 генерации и контроля сигналов произвольной формы, генератора 15 )последовательного кода, генератора 16 тесИзобретение относится к технике автоматизированного контроля и может быть использовано в устройствах как модуль гибких производственных систем или в качестве средства цехового экономического контроля при мелкосерийном производстве электронных модулей, отличающихся широким спектром выполняемых функций.Целью изобретения является расширение области применения и функциональных возможностей, заключающееся в обес печении контроля и диагностики модулей аналого-дискретного типа, программируемых контроллеров с различными системами команд и интерфейсов при повышении производительности за счет упрощения испытательных программ.На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема коммутатора; на фиг. 3 - структурная схема блока памяти; на фиг. 4 - структурная схема диспетчера; на фиг, 5 - структурная схема блока обмена; на фиг, 6 - структурная схема блока генерации сигналов произвольной формы; на фиг. 7 - структурная схема блока контроля сигналов произ вольной формы; на фи г. 8 - структурная 25 схема генератора тестов, на фиг, 9 - структурная схема блока сравнения.Тестер контроля и диагностики электронных модулей содержит (фиг, 1) диспетчер 1, запоминающий блок 2, индикатор 3, печатаюций блок 4, измеритель 5 дискретных сигналов, измеритель 6 аналоговых сигналов, коммутатор 7, генератор 8 дискретных сигналов, генератор 9 аналоговых сигналов, блок 10 памяти коммутатора, измеритель 11 сопротивлений и напряжений, блок 12 обмена, блок 13 генерации сигналов произвольной формы, блок 14 контроля сигналов произвольной формы, генератор 15 последовательного кода, генератор 16 тестов, и),:т 17 ввода данных, блок 18 сравтов и измерительного резистора 20 обеспечивает контроль и диагностику модулей аналого-дискретного типа, программируемых контролеров с различными системами команд и интерфейсов, В описании приведены примеры реализации коммутатора 7, блока 10 памяти, диспетчера 1, блока 12 обмена, блока 13 генерации сигналов произвольной формы, блока 14 контроля сигналов произвольной формы, генератора 16 тестов и блока 18 сравнения, 8 з,п, ф-лы, 9 ил. 2нения, шинный формирователь 19, измерительный резистор 20, первый 21 и второй 22 входы-выходы устройства соответственно, общую шину 23 источника, общую шину 24 модуля, вход 25 наличия питания.Коммутатор 7 (фиг. 2) содержит первый блок 26 переключения, являющийся частью коммутатора и выполненный на бесконтактных элементах, второй блок 27 переключения, являющийся частью коммутатора и выполненный на контактных структурах, элементы 28.1 - 28.гп ИЛИ, связывающие вертикальные шины матрицы на контактных и бесконтактных структурах и реализующие проводную функцию ИЛИ, переключатель 29, бесконтактный для сигналов ТТЛ и КМОП уровней (-15 в - +15 в), переключатель 30, контактный для сильно- точных сигналов с низкими и высокими напряжениями, управляющий элемент 31 контактного переключателя, дешифратор 32 бесконтактного переключателя.Блок 10 памяти коммутатора (фиг. 3) содержит первые сдвигающие регистры 33.1 - 33.к, первые элементы И 34.1 - 34 к, вторые элементы И 35,1 - 35.к, третий элемент И 36, четвертый элемент И 37, второй сдвигающий регистр 38, пятые элементы И 39.1 - 39 лп, регистры 40.1 - 40,тп.Диспетчер 1 (фиг, 4) содержит микропроцессор 41, первый регистр 42, генератор 43, блок 44 памяти отображения, второй регистр 45, третий регистр 46, первый адептер 47, второй адептер 48, четвертый регистр 49, первый 50 и второй 51 блоки памяти.Блок 12 обмена (фиг, 5) содержит первый регистр 52, второй регистр 53, передающий регистр 54, приемный регистр 55, первый блок 56 памяти, блок 57 памяти, третий блок 58 памяти.Блок 13 генерации сигналов произвольной формы (фиг, 6) содержит элемент ИЛИ59, цифроаналоговый преобразователь (ЦАП) 60, регистры 61.1 - 61.к, таймеры 62.1 - 62,к, первый блок 63 памяти, второй блок 64 памяти.Блок 14 контроля сигналов произвольной формы (фиг, 7) содержит аналого-цифровой преобразователь (АЦП) 65, регистры 66.1 - 66.к, таймер 67, счетчик 68 каналов, первый блок 69 памяти, второй блок 70 памяти.Генератор 16 тестов содержит (фиг. 8) микропроцессор 71, регистр 72 прерываний, первый 73, второй 74, третий 75, четвертый 76, пятый 77, шестой 78 блоки памяти, блок 79 обмена, двунаправленный регистр 80, блок 81 сравнения.Блок 73 является постоянным запоминающим устройством (ПЗУ), содержащим стандартные тесты, блок 74 содержит каталог стандартных тестов, блок 75 содержит программу формирования матрицы входных и выходных данных модуля. Исходные данные хранятся в блоке 76. В блоке 77 содержится каталог данных для управляемых измерителей. Каталог данных управляемых генераторов хранится в блоке 78.Блок 18 сравнения содержит (фиг. 9) микропроцессор 82, блок 83 обмена, первый 84, второй 85, третий 86, четвертый 87 блоки памяти, регистр 88 генерации прерываний, регистр 89, элемент 90 сравнения, Блок 84 является оперативным запоминающим устройством (ОЗУ) матрицы выходных данных модуля с границами допусков. Блок 85 является ОЗУ матрицы замеренных данных модуля. Блок 86 - постоянное запоминающее устройство (ПЗУ) стандартных сообщений, блок 87 - ПЗУ ввода переменных. Выходы генераторов 8 и 9, измерительные входы измерителей 5 и 6, первый и второй выходы блока 13 генерации сигналов произвольной формы и вход блока 14 контроля сигналов произвольной формы подключены к второй группе горизонтальных шин коммутатора 7, который для уменьшения габаритов, потребляемой мощности, числа управляющих связей выполнен из двух частей: первая часть - (первый блок 26 переключения) по числу точек коммутации наиболее емкая, обеспечиваюшая коммутацию сигналов уровня ТТЛ, и вторая часть (второй блок 27 переключения), выполненная на контактных элементах, например, релейного типа в сочетании с управляющими ключевыми схемами, обеспечивающая прохождение сильноточных сигналов как больших, так и малых амплитуд и прохождение как малых, так и больших токов.По вертикальным шинам оба блока 26 и 27 переключения соединены по проводной схеме ИЛИ и составляют гп (по числу кон 5 1 О 15 20 25 30 35 40 45 50 55 тактов контролируемых модулей) выходов- входов для подключения модулей произвольного типа (на фиг. 1 входы-выходы 21); в каждой части вертикальная шина образуется путем соединения и+ к (где и - число горизонтальных входов-выходов блока 26, к - число горизонтальных входов-выходов блока 27) полюсов переключателей 29 и 30 соответственно. В каждой части горизонтальная шина образуется путем соединения гп переключателей 29 блока 26 и гп переключателей блока 27, при этом в блоке 27 каждый контактирующий элемент имеет отдельный управляющий вход, образуя вторую группу управляющих входов: к шин по гп линий в каждой; в блоке 26 для каждой из гп вертикальных шин предусмотрен дешифратор 32, выходы которого обеспечивают управление одним из переключателей 29, причем входы управления образуют первую группу управляющих входов. Управляющие входы первой и второй групп подсоединены к выходам блока памяти 10 матричного коммутатора, который содержит к сдвигающих регистров 33.1 - 33.к, к первым входам которых подсоединены выходы первых элементов И 34.1 - 34.к, к первым входам которых подключен вход последовательного кода блока памяти, поступающий с выхода генератора 15 последовательного кода, а к вторым - соответствующие уп равляющие входы выборки горизонтальной шины контактной части матричного коммутатора 7, подсоединенные также к первым входам вторых элементов И 35 1 - 35 к, к вторым входам которых подключен вход тактовых импульсов блока 10 памяти коммутатора, подключенный к выходу управляемых тактовых импульсов диспетчера 1. Выходы вторых элементов И 35.1 - 35.к подсоединены к вторым входам сдвигающих регистров 33.1 - 33.к,Третьи входы сдвигающих регистров 33.1 - 33.к подсоединены к входу блока 10 памяти Сброс, подсоединенного к выходу Сброс диспетчера 1. Вторая группа р-разрядных выходов блока 10 памяти является выходами каждого из гп регистров 40,1 - 40.т, на входы которых подключен вход группы р-разрядного кода диспетчера 1. Стробирующие входы регистров 40.1 - 40.гп соединены с выходами пятых элементов И 39.1 - 39.гп, к первым входам которых подсоединен вход записи (Вх.з) блока 10 памяти коммутатора, поступающий с выхода записи (Вых.з) диспетчера 1. К вторым входам элементов И 39.1 - 39 лп подключен один из гп выходов второго сдвигающего регистра 38, к первому входу которогоподсоединен выход третьего элемента И 36, к второму входу-выходу четвертого элемента И 37, причем к вторым входам третьего 36 и четвертого 37 элементов И подключенуправляющий вход (Вх.У) блока памяти для управления блоком 26 матричного коммутатора 7. К третьему входу третьего элемента И 36 подключен вход последовательного кода (Вх.ПК), а к первому входу четвертого элемента И 37 - вход управляющих импульсов (Вх.ТИ) блока 10 памяти. Диспетчер 1, генератор 15, запоминающий блок 2 и блок 18 сравнения по группе входов-выходов соединены шиной Адрес-Данные по схеме проводного ИЛИ, Диспетчер 1 (фиг. 4) содержит соединенные общей шиной микропроцессор 41, первый регистр 42 генератор 43, выполненный на базе квар цуемого мультивибратора и делителя час. тоты с программно задаваемым коэфициен 5 10 15 50 55 М 1 (контролируемые модули с базовым интерфейсом) - с входом выборки шинного формирователя 19, вход управления тактовыми импульсами (Вх. Т) соединен с вторым выходом блока 18 сравнения. Входы-выходы блока 83 поступают на вторую группу входов-выходов блока 18 сравнения, соединенных с второй группой входов-выходов генератора 16. Блоки 85,86,87 соединены том деления. Блок 44 памяти отображения, второй регистр 45, третий регистр 46, первый адаптер 47, второй адаптер 48, четвертый регистр 49, предназначенный для ввода условного кода контролируемого модуля, блок 50 - с программами начального пуска, подготовки поля коммутации, программами управления устройствами (дрейверами), второй блок 51 для стандартных сообщений для индикатора 3 и печатающего блока 4, связанные между собой по группе входов-вы ходов шиной Адрес-Данные по схеме проводного ИЛИ, Вход управления тактами диспетчера 1 соединен с вторым входом генератора 43, выход которого является выходом тактовых импульсов (Вых. ТИ) Диспетче.ра 1. Выходы первого 42, второго 45 и третьего 46 регистров являются выходами управляющего (Вых, У), стробирующего (Вых, С) записывающего (Вых. 3) сигналов, выходом сигнала (Вых. М 1) управления шинным формирователем 19, выходами р-разрядного кода (Вых. Р). Входы данных контролируемого модуля (Вх. Д) являются входами четвертого регистра 49. Вход прерывания (Вх. Пр) является входом прерывания микропроцессора 41, вход продолжения программы (Вх. ПП) которого соединен с 40 входом 25 устройства, на который поступает сигнал наличия питания с блока питания контролируемого модуля. Диспетчер 1 по выходу управляемой тактовой частоты (Вых. ТИ) соединен с входом тактовых 45 импульсов блока 10 памяти, входом тактовых импульсов генератора 15 и вторыми входами блоков 14 и 13, выходом Пуск 1- с входом Пуск генератора 16 тестов, выходом управления контролем модулей типа между собой по проводной схеме ИЛИ общей шиной Адрес-Данные, К входам элемента 90 подсоединены выходы блоков 84 и 85, 1 выходов элемента 90 и первый вход блока 18 подсоединены к разрядным входам регистра 88, выходы которого являются группой выходов прерываний (Вых,Пр) блока, поступающие на группу входов прерываний генератора 16, а первый выход соединен к входу прерываний диспетчера 1, Генератор 16 (фиг. 8) содержит микропроцессор 71, блок 73, блоки 74 - 78, блок 79 обмена, двунаправленный регистр 80 и блок 81 сравнения, соединенные между собой через проводную схему ИЛИ общей шиной Адрес- Данные. причем входы прерывания генератора 16 тестов подключены к разрядным входам регистра 72 прерываний, вторые входы-выходы подключены к входам-выходам последовательного канала блока 79 обмена. Входы-выходы кодов стандартных тестов подключены к входам-выходам двунаправленного регистра 80. Блок 12 обмена содержит первый 52 и второй 53 регистры с управляемым направлением обмена, передающий 54 и приемный 55 регистры (все регистры имеют интерфейс ОБ 1 ЦАЯ ШИНА Адрес-Данные), первый блок 56 памяти и второй блок 57 памяти, связанные между собой по проводной схеме ИЛИ общей шиной Адрес-Данные, причем входы-выходы регистров 52 - 55 являются входами-выходами блока 12 обмена, соединенными с измерителями 5,6,11 и генераторами 8,9 по первой группе входов-выходов шины данных, по второму входу-выходу сопровождения данных, управляющим выходам - с соответствующими входами ЭУ Вх.), управляющим входом - с соответствующими выходами (у Вых,). Работа тестера контроля и диагностики электронных модулей заключена в следующем.В тестере предусмотрена возможность контроля модуля с произвольным типом интерфейса (вход-выход 21) и отдельно для упрощения программы предусмотрен вход- выход 22 для модулей с базовым интерфейсом. Тип модуля задается на пульте 17 ввода данных путем ввода данных с помощью клавиатуры, которые с первого выхода пульта ввода данных в виде кода поступают в регистр диспетчера 1. Программный опрос регистра 49 выполняется только после поступления с пульта 17 ввода данных (с Вых. 2) сигнала Пуск, который поступает на Вх. 1 микропроцессора 41 и производит запуск программы начального пуска по установленному в микропроцессоре начальному адресу для первого блока 50 памяти. Программа начального пуска обеспечивает установку всех регистров и счетчиков в исходное состояние, кроме регистра 49, очистку всех ОЗУ, приведение коммутатора 7 в исходное состояние, при котором разомкнуты все контакты второго блока 27 и ключи блока 26 коммутатора 7, что обеспечивается подачей сигнала Сброс, поступающего на вход Сброс (Вх.С) блока 10 памяти коммутатора и соответственно на элементы памяти - первые сдвигающие регистры 33.1 - ЗЗ.к, и второй сдвигающий регистр 38 от диспетчера 1 с регистра 45, также подачей нулевого кода с регистра 46. По первому двоичному разряду заданного кода определяется место подключения контролируемого модуля (вход-выход 21 или 22), о чем выводится сообщение на индикатор 3 через Выход В диспетчера 1, формируемое с помощью адаптера 47, в кодах стандартных сообщений, хранимых в блоке 51 памяти, поступающие через внутреннюю шину Адрес-Данные (ОШ) .Подключенный согласно сообщению контролируемый модуль (на вход-выход 21-или 22) проверяется прежде всего на отсутствие коротких замыканий, при наличии которых в любой из линий шины М 1 с Вых,1 шинного формирователя 19 поступает сигнал с низким уровнем на Вх.1 блока 18 сравнения регистра 88 генерации прерываний., обобщенный сигнал прерываний, с которого через Вых.Пр блока 18 сравнения поступает через Вх, Пр диспетчера 1 на Вх. Пр микропроцессора 41, что фиксируется программной обработкой прерываний микропроцессора 41 и отображается в виде сообщения на индикаторе 3 без диагностики номера контакта входа-выхода 22.При контроле модуля на входе-выходе 21 (ведется контроль входных сопротивлений относительно общего провода) данные пользователя для конкретных модулей предварительно вводятся в запоминающий блок 2 в форме функциональных матриц (формализованные таблицы базы данных модуля). В процессе выполнения программы блока 50 памяти производится загрузка блока 44 памяти отображения через общую шину (ОШ) - Адрес-Данные диспетчера 1 и генерация сигнала Пуск для блока 18 сравнения с выхода П 2 диспетчера 1, при этом наличие 1 в соответствующем разряде обеспечивает генерацию высокого уровня напряжения при выполнении преобразования параллельного кода, хранящегося в блоке 44 памяти отображения, в последовательный с помощью генератора 15 последовательного кода, с выхода которого последовательный код поступает на вход ПК блока 10 памяти коммутатора. Последовательный код поступает в блоке 10 памяти коммутатора на первые входы элементов И 34.1 - 34.к, на вторые входы которых поступают сигналы выборки регистров 33.1 -5 1 О 15 20 25 30 35 40 45 50 55 ЗЗ.к через Вх. 1 блока 10 памяти коммутатора от диспетчера 1 с первого регистра 42, Тактирующие импульсы, поступающие от генератора 43, обеспечивают продвижение последовательного кода при поступ. пении от блока 8 сравнения с Вых. 2 управляющих кодов, обуславливающих коэффициент деления с генератора 43. Совместно с заполнением блока 44 памяти отображения производится выборка данных для заполнения блока 84 памяти матрицы выходных данных модуля с границами допусков по каждому контакту контролируемого модуля на входе-выходе 21. Данные записываются в форме инвертированных таблиц и выбираются в буфер элемента 90 сравнения одновременно с последовательным подключением контактов контролируемого модуля на вход-выход 2 через коммутатор 7 (одну из горизонтальных шин второй группы) к входу измерителя 11 сопротивлений и напряжений. Замеренные данные через выход ШД измерителя 11 сопротивлений и напряжений поступают на первую группу входов-выходов блока 12 обмена, содержащего управляемые измерители, где через первый регистр 52 обеспечивается преобразование и ввод данных на общую шину, с третьих входов-выходов блока 12 обмена сигналы поступают на первый вход-выход генератора 16 тестов, преобразуются в последовательный код в блоке 79 обмена и далее в форме последовательного кода через вторые входы-выходы генератора 16 тестов - на вторые выходы блока 18 сравнения. Под управлением микропроцессора 82 данные вводятся во второй буфер элемента 90 сравнения. Если замеренные данные выходят за пределы допусков, то с выхода элемента 90 сравнения на вход регистра 88 генерации прерываний поступает по шинам код, обуславливающий выдачу сигнала прерывания с первого выхода элемента 90 сравнения, который поступает на вход прерываний Вх. Пр диспетчера 1. Микропроцессор 41 переходит на программу обработки прерываний по выявленной неисправности; из блока 51 памяти поступают на первый47 и второй 48 адаптеры коды для отображений и печати стандартной части, а из блока 44 памяти отображения данные по номеру контакта контролируемого модуля, из блока 85 памяти через общие шины Адрес-Данные поступает код замеренного параметра и далее через адаптеры 47 и 48 - на печатающий блок 4 и индикатор 3. При отсутствии отклонений от заданных границ измеряемого параметра сопротивления Контакт - Общий провод проводится дальнейший последовательно-сканирующий замер данных до завершения программы. По завершению замера сопротивлений на индикаторе 3 высвечивается сообщение Вклю 1396099 10чить питание модуля, а микропроцессоры 41, 71 и 82 переходят в режим Ожидание, Подача питания на контролируемые модули производится оператором. Сигналы о подаче питания поступают через вход 25 устройства на диспетчер 1, генератор 16 тестов и блок 18 сравнения. В генераторе 16 тестов через регистр 72 прерывания сигнал прерывания поступает на вход прерывания микропроцессора 71, а в блоке 18 сравнения сигнал поступает непосредственно на вход прерывания микропроцессора 82, в диспетчере 1 сигнал о подаче питания поступает на вход микропроцессора 41 Продолжение программы: Вх. ПП. Пер вым параметром замера для всех модулей является величина Общий ток в цепи общего провода, замер которого выполняется на измерительном регистре 20, падение напряжения вводится в виде аналогового сигнала на третий вход блока 14 контроля сигналов произвольной формы, который поступает на вход одного из каналов аналогоцифрового преобразователя 65, преобразуется в код, поступающий на один из регистров 66.1 - 66.к. Данные по программе блока 69 памяти обработки преобразований выводятся через входы-выходы блока 14 контроля сигналов произвольной формы по общей шине на генератор 16 тестов и далее - в блок 18 сравнения, далее попадают в блок 85 памяти. В блоке 18 сравнения сравнение измеренных данных и допусков выполняется под уп равлением микропроцессора 41, При отклонении от допусков дальнейшая проверка контролируемого модуля останавливается, выдается диагностика Питание неисправно. Ток потребления 166 == При соответствии допусковых требований по потреблению тока производится тестовый контроль модуля. В зависимости от типа модуля тестовая проверка и синтез теста выполняются следующим образом. Из запоминающего блока 2 выводятся согласно номеру контролируемого модуля данные в виде матрицы и попадают в блок 18 сравнения и в генератор 16 тестов в четвертый блок 76 памяти, содержащий таблицы исходных данных. Анализ данных в генераторе 16 тестов производится по иерархическому принципу: определяется тип входных сигналов и входной последовательности измножества Стандартные тесты, Комбинация стандартных последовательностей, Последовательности, формируемые управляемыми генераторами. Каждому стандартному тесту присвоена кодовая комбинация, хранящаяся во втором блоке 74 памяти. При совпадении кодовых комбинаций параллельно формируется матрица контактного поля для коммутатора 7 в блоке 44 памяти отображения. Анализ совпадения выполняется для входных данных в блоке81 сравнения. Если данные контролируемого модуля таковы, что необходимо инициировать две или более стандартные последовательности одновременно или послвдовательно, то набор констант из третьего блока 75 памяти поступает в определенные ячейки ОЗУ, подключая тем самым соответствуюшие ветки программ третьего блока 75 памяти, Стандартные последовательности формируются программами и поступают на выходные каналы двунаправленного регистра 80 и далее - на соответствующие входы коммутатора 7. 5 10 ходы каналов. Момент выдачи сигналов с блока 13 генерации сигналов произвольной формы определяется поступлением сигнала низкого уровня (разрешение) с выхода диспетчера 1. Одновременно вводится в действие микропроцессор 82 блока 18 сравнения и в блоке 44 памяти отображения формируются ячейки, обуславливающие замыкание цепей коммутатора 7 для контроля выходных данных проверяемого модуля 50 55 Если входную последовательность невозможно сформировать из стандартных наборов, то по выданному признаку в блоке 81 сравнения начинает производиться анализ по каталогу шестого блока 78 памяти, управление передается блоку 12 об мена, сигналы поступают через третьи входы-выходы; первый блок 56 памяти начинает выполнять программу протоколов обмена в зависимости от данных, поступивших в определенные ячейки третьего блока 25 58 памяти, которые определяют тип инициированного генератора, режим циклов и параметры отдельного импульса, синусоиды, пилы и т.п, Если с блока 81 сравнения поступает сигнал о невозможности получения нужной формы кривой периодического или З 0 непериодического сигнала или в составевходных данных, поступающих от запоминающего блока 2, содержится признак необходимости генерации сигнала, относящегося к типу Произвольная форма (например, ступенчатое напряжение с плоской или пилообразной закономерностью изменения, псевдослучайные скачки напряжений и т.п.), то управление передается блоку 13 генерации сигналов произвольной формы, при этом в выделенные ячейки второго блока 64 па мяти записываются одновременно константы, определяющие длительность экспонирования для таймеров 62.1 - 62.к, адрес запуска программ в первый блок 63 памяти для ввода кодов преобразования в регистры 61.1 - 61,к. Для получения сигнала, представляющего собой сумму разных каналов цифроаналогового преобразователя 60 данные поступают через элемент ИЛИ 59 на первый выход, группа сигналов второго выхода представляет собой локальные вы 1396099для чего выполняется анализ выходных данных, засылаемых из запоминающего блока 2 зоны выходных данных параметров модуля в блок 84 памяти. Производится последовательный опрос данных, выявляющих 5 требуемые средства контроля выходных параметров из числа возможных: контроль средствами генератора 16 тестов по сигналам, поступающим на входы-выходы двунаправленного регистра 80, контроль с помощью измерителя 5 дискретных сигналов (например, С 9 - 8) или измерителя 6 аналоговых сигналов, сигналы произвольной формы контролируются блоком 14 контроля сигналов произвольной формы, в котором сигналы поступают от различных цепей на группу первых входов, на аналого-цифровой преобразователь 65, - на выходные каналы которого поступают коды на регистры 66.1 - 66.к. Момент регистрации кода выполняется по сигналу таймера 67, управ ляемого через общую шину АдресДанные, на второй вход которого поступают управляемые по частоте импульсы с выхода ТИ диспетчера 1. В счетчике 68 каналов происходит учет номера канала для управления адресацией записи данных в блок 70 памяти.Формула изобретения 1, Тестер контроля и диагностики электронных модулей, содержащий запоминающий блок, индикатор, измеритель дискретных сигналов, печатающий блок, коммутатор, блок сравнения, генератор дискретных сигналов, пульт ввода данных, диспетчер, шинный формирователь, выход которого соединен с входом блока сравнения, первый выход которого соединен с входом прерывания диспетчера, первая группа входов- выходов коммутатора соединена с первым входом-выходом устройства, первый выход пульта ввода данных соединен с входом ввода данных диспетчера, а второй выход соединен с входом Пуск диспетчера, выход индикации которого соединен с входом индикатора, а выход печати - с входом печатающего блока, запоминающий блок соединен входами-выходами с входами-выходами диспетчера, отличающийся тем, что, с целью расширения области применения и функциональных возможностей за счет возможности контроля различных типов модулей, а также повышения производительности за счет сокрашения сроков разработки испытательных программ в него введены измеритель аналоговых сигналов, блок памяти коммутатора, измеритель сопротивлений и напряжений, блок обмена, блок генерации сигналов произвольной формы, блок контроля сигналов произ вольной формы, генератор последовательного кода, генератор тестов, измерительный резистор, гене 3035405055 ратор аналоговых сигналов, причем входы- выходы общей шины генератора тестов, шинного формирователя, блока генерации сигналов произвольной формы, блока контроля сигналов произвольной формы и блока обмена соединены между собой, вход управления тактовой частотой диспетчера соединен с вторым выходом блока сравнения, входы прерывания по питани ю диспетчера, генератора тестов и блока сравнения соединены с первым входом устройства, выход тактовых импульсов диспетчера соединен с входами тактовых импульсов генератора последовательного кода, блока памяти коммутора, блока генерации сигналов произвольной формы и блока контроля сигналов произвольной формы, выход управления - с входом управления блока памяти коммутатора, выход сброса - с входом сброса блока памяти коммутатора, выход стробирования - с первым входом блока генерации сигналов произвольной формы, выход записи, кодовый выход и информационные выходы соединены с входами записи, кодовыми входами и информационными входами блока памяти коммутатора соответственно, выход Пуск 1 диспетчера соединен с входом Пуск 1 генератора тестов, выход Пуск 2 - с входом пуска блока сравнения, выход управления диспетчера - с входом шинного формирователя, а вход-выход - с входом-выходом генератора последовательного кода и первым входом-выходом блока сравнения, второй вход-выход которого соединен с первым входом-выходом генератора тестов, вход прерывания которого соединен с выходом прерывания блока сравнения, выход генератора последовательного кода соединен с входами последовательного кода блока памяти коммутатора и коммутатора, выход кода которого соединен с входом генератора последовательного кода, вторая группа входов-выходов коммутатора соединена с соответствующей группой входов-выходов генератора тестов, первая и вторая группа входов - с первой и второй группой выходов блока памяти коммутатора соответствен но, первый, второй, третий и четвертый выходы - с входами измерителя дискретных сигналов, измерителя аналоговых сигналов, блока контроля сигналов произвольной формы и измерителя сопротивлений и напряжений, первый, второй, третий и четвертый входы коммутатора соединены соответственно с первым и вторым выходами блока генерации сигналов произвольной формы, выходами генератора дискретных сигналов и генератора аналоговых сигналов, третий вход блока контроля сигналов произвольной формы соединен с общей шиной модуля и через измерительный резистор с общей шиной источника, вход блока обмена соединен спрагглякнцими выходами измерителя дискретных сигналов, измерителя аналоговых сигналов, генератора аналоговых сигналов и измерителя сопротивлений и напряжений, управляюгций вход которых соединен с выходом блока обмена, а управляюгцие входы-выходы и входы-выходы данных соединены с первыми и вторыми входами-выходами блока обмена соответственно, а информационный вход-шход шинного формирователя соединен с вторым входом-выходом устройства. 2. Тестер по п. 1, огли гающийся тем, что коммутатор содержит первый и второй блоки переключения, выполненные в виде матриц соответственно с контактными и бесконтактными переключателями, причем первые входы ггерво о с":лока переключения соединены с первыми входами коммутатора, первые входы-выходы ком мутатора соединены с первыми входами-выходами первого блока переключения, вторые входы-выходы коммутатора соединены с первыми входами-выходами второго блока переклк- чения, вторые входы коммутатора - с входами второго блока переключения, а вторые входы-выходы первого и второго блоков переключения - соответственно с первыми и вторыми входами-выходами элементов ИЛИ, третьи входы-выходь которых соединены с третьими входами-выходами ком мутатора.3. Тестер по и. 1, отличающийс тем, что блок памяти коммутатора содержит первые сдвигающие регистры по числу горизонтальных шин контактной части коммутатора, первые входы которых соединены с выходами соответствующих первых элементов И, первые входы которых соединены с входом ввода последовательного кода бло ка, а вторыес ссютветствующими управ. ляющими входами выборки горизонтальной шины контактной части коммутатора и с первыми входами вторых элементов И, вторые входы которых соединены с входом такто вых импульсов блока, а выходы вторых элементов И соединены соответственно с вторыми входами первых с:двигающих регистров, третьи входы которых соединены с входом Сброс блока, входы кодов бло ка соединены с соответствующими входами регистров, выходы которых соединены с исходами кодов блока, а тактовые входы - с выходами третьих элементов И, первые входы которых соединен. с соответствующи м и вы ходам и второго сд ви га кнцсго регистра, а вторые входы - с входом записи блока, первый вход соединен с выходом четвертого элемента И, а третий вход - с входсе, Сброс блока, второй вход - с выход;ом снятого элемента И, первые входы четвертого и пятого элементов И соединены с 5 10 20 25 ЗО 35 40 45 50 55 управляющим входом блока, а вторые - соответственно с входом ввода последовательного кода блока и входом тактовых импульсов блока.4. Тестер по п, 1, отличающийся тем, что диспетчер содержит соединенные входами-выходами микропроцессор, первыи регистр, генератор, блок памяти отображения, второй регистр, третий регистр, первый адаптер, второй адаптер, четвертый регистр, первый и второй блоки памяти и вход-выход данных диспетчера, вход управления тактами соединен с вторым входом генератора, выход которого является выходом тактовых импульсов диспетчера, вьгходы управляющих и стробирующих сигналов - выходами первого, второго и третьего регистров, а входы данных диспетчера - входами четвертого регистра, вход прерывания диспетчера - входом прерывания микропроцессора, вход Пуск диспетчера соединен с входом Пуск микропроцессора, выход индикации соединен с выходом первого адаптера, выход Пуск диспетчера - с первым выходом второго адаптера, а выход Пуск 3 диспетчера - с вторым выходом.5, Тестер по п. 1, отличоющийся тем, что блок обмена содержит соединенные информационными входами-выходами первый и второй регистры, передающий регистр и приемный регистр, первый, второй и третий блоки памяти, соединенные с первым входом-выходом блока, вход-выход первого регистра соединен с вторым входом-выходом блока, вход-выход второго регистра - с третьим входом-выходом блока, выход передающего регистра - с выходом блока, а вход приемного регистра - с входом блока.б. Тестер по п. 1, отличающийся тем, что блок генерации сигналов произвольной формы содержит цифроаналоговый преобразователь, регистры, выходгг которых соединены с соответствующими входами цифроаналогового преобразователя, а входы с входами-выходами таймеров и входом- выходом Адрес-Данные блока, при этом выходы каналов цифроаналогового преобразователя соединены с выходом блока и входами элемента ИЛИ, выход которого соединен с вторым выходом блока, первый вход которого соединен с входом стробирования ггифроаналогового преобразователя, второй вход управляемых тактовых импульсов - с входами таймеров, а вход-выход блока - с входами-выходами первого и второго блоков памяти.7. Тестер по п. 1, отличающийся тем, что блок контроля сигналов произвольной формы содержит аналого-цифровой преобразователь, выходы которого подключены к первым входам регистров, интерфейсные входы-выходы которых соеди нены с входом1396099 16 15 Жг мюРуль выходом Адрес-Данные блока и входом- выходом таймера, вход-выход блока соединен с входами-выходами первого и второго блоков памяти, выход таймера соединен с вторыми входами регистров и через счетчик каналов - с входом второго блока памяти, вход управляемых тактовых импульсов контроля блока - с входом таймера, а первый и второй входы блока соединены соответственно с первым и вторым входами аналого-цифрового преобразователя.8. Тестер по п. 1, отличающийся тем, что генератор тестов содержит соединенные первыми входами-выходами блок обмена, двунаправленный регистр и входами-выходами микропроцессор, блок сравнения, первый, второй, третий, четвертый, пятый и шестой блоки памяти соединены с входом-выходом Адрес-Данные генератора, при этом входы прерывания генератора соединены с соответствующими информационными входами регистра прерываний, входы- выходы генератора - с вторыми входами- выходами блока обмена, входы-выходы кодов стандартных тестов генератора - с вторыми входами-выходами двунаправленного регистра, вход питания модулей генератора соединен с входом регистра прерываний, первый, второй, третий и четвертый входы блока сравнения соединены соответственно с выходами второго, четвертого, пятого и шестого блоков памяти.9. Тестер по п. 1, отличающийся тем,что блок сравнения содержит микропроцессор, блок обмена, первый, второй, третий и четвертый блоки памяти, соединенные входами-выходами с входом-выходом Адрес- Данные блока, причем первый и второй входы элемента сравнения соединены с выходами первого и второго блоков памяти, выходы элемента сравнения и первый вход блока соединены с первым и вторым входами регистра генерации прерываний соответственно, первые выходы регистра генерации прерываний соединены с выходами прерываний блока, вторые выходы - с первым выходом блока, выход регистра соединен с вторым выходом блока, вход Пуск - с первым входом микропроцессора, второй вход которого соединен с входом питания модулей блока, а вход-выход тестов блока 25обмена - с первым входом-выходом блока.

СмотретьЗаявка

4105593, 14.08.1986

ПРЕДПРИЯТИЕ ПЯ А-3462

КАРЛСБРУН ИЗРАИЛЬ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G01R 31/02, G01R 31/28

Метки: диагностики, модулей, тестер, электронных

Опубликовано: 15.05.1988

Код ссылки

<a href="https://patents.su/12-1396099-tester-kontrolya-i-diagnostiki-ehlektronnykh-modulejj.html" target="_blank" rel="follow" title="База патентов СССР">Тестер контроля и диагностики электронных модулей</a>

Предыдущий патент: Устройство для определения направления поиска короткого замыкания

Следующий патент: Устройство для измерения неоднородности среднего значения составляющей индукции постоянного магнитного поля

Случайный патент: 336540