Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1140126

Автор: Минутин

Текст

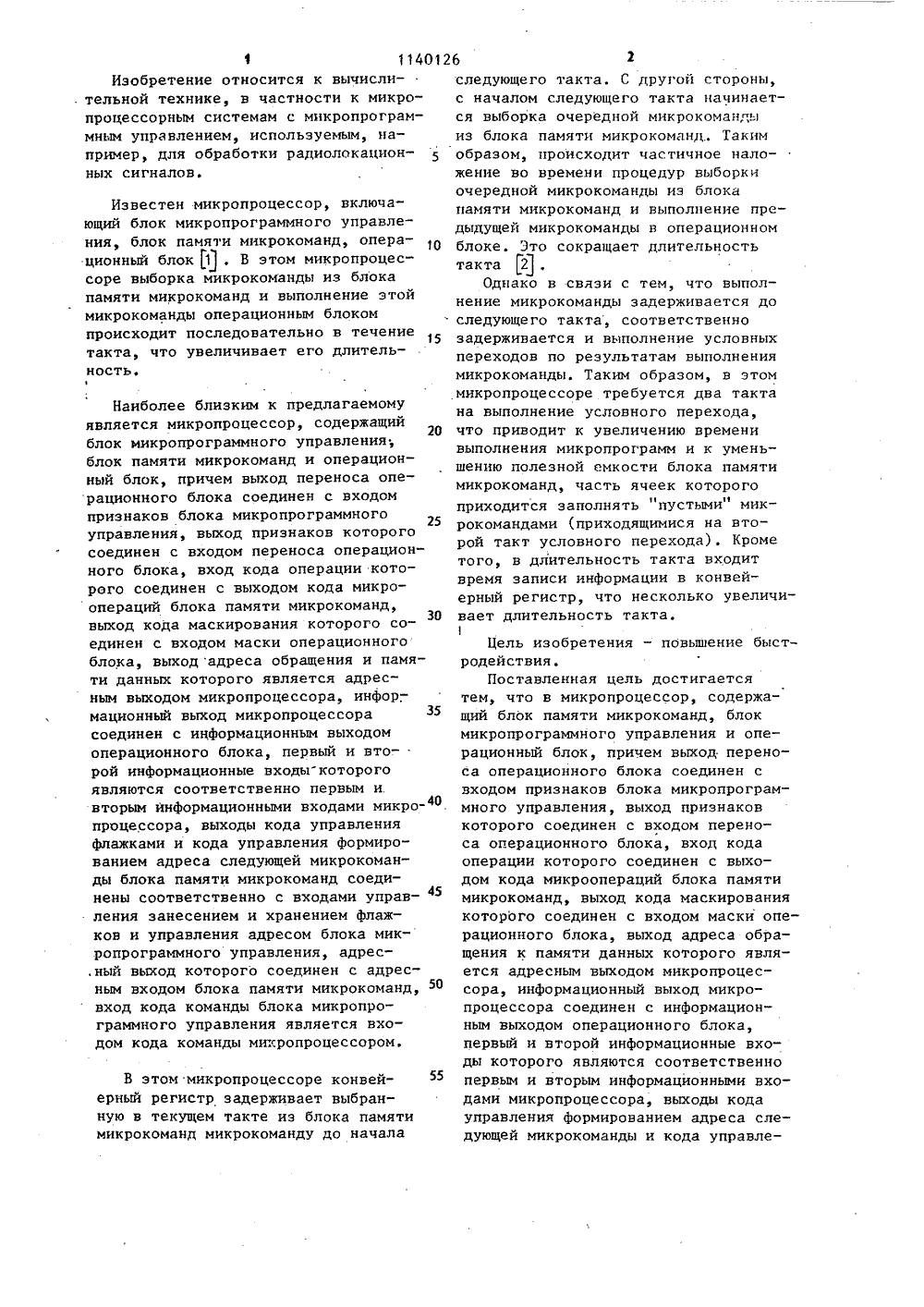

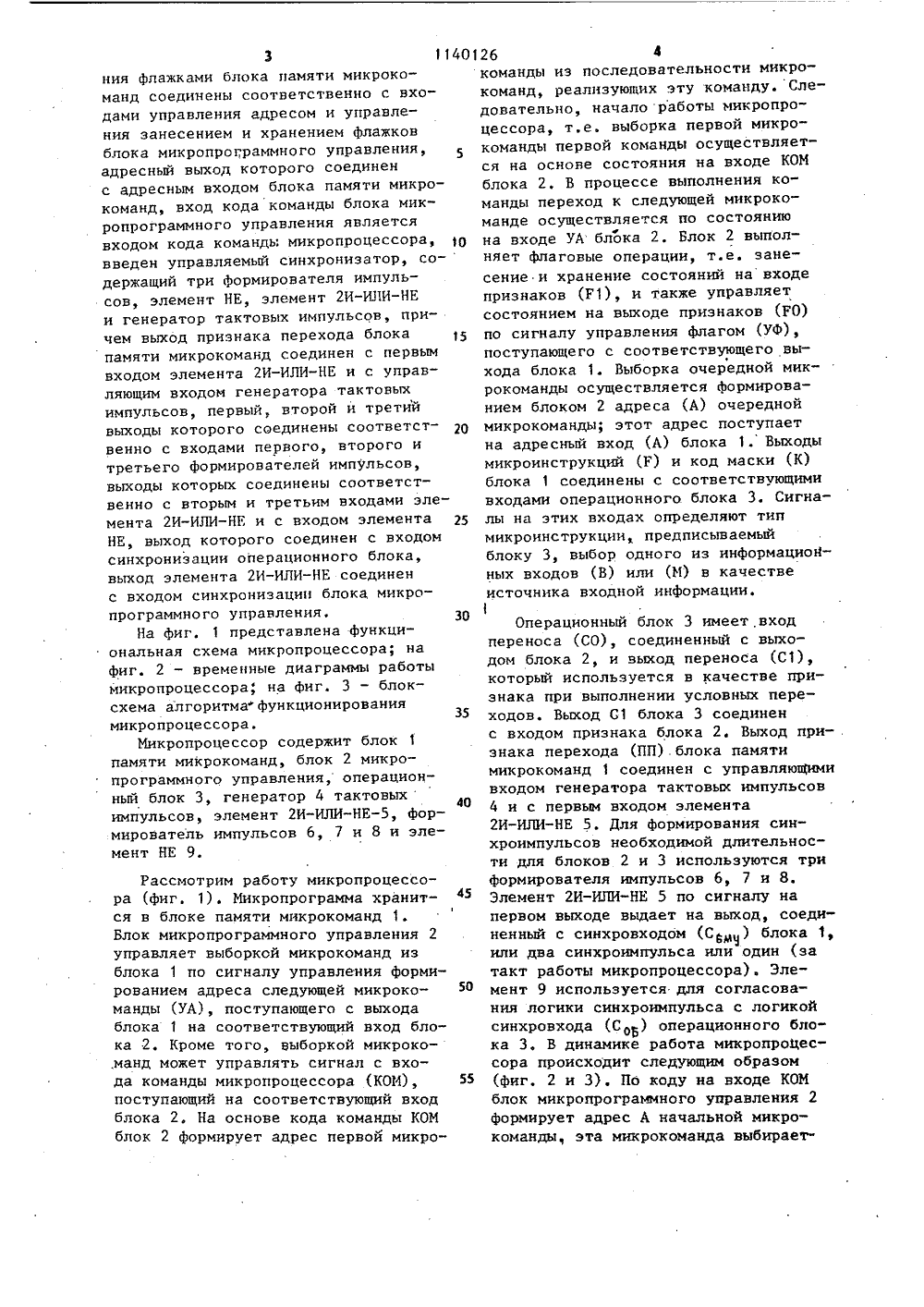

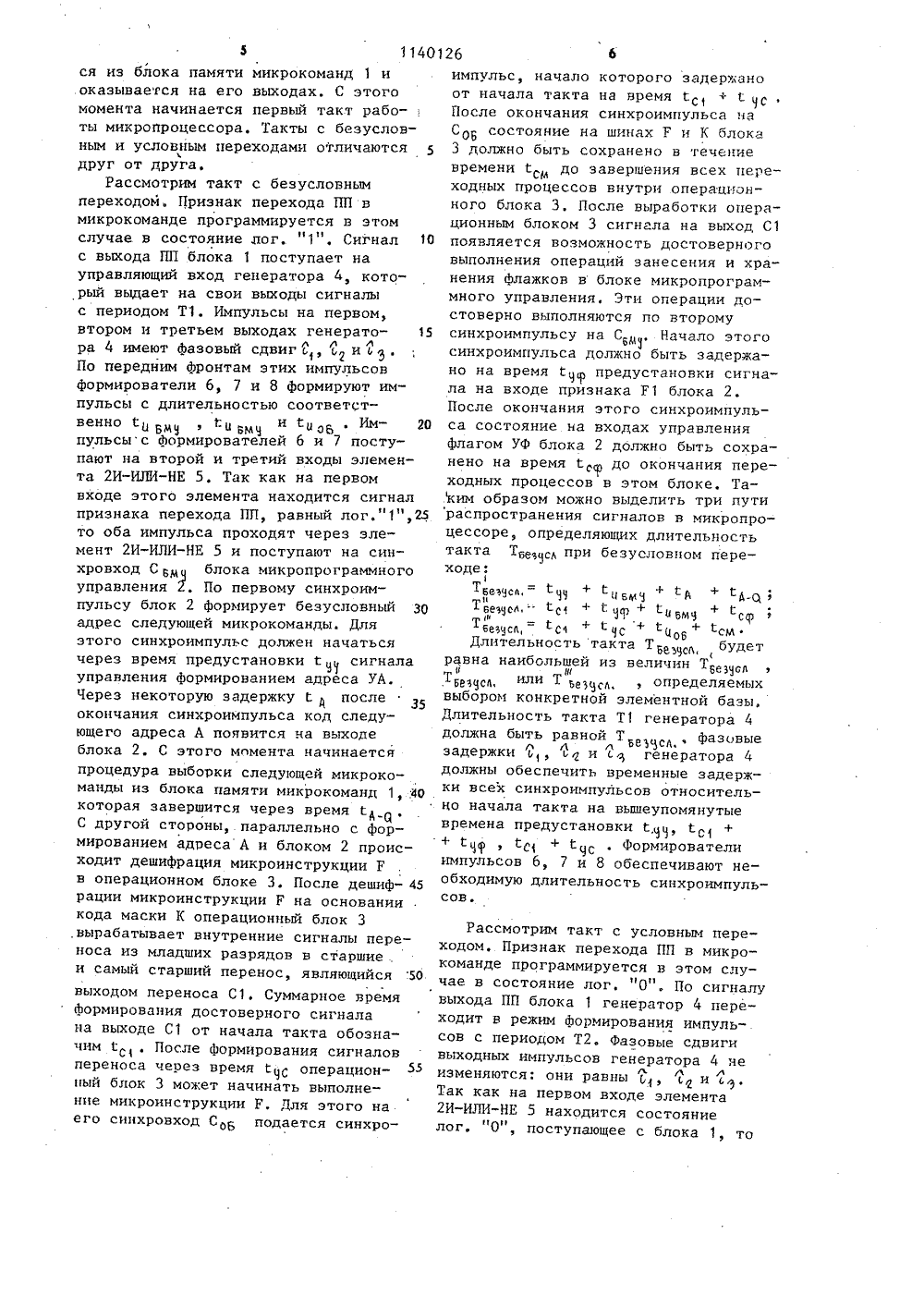

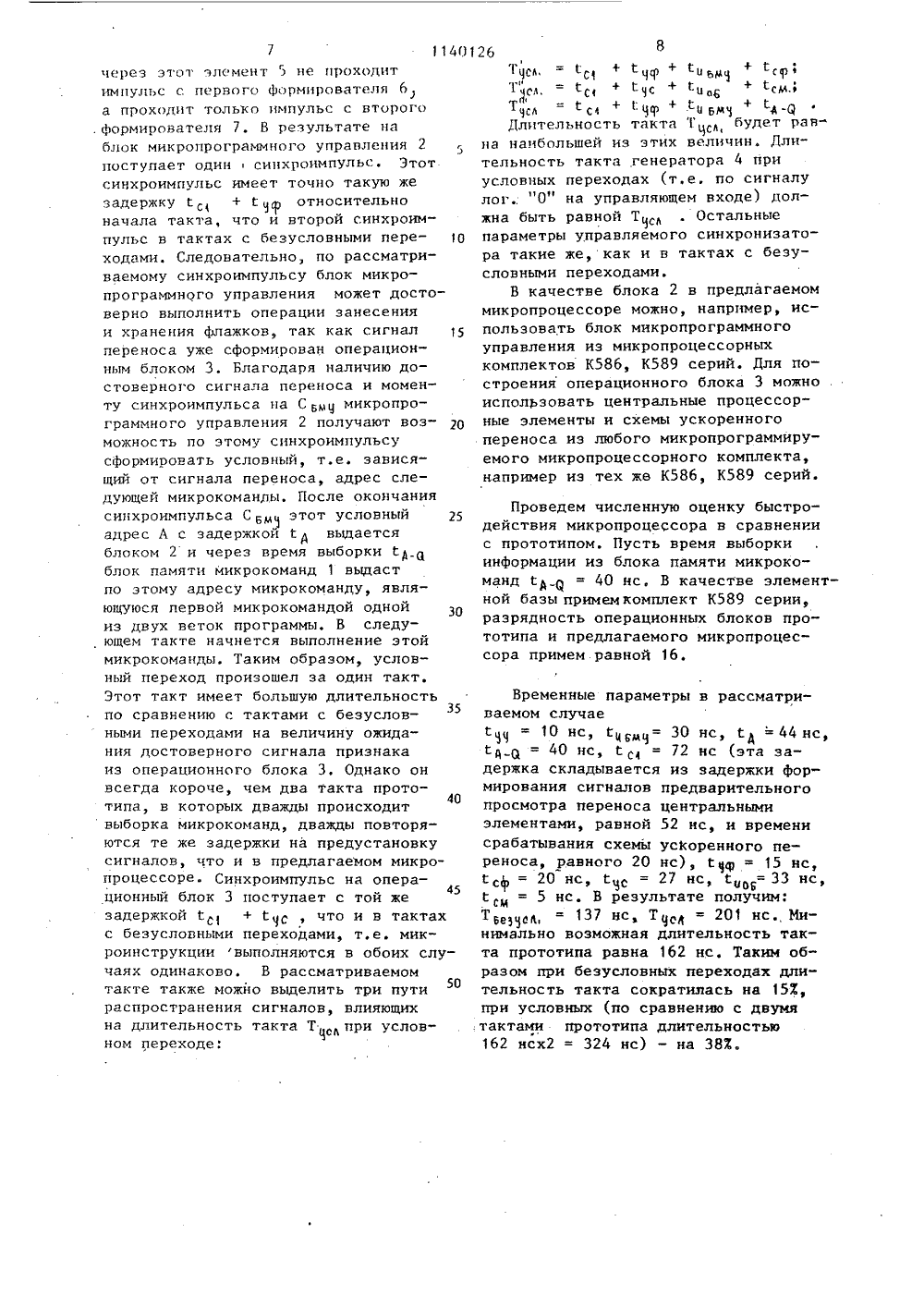

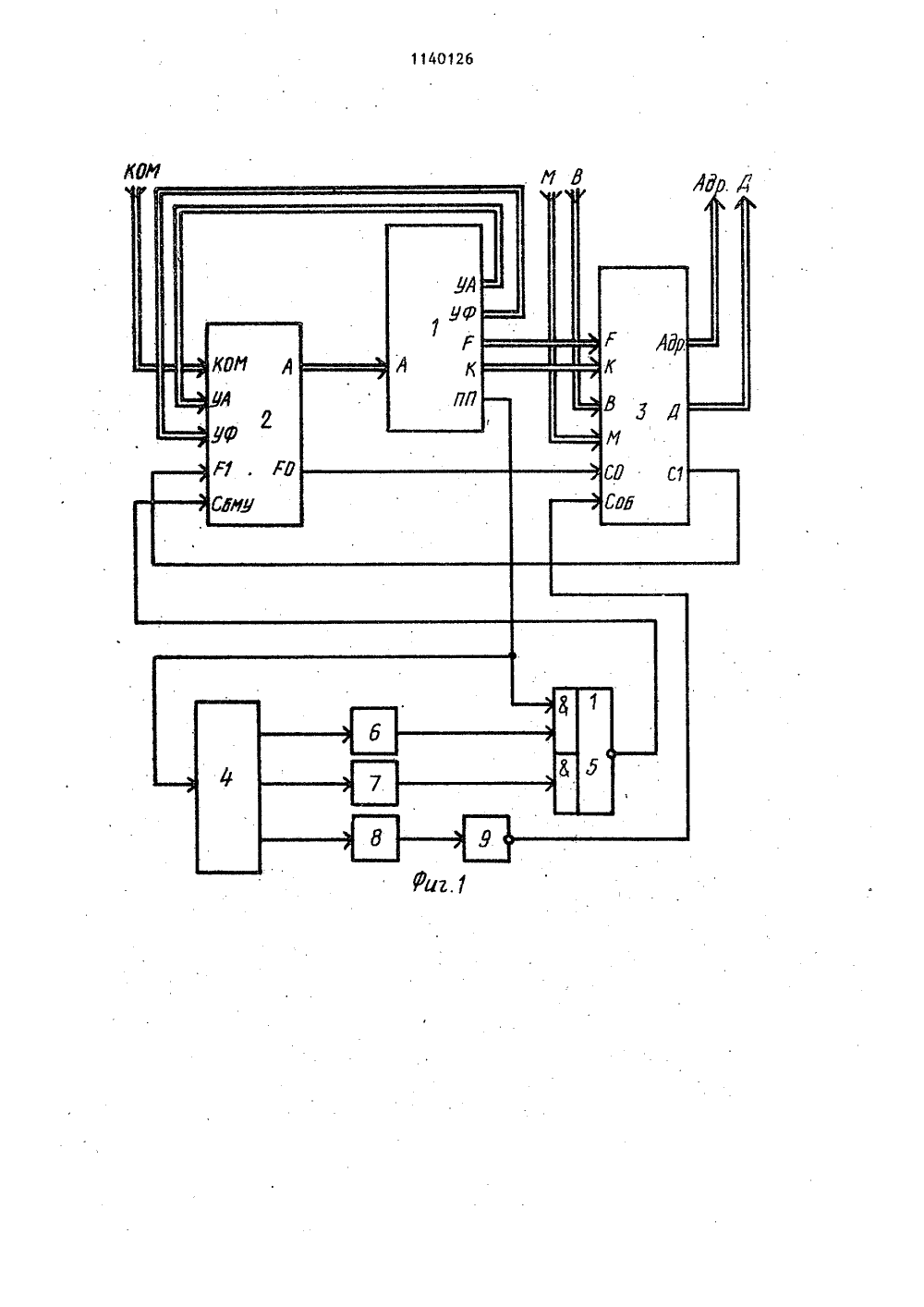

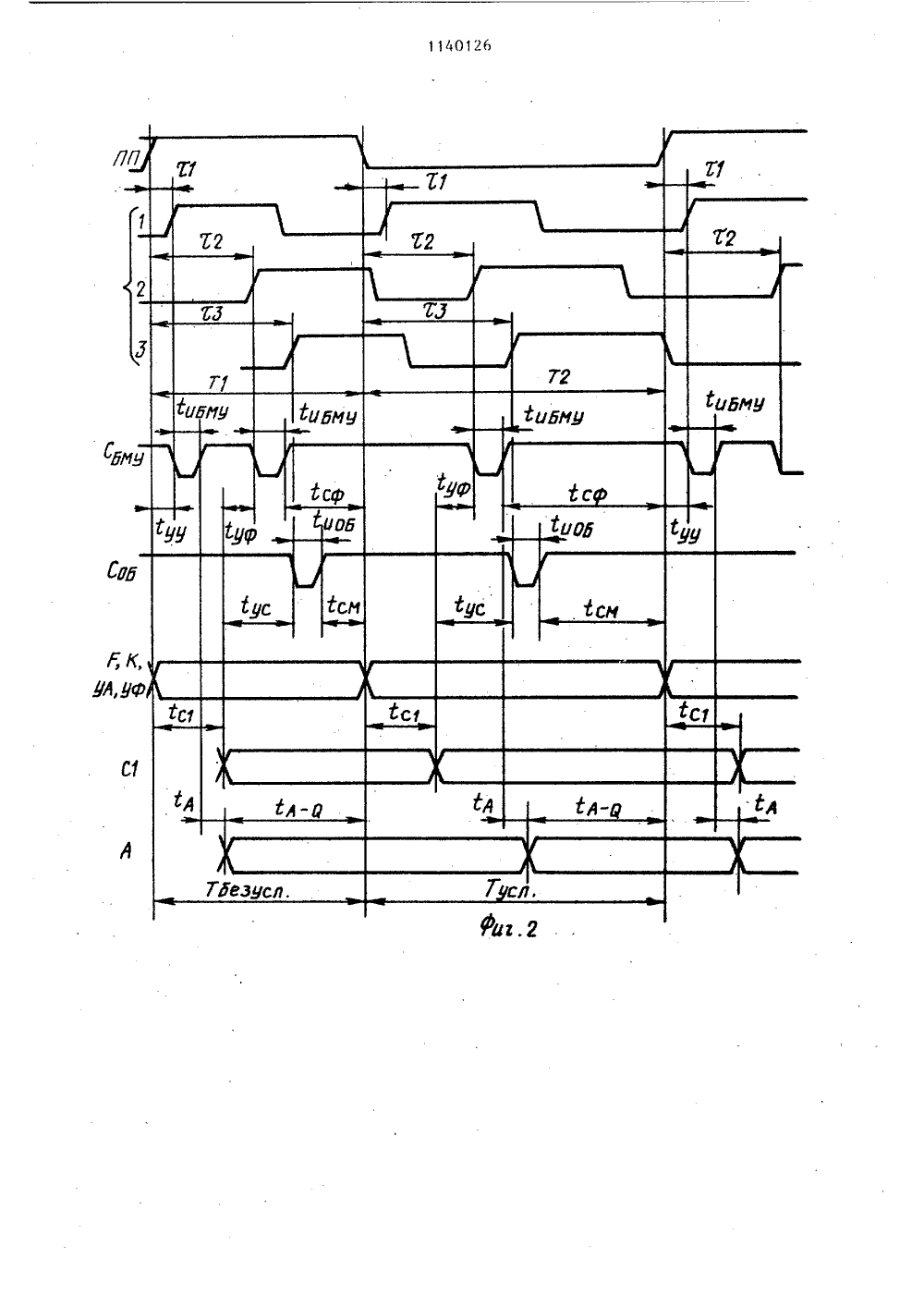

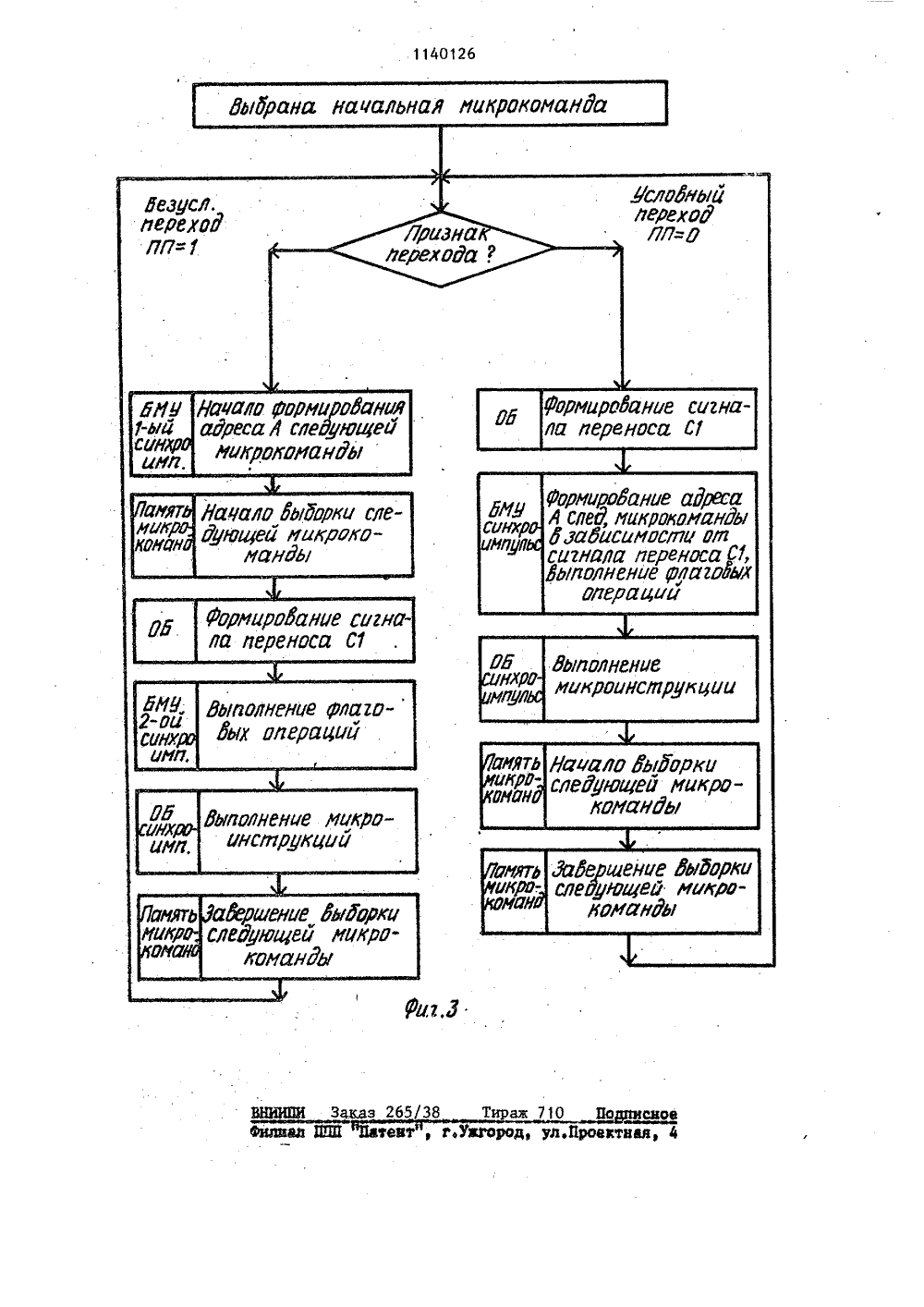

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 3544720/24-2426.01,8315.02.85. Бюл. В 6Л.Д, Минутин681.325(088.8)1, Березенко А,И., Корьян А.Р. Микропроцессы повышенного быстродРадио и связь", 1981,Там же, с. 122-126 ((54) (57) МИКРОПРОЦЕССОР, содержащийблок микропрограммного управления,блок памяти микрокоманд и операционный блок, причем выход переноса операционного блока соединен с входомпризнаков блока микропрограммногоуправления, выход признаков которогосоединен с входом переноса операционного блока, вход кода операции которого соединен с выходом кода микроопераций блока памяти микрокоманд,выход кода маскирования которого соединен с входом маски операционногоблока, выход адреса обращения к памя-.ти данных которого является адресным выходом микропроцессора, информационный выход микропроцессора соединен с информационным выходом операционного блока, первый и второйинформационные входы которого являются соответственно первым и вторыминформационными входами микропроцессора, выходы кода управления формированием адреса следующей микрокоманды и кода управления флажками блока памяти микрокоманд соединены соответственно с входами управления адресом и управления занесением и хранением флажков блока микропро. граммного управления, адресный выход которого соединен с адресным входом блока памяти микрокоманд, вход кода команды блока микропрограммного управления является входом кода команды микропроцессора, о т л и ч а ющ и й с я тем, что, с целью повышения быстродействия, он содержит управляемый синхронизатор, содержащий три формирователя импульсов, З элемент НЕ, элемент 2 И-ИЛИ-НЕ и генератор тактовых импульсов, причем выход признака перехода блока памяти микрокоманд соединен с первым входом элемента 2 И-ИЛИ-НЕ и с управляющим входом генераторатактовых импульсов, первый, второй и третий выходы которого соединены соответственно с входами первого, второго и май третьего формирователей импульсов, , ф выходы которых соединены соответствев но с вторым и третьим входами элемен- та 2 И-ИЛИ-НЕ и с вхддом элемента НЕ, выход которого соединен с входом сии- фф хронизации операционного блока, выход элемента 2 И-ИЛИ-НЕ соединен с входом синхронизации блока микропрограммного управления. .Ь114012Изобретение относится к вычислительной технике, в частности к микропроцессорным системам с микропрограммным управлением, используемым, например, для обработки радиолокационных сигналов. Известен микропроцессор, включающий блок микропрограммного управления, блок памяти микрокоманд, операционный блок 1 . В этом микропроцессоре выборка микрокоманды из блока памяти микрокоманд и выполнение этой микрокоманды операционным блоком происходит последовательно в течение такта, что увеличивает его длительность,Наиболее близким к предлагаемому является микропроцессор, содержащий блок микропрограммного управления; блок памяти микрокоманд и операционный блок, причем выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выход признаков которого соединен с входом переноса операционного блока, вход кода операции которого соединен с выходом кода микро-операций блока памяти микрокоманд,30 выход кода маскирования которого соединен с входом маски операционного блока, выход адреса обращения и памяти данных которого является адресным выходом микропроцессора, инфор; мационный выход микропроцессора соединен с информационным выходом операционного блока, первый и вто-. рой информационные входы-которого являются соответственно первым и. вторым информационными входами микропроцессора, выходы кода управления флажками и кода управления формированием адреса следующей микрокоманды блока памяти микрокоманд соединены соответственно с входами управ ления занесением и хранением флажков и управления адресом блока микропрограммного управления, адрес.ный выход которого соединен с адресным входом блока памяти микрокоманд, 5 О вход кода команды блока микропрограммного управления является входом кода команды микропроцессором,В этом микропроцессоре конвейерный регистр задерживает выбранную в текущем такте из блока памяти микрокоманд микрокоманду до начала 6 2следующего такта. С другой стороны, с началом следующего такта начинается выборка очередной микрокоманды из блока памяти микрокоманд, Таким образом, происходит частичное наложение во времени процедур выборки очередной микрокоманды из блока памяти микрокоманд и выполнение предыдущей микрокоманды в операционном блоке. Это сокращает длительность такта 2 .Однако в связи с тем, что выполнение микрокоманды задерживается до следующего такта, соответственно задерживается и выполнение условных переходов по результатам выполнения микрокоманды. Таким образом, в этом микропроцессоре требуется два такта на выполнение условного перехода, что приводит к увеличению времени выполнения микропрограмм и к уменьшению полезной емкости блока памяти микрокоманд, часть ячеек которогоприходится заполнять пустыми" микрокомандами (приходящимися на второй такт условного перехода). Крометого, в длительность такта входитвремя записи информации в конвейерный регистр, что несколько увеличивает длительность такта,Цель изобретения - повышение быстродействия.Поставленная цель достигаетсятем, что в микропроцессор, содержащий блок памяти микрокоманд, блокмикропрограммного управления и операционный блок, причем выход переноса операционного блока соединен свходом признаков блока микропрограммного управления, выход признаковкоторого соединен с входом переноса операционного блока, вход кодаоперации которого соединен с выходом кода микроопераций блока памятимикрокоманд, выход кода маскированиякоторого соединен с входом маски операционного блока, выход адреса обращения к памяти данных которого является адресным выходом микропроцессора, информационный выход микропроцессора соединен с информационным выходом операционного блока,первый и второй информационные входы которого являются соответственнопервым и вторым информационными входами микропроцессора, выходы кодауправления формированием адреса следующей микрокоманды и кода управле55 ния Флажками блока памяти микракоманд соединены соответственно с входами управления адресом и управления занесением и хранением флажковблока микропрограммного управления,адресный выход которого соединенс адресным входом блока памяти микрокоманд, вход кода команды блока микропрограммного управления являетсявходом кода команды микропроцессора,введен управляемый синхронизатор, содержащий три Формирователя импульсов, элемент НЕ, элемент 2 И-ИЛИ-НЕи генератор тактовых импульсов, причем выход признака перехода блокапамяти микрокоманд соединен с первымвходом элемента 2 И-ИЛИ-НЕ и с управляющим входом генератора тактовыхимпульсов, первый, второй и третийвыходы которого соединены соответственно с входами первого, второго итретьего формирователей импульсов,выходы которых соединены соответственно с вторым и третьим входами элемента 2 И-ИЛИ-НГ и с входом элементаНЕ, выход которого соединен с входомсинхронизации операционного блока,выход элемента 2 И-ИЛИ-НЕ соединенс входом синхронизации блока микропрограммного управления,На Фиг. 1 представлена функциональная схема микропроцессора; нафиг. 2 - временные диаграммы работымикропроцессора, на Фиг. 3 - блоксхема алгоритма функционированиямикропроцессора.Микропроцессор содержит блок 1памяти микрокоманд, блок 2 микропрограммного управления, операционный блок 3, генератор 4 тактовыхимпульсов, элемент 2 И-ИЛИ-НЕ, формирователь импульсов 6, 7 и 8 и элемент НЕ 9. Рассмотрим работу микропроцессора (фиг. 1). Микропрограмма хранится в блоке памяти микрокоманд 1, Блок микропрограммного управления 2 управляет выборкой микрокоманд из блока 1 по сигналу управления формированием адреса следующей микрокоманды (УА), поступающего с выхода блока 1 на соответствующий вход блока 2, Кроме того, выборкой микроко,манд может управлять сигнал с входа команды микропроцессора (КОМ), поступающий на соответствующий вход блока 2. На основе кода команды КОМ блок 2 формирует адрес первой микро 10 15 20 25 30 35 40 45 50 команды из последовательности микро- команд, реализующих эту команду.Следовательно, начало работы микропроцессора, т.е. выборка первой микро- команды первой команды осуществляется на основе состояния на входе КОМ блока 2, В процессе выполнения команды переход к следующей микрокоманде осуществляется по состоянию на входе УА блока 2. Блок 2 выполняет флаговые операции, т.е. занесение и хранение состояний на входе признаков (Р 1), и также управляет состоянием на выходе признаков (РО) по сигналу управления флагом (Уф), поступающего с соответствующего выхода блока 1. Выборка очередной микрокоманды осуществляется Формированием блоком 2 адреса (А) очередной микрокоманды; этот адрес поступает на адресный вход (А) блока 1. Выходы микроинструкций (Г) и код маски (К) блока 1 соединены с соответствующими входами операционного блока 3. Сигналы на этих входах определяют тип микроинструкции предписываемый блоку 3, выбор одного из информационных входов (В) или (М) в качестве источника входной информации.Операционный блок 3 имеет, вход переноса (СО), соединенный с выходом блока 2, и выход переноса (С 1), который используется в качестве признака при выполнении условных переходов. Выход С 1 блока 3 соединен с входом признака блока 2. Выход при- . знака перехода (ПП) блока памяти микрокоманд 1 соединен с управляющими входом генератора тактовых импульсов 4 и с первым входом элемента 2 И-ИЛИ-НЕ 5, Для формирования синхроимпульсов необходимой длительности для блоков 2 и 3 используются три Формирователя импульсов 6, 7 и 8Элемент 2 И-ИЛИ-НЕ 5 по сигналу на первом выходе выдает на выход, соединенный с синхровходом (С) блока 1, или два синхроимпульса или один (за такт работы микропроцессора). Элемент 9 используется для согласования логики синхроимпульса с логикой синхровхода (СВ) операционного блока 3. В динамике работа микропроЦессора происходит следующим образом (Фиг. 2 и 3). По коду на входе КОМ блок микропрограммного управления 2 формирует адрес А начальной микро- команды, эта михрокоманда выбирает 1140126ся из блока памяти микрокомакд 1 и оказывается на его выходах. С этого момента начинается первый такт рабо-: ты микропроцессора. Такты с безусловным и условным переходами отличаются друг от друга.Рассмотрим такт с безусловным переходом. Признак перехода ПП в микрокоманде программируется в этом случае в состояние лог, "1", Сигнал 10 с выхода ПП блока 1 поступает на управляющий вход генератора 4, кото" рый выдает на свои выходы сигналы с периодом Т 1. Импульсы на первом, втором и третьем выходах генерато ра 4 имеют фазовый сдвиг с ь 2 и ь 3,л Л По передним фронтам этих импульсов формирователи б, 7 и 8 формируют импульсы с длительностью соответстВенно С Бму , 1 ц у и Йц. Им пульсы с формирователей 6 и 7 поступают на второй и третий входы элемента 2 И-ЮИ-НЕ 5, Так как на первом входе этого элемента находится сигнал признака перехода ПП, равный лог."1",25 то оба импульса проходят через элемент 2 И-ИЛИ-НЕ 5 и поступают на синхровход С ьмч блока микропрограммного управления Я. По первому синхроимпульсу блок 2 формирует безусловный З 0 адрес следующей микрокоманды. Для этого синхроимпульс должен начаться через время предустановки й у сигнала управления формированием адреса УА. Через некоторую задержкупосле окончания синхроимпульса код следующего адреса А появится ча выходе блока 2С этого момента начинается процедура выборки следующей микрокоманды из блока памяти микрокоманд 1,:40которая завершится через времяС другой стороны,.параллельно с формированием адреса А и блоком 2 происходит дешифрация микроинструкции Рв операционном блоке 3. После дешифрации микроинструкции Р на основаниикода маски К операционный блок 3 ,вырабатывает внутренние сигналы переноса из младших разрядов в старшие .и самый старший перенос, являющийся БОвыходом переноса С 1. Суммарное времяФормирования достоверного сигналана выходе С 1 от начала такта обозначим 1:. После формирования сигналовпереноса через время 1 у операционный блок 3 может начинать выполнение микроинструкции Р. Для этого наего сикхровход СОБ подается синхроимпульс, начало которого задержано от начала такта на время г.с 1 + После окончания сикхроимпульса ка СОБ состояние ка шинах Р и К блока 3 должно быть сохранено в течение времени С до завершения всех переходных процессов внутри операционного блока 3. После выработки операционным блоком 3 сигнала на выход С 1 появляется возможность достоверного выполнения операций занесения и хранения флажков в блоке микропрограммного управления, Эти операции достоверно выполняются по второму синхроимпульсу на С . Начало этого синхроимпульса должно быть задержано на время 1 ут предустановки сигнала на входе признака Р 1 блока 2, После окончания этого синхроимпульса состояние ка входах управления флагом УФ блока 2 должно быть сохранено на время ТсФ до окончания переходных процессов в этом блоке. Таким образом можно выделить три пути распространения сигналов в микропроцессоре, определяющих длительность такта Тбеусь при безусловном пере - ходе:ТБеъуси, УУ + ц емУ + й + Д О 3еТеезуел " "с 1 + г ур + е ьмЧ + "сИУТееусе, с + "ус + "ц + смДлительность такта Тье усе бУдетравна наибольшей из величин Тьецсее йТьер се, или Т ье 3 усь опРеделЯемых выбором конкретной элементной базы, Длительность такта Т 1 генератора должна быть равной Т , фазовые задержки ь ь и с генератора 4 должны обеспечить временные задержки всех сикхроимпульсов относительно начала такта на вышеупомянутыевремена предустановки 1,уу, Сс 1 + + ур , с + Чс . Формирователи импульсов 6, 7 и 8 обеспечивают необходимую длительность синхроимпульсов. Рассмотрим такт с условным переходом,. Признак перехода ПП в микрокоманде программируется в этом случае в состояние лог. 0. По сигналу выхода ПП блока 1 генератор 4 переходит в режим формирования импульсов с периодом Т 2. Фазовые сдвиги выходных импульсов генератора 4 ке изменяются: они равны Ь,и с , Так как на первом входе элемента 2 И-ИЛИ-НЕ 5 находится состояние лог. "0", поступающее с блока 1, то

СмотретьЗаявка

3544720, 26.01.1983

ОПЫТНО-КОНСТРУКТОРСКОЕ БЮРО СПЕЦИАЛЬНЫХ РАДИОТЕХНИЧЕСКИХ СИСТЕМ НОВГОРОДСКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

МИНУТИН ЛЕОНИД ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 15.02.1985

Код ссылки

<a href="https://patents.su/8-1140126-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для сопряжения вычислительной машины с каналами связи

Следующий патент: Устройство для перебора сочетаний

Случайный патент: Способ измерения фазовых искажений канала воспроизведения запоминающих устройств с магнитным носителем