Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 985790

Авторы: Благодарный, Тимонькин, Ткаченко, Харченко

Текст

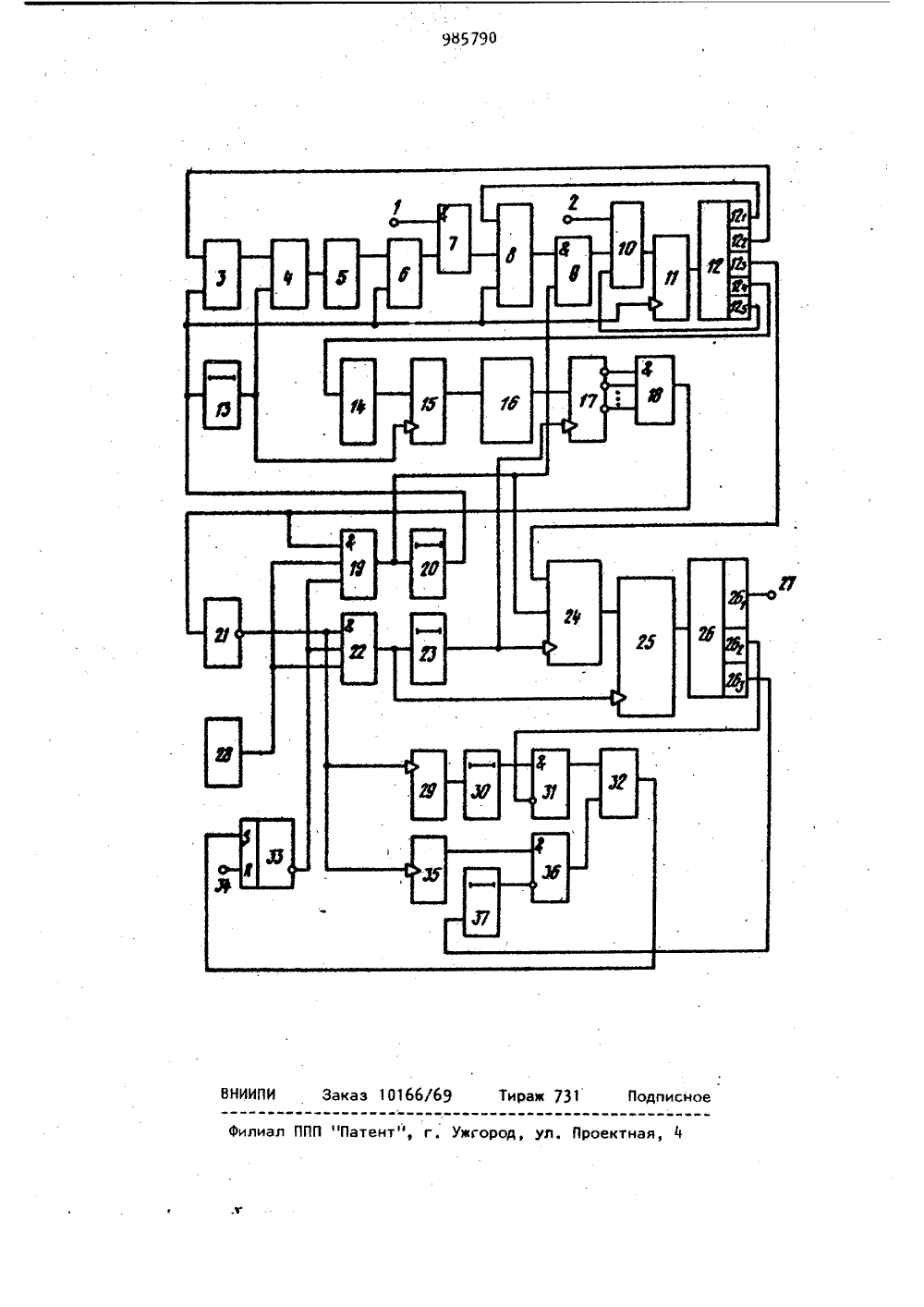

(54)МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ 1Изобретение относится к вычислительной технике и может быть использовано при построении процессоров ЭВМ.Известно микропрограммное устройство управления, содержащее два блока памяти, буферный и адресный. регистры, счетчик микрокоманд, дешиг раторы, генератор импульсов, элементы задержки и логические элементы И, НЕ 1.Недостатком указанного устройства является сложность, низкая универсальность, отсутствие контроля пра-. вильности работы.Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является микропрограммное устройство управления, содержащее регистр логических условий, первый блок элементов И, буферный регистр, второй блок элементов И, первый регистр адреса, первый и второй дешифраторы, первый и 2второй блоки памяти, счетчик адреса. счетчик микрокоманд, генератор тактовых импульсов первый второй итретий элементы И, элемент НЕ, первый и второй элементы задержки, приз чем выход генератора импульсов соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с выходом элемента. НЕ, вход ко О торого соединен с выходом третьегоэлемента И и вторым входом первогоэлемента И, выход первого элементазадержки соединен с входом второгоэлемента задержки, установочный входсчетчика адреса соединен с первымвходом первого блока элементов И, выход которого соединен с первым входом первого блока элементов И, выход которого соединен с первым ин"формационным входом первого регистра адреса, второй информационный входкоторого является внешним входом устройства, установочный вход соединенвходом буферного регистра, второй информационный вход которого соединен с выходом второго блока элементов И, первый вход которого подключен квходу логических условий устройства,второй вход = к выходу регистра логических условий, установочный вход которого соединен с установочным вхо:дом буферного регистра и управляющим 3 98579 с первым выходом первого блока памяти, а выход - с информационным входом первого дешифратора, выход которого соединен с входом первого блока памяти, второй выход которого соединен с первым информационным входом буферного регистра, второй информационный вход которого соединен с выходом второго блока элементов И, первый вход которого является входом кода логических условий, а второй вход соединен с выходом регистра логических условий, установочный вход которого соединен с установочным входом буферного регистра и управляющим входом первого 1 дешифратора, третий вход первого , блока памяти соединен с информационным входом счетчика адреса, выход которого соединен с информационным входом второго дешифратора, управляющий вход которого соединен с выходом второго элемента И, а выход с входом второго блока памяти, выход которого является выходом устройства, выходы счетчика микрокоманд сое динены с входами третьего элемента И 2.Недостатками этого устройства являются низкая универсальность, которая обусловливает неудобство эксплуатации и низкую приспособленность к модернизации,и отсутствие контроля правильности функционирования устройства.Цель изобретения - повышение достоверности функционирования микропрограммного устройства управления,Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее регистр логических условий, первыи и второй блоки элементов И,буферный регистр, первый 40 регистр адреса, первый и второй дешифраторы, первый и второй блоки памяти, счетчик адреса, счетчик микро- команд, генератор тактовых импульсо первый, второй и третий элементы И, элемент НБ, первый и второй элементы задержки, причем выход генератора импульсов соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с вы 50 ходом элемента НЕ, вход которого соединен с выходом третьего элемента И и вторым входом первого элемента И,выход первого элемента задержки соединен с входом второго элемента задержки, установочный вход счетчика адреса соединен с первым входом первого блока элементов И,выход которого соединен с первым ин. формационным входом первого регистра адреса, второй информационный вход которбго соединен с входом ко. да операции. устройства, установочный вход - с выходом метки первого блока памяти, а выход - с информационным входом первого дешифратора, выход которого соединен с адресным входом первого блока памяти, выход косвенного адреса характеристик следующей микроподпрограммы которогосоединен с первым информационным входом первого дешифратора, выход начального адреса текущей микооподпрограммы первого блока памяти соединен синформационным входом счетчика адреса, выход которого соединен с информационным входом второго дешифратора, управляющий вход которого соединен с выходом второго элемента И, а выход - с адресным входом второго блока памяти, операционный выход которого подключен к выходу устройства, выходы счетчика микрокоманд соединены с входами третьего элемента И, дополнительно содержит третий и четвертый блоки памяти,тре" тий и четвертый дешифраторы, второй и третий регистры адреса, триггер, первый и второй одиовибраторы, третий, цетвертый и пятый элементы задержки, цетвертый и пятый элементы И, элемент ИЛИ, причем информационный вход второго регистра адреса соединен с выходом адреса кода логических условий первого блока памяти, установочный вход - с выходом первого элемента задержки, а выход - с информационным входом третьего дешифратора, выход которого подключен к.адресному входу третьего блока памяти, выход которого соединен с информационным входом регистра логических условий, управляющий вход третьего дешифратора соединен с выходом второго элемента задержки и управляющим входом четвертого дешиф ратора, выход которого соединен с адресным входом четвертого блока па 45 9857мяти, выход которого соединен с информационным входом счетчика микрокоманд, информационный вход четвертого дешифратора соединен с выходомтретьего регистра адреса, информа- .ционный вход которого соединен с выходом адреса кода числа микрокомандпервого блока памяти, установочныйвход третьего регистра адреса соединен с выходом первого элемента задержки, выход второго элемента И через третий элемент задержки соединен со счетными входами счетчика адреса и счетчика микрокоманды, выходэлемента НЕ соединен с входами первого и второго одновибраторов, выходпервого. одновибратора через четвертый элемент задержки соединен с первым входом четвертого элемента И, выход которого соединен с первым входомМэлемента ИЛИ, а второй вход - с выходом метки начала микроподпрограммывторого блока памяти, выход метки конца микроподпрограммы которого черезпятый элемент задержки соединен с перунвым входом пятого элемента И, второйвход которого соединен с выходом второго одновибратора, выход пятого элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен З 0с единичным входом триггера, нулевойвыход которого соединен с третьимивходами первого и второго элементовИ, нулевой вход триггера подключенк входу сброса устройства, выходпервого элемента И соединен с входомпервого элемента задержки,На чертеже представлена функциональная схема предлагаемого устройства.40Устройство содержит вход 1 логических условий устройства, вход 2кода операций устройства, регистр 3адреса, дешифратор 4, блок 5 памяти,регистр 6 логических условий, блок7 элементов И, буФерный регистр 8,блок 9 элементов И, регистр 10 адреса, дешифратор 11, блок 12 памятиэлемент 13 задержки, регистр 14: адреса, дешифратор 15, блок 16 памяти,счетчик 1). микрокоманд, эле-мент И 18, элемент И 19, эле мент 20 задержки, элемент НБ 21, эле. мент И 22, элемент 23 задержки, счетчик 24 адреса, дешифратор 25 блок26 памяти, операционный выход 27устройства, генератор 28 тактовых импульсов, одновибратор 29, элемент 30задержки, элемент И 31, элемент90 6ИЛИ 32, триггер 33, вход 34 сброса устройства, одновибратор 35, элемент И 36, элемент 37 задержки.Предлагаемое устройство Функционирует следующим образом.В исходном состоянии регистры 10;3 и 14, счетчики 17 и 24, буферный регистр 8 находятся в нулевом состоянии.Код операции с входа 2 поступает на регистр 10. Очередной импульс с генератора 28 через открытый элемент И 19 поступает на элемент 20 задержки. Сигнал с выхода элемента 20 поступает на вход элемента 13 задержки, устанавливает в нулевое состояние регистр 6 логических условий, регистр 3 адреса, буферный регистр 8 и запускает дешифратор 11, который по адресу, поступающему на его информационный вход с выхода ре" гистра 10 адреса, считывает структурную характеристику очередной микроподпрограммы с блока 12 памяти. При этом с выхода 12 первого блока 12 памяти в буферный регистр 8 записывается косвенный адрес структурной характеристики следующей микроподпрограммы. С выхода 12 блокапамяти в регистр 3 адреса записывается адрес кода проверяемымилогических условий в конце выйолнения текущей микроподпрограммы ( если после выполнения микроподпрограммы.логические условия не проверяются, то в регистр 3 адреса записывается нулевой код. С выхода 12 блока 12 в регистр 14 записывается адрес кода длины микроподпрограммы (числа операционных микрокоманд в ней),С выхода 12 з блока 12 памяти в счетчик 24 адреса записывается код адреса первой операционной микрокомандымикроподпрограммы. СИгналом с выхо-: да 12 блока 12 .памяти регистр 10 адреса устанавливается в нулевое. состояние.Сигнал с выхода элемента 13 задержки запускает дешифраторы 4 и 15, При этом по адресу, записанному в регистре 3 адреса, из блока 5 памяти считывается код проверяемого логического условия и записывается в регистр 6 логических условий, а также по адресу, записанному в регистре 14 адреса, из блока 16 памяти считывается код числа операционных микрокоманд в микроподпрограмме и записывается в счетчик 17 микрокоманд.При этом сигнал на выходе элемента И 18 становится равным нулю, ана выходе элемента НЕ 21 - единице.В данном случае возбуждается одновибратор 29 и выдает сигнал на вход, элемента 30 задержки. Следующий тактовый импульс с выхода генератора 28через открытый элемент И 22 поступает на элемент 23 задержки и на управляющий вход дешифратора 25, При этом 10происходит считывание с блока 26 памяти по адресу, записанному в счетчике 21 адреса, первой операционноймикрокоманды микроподпрограммы. С выхода 26 первое поле операционной 15микрокоманды ( код микроопераций ) поступает на выяод 27 устройства, сигнал с поля операционной микрокоманды(метка начала микроподпрограммы),через выход 26 блока 26 памяти посту- епает на инверсный. вход элемента И 31,Причем на первый .вход элемента И 31в это же время поступает сигнал с выхода элемента 30. При этом на выходеэлемента И 31, а следовательно, и на 25единичном входе триггера 33 сигналотсутствует. Это соответствует исправному состоянию устройства. Еслисигнал с выхода 262 блока 26 памятиотсутствует (что соответствует не- ЗОисправному функционированию управляющей системы ), то сигнал с выходаэлемента И 31 поступает через элементИЛИ 32 на единичный вход триггера 33,устанавливает его в единичное состояние,При этом элементы И 19 и 22 закрываются по первому входу, тактовыеимпульсы с выхода генератора 28 насистему не поступают.После устранения отказа триггер33 устанавливается в нулевое состояние сигналом на его нулевой вход свхода 3 ч. Функционирование устройства продолжается После считывания первой операционной микрокомандыпри правильном Функционировании системы импульс с выхода элемента 23воздействует. на счетный вход счетчи-.ка 2 М адреса, увеличивая его содержимое на единицу и формируя такимобразом адрес следующей операционной микрокоманды,и на счетный входсчетчика 17 микрокоманд, При этомего содержимое уменьшается на единицу и формируется код числа микрокоманд, оставшихся невыполненными.По следующему импульсу генератора 28 производится считывание следующей операционной микрокоманды текущей микроподпрограммы иэ блока 26памяти, При выполнении всех остальных операционных микрокоманд системафункционирует аналогично,При выполнении последней операционной микрокоманды текущей микропод;программы с ее третьего поля черезвыход 26 З блока 26 памяти считываетсяметка конца микроподпрограммы и поступает на элемент 37 задержки. Послесчитывания последней микрокомандысчетчик 17 микрокоманд устанавливается в нуль. При этом на выходеэлемента И 18 формируется сигнал,который открывает элемент И 19 изапускает через элемент НЕ 21 одновибратор 35. Если считывание микрокоманды происходит правильно (навыходе элемента И 36 сигнал отсутствует Р, то система переходит к выполнению следующей микроподпрограммы.Очередной тактовый импульс с генератора 28 через открытый элементИ 19 открывает блок 9 элементов И,через который адрес структурной характеристики следующей микроподпро.граммы с буферного регистра 8 поступает в регистр 1 О адреса.На блоке 7 элементов И происходит проверка значения логических условий, код которых записан в регистре 6 логических условий. Сигналы логических условий поступают с входа1 устройства на второй вход блока 7элементов И, Сигналы с выхода блока7 элементов И модифицируют адресструктурной характеристики 1-й микроподпрограммы, хранящейся в буферном регистре 8, в соответствии со значениями поступающих сИгналов логических условий. Далее импульс выходаэлемента 20 задержки запускает дешифратор 11, который по адресу, записанному в регистре 10 адреса, считывает с блока 12 памяти структурную характеристику 1-й микроподпрограммы.Далее устройство функционируетаналогично описанному выше алгоритму.Изменение одной из структурныххарактеристик микропрограммы требуетзамены только одного блока памяти,что повышает универсальность, уменьшает стоимость модернизации и повышает гибкость микропрограммирования.Раздельная запись параметров микропрограммы без повторений увеличивает степень информативного запол5 16 35 45 нения каждого блока памяти до единицы, что повышает экономичность системы.Неправильное считывание, йередача или запись начального адреса линейной последовательности, числа микрокоманд в линейной последоватвльности, пропуск одной или несколькихмикрокоманд, ложное считывание нескольких микрокоманд фиксируются схемой контроля, и дальнейшее неправиль-ное функционирование устройства прекращается. Это повышает достоверностьфункционирования устройства. Формула изобретения Микропрограммное устройство управления, содержащее регистр логических 20условий, первый и второй блоки элементов И, буферный регистр, первыйрегистр адреса, первый и второй дешифраторы, первый и второй блоки памяти, счетчик адреса, счетчик микрокоманд, генератор тактовых импульсов,первый, второй и третий элементы И, элемент НЕ, первый и второй элементы задержки, причем выход генератора тактовых импульсов соединен с пер-зовым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом третьего элемента И и вторым входом первого элемента И, выход первого элемента задержки соединен с входом второго элемента за;держки, установочный вход счетчика адреса соединен с первым входом первого блока элементов И, выход которого соединен с первым информационным входом первого регистра адреса, второйинформационный вход которого .соединен с входом кода. операции устройства, установочный вход - с выходом метки первого блока памяти, а выход - с информационным входом первого дешифратора, выход которого соединен с адресным входом первого блока памяти, выход косвенного адресахарактеристик следующей микроподпрограммы которого соединен с первым информационным входом буферного регистра, второй информационный вход которого соединен с выходом второго блока элементов И, первый вход которогоподключен к входу логических условийустройства, второй вход - к выходу регистра логических условий, установочный вход которого соединен с установочным входом буферного регистра и.управляющим входом первого дешифраторра, выход начального адреса текущеймикроподпрограммы первого блока памяти соединен с информационным входом.счетчика адреса, выход которого соединен с информационным входом второго,дешифратора, управляющий вход которого соединен с выходом второго элементаИ,а выход.- с адресным входом второгоблона памяти, операционный выход которого подключен к выходу устройства,выходы счетчика микрокоманд соединены с входами третьего элемента И,о т л и ч а ю щ е е с я тем, что,с целью повышения достоверности функционирования, она дополнительно содержит третий и четвертый блоки памяти, третий и четвертый дешифраторы,второй и третий регистры адреса, триггер, первый и второй одновибраторы,третий, четвертый и пятый элементызадержки, четвертый и пятый элементыИ, элемент ИЛИ, причем информационный вход второго регистра адреса соединен с выяодом адреса кода логических условий первого блока памяти, установочный вход - с выходом первого:элемента задержки, а выход - с информационным входом третьего дешифрато"ра, выход которого подключен к адресному входу т.ретьего блока памяти, выход которого соединен с информационным входом регистра логическихусловий, управляющий вход третьегодешифратора соединен с выходом второго элемента задержки и управляющимвходом четвертого дешифраторавыход которого соединен с адресным входом четвертого блока памяти, выходкоторого соединен с информационнымвходом счетчика микрокоманд, информационный вход четвертого дешифратора соединен с выходом третьего регистра. адреса, информационныи входкоторого соединен с выходом адресакода числа микрокоманд первого блокапамяти, установочный вход третьегорегистра адреса соединен с выходомпервого элемента задержки, выход второ"го элемента И. через третий элемент задержки соединен со счетными входамисчетчика адреса и счетчика микроко-,манды, выход элемента НЕ соединен свходами первого и второго одновибраторов, выход первого одновибраторачерез четвертый элемент задержки сое 11, 985790 12динен с первым входом четвертоговыход которого соединен с третьимиэлемента И, выход которого соединен входами первого и второго элементовс первым входам элемента ИЛИ, а вто- И, нулевойвход триггера подключенрой вход - с выходом метки начала к входу сброса устройства, выходпермикроподпрограммы второго блока па-вого элемента И соединен с входоммяти, выход метки конца микроподпро- первого элемента задержки.граммы которого через пятый элементзадержки соединен с первым входомИсточники информации,пятого элемента И, второй вход кото-, принятые во внимание при экспертизерого соединен с выходом второго од фв 1. Авторское свидетельство СССРновибратора, выход пятого элемента И Н 119893, кл. С 06 Р 9/22, 1972.соединен с вторым входом элемента 2Авторское свидетельство СССРИЛИ, выход которого соединен с еди- У 763898, кл. О 06 Р 9/22, 1 е 80ничным входом триггера, нулевой. (прототип).

СмотретьЗаявка

3322339, 27.07.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/7-985790-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления с исправлением ошибок

Следующий патент: Микропрограммный процессор с контролем

Случайный патент: Диспергатор