Логическое запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

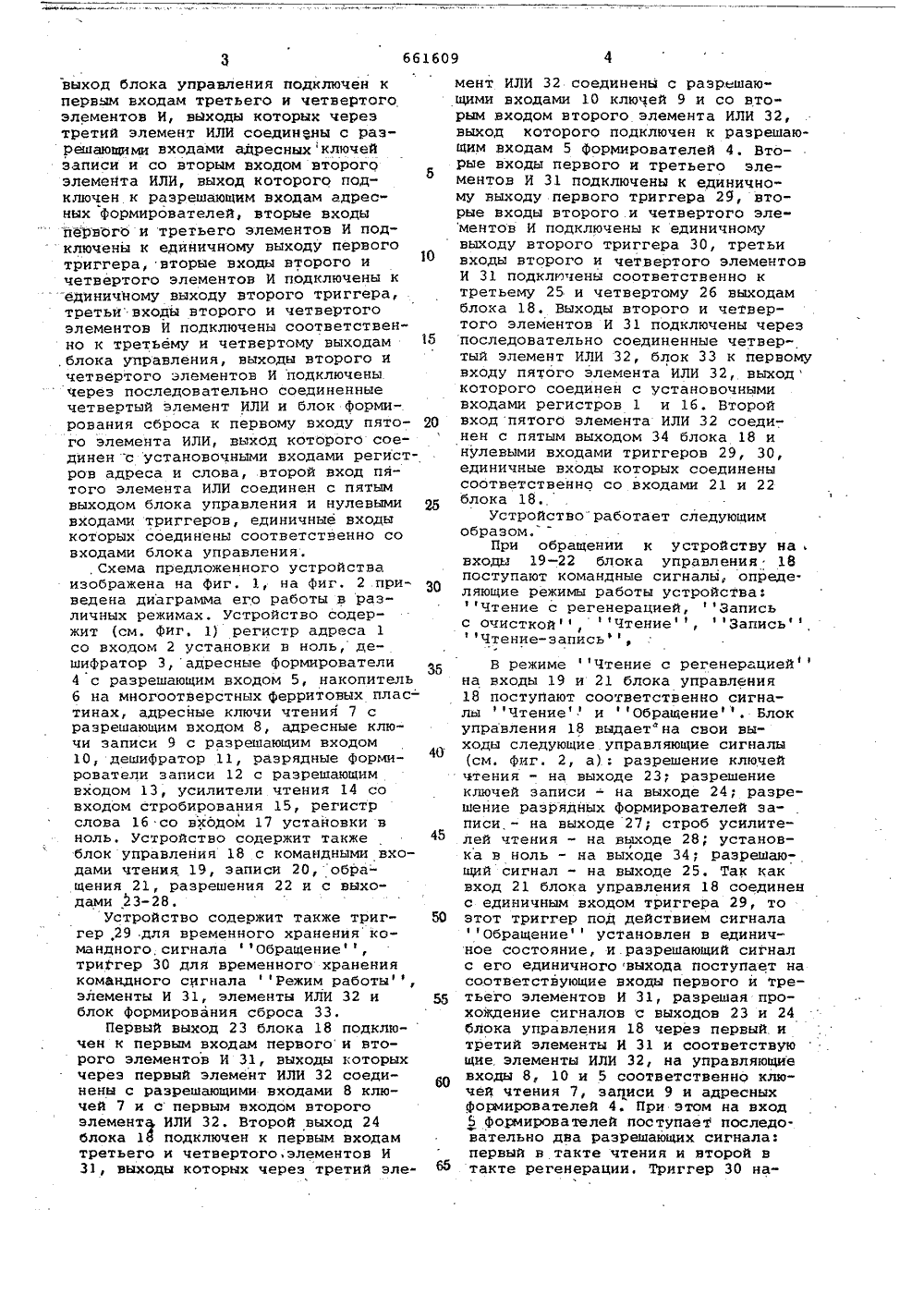

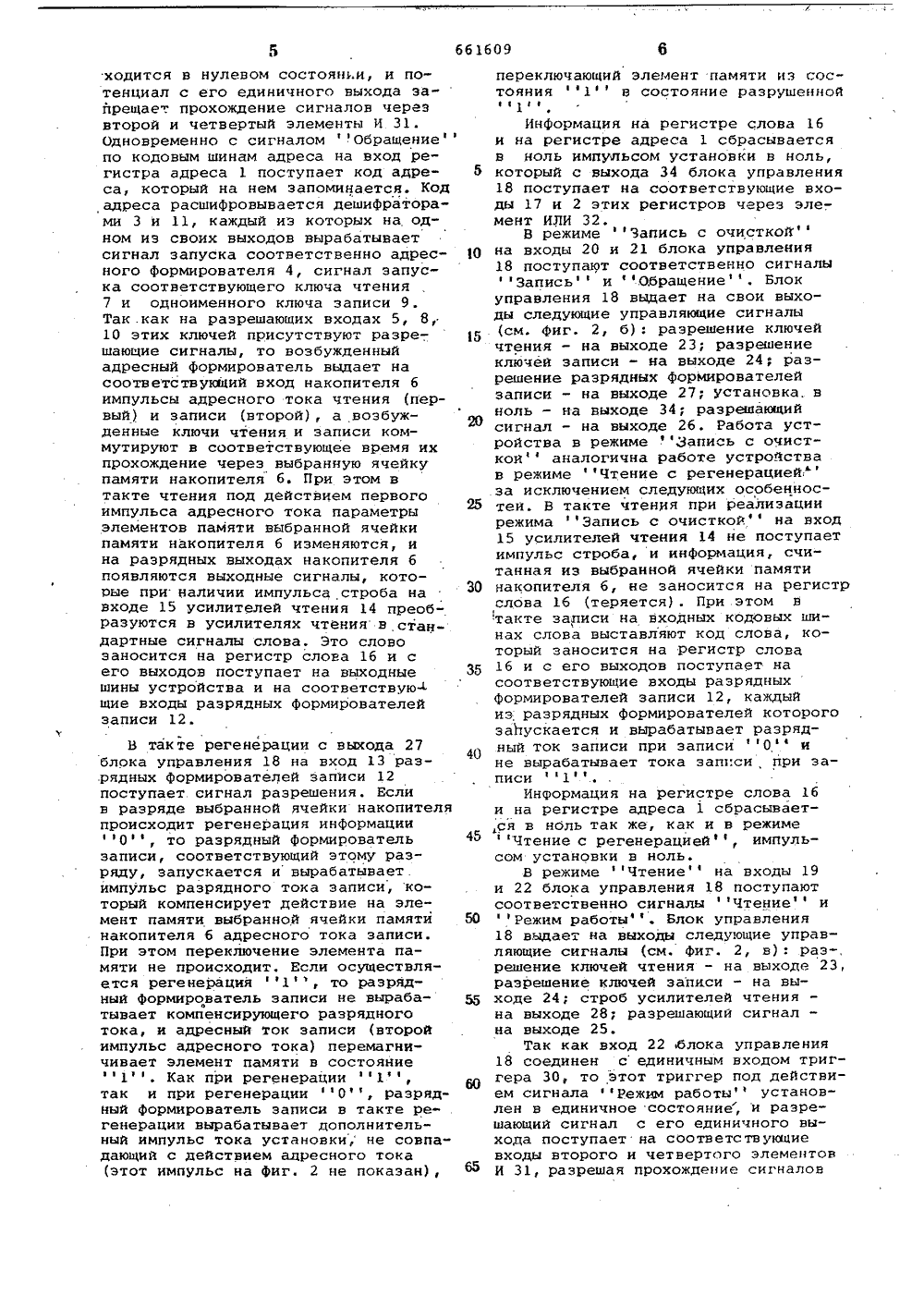

(22) Заявлено 070177(21) 2441552/18-24 присоединением заявки Ко О осударствеииый комитет СССР ио делам изобретений и открытийриоритет публиковено 050579 Бюллетень йо 17 ата опубликования описания 090579 Щ)( б 81. 32(71) Заявитель ена Ленила институт кибернетики АН УСС 54) ЛОГИЧЕСКОЕ ЗЛПОМИНЛЮЩЕЕ УСТРОИСТВС( аст Изобретение относится к обл и запоминающих устройств.Одно из известных устройств имеет в составе накопителя набор логических ячеек, которые отличаются от остальных ячеек накопителя более сложной прошивкой управляющих и выходных шин 11). Это требует не только усложнения структуры накопителя запоминающего устройства, увеличения электроники управления накоплтелем, но и организации работы устройства по специальной программе.Из известных устройств наиболее близким техническим решением к данному изобретению является логическое запоминающее устройство, содержащее регйстр адреса, подключенный к дешифраторам, выходы которых через адресные формирователи и адресные ключи записи и чтения соединены со . входами накопителя, подключенного к разрядным формирователям записи и через усилители чтения соединенного с регистром слова, блок управления 2).Недостается низканость, тактолько два тком этого устройства являя функциойальная возможкак он может реализовать. режима работы (Чтение 2с регенерациейф, 1 фЗапись с очисткой,) и выполнять только, свои классические Функцииг запись инФормациив накопитель, ее хранение и выдачу (чтение) информации из блЬка накопителя. Это снижает также областьприменения устройства,Другим недостатком устройстваявляется неэффективное использованиевремени цикЛа работы устройства, таккак в нем исключается возможностьчтения информациииз одной ячейкинакопителя и записи другой информации в ту же или любую другую ячейку15 накопителя за время одного циклаобращения к устройству, что снижаетбыстродействие устройства.Целью настоящего изобретения является расширение области примененияи повышение быстродействия устройства. Поставленная цель достигаетсятем, что устройство содержит тригге"ры, блок Формирования сброса и эле- .менты И и ИЛИ, причем первый выходблока управлейия подключен к.первымвходам первого и второго элементов И,выходы которых через первый элементИЛИ соединены с разрешающими входамиадресных ключей чтения и с первым вхоЗО дом второго элемента ИЛИ, второйвыход блока управления подключен кпервым входам третьего и четвертогоэлементов И, выходы которых черезтретий элемент ИЛИ соединдны с разрешающими входами адресныхключейзаписи и со вторым входом второгоэлемента ИЛИ, выход которого подключен к разрешающим входам адресных формирователей, вторые входыпервого и третьего элементов И подключены к единичному выходу первоготриггера, вторые входы второго и10четвертого элементов И подключены кединичному выходу второго триггера,третьи входы второго и четвертогоэлементов И подключены соответственно к третьему и четвертому выходам,блока управления, выходы второго ичетвертого элементов И подключенычерез последовательно соединенныечетвертый элемент ИЛИ и блок формирования сброса к первому входу пятого элемента ИЛИ, выхбд которого соединен "с установочными входами регистров адреса и слова, второй вход пятого элемента ИЛИ соединен с пятымвыходом блока управления и нулевымивходами триггеров, единичные входыкоторых соединены соответственно совходами блока управления., Схема предложенного устройстваизображена на фиг, 1, на фиг. 2.приведена диаграмма его работы в различных режимахУстройство содержит (см, фиг, 1) регистр адреса 1со входом 2 установки в ноль, дешифратор 3,адресные формирователи4 с разрешающим входом 5, накопительб на многоотверстных ферритовых плас-тинах, адресные ключи чтения 7 сразрешающим входом 8, адресные ключи записи 9 с разрешающим входом10, дешифратор 11, разрядные формирователи записи 12 с разрешающимвходом 13, усилители чтения 14 совходом стробирования 15, регистрслова 16 со входом 17 устайовки вноль. Устройство содержит также 45блок управления 18 с командными входами чтения 19, записи 20, обра- щения 21, разрешения 22 и с выходами 23-28,Устройство содержит также триггер,29 для временного хранениякомандного, сигнала Обращение,триггер 30 для временного хранениякомандного сигнала Режим работы,элементы И 31, элементы ИЛИ 32 и Мблок формирования сброса 33.Первый выход 23 блока 18 подключен к первым входам первогои второго элементов И 31, выходы которыхчерез первый элемент ИЛИ 32 соедииены с разрешающими входами 8 ключей 7 и спервым входом второгоэлемента ИЛИ 32. Второй выход 24блока 18 подключен к первым входамтретьего и четвертого, элементов И31, выходы которых через третий элемент ИЛИ 32 соединены с разрешающими входами 10 ключей 9 и со вторым входом второго элемента ИЛИ 32,выход которого подключен к разрешающим входам 5 формирователей 4. Вторые входы первого и третьего элементов И 31 подключены к единичному выходу первого триггера 29, вторые входы второго и четвертого элементов И подключены к единичномувыходу второго триггера 30, третьивходы второго и четвертого элементовИ 31 подключены соответственно ктретьему 25 и четвертому 26 выходамблоха 18. Выходы второго и четвертого элементов И 31 подключены черезпоследовательно соединенные четвертый элемент ИЛИ 32, блок 33 к первомувходу пятого элемента ИЛИ 32, выходкоторого соединен с установочнымивходами регистров 1 и 16. Второйвход пятого элемента ИЛИ 32 соединен с пятым выходом 34 блока 18 инулевыми входами триггеров 29, 30,единичные входы которых соединенысоответственно со входами 21 и 22блока 18.Устройство работает следующимобразом.При обращении к устройству навходы 19-22 блока управления 18поступают командные сигналы, определяющие режимы работы устройства:Чтение с регенерацией, Записьс очисткой, Чтение, Запись,Чтение-запись,В режиме Чтение с регенерацией"на входы 19 и 21 блока управления18 поступают соответственно сигналы Чтение и Обращение. Блокуправления 18 выдает"на свои выходы следующие управляющие сигналы(см, фиг. 2, а): разрешение ключейчтения - на выходе 23; разрешениеключей записи вна выходе 24; разрешение разрядных формирователей записи, - на выходе 27; строб усилителей чтения - на выходе 28; установка в ноль - на выходе 34; разрешаюшдй сигнал - на выходе 25. Так каквход 21 блока управления 18 соединенс единичным входом триггера 29, тоэтот триггер под действием сигналаОбращение установлен в единичное состояние, и.разрешающий сигналс его единичного выхода поступает насоответствующие входы первого и третьего элементов И 31, разрешая прохождение сигналов с выходов 23 и 24блока управления 18 через первый итретий элементы И 31 и соответствующие. элементы ИЛИ 32, на управляющиевходы 8, 10 и 5 соответственно ключей чтения 7, записи 9 и адресныхформирователей 4. При этом на вход5 формирователей поступает последовательно два разрешающих сигнала:первый в такте чтения и второй втакте регенерации. Триггер 30 находится в нулевом состоянии, и потенциал с его единичного выхода запрещае . прохождение сигналов черезвторой и четвертый элементы И 31.Одновременно с сигналом Обращениепо кодовым шинам адреса на вход регистра адреса 1 поступает код адреса, который на нем запоминается. Кодадреса расшифровывается дешифраторами 3 и 11, каждый из которых на одном из своих выходов вырабатываетсигнал запуска соответственно адресного формирователя 4, сигнал запуска соответствующего ключа чтения7 и одноименного ключа записи 9.Так .как на разрешающих входах 5, 8,10 этих ключей присутствуют разрешающие сигналы, то возбужденныйадресный формирователь выдает насоответствукщий вход накопителя 6импульсы адресного тока чтения (первый) и записи (второй), а возбужденные ключи чтения и записи коммутируют в соответствующее время ихпрохождение через выбранную ячейкупамяти накопителя 6. При этом втакте чтения под действием первогоимпульса адресного тока параметрыэлементов памяти выбранной ячейкипамяти накопителя б изменяются, ина разрядных выходах накопителя 6появляются выходные сигналы, которые при наличии импульса строба навходе 15 усилителей чтения 14 преобразуются в усилителях чтения в стандартные сигналы слова. Это словозаносится на регистр слова 16 и сего выходов поступает на выходныешины устройства и на соответствую-щие входы разрядных формирователейзаписи 12. В такте регенерации с выхода 27 блока управления 18 на вход 13 раз.рядных формирователей записи 12 поступает сигнал разрешения. Если в разряде выбранной ячейки накопителя происходит регенерация информации 0, то разрядный формирователь записи, соответствующий этому разряду, запускается и вырабатывает импульс разрядного тока записи, который компенсирует действие на элемент памяти выбранной ячейки памяти накопителя 6 адресного тока записи. При этом переключение элемента памяти не происходит. Если осуществляется регенерация ф 1, то разрядный формирователь записи не вырабатывает компенсирующего разрядного тока, и адресный ток записи (второй импульс адресного тока) перемагничивает элемент памяти в состояние 1 ф. Как при регенерации 1, так и при регенерации Оф, разрядный Формирователь записи в такте регенерации вырабатывает дополнительный импульс тока установки, не совпадающий с действием ацресного тока (этот импульс на фиг. 2 не показан),15 О 5 Ю 30 35 40 45 50 55 60 65 переключающий элемент памяти нз состояния 1 в состояние разрушенной 11 4 1Информация на регистре слова 16 и на регистре адреса 1 сбрасывается в ноль импульсом установки в ноль, который с выхода 34 блока управления 18 поступает на соответствующие входы 17 и 2 этих регистров через элемент ИЛИ 32.В режиме Запись с очисткойф на входы 20 и 21 блока управления 18 поступают соответственно сигналы Запись и фОбращение. Блок управления 18 выдает на свои выходы следующие управляющие сигналы (см. Фиг. 2, б): разрешение ключей чтения - на выходе 23; разрешение ключей записи - на выходе 24; разрешение разрядных формирователей записи - на выходе 27; установка, в ноль - на выходе 34; разрешающий сигнал - на выходе 26. Работа устройства в режиме Запись с очисткой аналогична работе устройства в режиме Чтение с регенерацией за исключением следующих особенностеи. В такте чтения при реализации режима Запись с очисткой на вход 15 усилителей чтения 14 не поступает импульс строба, и информация, считанная из выбранной ячейки памяти накопителя 6, не заносится на регистр слова 16 (теряется)При этом в такте записи на входных кодовых шинах слова выставляют код слова, который заносится на регистр слова 16 и с его выходов поступает на соответствующие входы разрядных формирователей записи 12, каждый из разрядных формирователей которого запускается и вырабатывает разрядный ток записи при записи 0 и не вырабатывает тока записи, при записи 1 фИнФормация на регистре слова 16 и на регистре адреса 1 сбрасывает,ся в нбль так же, как и в режиме Чтение с регенерацией, импульсом установки в ноль.В режиме Чтение на входы 19 и 22 блока управления 18 поступают соответственно сигналы Чтение и Режим работыф. Блок управления 18 выдает на выходы следующие управляющие сигналы (см, фиг. 2, в): раз-, решение ключей чтения - на выходе 23, разрешение ключей записи - на выходе 24; строб усилителей чтения на выходе 28; разрешающий сигнал - на выходе 25.Так как вход 22 блока управления 18 соединен с единичным входом триггера 30, то этот триггер под действием сигнала фрежим работыф установлен в единичное состояние, и разрешающий сигнал с его единичного выхода поступает на соответствукшие входы второго и четвертого элементов И 31, разрешая прохождение сигналов661609 10 с выиода 23 блока управления 18 через второй элемент И 31 и соответствующие элементы ИЛИ 32 на управляющиевходы 8 и 5 соответственно ключейчтения 7 адресных формирователей 4(первый импульс). При этом на выходе 26 блока управления 18 сигналотсутствует, и поэтому на вход 10ключей записи 9 разрешающего сигналане поступает исоответственно навходе 5 адресных формирователей отсутствует второй разрешающий сигнал,Триггер 29 находится в нулевом"состоянии, и потенциал с его единичного выхода запрещает прохождение сиг-налов с выходов 23 и 24 блока управления 18 через первый и третий элементы И 31. Однсвременно с сигналомРежим работы по кодовым шинамадреса на вход регистра адреса 1поступает код адреса, который на немзапоминается. Код адреса расшифровывается дешифраторами 3, 11, каждыйиз которых на одном из своих выходов соответственно вЫрабатывает сигнал запуска адресного формирователяблока 4, сигнал запуска соответствую;щего ключа чтения 7 и одноименно-,го ключа записи 9. Так как разрешающий сигнал присутствует на входе 8ключей 7, а на входе 5 адресныхформирователей 4 присутствует только первый разрешающий импульс, товозбужденный адресный формировательвыдает на соответствующий вход накопителя б только импульс адресноготока чтения (первый), а возбужденный 35ключ чтения 7 коммутйрует его прохождение через выбранную ячейку, памяти накопителя. б. При этом под действием гдресного тока параметры элементов памяти выбранной ячейки нако 40пителя б изменяются и на разрядныхвыходах накопителя б появляются выходные сигналы, которые при наличииймпульса с;роба на входе 15 усилителей чтения 14 преобразуются в усилителях чтения в стандартные .сигналыслова. Это слово заносится на регистр слова 16 и с его вьходов пос тупает на выходные шины устройстваи на соответствующие входы Разрядных Формирователей записи 12.Информация на регистре слова 16и регистре адреса 1 сбрасывается вноАь -импульсом установки в ноль,который Формируется по длительности 58сразу же после окончания импульсаадресного тока чтения блоком формирования сброса 33, на вход которой через элемент ИЛИ 32 поступаетсигнал с выхода второго элементаИ 31. В связи с отсутствием второгоимпульса адресного тока и разрешающего сьгнала на входе 13 разрядныхформирователей записи 12 такт регенерации при работе устройства в режиме Чтение не выполняется,8В режимеЗаписьна в.ходы 20 и 22 блока управления 18 поступают ,соответственно сигналы Записьф и ,Режим работы, Влок местного управления 18 выдает на выходы следующие управляющие сигналы (см.1 ФИГ 2 г): разрешение ключей чтения- . на выходе 23, разрешение ключей записи - на выходе 24, разрешающий сигнал - на выходе 26 1 разрешение разрядных формирователей записи - на выходе 27.При этом триггер 30 так же, как а при.,выполнении режима Чтение 4 установлен в единичное состояние, а триггер 29 - в нулевое. Однако в отличие от режима Чтение в режиме Запись вместо разрешающего сигнала на выходе 23 блока управления 18 вырабатывается сигнал на выходе 2 б,этого же блока, поэтому сигнал с выхода 24 блока управления 18 через четвертый элемент И 31 и соответствующие элементы ИЛИ 32 поступает на разрешающие входы 10 и 5 соответственно ключей записи 9 и адресных формирователей 4. При этом адресный формирователь вырабагывает только второй импульс адресного тока (такт записи), и в тот же момент времени открывается соответствующий ключ записи, коммутирующий прохождение этого тока через выбранную ячейку памяти накопителя б. Одновременно с сигналом разрешения ключей записи на входных кодовых шинах слова выставляют код слова, которыйзаносится на регистр слова 16 и с его выходов поступает на соответствую" щие входы блока разрядных формирователей записи 12, ка;кдый из разрядных формирователей которого запускается и вырабатывает разрядный ток записи при записи 0 и не вырабатывает тока записи при записи 1.Информация на регистре слова 16 и на регистре адреса 1 сбрасываетсяв ноль импульсом установки вноль, который Формируется по длительности сразу же после окончания импульсаадресного тока записи блоком Формирования сброса 33, на вход которойчерез элемент ИЛИ 32 поступает сигнал с выхода четвертого элемента И 31.В связи с отсутствием первогоимпульса адресного така такт чтенияпри работе с устройства в режимеЗапись не выполняется, что даетвоэможность осуществлять запись информации в любую ячейку накопителя безее предварительной очистки, Еслив выбранной ячейке накопителя находилось слово А и осуществляетсязапись в нее слова В, то после реализации режима " Запись в этойячейке образуется слово С, как результат выполнения логической функцииИЛИ над словами А, В .Режим Чтение-запись ( см.фиг. 2, д) является комбинацией ре661609 формула изобретения с,. 76-79. 9жима Чтениеф и режима ЗаписьфПри этом на входы 19, 20, 22 блокауправгения 18 поступают командныесигналы: Чтение, Запись 1,Режим работы. Блок местного упраВления 18 выдает на свои выходы всеуправЛяющне сигналы, необходимЫе 5для выполнения режимов фЧтение иЗапись в отдельности: разрЕшезие ключей чтения - на выходе 23азрешение ключей записи - на выоде 24, разрешающие сигналы на вы- рходах 25 и 26; разрешение разрядныхформирователей записи - на выходе27; строб усилителей чтения - навыходе 28. При этом триггер 29 на.ходится в нулевом состоянии, а триггер 30 - в единичном достоянии,разрешаяпроходжение импульсов свыходов 23.и соответственно через второй и четвертый элементы И 31и соответствующие элементы ИЛИ 32 навходы 8, 10 и 5 ключей чтения,записи и адресных формирователей.При этом так же, как и в режиме.Чтение, адресный формировательвырабатывает первый импульс адресного тока, который осуществляет считывание информации из ячейки памятинакопителя 6, а затем так же, как врежиме Запись - второй импульсадресного тока для записи считаннойили любой другой информации в эту ЗОже или любую другую ячейку памятинакопителя б, причем информация нарегистр адреса 1 и регистр слова16 заносится в йачале такта чтенияи как в режиме Чтение сбрасывается в ноль в конце этого такта,а затем на эти же регистры в началетакта записи заносится новая информация, которая, как в режиме Запись,сбрасывается в ноль в конце такта 40записи,В остальном работа устройства врежиме 1 Чтение-запись аналогичнаработе устройства сигнала в режимеЧтение а затем 1 Записьф,е45Таким образом, описанное устройство позволяет выполнять в любойячейке накопителя логическую функцию ИЛИ, что невозможно в прототипе, и осуществлять чтение информации из одной ячейки блока накопи- .теля и запись любой другой информации. в эту же или любую другую ячейкуза время одного цикла работы запоминающего устройства вместо требуе-.мого времеяи двух циклов прототипа 5521 Логйческое запоминающее устройствб, содержащее регистр адреса, подключенный к дешифраторам, выходы которых через адресные формирователи и адресные ключи записи и чтения соединены со входами накопителя, подключенного к разрядным Формирователям записи и через усилители.чтения соединенного с регистром слова, блок управления, о т л и ч а ю щ е е -с я тем, что, с целью расширенияобласти применений и повышения быстродействия устройства, оно содержиттриггеры, блок формирования сбросаи элементы И и ИЛИ, причем первыйвосход блока управленияподключен кпервым входам первого и второгоэлементов И, выходы которых черезпервыйэлемент ИЛИ соединены с разрешающими входами адресных ключейчтения и с первым входом второгоэлемента ИЛИ второй выход блокауправления подключен к первым входамтретьего и четвертого элементов И,выходы которых через третий элементИЛИ соединены с разрешающими входами адресных ключей, записи и со вторым входом второго .элемента ИЛИ,выход которогоподключен к разрешающим входам адресных формирователей,вторые входы первого и третьего элементов И подключены к единичномувыходу первого триггера, вторые входы второго и четвертого элементов Иподключены к единичному выходу второго триггера, третьи входы второгоя четвертого элементов И подключены соответственно к третьему и четвертому выходам блока управления, выходы второго и четвертого элементовИ подключены через последовательносоединенные четвертый элемент ИЛИ иблок Формирования сброса к первомувходу пятого элемента ИЛИ, выход которого соединен с установочными входами регистров адреса и слова, второи вход, пятого элемента ИЛИ сое- динен с пятым выходом блока управления и нулевыми входами триггеров,единичные входы которых соединенысоответственно со входами блока управления,Источники информации, принятые вовнимание при экспертизеСоставитель В. Рудакоцкая Техред Я,Бабурка Тираж 680И Государственного, комитета делам изобретений и открытий Москва ЖРа ская наб.

СмотретьЗаявка

2441552, 07.01.1977

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

ЯКОВЛЕВ ЮРИЙ СЕРГЕЕВИЧ, НОВИКОВ БОРИС ВАСИЛЬЕВИЧ, ЮРАСОВ АЛЕКСАНДР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G11C 15/00

Метки: запоминающее, логическое

Опубликовано: 05.05.1979

Код ссылки

<a href="https://patents.su/7-661609-logicheskoe-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Логическое запоминающее устройство</a>

Предыдущий патент: Оптоэлектронный элемент памяти

Следующий патент: Запоминающее устройство

Случайный патент: Способ получения отливок