Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

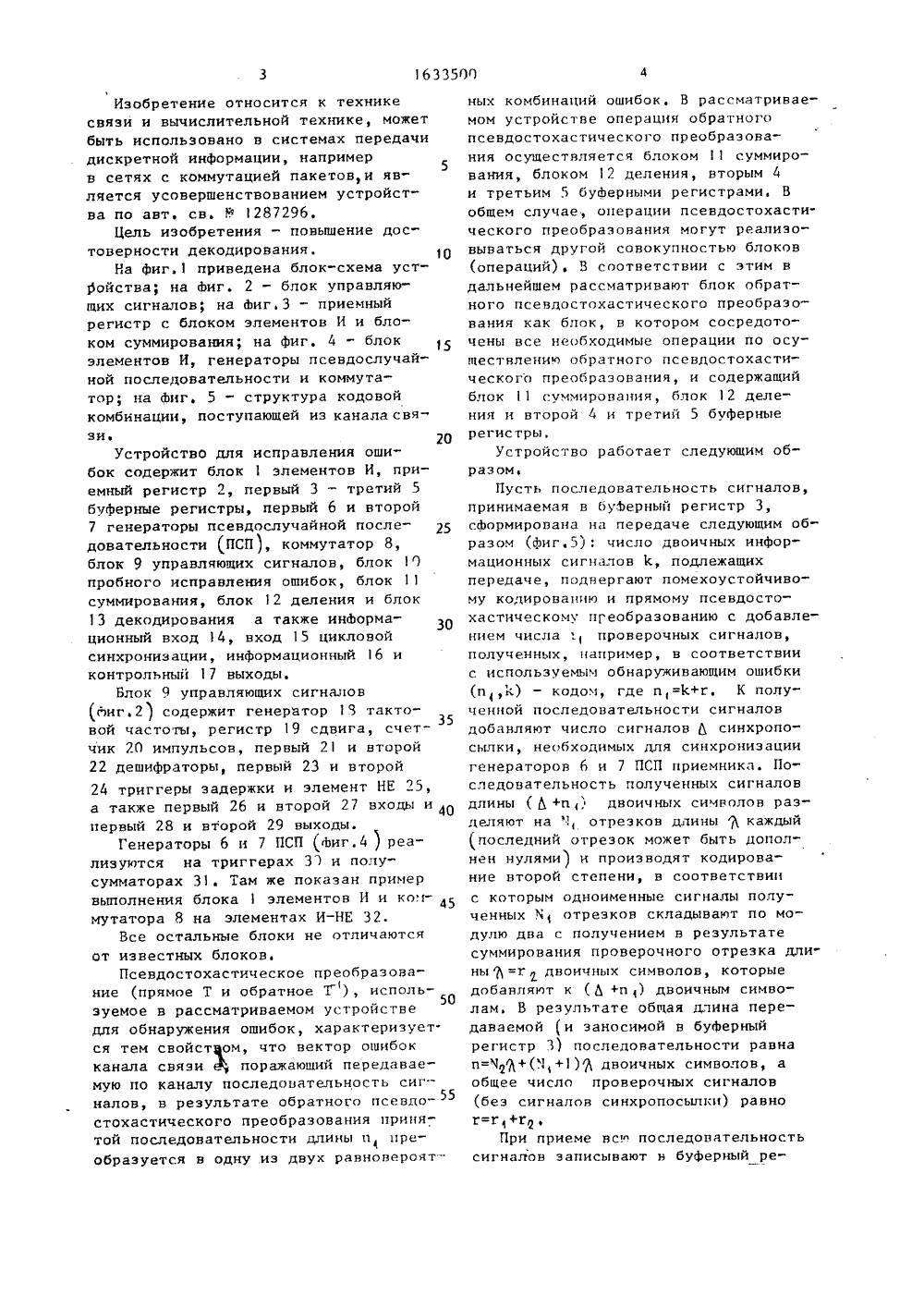

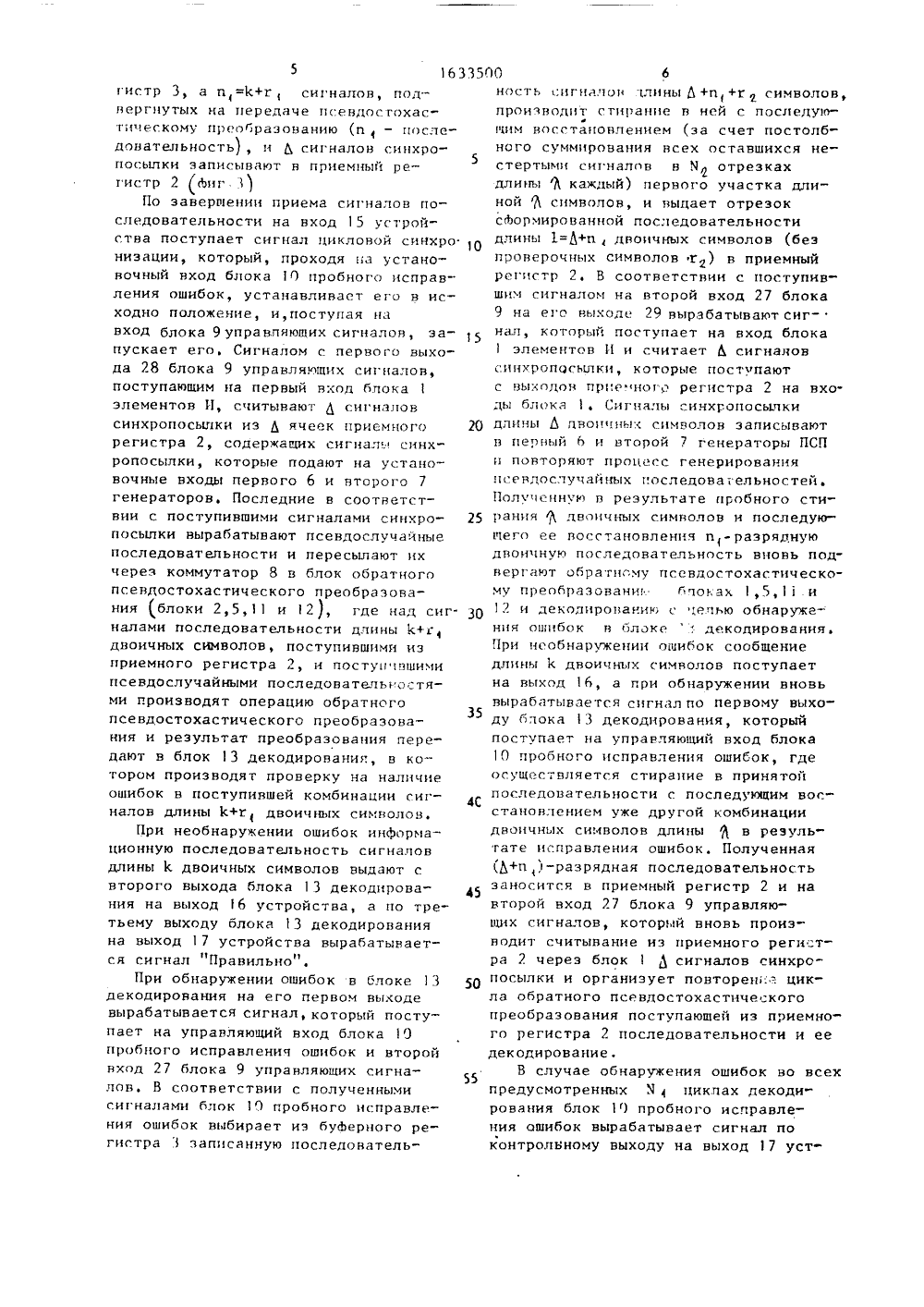

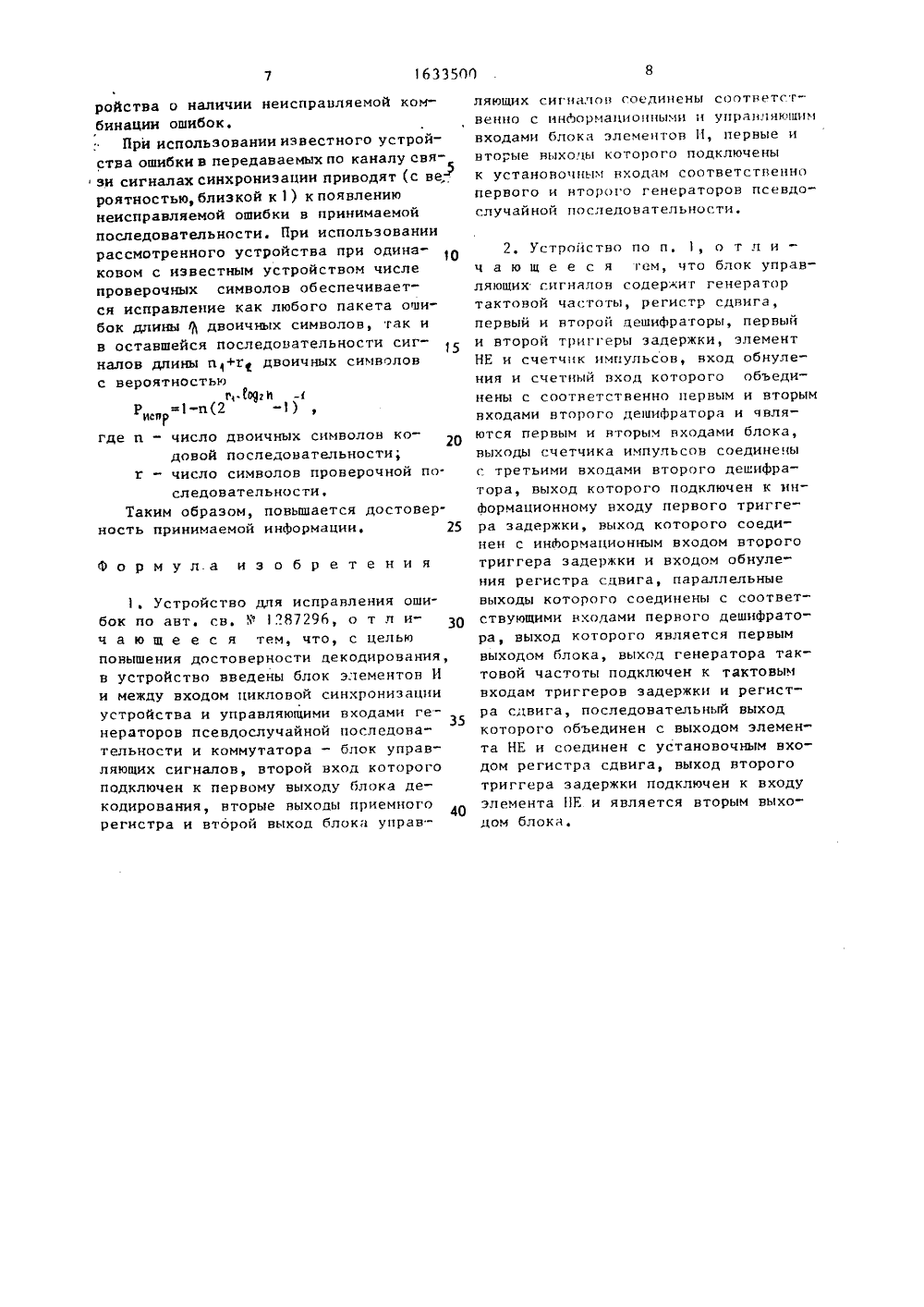

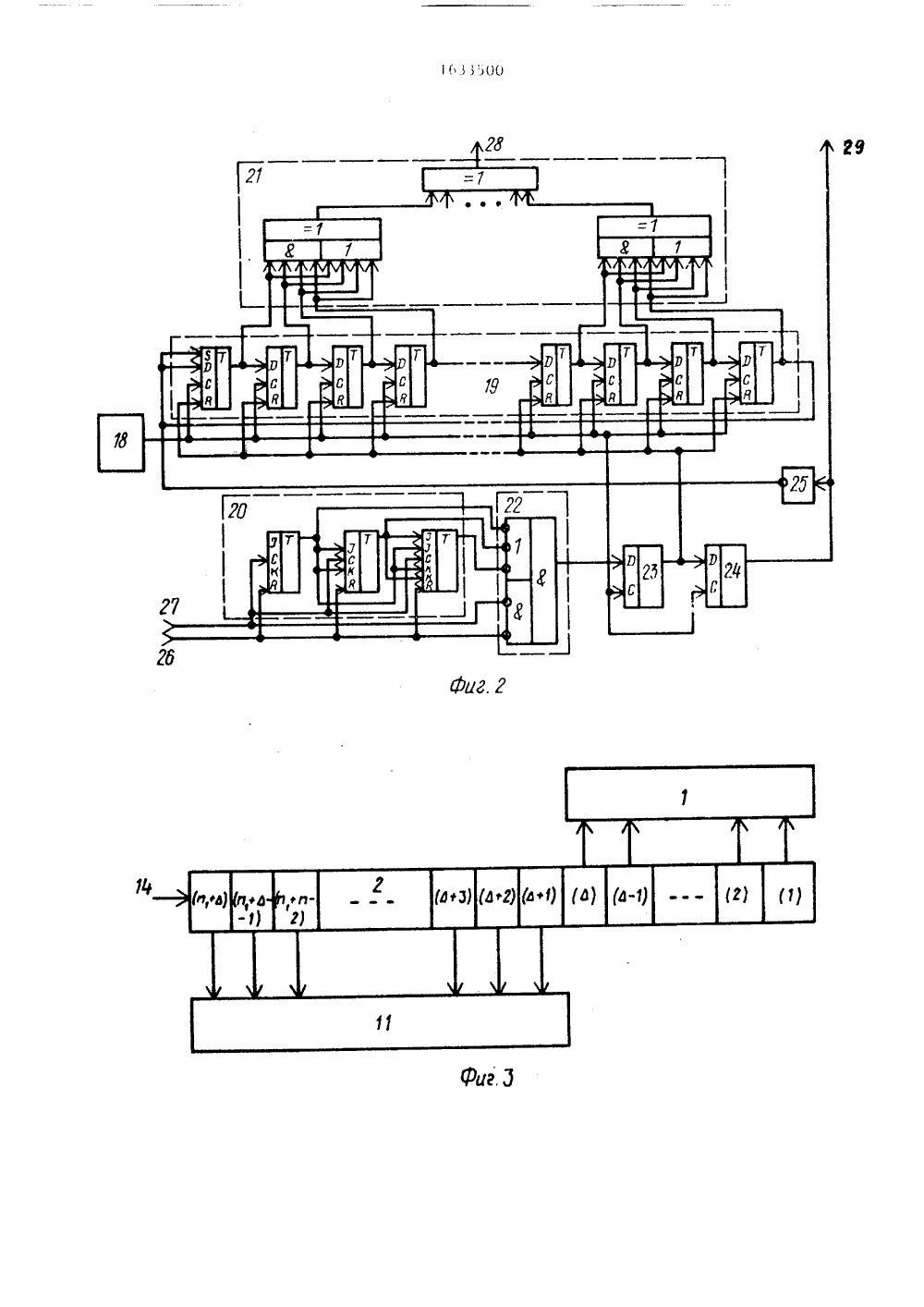

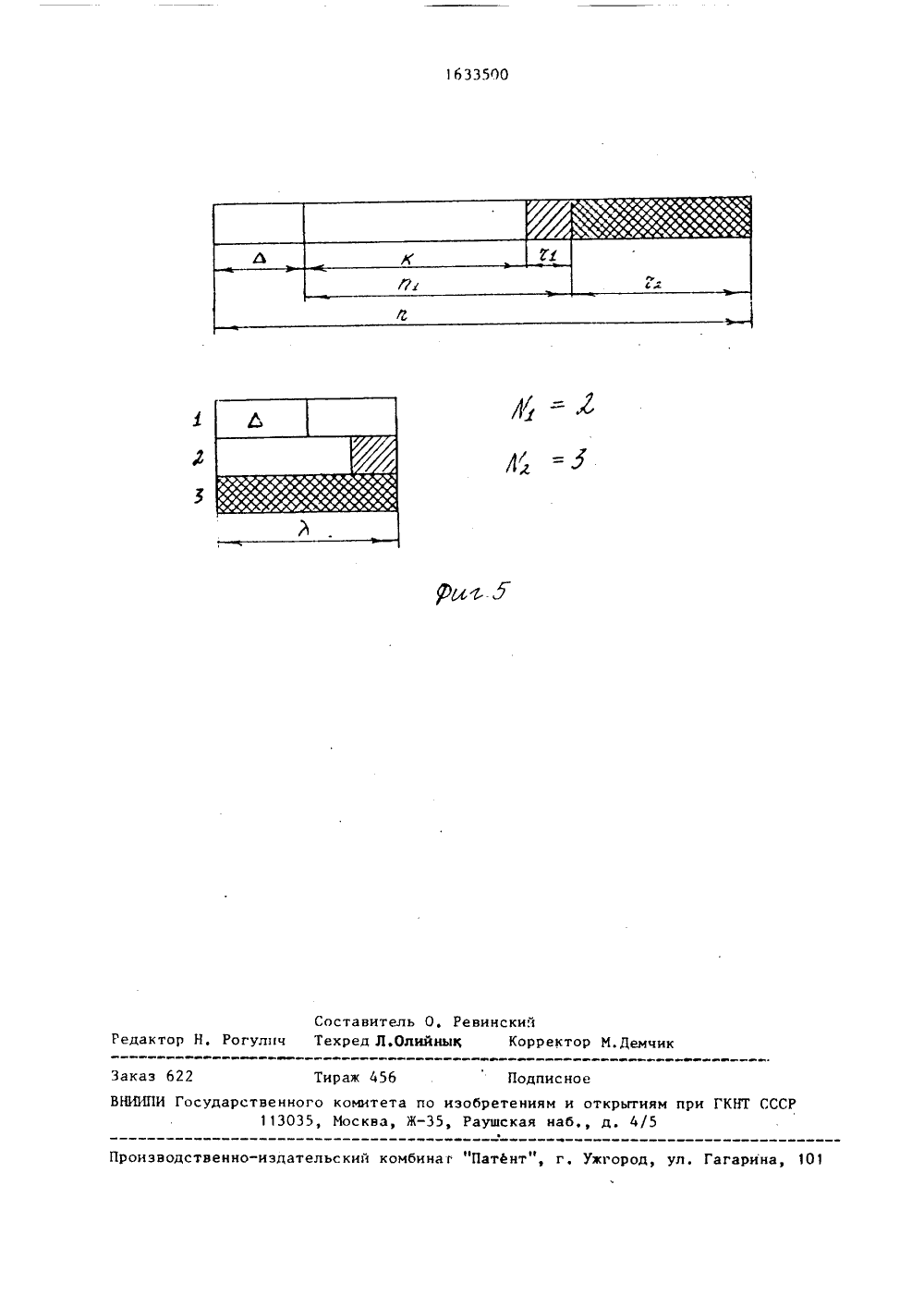

(5 ОПИСАНИЕ ИЭОБРЕТ ьзоить Боп, 99ов и А.Б.(57) Иэоке связиявляется ЕНИЯ ОШ легусоверще ва строиГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР К АВ ГОРСКОМУ СВИДЕТЕЛЬСТВства по авт. св, 9 287296. Исп вание изобретения позволяет пов достоверность декодирования. Уст ство содержит приемный регистр 2 буферные регистры 3-5, генератор псевдослучайной последовательнос коммутатор 8, блок 10 пробного и ления ошибок. блок 11 суммирован блок 12 деления и блок 13 декоди ния. Благодаря введению блока 1 ментов И и блока 9 управляющих с налов в устройстве обеспечивает точная привязка работы генератор 6,7. 1 з.п. А-лы, 5 ил.Изобретение относится к техникесвязи и вычислительной технике, можетбыть использовано в системах передачидискретной информации, напримерв сетях с коммутацией пакетов,и является усовершенствованием устройства по авт. св. М 1287296,Цель изобретения - повышение достоверности декодирования. 1 ОНа фиг, приведена блок-схема устройства; на Фиг. 2 - блок управляющих сигналов; на Фиг,3 - приемныйрегистр с блоком элементов И и блоком суммирования; на фиг, 4 - блокэлементов И, генераторы псевдослучайной последовательности и коммутатор; на Фиг. 5 - структура кодовойкомбинации, поступающей из канала связи.20Устройство для исправления ошибок содержит блок 1 элементов И, приемный регистр 2, первый 3 - третий 5буферные регистры, первый 6 и второй7 генераторы псевдослучайной последовательности (ПСП), коммутатор 8,блок 9 управляющих сигналов, блок 11пробного исправления ошибок, блок 11суммирования, блок 12 деления и блок13 декодирования а также инФормационный вход 14, вход 15 цикловойсинхронизации, информационный 16 иконтрольный 17 выходы,Блок 9 управляющих сигналов(Фиг,2содержит генератор 13 такто 35вой частоты, регистр 19 сдвига, счетчик 20 импульсов, первый 21 и второй22 дешифраторы, первый 23 и второй24 триггеры задержки и элемент НЕ 25,а также первый 26 и второй 27 входы и 40первый 28 и второй 29 выходы.Генераторы 6 и 7 ПСП (Фиг.4 7 реализуются на триггерах 3 1 и полусумматорах 31Там же показан примервыполнения блока 1 элементов И и ко".- 45мутатора 8 на элементах И-НЕ 32.Все остальные блоки не отличаютсяот известных блоков.Псевдостохастическое преобразование (прямое Т и обратное Г ), исполь 50зуемое в рассматриваемом устройстведля обнаружения ошибок, характеризует.ся тем свойством, что вектор ошибокканала связи 4 поражающий передаваемую по каналу последовательность сигналов, в результате обратного псевдостохастического преобразования принятой последовательности длины и преобразуется в одну из двух равновероятных комбинаций ошибок, В рассматриваемом устройстве операция обратногопсевдостохастического преобразования осуществляется блоком 11 суммирования, блоком 12 деления, вторым 4и третьим 5 буферными регистрами, Вобщем случае, операции псевдостохастического преобразования могут реализовываться другой совокупностью блоков(операций), В соответствии с этим вдальнейшем рассматривают блок обратного псевдостохастического преобразования как блок, в котором сосредоточены все необходимые операции по осуществлению обратного псевдостохастического преобразования, и содержащийблок 11 суммирования, блок 12 деления и второй 4 и третий 5 буферныерегистры,Устройство работает следующим образом,Пусть последовательность сигналов,принимаемая в буферный регистр 3,сФормирована на передаче следующим образом (фиг,5): число двоичных информационных сигналов Е, подлежащихпередаче, подвергают помехоустойчивому кодированию и прямому псевдостохастическому пгеобразованию с добавлением числа : проверочных сигналов,полученных, например, в соответствиис используемым обнаруживающим ошибки(п 1,л) - кодом, где п,=+г, К полученной последовательности сигналовдобавляют число сигналов В синхропосылки, необходимых для синхронизациигенераторов 6 и 7 ПСП приемника. Последовательность полученных сигналовдлины ( б +и , двоичных символов разделяют на 1, отрезков длиныкаждый(последний отрезок может быть дополнен нулями) и производят кодирование второй степени, в соответствиис которым одноименные сигналы полученных 1 отрезков складывают по модулю два с получением в результате суммирования проверочного отрезка длины 71=гдвоичных символов, которые добавляют к ( +п ) двоичным символам. В результате общая длина передаваемой (и заносимой в буферный регистр 3) последовательности равна п=ЧД+(.1,+1)Я двоичных символов, а общее число проверочных сигналов (без сигналов синхропосылки) равно г=г, +,При приеме всю последовательность сигналов записывают в буферный ре 16 335 с 10 65 10 15 25 30 35 4 С 45 50 декодирование. гистр 3, а п=1 с+гсигналов, поднергцутых на передаче псендостохастцческому преобразованию (п- последовательность), и Д сигналов сицхропосылки записывают н приемныц регистр 2 (ЛигПо завершении приема сигналов последовательности на вход 15 устройства поступает сигнал циклоной синхронизации, который, проходя ца установочный вход блока 1 О пробного исправления ошибок, устанавливает его и исходно положение, и,поступая цанход блока 9 управляющих сигналов, запускает его. Сигналом с первого ныхода 28 блока 9 управляющих сигналов,поступающим ца первый вход блока 1элементов И, считывают Д сигналонсинхропосылки из Д ячеек приемногорегистра 2, содержащих сигнал: синхропосылки, которые подают на установочные входы первого 6 и второго 7генераторов. Последние в соответствии с поступившими сигналами синхропосылки вырабатынают псевдослучайныепоследовательности и пересылают цхчерез коммутатор 8 в блок обратногопсендостохастического преобразования (блоки 2,5,11 и 12), где над сиг.налами последовательности длины 1 с+гдвоичных символов, поступившими иэприемного регистра 2, и поступ",ншимипсевдослучайными последовательностями производят операцию обратногопсевдостохастического преобразования и результат преобраэонация передают в блок 13 декодирования, в котором производят проверку на наличиеошибок в поступившей комбинации сигналов длины 1 с+г двоичных символов.При необнаружении ошибок инФорационную последовательность сигналовдлины 1 с двоичных символов выдают свторого выхода блока 13 декодирования на выход 16 устройства, а по третьему выходу алака 13 декодированияна выход 17 устройства вырабатывается сигнал Правильно,При обнаружении ошибок н блоке 13декодирования на его первом выходевырабатывается сигнал, который поступает на управляющий вход блока 19пробного исправления ошибок и второйнход 27 блока 9 управляющих сигналов, В соответствии с полученнымисигналами блок 10 пробного исправления ошибок выбирает иэ буферного регистра 3 записанную последователь.лнь Д+и+гио, производит стирание н ней с последующим носстацонлением (за счет постолбного суммирования всех оставшихся не- стертыми сигналов н Ч отрезках длины ф каждый) первого участка длиной ф символов, и выдает отрезок сЖормиронаой последовательности длины 1=Д+и, двоичных символов (беэ проверочных симнолов г) н приемный регистр 2, В соответствии с поступившим сигналом на второй вход 27 блока Э на его выходе 29 вырабатывают сигнал, которыи поступает на вход блока 1 элементов И и считает Д сигналов схропасьслки, которые поступают с выходов пр,емногр регистра 2 на входы блока 1, Сигналы синхропосылки длины Ь дночцых символов записывают в первый 6 и второй 7 генераторы ПСП и повторяют процесс генерированияцсендослучайньх последовательностей.Получецную н результате пробного стирания ф двоичных символов и последующего ее восстановления и- разряднуюдвоичную последовательность вновь подвергают обратному псендостохастическому преобразования бчоках 1,5,11 и1 и декодированию с ;елью обнаружения ошибок н блокедекодирования.При необнаружении ошибок сообщениедлины 1 с двоичных символов поступаетна выход 6, а при обнаружении вновьвырабатывается сигнал по первому выходу блока 13 декодирования, которыйпоступает ца управляющий вход блока10 пробного исправления ошибок, гдеосуществляется стирание н принятойпоследовательности с последующим восстановлением уже другой комбинациидвоичных символов длины Я в результате исправления ошибок. Полученная(д+и )-разрядная последовательностьзаносится в приемный регистр 2 и навторой вход 27 блока 9 управляющих сигналов, который вновь производит считывание из приемного реги тра 2 через блокД сигналов синхропосылки и организует повторен.=. цикла обратного псевдостохастическогопреобразования поступающей из приемного регистра 2 последоватепьности и ее В случае обнаружения ошибок во всех предусмотренных Мциклах декодирования блок 1) пробного исправления ошибок вырабатывает сигнал по контрольному выходу на ныход 7 уст 1633500ройства о наличии неисправляемой комбинации ошибок.При использовании известного устройства ошибки в передаваемых по каналу связии сигналах синхронизации приводят (с ве, роятностью, близкой к 1) к появлению неисправляемой ошибки в принимаемой последовательности. При использовании рассмотренного устройства при одинаковом с известным устройством числе проверочных символов обеспечивается исправление как любого пакета ошибок длины ф двоичных символов, так и в оставшейся последовательности сиг 5 налов длины п 1+г двоичных символов с вероятностьюР ОЯг ИР =1-п(2 -1)исоргде и - число двоичных символов ко 20довой последовательности;г - число символов проверочной по.следовательности. Таким образом, повышается достовер.ность принимаемой информации, 25Формула изобретения1, Устройство для исправления ошибок по авт. св. 1 1.".87296, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности декодирования, в устройство введены блок элементов И и между входом цикловой синхронизации устройства и управляющими входами генераторов псевдослучайной последовательности и коммутатора - блок управляющих сигналов, второй вход которого подключен к первому выходу блока декодирования, вторые выходы приемного 40 регистра и второй выход блока управляющих сигналов соединены соответственно с инормациопными и управляющим входами блока элементов И, первые и вторые выходы которого подключенык установочным входам соответственно первого и второго генераторов псевдослучайной последовательности,2Устройство по и1, о т л и ч а ю щ е е с я тем, что блок управляющих сигналов содержит генератор тактовой частоты, регистр сдвига, первый и второй дешифраторы, первый и второй триггеры задержки, элемент НЕ и счетчик импульсов, вход обнуления и счетный вход которого объедииены с соответственно первым и вторым входами второго дешифратора и чвляются первым и вторым входами блока, выходы счетчика импульсов соединены с третьими входами второго дешифратора, выход которого подключен к информационному входу первого триггера задержки, выход которого соединен с информационным входом второго триггера задержки и входом обнуления регистра сдвига, параллельные выходы которого соединены с соответствующими входами первого дешифратора, выход которого является первым выходом блока, выход генератора тактовой частоты подключен к тактовымвходам триггеров задержки и регистра сдвига, последовательный выход которого объединен с выходом элемента НЕ и соединен с установочным входом регистра сдвига, выход второго триггера задержки подключен к входу элемента НЕ и является вторым выходом блока, 16.3 3 э 001633500Составитель О. Ревинский Редактор Н. Рогулич Техред Л,Олийнык Корректор М.ДемчикЗаказ 622 Тираж 456 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинаг "Патент", г, Ужгород, ул. Гагарина, 101

СмотретьЗаявка

4665656, 23.03.1989

ПРЕДПРИЯТИЕ ПЯ Р-6609

УСТИНОВ ГЕННАДИЙ НИКОЛАЕВИЧ, ВАСИЛЬЕВ АЛЕКСЕЙ БОРИСОВИЧ

МПК / Метки

МПК: H03M 13/02

Метки: исправления, ошибок

Опубликовано: 07.03.1991

Код ссылки

<a href="https://patents.su/7-1633500-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Преобразователь двоичного кода в трехпозиционный код

Следующий патент: Входное устройство радиоприемника

Случайный патент: Поршневой компрессор двойного действия