Систолический процессор дискретного преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

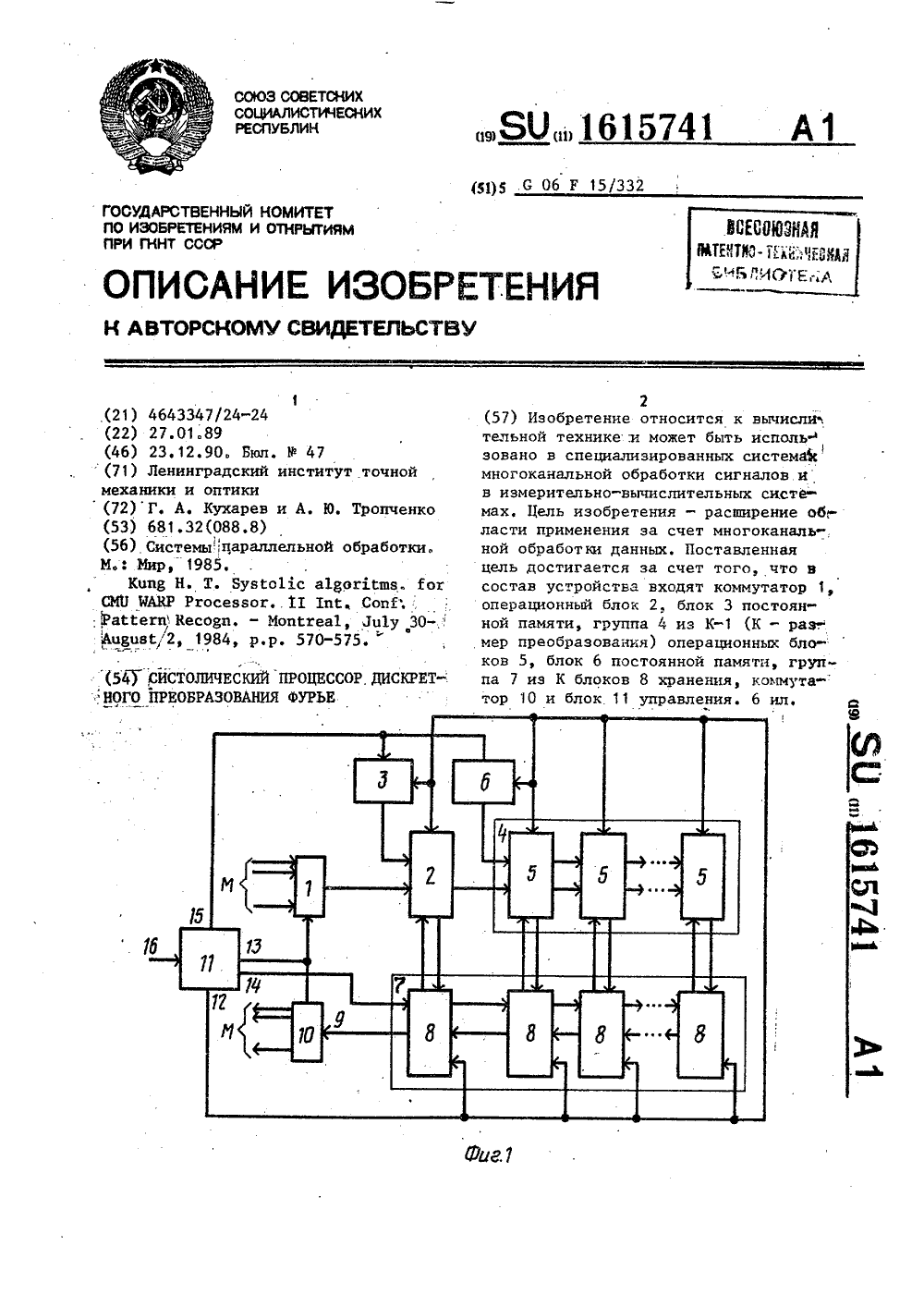

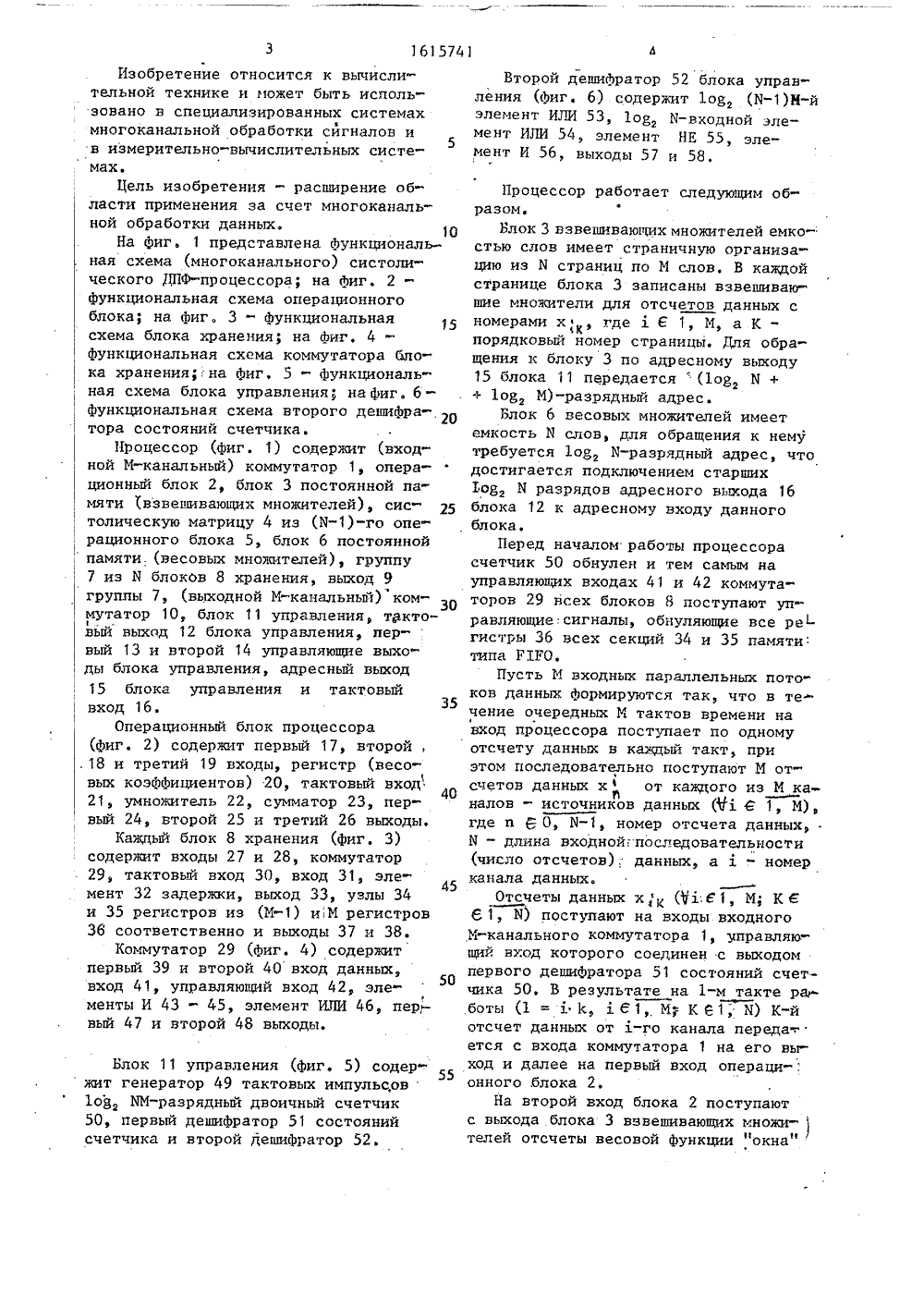

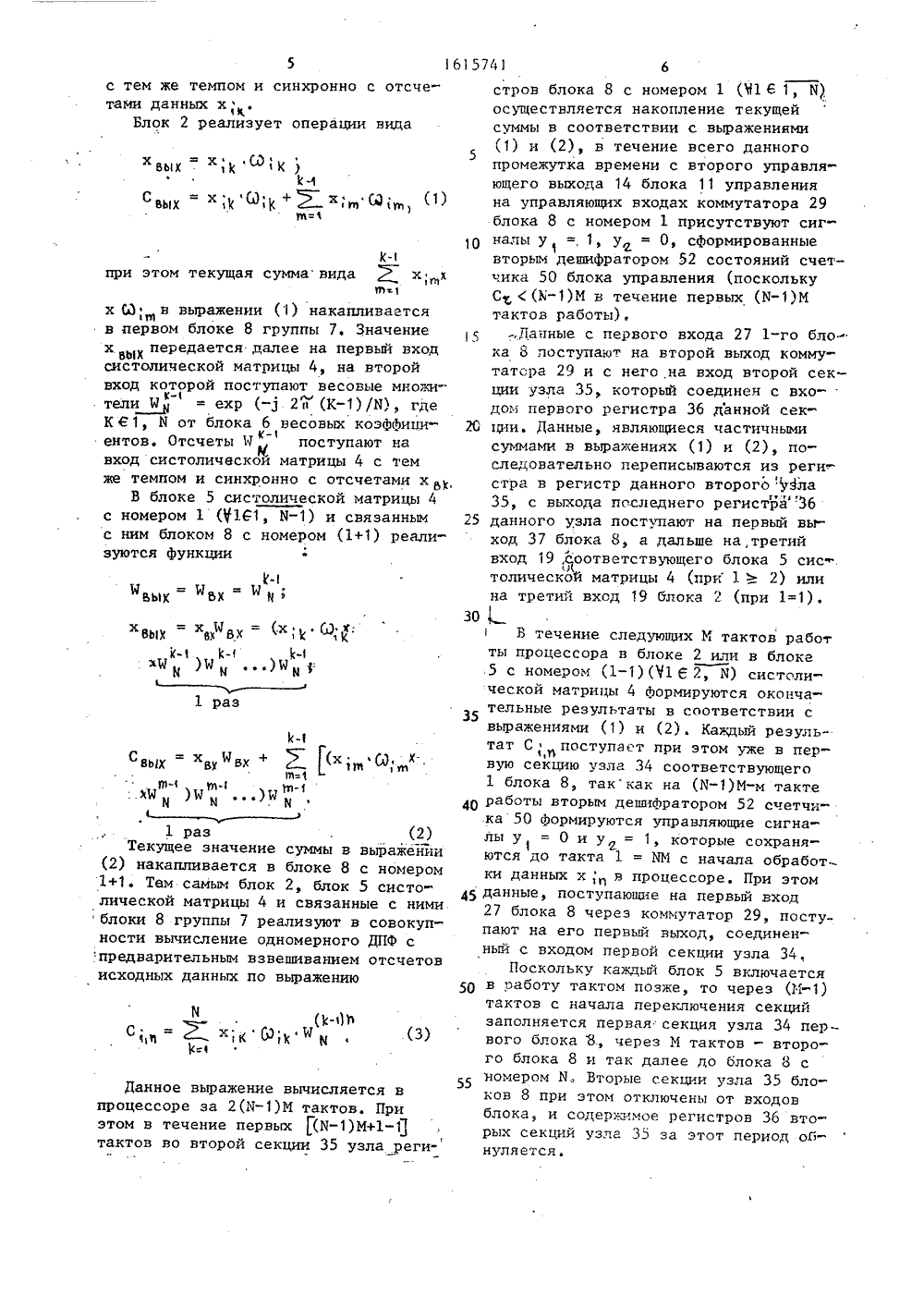

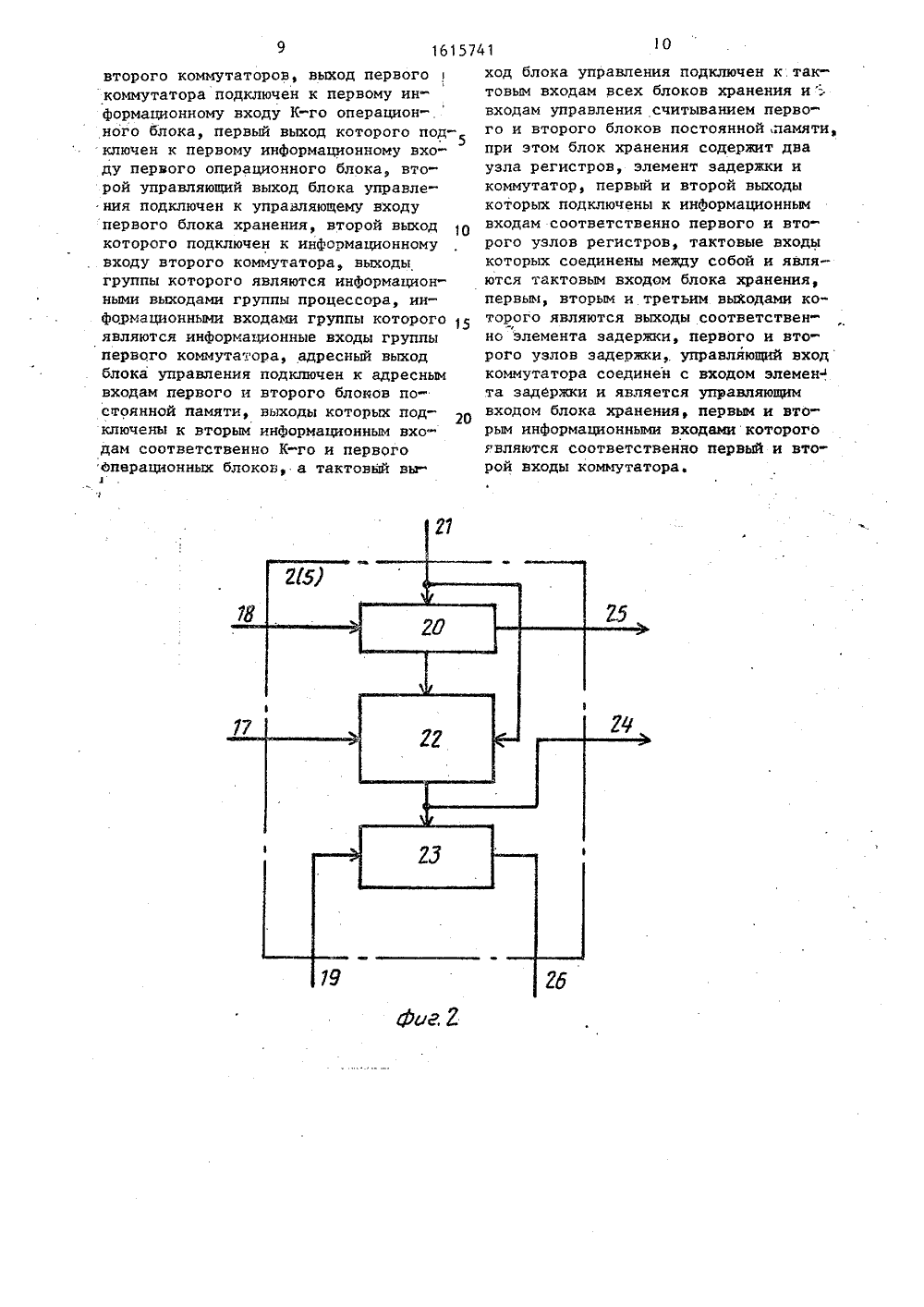

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН М) О 1 А 1 15/33 Щ)5 .С очной о з. Еогй;у 30 ав устроиства ационный блок памяти, группа преобразования 5, блок 6 пост из К блоков 8 10 и блок 11 входят ко 2. блок 3 4 из К) опер аци оянной памяти, хранения, ксв управления. 6 ил ор 1,янразблос ммута пост (К - онных н рко апатор ОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГННТ СССР(71) Ленинградский институт тмеханики и оптики(57) Изобретение относится к вычислительной технике:и может быть исполь-зовано в специализированных системаМмногоканальной обработки сигналов.ив измерительно-вычислительных системах. Цель изобретения - расширение области применения за счет многоканальной обработки данных. Поставленнаяцель достигается за счет того, что в1615741Изобретение относится к вычислительной технике и может быть использовано в специализированных системахмногоканальной обработки сйгналов ив измерительно-вычислительных систе 5мах.Цель изобретения - расширение области применения за счет многоканальной обработки данных,На Фиг. 1 представлена Функциональная схема (многоканального) систолического ДПФ-процессора; на Фиг. 2 - Функциональная схема операционногоблока; на Фиг. 3 - функциональная схема блока хранения; на Фиг. 4- функциональная схема коммутатора блока хранения:на Фиг, 5 - ФункциональЭная схема блока управления; на фиг. 6 функциональная схема второго дешифра тора состояний счетчика.Процессор (Фиг. 1) содержит (входной М-канальный) коммутатор 1, операционный блок 2, блок 3 постоянной памяти (взвешивающих множителей), систолическую матрицу 4 из (И)-го операционного блока 5, блок 6 постояннойпамяти. (весовых множителей), группу7 из И блоков 8 хранения, выход 9группы 7, (выходной М-канальный) ком, мутатор 10, блок 11 управления, такто 1вый выход 12 блока управления, первый 13 и второй 14 управляющие выходы блока управления, адресный выход15 блока управления и тактовыйвход 16.35Операционный блок процессора (Фиг. 2) содержит первый 17, второй, . 18 и третий 19 входы, регистр (весовых коэффициентов) 20, тактовый вход 21, умножитель 22, сумматор 23, пер 40 вый 24, второй 25 и третий 26 выходы,Каждый блок 8 хранения (Фиг. 3) содержит входы 27 и 28, коммутатор 29, тактовый вход 30, вход 31, элемент 32 задержки, выход 33, узлы 3445 и 35 регистров из (М) иМ регистров 36 соответственно и выходы 37 и 38.Коммутатор 29 (фиг. 4) содержит первый 39 и второй 40 вход данных, вход 41, управляющий вход 42, элементы И 43 - 45, элемент ИЛИ 46, пер, - вый 47 и второй 48 выходы.Блок 11 управления (фиг. 5) содержит генератор 49 тактовых импульсов1 од, ИМ-разрядный двоичный счетчик 50, первый дешифратор 51 состояний счетчика и второй дешифратор 52. Второй дешифратор 52 блока управления (Фиг. 6) содержит 1 оя, (И)И-й элемент ИЛИ 53, 1 оя И-входной элемент ИЛИ 54, элемент НЕ 55, эле" мент И 56, выходы 57 и 58,Процессор работает следующим образом.Блок 3 взвешивающих множителей емкостью слов имеет страничную организацию из И страниц по М слов. В каждойстранице блока 3 записаны взвешиваюшие множители для отсчетов данных сномерами х где 3. б 1, М, а К -порядковый йомер страницы. Для обращения к блоку 3 по адресному выходу15 блока 11 передается (1 о 8 И ++ 1 оя М)-разрядный адрес.Блок 6 весовых множителей имеетемкость И слов, для обращения к немутребуется 1 оя, И-разрядный адрес, чтодостигается подключением старших1 о 8, М разрядов адресного выхода 6блока 12 к адресному входу данногоблока.Перед началом работы процессорасчетчик 50 обнулен и тем самым науправляющих входах 41 и 42 коммутаторов 29 всех блоков 8 поступают управляющие.сигналы, обнуляющие все ре 1 гистры 36 всех секций 34 и 35 памяти:типа РХГО.Пусть М входных параллельных пото"ков данных Формируются так, что в течение очередных М тактов времени навход процессора поступает по одномуотсчету данных в каждый такт, приэтом последовательно поступают М отсчетов данных хот каждого из М кабй Мналов - источников данных ф Ю 1, М),где и б О, И, номер отсчета данных, .И - длина входной:последовательности(число отсчетов), данных, а х - номерканала данных.Отсчеты данных х, Яд;61, М; К бб 1, И) поступают на входы входногоМ-канального коммутатора 1, управляющий вход которого соединен с выходомпервого дешифратора 51 состояний счетчика 50. В результате на 1-м такте ра,боты О = 1 1 с, х 6 1 Мр К 1": 1; И) К йотсчет данных от х-го канала переда- .ется с входа коммутатора 1 на его выход и далее на первый вход операци-:онного .блока 2,На второй вход блока 2 поступаютс выхода блока 3 взвешивающих множи- )телей отсчеты весовой функции "окна"1615 с тем же темпом и синхронно с отсчетами данных х;Блок 2 реалйзует операции вида 1 О К-Ф при этом текущая сумма видах хФ 1 х Я в выражении (1) накапливается31в первом блоке 8 группы 7. Значение хпередается далее на первый вход ыхсистолической матрицы 4, на второй вход которой поступают весовые множители ЮМ = ехр (-3 2 Т (К) /М), где К б 1, М от блока 6 весовых коэффипик-ентов. Отсчеты И поступают на вход систолическои матрицы 4 с тем же темпом и синхронно с отсчетами хВ блоке 5 систолической матрицы 4 с номером 1 (161, М) и связанным 25 с ним блоком 8 с номером (1+1) реализуются функцииВ ьыК = 1 ьн = 1 И30 х Ы- (.ххЯ. К-ю К)н ")"иф ВЫХк Щ 1 раз К Сых+ с. 1 рЦВ=1Р- В. и(2)Текущее значение суммы в выражейии (2) накапливается в блоке 8 с номером 1+1. Тем самым блок 2 блок 5 систоУ45 лической матрицы 4 и связанные с ними блоки 8 группы 7 реализуют в совокупности вычисление одномерного ДПФ с предварительным взвешиванием отсчетов исходных данных по выражению(3) Данное выражение вычисляется в55 процессоре за 2(М)И тактов. При этом в течение первых 1(М)М+1-11 тактов во второй секции 35 узла реги 43 6стров блока 8 с номером 1 (Н 1 Е 1, М)осуществляется накопление текущейсуммы в соответствии с выражениями(1) и (2), в течение всего данногопромежутка времени с второго управляющего выхода 14 блока 11 управленияна управляющих входах коммутатора 29блока 8 с номером 1 присутствуют сигналы у 1 =, 1, у = О, сформированныевторым дешифраторок 52 состояний счетчика 50 блока управления (посколькуС М)М в течение первых (М)Мтактов работы),,Данные с первого входа 27 1-го блока 8 поступают на второй выход коммутатора 29 и с него на вход второй секции узла 35, который соединен с входом первого регистра 36 данной секции. Данные, являющиеся частичнымисумками в выражениях (1) и (2), последовательно переписываются из регистра в регистр данного второго Яла35, с выхода последнего регистра"36данного узла поступают на первый выход 3 блока 8, а дальше на,третийвход 19,соответствующего блока 5 сис.1 ятолической матрицы 4 (при 1 ) 2) илина третий вход 19 блока 2 (при 1=1).В течение следующих М тактов работты процессора в блоке 2 нли в блоке5 с номером (1-1)(У 1 Е 2, М) систолической матрицы 4 формируются окончательные результаты в соответствии свыражениями (1) и (2). Каждый результат Споступает при этом уже в первую секцию узла 34 соответствующего1 блока 8, таккак на (М)М-м тактеработы вторым дешифратором 52 счетчи.ка 50 Формируются управляющие сигналы у = 0 и у = 1, которые сохраняются до такта 1 = ММ с начала обработки данных х; в процессоре. При этомданные, поступающие на первый вход27 блока 8 через коммутатор 29, поступают на его первый выход, соединенный с входом первой секции узла 34,Поскольку каждый блок 5 включаетсяв работу тактом позже, то через (И)тактов с начала переключения секцийзаполняется первая секция узла 34 первого блока 8., через М тактов - второго блока 8 и так далее до блока 8 сномером М Вторые секции узла 35 блоков 8 при этом отключены от входовблока, и содержимое регистров Зб вторых секций узла 35 за этот период обнуляется.Начиная с такта М(И) р т.е. на М-м такте после переключения секций узлов 34 и 35, в первом блоке 8 про,изводится вывод результатов С, с вто 1 р ,рого выхода 38 данного блока 8, ко" торый занимает М тактов. Выводимые отсчеты Со с второго выхода 38 перВого блока 8 поступают на выход 9 руппы блоков 8 и с него на выход 1 О ыходного М-канального коммутатора 10далее в выводные каналы данных. При том выходной И-канальный коммутаторравляется также управляющими сигалами от первого дешифратора 51 счет-,5 ика 50, представляющими собой униарный М-разрядный код, В результате а каждом 1-м такте (1 =и + МБр де х 6 1, М, и 1" .1, И) отсчет резульата С; передается в 1-йг выходной анал.На такте (М+1) с начала вывода анных коммутатор 29 первого блока 8руппыподключает к второму входу 8 данного блока 8 второй выход 38 25 торого блока 8. Это осуществляется оступлением на управляющие входы 41 42 коммутатора управляющих сигналов1 р Уо = О, сформированных к этос. у моменту дешифратором 56. При этом аборе управляющих сигналов уй в ууу анные поступаютна второй вход 42 оммутатора 29 и с его первого вы" ода 47 на вход первой секции узла 34. Одновременно с этим данные с первого входа 27 блока 8 (т.еоот тре 35 т его выхода 26 блока 2) поступают на первый вход коммутатора 29 перво,г 1 э блока Зи с его второго выхода 48 на вход второго узла 35.ф)На такте (М+1) с начала вывода днных аналогичные переключения осуществляются в 1-го блока 8, в кото- ром вновь третий выход 26 соответствующего блока 5 подключается комму"45 татором 29 к входу второго узла 35, а вход первого узла 34 в данном блокроказывается подключенным к второму выходу 38 следующего (1+1)-го пасха 8 (Ч 1 Е 2, Е). Таким образом, в течение следующих5 О Ж 1 тактов, считая с начала вывода рйзультатову осуществляется выводвсех сформированных результатов С,., Первые узлы 34 всех блоков 8 при э,ом оказываются последовательно поди 1 юченными один за другим, образуя кйк бы единую память типа Р 1 РО емкостью 11(М) регистров, Одновременно во вторых узлах 35 постепенно накай-ливаются текущие суммы в соответствиис выражениями (1) и (2) для вновь поступающих следующих последовательностей данных х 1 к по всем входным каналам, тем самым в таком многоканаль-,ном процессоре отсутствуют паузы наввод/вывод данных,Формула изобретения. Систолический процессор дискретного преобразования Фурье, содержащий блок управления и К(где К - размер преобразования) операционных блоков, причем первый и второй выходы К-го (К = 1, К - 2) операционного блока подключены соответственно к первому и второму информацлоннымрвходам (К+ +1)го операционного блока, тактовые входы всех операционных блоков подключены к тактовому выходу блока управления, тактовый вход которого подключен к тактовому входу процессора, при этом операционный блок содержит сумматор, умножитель и регистр, выход которого подключен к первому входу уиножителя, выход которого подклю чен к первому информацчонному входу сумматора и является первым выходом операционного блока, вторым выходом. которого является выход регистра, тактовый вход которого соединен с так - товым входом умножителя.и является тактовым входом операционного блока, первым и вторым информационными входами которого являются соотввтственно второй информационный вход умножителя и информационный вход регистра, о т л и ч и ю щ и й с я тему чтой с целью расдирения области применения за счет многокачальной обработки данных, в него введены два блока по-" стоянной памяти, два коммутатора, К-й операционный блок из К блоков хранении, при агом первый выход н первый иыФорманноннвй вход р-го Срт 1, К); , блока хранения подключены соответственно к управляющему входу и второму выходу (р+1)-го блока хранения, третий выход К-го (К:1, К) операционного блока подключен к второму информа- ционному входу К-го блока хранения, третий выход которого подключен к третьему информационному входу К-го операционного блока, первый управляющий выход блока управления подключен к управляющим входам первого и20 второго коммутаторов, выход первогокоммутатора подключен к первому информационному входу К-го операцион-.ного блока, первый выход которого подключен к первому информационному входу первого операционного блока, второй управляющий выход блока управления подключен к управляющему входупервого блока хранения, второй выходкоторого подключен к информационномувходу второго коммутатора, выходыгруппы которого являются информационными выходами группы процессора, информационными входами группы которого 1являются информационные входы группыпервого коммутатора, адресный выходблока управления подключен к адреснымвходам первого и второго блоков постоянной памяти, выходы которых подключены к вторым информационным вхо"дам соответственно К-го и первогооперационных блоков, а тактовый вы 4 ход блока управления подключен к.тактовым входам всех блоков хранения и - входам управления считыванием первого и второго блоков постоянной, памяти, при этом блок хранения содержит два узла регистров, элемент задержки и коммутатор, первый и второй выходы которых подключены к информационным входам соответственно первого и второго узлов регистров, тактовые входы которых соединены между собой и являются тактовым входом блока хранения, первым, вторым и третьим выходами которого являются выходы соответственфно элемента задержки, первого и второго узлов задержки, управляющий вход коммутатора соединен с входом элемен- .та задержки и является управляющим входом блока хранения, первым и вторым информационными входами которого являются соответственно первый и второй входы коммутатора.,Шароши Заказ 398 раж 567 Подпи ВНИИП Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101 Составитель А. Бар-новКозориз Техред Л. Сердюкова Коррек сударственного комитета по изобретени 113035, Москва, Ж-.35, Раушская и открытиям при ГКНТ СССаб., д. 4/5

СмотретьЗаявка

4643347, 27.01.1989

ЛЕНИНГРАДСКИЙ ИНСТИТУТ ТОЧНОЙ МЕХАНИКИ И ОПТИКИ

КУХАРЕВ ГЕОРГИЙ АЛЕКСАНДРОВИЧ, ТРОПЧЕНКО АЛЕКСАНДР ЮВЕНАЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 17/14

Метки: дискретного, преобразования, процессор, систолический, фурье

Опубликовано: 23.12.1990

Код ссылки

<a href="https://patents.su/7-1615741-sistolicheskijj-processor-diskretnogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Систолический процессор дискретного преобразования фурье</a>

Предыдущий патент: Анализатор спектра в ортогональном базисе

Следующий патент: Устройство для быстрого ортогонального преобразования цифровых сигналов по уолшу-адамару

Случайный патент: Способ настройки режущего инструмента