Устройство для вычисления тригонометрических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1332313

Автор: Чуватин

Текст

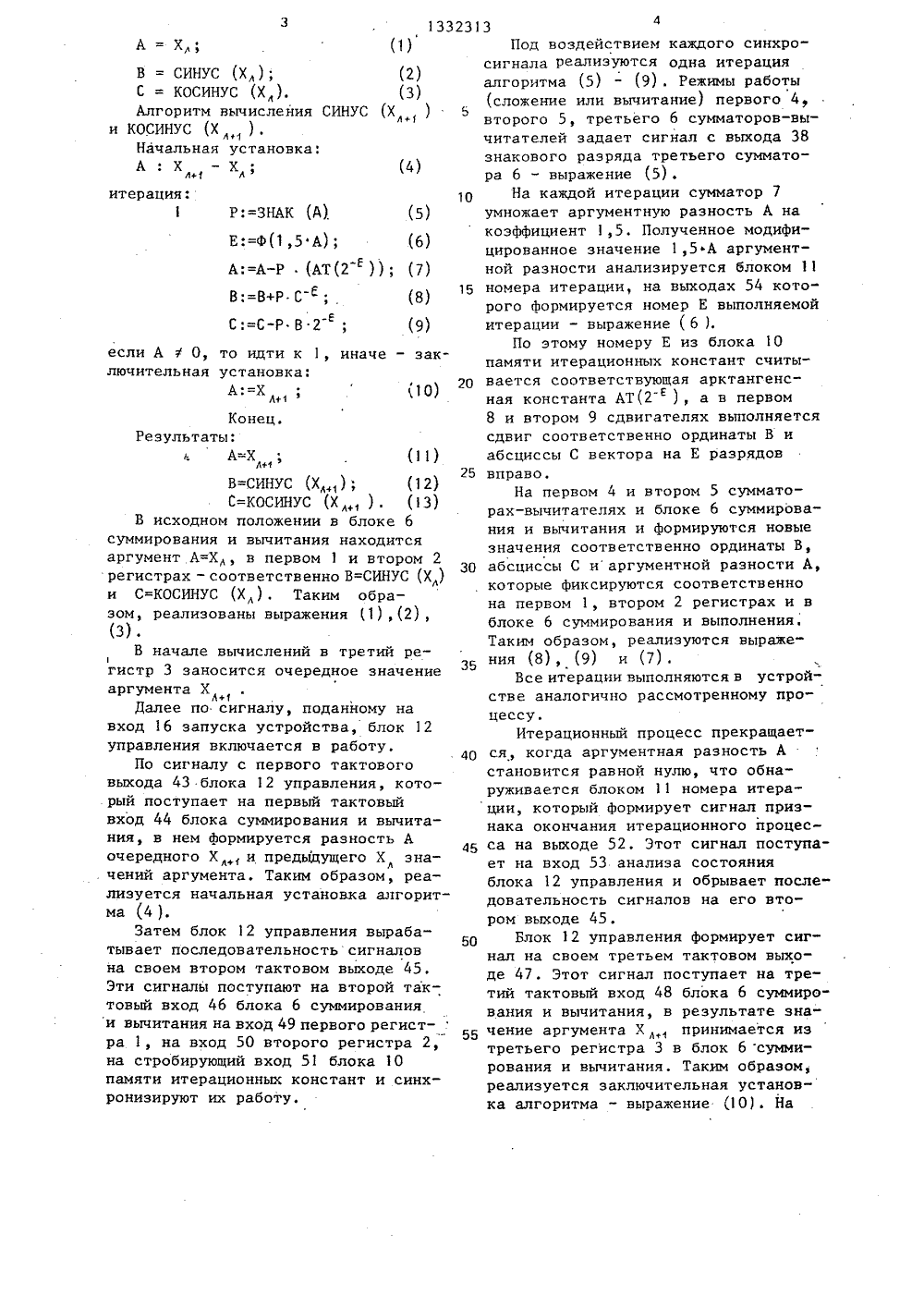

20 5 ИЛИ 71ЗО 40 щие обозначения 45 50 5513Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.Цель изобретения - повышение быстродействия за счет сокращения числа требуемых для вычисления операций.На Фиг, представлена Функциональная схема устройства; на фиг.2 Функциональная схема блока управления; на Фиг.3 - Функциональная схема блока номера итераций; на фиг.4 пример реализации схемы блока суммирования и вычитания.Устройство содержит первый 1, второй 2 и третий 3 регистры, первый 4 и второй 5 сумматоры-вычитатели, блок 6 суммирования и вычитания, сумматор 7, первый 8 и второй 9 сдвига- тели, блок 10 памяти итерационных констант, блок 11 номера итерации, блок 12 управления, вход 13 ординаты, вход 14 абсциссы, вход 15 угла, вход 16 запуска, первые информационные входы 17 - 19 соответственно первого, второго и третьего регистров, выход 20 первого регистра, первый информационный вход 21 первого сумматоравычитателя, выход 22 второго регистра первый информационный вход 23 второго сумматора-вычитателя, входы аргументов 24 и 25 соответственно первого и второго сдвигателей, выход 26 первого сдвигателя, второй информационный вход 27 второго сумматоравычитателя, выход 28 второго сдвигателя, второй информационный вход 29 первого сумматора-вычитателя, выход 30 первого сумматора, второй информационный вход 31 первого регистра, выход 32 второго сумматора-вычитателя второй информационный вход 33 второго регистра, выход 34 третьего регистра, первый информационный вход 35 блока суммирования и вычитания, выход 36 блока памяти итерационных констант, второй информационный, вход 37 блока суммирования и вычитания, выход 38 знакового разряда блока суммирования и вычитания, управляющий вход 39 блока суммирования и вычитания, управляющие входы 40 и 41 соответственно второго и первого сумматоров-вычитателей, вход 42 запуска блока управления, первый тактовый выход 43 блока управления, первый тактовый вход 44 блока суммирования и вычитапия, второй тактовый выход 32313 2 45 блока управления, второй тактовыйвход 46 блока суммирования и вычитания, третий тактовый выход 47 блокауправления, третий тактовый вход 48блока суммирования и вычитания,синхронизирующие входы 49 и 50 соответственно первого и второго регистров,стробирующий вход 51 блока памятиитерационных констант, выход 52 признака нуля разности блока номера итерации, вход 53 анализа состоянияблока управления, выход 54 блоканомера итерации, входы 55 и 56 величины сдвига соответственно первого и второго сдвигателей, адресный вход57 блока памяти итерационных конСтаит, информационный выход 58 блокасуммирования и вычитания, вход 59первого слагаемого сумматора, выход60 сумматора, вход 61 блока номера итерации, вход 62 второго слагаемого сумматора.Блок суммирования и вычитания содержит первый коммутатор 63, первыйсумматор 64, первый регистр 65, второй коммутатор 66, второй сумматор67, второй регистр 68, первый 69 ивторой 70 элементы НЕ, элемент Блок номера итерации содержитгруппу 72 элементов ИСКЛЮЧАТЕЕ ИЛИ,шифратор номера итераций 73,Блок управления содержит генераторЗ 5 74 тактовых импульсов, первый 75,второй 76, третий 77 элементы И,триггер 78.Устройство функционирует следующимобразом.В ходе вычислений приняты следуюэ 1 п (Х) - С 1;НУС (Х); со 5 (Х) КОСИНУС (Х); агсСц(Х) - АТ (Х);э 1 уп (Х) - ЗНАК (Х); А - угол ( аргумент, аргументная Разность); В - ордината вектора (синус ); С - абсцисса вектора ( косинус ); Р ь-1, +1оператор направления поворота вектора; Е - номер выполняемой итерации; Ф(Х) - преобразование формирования номера Е старшей значащей цифры числа Х; АТ(2 ) - угол, на который поворачивается вектор на Е-й ишерации; Х - л-е значение аргумента во входином потоке; Х- (л+1) -е - значение аргумента во входном потоке.Значения переменных до начала вычислении;А=Х итерация: В = СИНУС (Хл); (2) С = КОСИНУС (Х) (3) Алгоритм вычисления СИНУС (Х, ) и КОСИНУС (Х , ).Начальная установка:А: Х - Х; (4) 1 Р:=ЗНАК (А), (5) Е:=Ф(1,5 А); (6) А:=А-Р(АТ(2 ; (7) В:=В+Р.С ; (8) С:=С Р В 2 1 (9) если А Ф О, то идти к 1, иначе - заключительная установка:А:=Х ; . (10)Конец.Результаты:А=Х (1 1)В=СИНУС (Х); (12)С=КОСИНУС (Х+, ) . (13)В исходном положении в блоке 6 суммирования и вычитания находится аргумент А=Хл, в первом 1 и втором 2 регистрах - соответственно В=СИНУС (Х) и С=КОСИНУС (Хл). Таким образом, реализованы выражения (1),(2), (3) .В начале вычислений в третий регистр 3 заносится очередное значение аргумента Хл+Далее по сигналу, поданному на вход 16 запуска устройства, блок 12 управления включается в работу.По сигналу с первого тактового выхода 43 блока 12 управления, который поступает на первый тактовый вход 44 блока суммирования и вычитания, в нем формируется разность А очередного Х и предыдущего Х значений аргумента. Таким образом, реализуется начальная установка алгоритма (4).Затем блок 12 управления вырабатывает последовательность сигналов на своем втором тактовом выходе 45, Эти сигналы поступают на второй тактовый вход 46 блока б суммирования и вычитания на вход 49 первого регист-ра 1, на вход 50 второго регистра 2, на стробирующий вход 51 блока 10 памяти итерационных констант и синхронизируют их работу. 5 10 15 20 25 30 35 40 45 50 55 Под воздействием каждого синхросигнала Реализуются одна итерация алгоритма (5) - (9) . Режимы работы (сложение или вычитание) первого 4 второго 5, третьего 6 сумматоров-вычитателей задает сигнал с выхода 38 знакового разряда третьего сумматора 6 - выражение (5).На каждой итерации сумматор 7 умножает аргументную разность А на коэффициент 1,5. Полученное модифицированное значение 1,5 А аргументной разности анализируется блоком 11 номера итерации, на выходах 54 которого формируется номер Е выполняемой итерации - выражение ( 6 ).По этому номеру Е из блока 10 памяти итерационных констант считывается соответствующая арктангенсная константа АТ(2 ), а в первом 8 и втором 9 сдвигателях выполняется сдвиг соответственно ординаты В и абсциссы С вектора на Е разрядов вправо.На первом 4 и втором 5 сумматорах-вычитателях и блоке 6 суммирования и вычитания и формируются новые значения соответственно ординаты В, абсциссы С и аргументной разности А, которые фиксируются соответственно на первом 1, втором 2 регистрах и в блоке 6 суммирования и выполненияТаким образом, реализуются выражения (8), (9) и (7) .Все итерации выполняются в устройстве аналогично рассмотренному про" цессу.Итерационный процесс прекращается, когда аргументная разность А становится равной нулю, что обнаруживается блоком 11 номера итерации, который формирует сигнал признака окончания итерационного процесса на выходе 52, Этот сигнал поступает на вход 53 анализа состояния блока 12 управления и обрывает последовательность сигналов на его втором выходе 45.Блок 12 управления формирует сигнал на своем третьем тактовом выходе 47. Этот сигнал поступает на третий тактовый вход 48 блока 6 суммиро" вания и вычитания, в результате значение аргумента Х , принимается иэ третьего регистра 3 в блок 6 суммирования и вычитания. Таким образом, реализуется заключительная установка алгоритма - выражение (10). На32313 15 20 25 30 35 45 50 5 13этом блок 12 управления заканчиваетработу.В третьем сумматоре б находитсяаргумент А = Х, в первом 1 ивтором 2 регистрах соответственноВ фф СИНУС (Х ) и С = КОСИНУС (Х )Это - результаты вычислений, Такимобразом, реализуются выражения (11),(12) и (13) .Блок управления работает следую-щим образом.При подаче сигнала "Пуск" на первый вход 42 блока управления триггер78 устанавливается в состояние"Лог.1" и разрешает прохождение им-,.пульсон с выхода генератора тактовых импульсов через элемент И 75.Одновременно сигнал "Пуск" поступает на первый тактовый выход 43 блока управления, в результате чего выполняется выражение (4),Если на входе 53 анализа состояния блока управления имеется сигналсостояния Лог.О, что является признаком неравенства нулю аргументнойразности(АФ О), то третий элементИ 77 заблокирован, а импульсы с выхода первого элемента И 75 через второй элемент И 76 поступают на второйтактовый выход 45 блока управления,Под воздействием этих импульсов выполняются итерации в соответствии свыражениями (5) (9),При выполнении условия равенстванулю аргументной разности (А=О) навтором входе 53 блока управлениясостояние "Лог.О" изменяется на состояние "Лаг.1", в результате чегоблокируется второй элемент И 76, аочередной импульс с выхода первогоэлемента И 75 через третий элементИ 77 поступает на третий тактовыйвыход 47 блока управления, в результате чего выполняется выражение(10 ). Одновременно этот же импульсустанавливает триггер 78 в состояние"Лог.О", в результате блокируетсяпрохождение синхроимпульсов черезпервый элемент И 75 - устройство закончило работу.Блок номера итерации функционирует следующим образом,Группа 72 элементов ИСКЛЮЧАЮЩЕЕИЗПт предназначена для преобразованиямодифицированного значения аргументной разности 1,5 А, которое можетбыть как положительным, так и отрицательным, в такое положительное число О, у которого в разряде, соответствующем старшей значащей цифре модифицированного значения аргументной разности 1,5 А, стоит единица, а вразрядах, расположенных слева от нее,стоят нули.К выходам элементов ИСКЛЮЧАЮЩЕЕИЛИ группы 72 подключен шифратор номера итерации, который при отсутствии единицы в старших разрядаханализируемого числа формирует кодномера старшей значащей единицы модифицированного значения аргументной разности, т.е. Е = Ф(1,5 А). Формула изобретения 1. Устройство для вычисления тригонометрических функций, содержащее три регистра, два сумматора-вычитателя и блок суммирования и вычитания, два сдвигателя, блок памяти итерационных констант, блок номера итерации, содержащий шифратор номера итерации и блок управления, содержащий генератор тактовых импульсов, причем входы ординаты, абсциссы и угла устройства соединены с первыми информационными входами первого, второго и третьего регистров, выходы первого и второго регистров соединены с первыми информационными входами соответственно первого и второго сумматоров-вычитателей, вторые информационные входы которых соединены с выходами соответственно второго и первого сдвигателей, информационные входы которых соединены с выходами соответственно второго и первого регистров, вторые информационные входыкоторых соединены с выходами соответственно второго и первого сумматороввычитателей, управляющие входы перваго, второго и третьего сумматороввычитателей соединены с выходом знакового разряда блока суммирования ивычитания, первый и второй информационные входы которого соединены с выходами соответственна третьего регистра и блока памяти итерационных констант, информационные входы треть его регистра соединены с входом аргумента устройства, адресные входы бло 55- ка памяти объединены с входами величи, ны сдвига первого и второго сдвигате лей и соединены с выходом блока номера итерации, выход признака нуля разности блока номера итерации соединен13323 10 15 20 30 35 40 45 50 с входом режима анализа состоянияблока управления, вход запуска которого соединен с одноименным входомустройства, первый тактовый выходблока управления соединен с одноименным входом блока суммирования и вычитания, второй тактовый выход блока управления соединен с одноименным входом блока суммирования и вычитания, с синхронизирующими входамипервого и второго регистров и стробирующим входом блока памятиитерационных констант, о т л ич а ю щ е е с я тем, что, сцелью повышения быстродействия засчет сокращения числа итераций вычисления, в него дополнительно введенсумматор, а блок управления дополнительно содержит триггер и три элемента И, а блок номера итерации -группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,причем выход блока суммирования ивычитания соединен с входом первогослагаемого сумматора и со сдвигом наодин разряд в сторону младших разрядов с входом второго слагаемого сумматора, выход сумматора соединен свходом .блока номера итерации входзапуска блока управления соединенс входом установки триггера, прямойвыход которого и выход генераторатактовых импульсов соединены соответственно с первым и вторым входамипервого элемента И,выход которогосоединен с первыми входами второго итретьего элементов И, второй инверсный вход второго элемента И и второйвход третьего элемента И соединеныс входом режима анализа состоянияблока управления, выход третьегоэлемента И соединен с входом сбросатриггера и с третьим тактовым выходом блока управления, первый и второй тактовые выходы которого соединены соответственно с входом запускаи выходом второго элемента И блокауправления, причем 1-й вход блоканомера итерации (1=2п+1) соединен с первым входом )"го элементаИСКЛЮЧАЮЩЕЕ ИЛИ группы и вторым входом Ц -1) -го элемента ИСКЛЮЧАЮЩЕЕИЛИ группы, первый вход первого и 138второй вход (и+1) -го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и (и+1)-м входами блока но- мера итерации, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с входами шифратора номера итерации, выход которого является выходом блока номера итерации. 2,устройство по п.1, о т л и ч а ющ е е с я тем, что блок суммирова" . ния и вычитания содержит два регистра, два сумматора, два коммутатора, два элемента НЕ и элемент ИЛИ, причем первый информационный вход блока соединен с первым информационным и с инверсным вторым информационным входами первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с выходом первого регистра, информационные входы которого соединены с выходами второго коммутатора, пер- . вый информационный вход которого соединен с выходом первого сумматора, второй информационный вход второго коммутатора соединен с выходом второго сумматора, вход первого слагаемого которого соединен с инверсными выходами второго регистра, вход второго слагаемого второго сумматора соединен с вторым информационным входом блока и с информационным входом второго регистра, управляющий вход блока соединен с первым управляющим входом первого коммутатора и черезэлемент НЕ - с вторым управляющим входом первого коммутатора, первый тактовый вход блока соединен с первым входом элемента ИЛИ, с первым управляющим входом второго коммутатора и через элемент НЕ - с вторым управляющим входом второго коммутатора, второй и третий тактовые входы блока соединены соответственно с вторым входом элемента ИЛИ и синхронизирующим входом второго регистра соответственно, информационный выход и выход знакового разряда пер. вого регистра соединены с одноименны" ми выходами блока.332313 Составитель С.КуликоПапп Техред И,Попович едакт орректор Л.Па 3833/44 Тираж 672ВНИИПИ Государственного комитетапо делам изобретений и открытий 113035, Москва, Ж, Раушская наб Зак одписно д. 4/5 оизводственно-полиграфическое предприятие, г.ужгород, ул. Проектная,

СмотретьЗаявка

4018837, 22.01.1986

КИРОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ЧУВАТИН АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/548

Метки: вычисления, тригонометрических, функций

Опубликовано: 23.08.1987

Код ссылки

<a href="https://patents.su/7-1332313-ustrojjstvo-dlya-vychisleniya-trigonometricheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления тригонометрических функций</a>

Предыдущий патент: Устройство для деления

Следующий патент: Устройство преобразования координат для геометрической коррекции изображений

Случайный патент: Светосильный объектив