Мультипроцессорное вычислительное устройство с параллельной обработкой информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

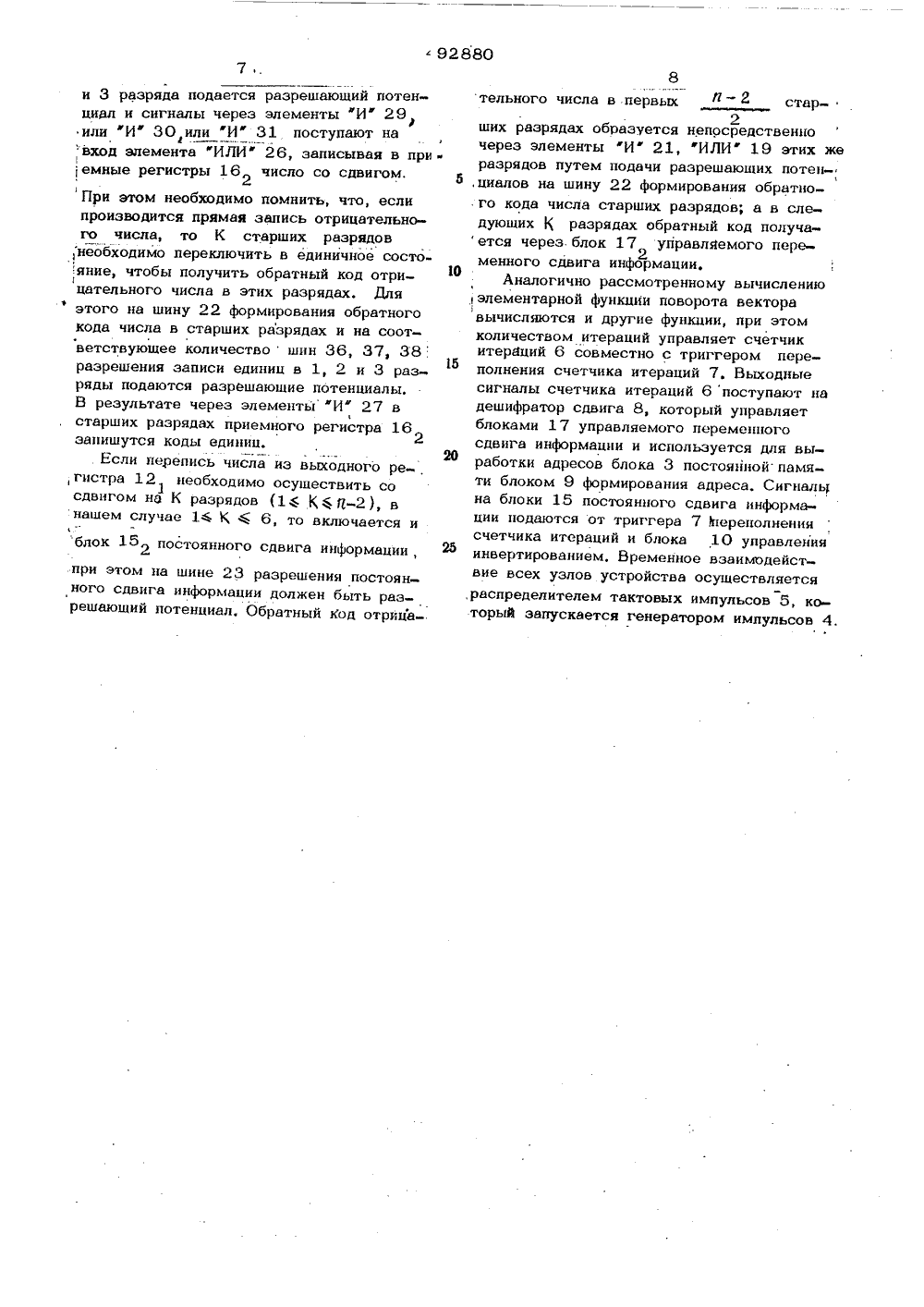

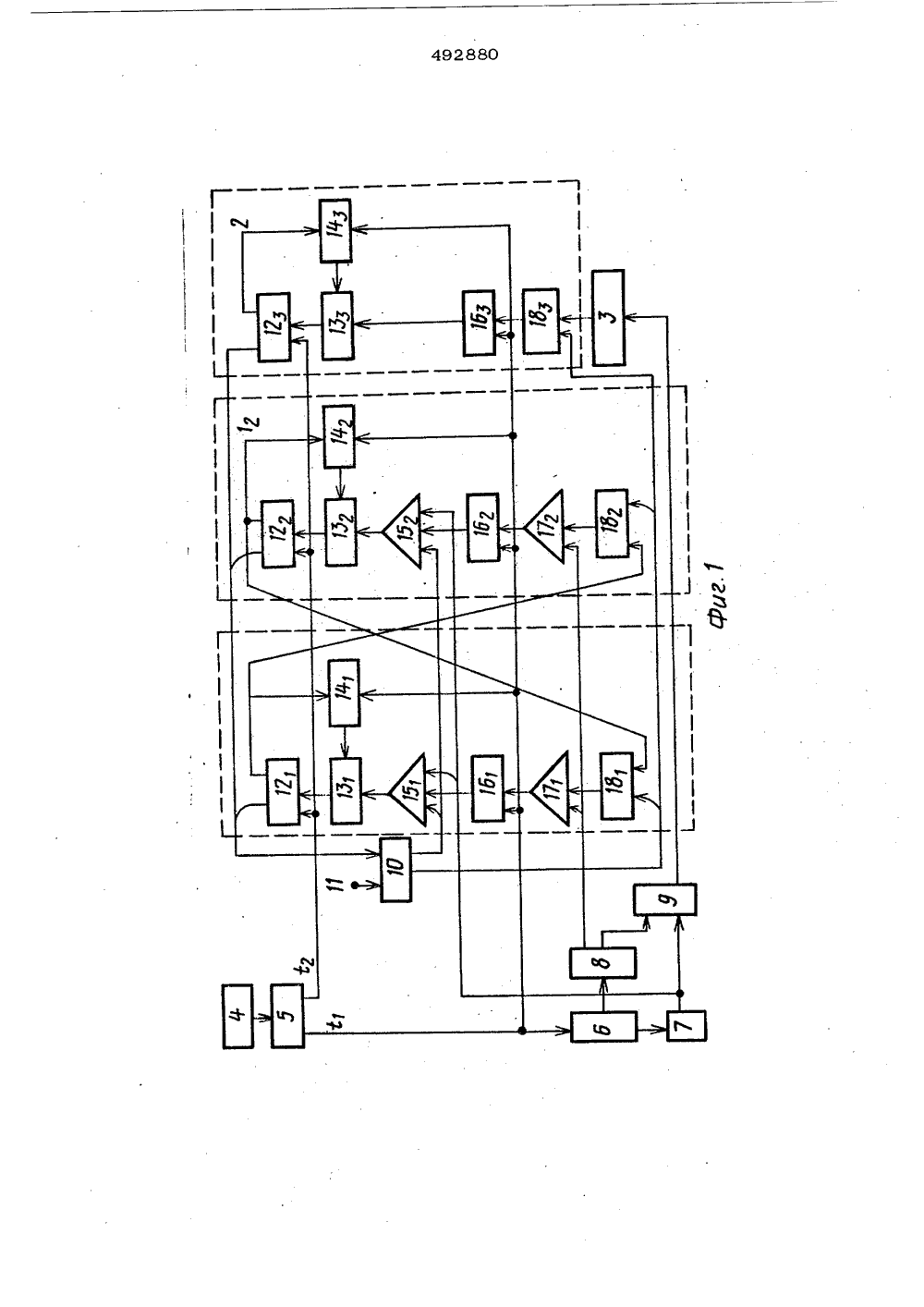

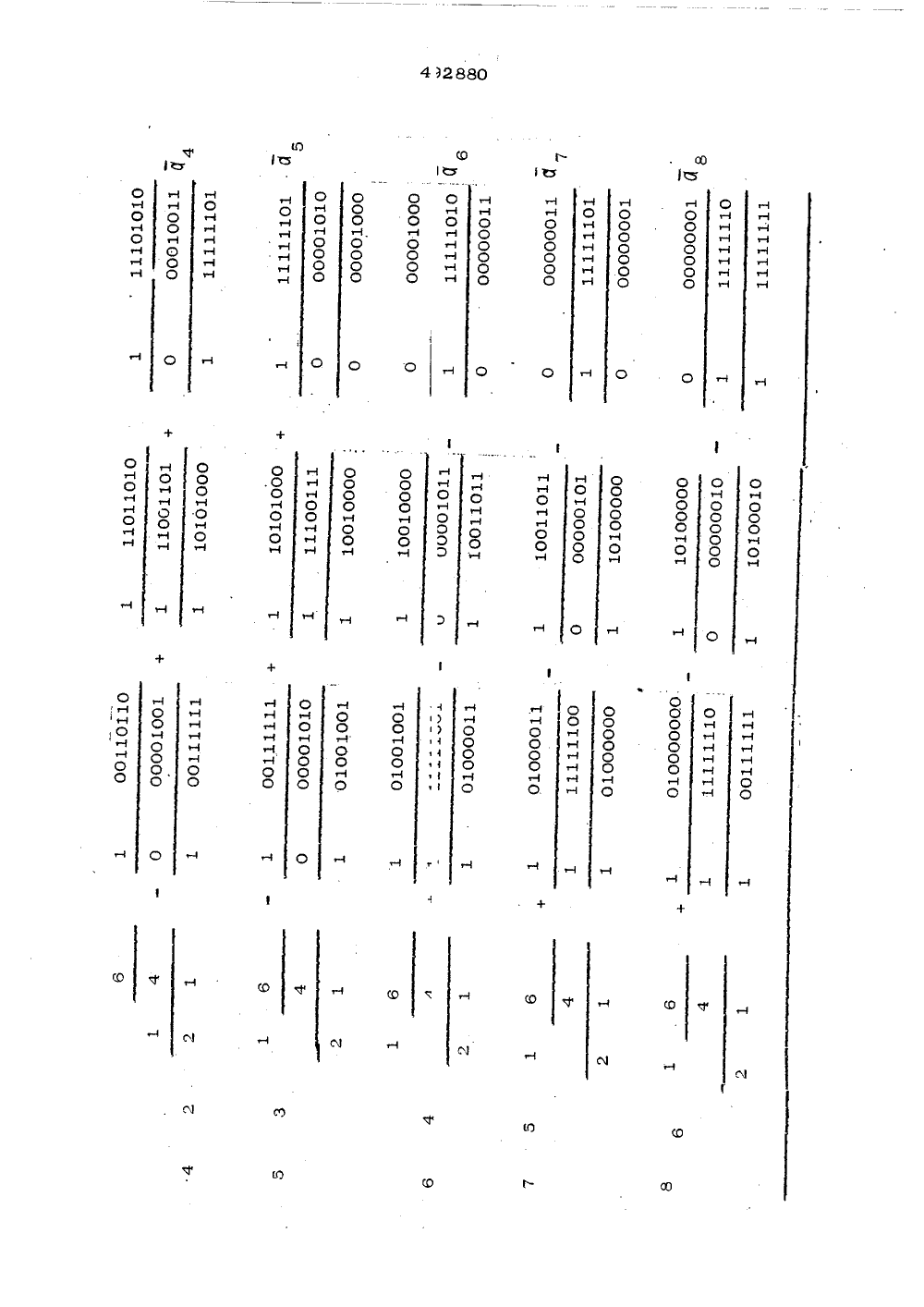

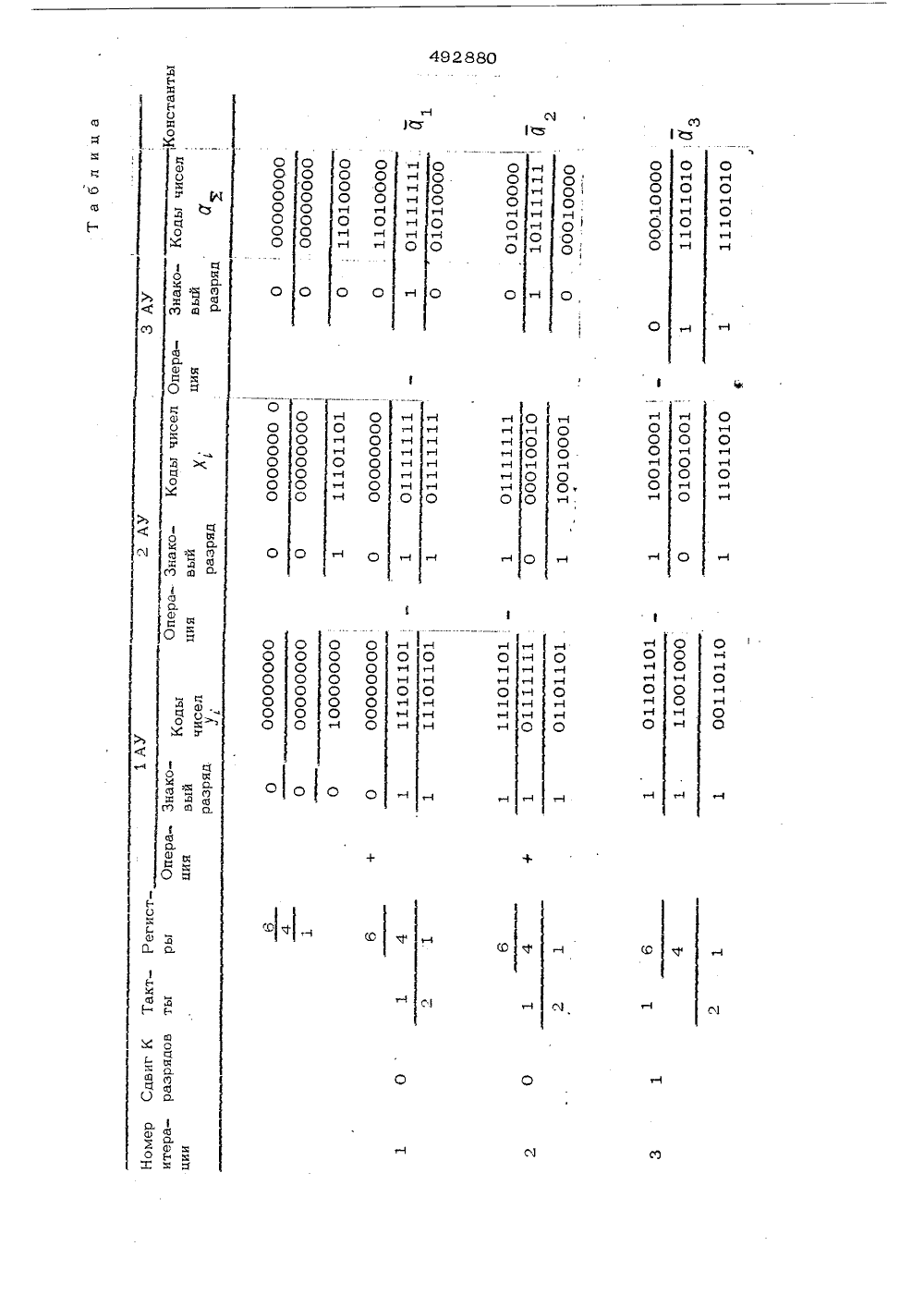

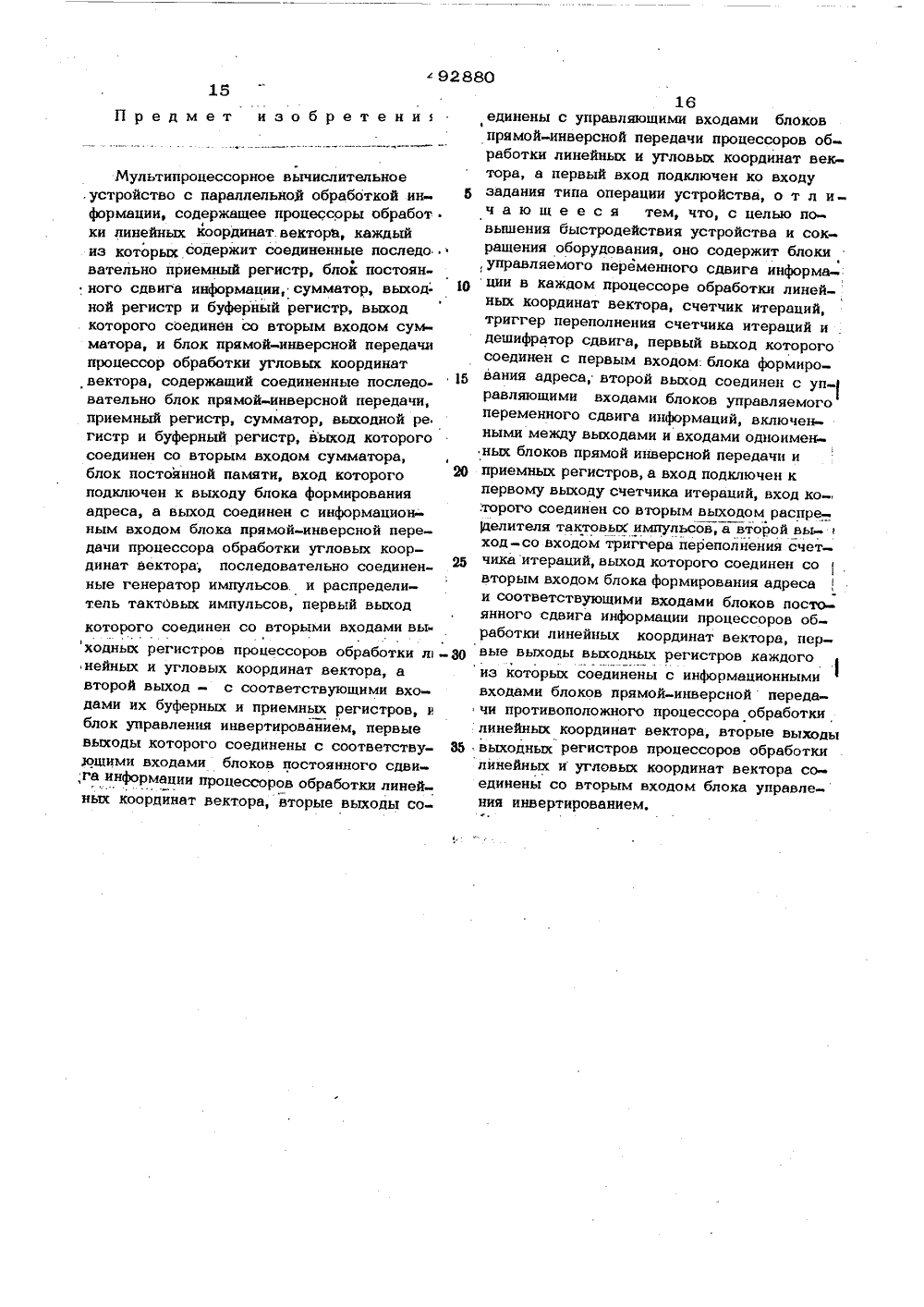

соЫАТБ:-. "-". библиотека Ы:.А О П И С А Н И Е49288 оИЗОБРЕТЕН ИЯ Союз Советских Социалистических Республик. 064 явки И присоединением 1 осударствеиный комитет Совета Мииистров СССР по делам изаоретвкий и открытий. Сазонов, 3, С, Кузин, В. Д, Лугинин 1) Заявитель Ленинград мирал кое училище им ысшее инженерное мо С, О. Макаров(54) МУЛЬТИПРОЦЕССОРНОЕ ВЫЧИСЛИТЕЛЬНОЕ С ПАРАЛЛЕЛЬНОЙ ОБРАБОТКОЙ ИНФОРМ СТРОИСИ брет ие относитс вычислительно ыстро ,приот технике.Известны мультипроцессорные вычислительные устройства с параллельной обработкой информации, содержащие процессоры обработки линейных координат вектора, каж, дый из которых содержит соединенные последовательно приемный регистр, блок постоянного сдвига информации, сумматор, выходной регистр и буферный .регистр, выход которого соединен с вторым. входом сумматора, и блок прямой-инверсной передачи, процессор обработки угловых хоорди нат вектора, содержащий соединенные последовательно блок прямой инверсной передачи, приемный регистр, сумматор, выходной регистр и буферный регистр, выход которого соединен со вторым. входом сумматора, блок постоянной памяти, вход которого подключен к выходу блока формирования ад реса, а выход соединен с информационным входом блока прямой инверсной передачи процессора обработки угловых координат вектора, последовательно соединенные гене.ратор импульсов и распределитель тактовых 25 импульсов, первый выход которого соединен свторыми входами выходных регистров процессоров обработки линейных и угловых координат вектора, а второй выходс соответствующими входами их буферныхи приемных регистров а блок управленияинвертированием, первые выходы которогосоединены с соответствующими входамиблоков постоянного сдвига информации процессоров обработки линейных координатвектора, вторые выходы соединены с управляющими входами блоков прямой инверснойпередачи процессоровобработки линейныхи угловых координат вектора, а первыйвход подключен к входу задания типа операции устройства.Цель изобретения - повышение бдействия и сокращение оборудованиявычислении элементарных функций,Предлагаемое устройство отличаетсяизвестных тем, что оно содержит блокиуправляемого переменного сдвига информации в каждом процессоре обработки линейных координат вектора, счетчик итераций,триггер переполнения счетчика итераций идешифратор сдвига, первый выход которогосоединен с первым входом блока формирования адреса, второй выход соединен с управляющими входами блоков управляемогопеременного сдвига информации, включенными между выходами и входами одноименных блоков прямой инверсной передачи иприемных регистров, а вход подключен кпервому выходу счетчика итераций, входкоторого соединен со вторым выходомраспределителя тактовых ймпульсов,авторой выход - с входом триггера переполнения счетчика итераций, выход которого соединен со вторым вхЬдом блока формирования адреса и соответствующимивходами блоков постоянного сдвига информации процессоров обработки линейныхкоординат вектора, первые выходы выходных регистров каждого из которых соединены с информационными входами блоковпрямой инверсной передачи противоположного процессора обработки линейных координат вектора, вторые выходы выходныхрегистров процессоров обработки линейныхи угловых координат соединены со вторымвходом блока управления инвертированием,На фиг, 1 дана блок-схема мультипро;цессорного вычислительного устройства спараллельной обработкой информации; нафиг, 2 - функциональные схемы блока постоянного сдвига информации, приемногорегистра и блока управляемого переменного сдвига информации.Устройство содержит процессоры 1и 1 обработки линейных координат векто 2ра, процессор 2 обработки угловой координаты вектора, блок 3 постоянной памяти,генератор импульсов 4, распределительтактовых импульсов 5, счетчик итераций6, триггер 7 переполнения счетчика ите.раций, дешифратор сдвига 8, блок 9 формирования адреса, блок 10 управления ин-вертированием и вход 1 1 задания типаоперации.1Процессоры 1 и 1 обработки линей 1 2ных координат вектора содержат, соответственно, выходные регистры 12 и 121 2сумматоры 13 и 13, буферные регистры 14 и 14, блоки 15 и 15 посто 1 2янного сдвига информации, приемйые регистры 16 и 16, блоки 171 и 17 управляемого переменного сдвига информациии блоки 18 и 18 прямой инверсной передачи,2Процессор 2 обработки угловых координат вектора содержит выходной регистр12, сумматор 13, буферный регистр3 14, приемный регистр 16 и блок пря 3мой - инверсной передачи 183Блок 15 постоянного сдвига информации 5 содержит элементы ИЛИ" 19 элементы"И 20 и 21, шину 22 формирования обратного кода числа в старших разрядах,шину 23 разрешения постоянного сдвигаинформации и шину 24 разрешения выдачи 10 информации без сдвига.Приемный регистр 16 содержит триггеры 25.Блок 17 управляемого переменногосдвига информации содержит элементы "ИЛИ", 15 26, элементы фИ" 27-31, шины 32-35разрешения приема информации со сдвигомна О, 1, 2 и 3 разряда, соответственно,шины 36-38 разрешения записи единиц в1, 2 и 3 разряды, соответственно, и ши ну 22 формирования обратного кода числав старших разрядах.Рассмотрим работу устройства на примере вычисления элементарйой функции"поворот вектора" с использованием алго 2 б ритма переменных приращений (алгоритмаВольдера).Алгоритм Вольдера - это итерационныйвычислительный процесс с фиксированнымколичеством итераций И, которые произ- ЗО водится над векторами, заданными своимикоординатами Х,Г в декартовой системе координат, Поворот вектора на угол Ув диапазоне -180 4 Я 4+180 осуществляо оется с помощью серии последовательных 35поворотов на заранее предрассчитанные углыО,, значения которых.пропорциональны числу 2 в отрицательной степенисогласно выражению)Ц =агС 1 2для )11где 1 -номер очередного поворотного шага, т. е. номер итераций.Первый поворот всегда осуществляетсяна + 90 о, а второй - нв +45 и т. д.Вектор поворачивается на базисную последовательность углов Яв таком направлении, чтобы суммарное значение угла ЯОопределяемое выражением 2)стремилоськ нулю, т. е, Я - 0йО =а - ,Е Я,а2) ;,где -.=+ 1 и характеризует направление псь7и 3 разряда подается разрешающий потенциал и сигналы через элементы "И 29или "И" 30,или "И" 31 поступают на вход элемента "ИЛИ" 26, записывая в при.емные регистры 16 число со сдвигом.При этом необходимо помнить, что, еслипроизводится прямая запись отрицательного числа, то К старших разрядов ,необходимо переключить в единичное состояние, чтобы получить обратный код отрицательного числа в этих разрядах. Дляэтого на шину 22 формирования обратного ода числа в старших разрядах и на соответствующее количествошин 36, 37, 38разрещения записи единиц в 1, 2 и 3 разряды подаются разрешающие потенциалы.В результате через элементы "И" 27 встарших разрядах приемного регистра 16запишутся коды единиц.Если перепись числа из выходного ре-,, гистра 12 необходимо осуществить со1сдвигом на К разрядов г 14 К(Я), внашем случае 14 К ( 6, то включается иблок 152 постоянного сдвига информации,при этом на шине 23 разрешения постоянного сдвига информации должен быть разрещаюший потенциал. Обратный код отрица 8тельного числа в первыхстар 2ших разрядах образуется непосредственночерез элементы И 21, ФИЛИ" 19 этих жеразрядов путем подачи разрешающих потенб ,циалов на щину 22 формирования обратного кода числа старших разрядов; а в следующих К разрядах обратный код получа ется через блок 17 управляемого пере 21 Оменного сдвига информации,Аналогично рассмотренному вычислениюэлементарной функции поворота векторавычисляются и другие функции, при этомколичеством итераций управляет счетчикитераций 6 совместно с триггером переполнения счетчика итераций 7, Выходныесигналы счетчика итераций 6 поступают надешифратор сдвига 8, который управляетблоками 17 управляемого переменногосдвига информации и используется для выработки адресов блока 3 постояннои памяти блоком 9 формирования адреса. Сигнальгна блоки 15 постоянного сдвига информации подаются от триггера 7 )перегголнениясчетчика итераций и блока 10 управления 25инвертированием, Временное взаимодействие всех узлов устройства осуществляется,распределителем тактовых импульсов 5, который запускается генератором импульсов 4.Предмет изобретени Мультипроцессорное вычислительное .устройство с параллельной обработкой информации, содержащее процессоры обработки линейных координат. вектора, каждый из которьм содержит соединенные последо вательно приемный регистр, блок постоянного сдвига информации, сумматор, выход- ной регистр и буферный регистр, выход которого соединен со вторым входом сумматора, и блок прямой-инверсной передачи процессор обработки угловых координат вектора, содержащий соединенные последовательно блок прямой-инверсной передачи, приемный регистр, сумматор, выходной ре гистр и буферный регистр, выход которого соединен со вторым входом сумматора, блок постоянной памяти, вход которого подключен к выходу блока формирования адреса, а выход соединен с информационным входом блока прямой-инверсной передачи процессора обработки угловых координат вектора; последовательно соединенные генератор импульсов и распределитель тактовых импульсов, первый выходкоторого соединен со вторыми входами выходных регистров процессоров обработки л- нейных и угловых координат вектора, а второй выход - с соответствующими входами их буферных и приемных регистров, и блок управления инвертированием, первые выходы которого соединены с соответству,ющими входами блоков постоянного сдвига информации процессоров обработки линейных координат вектора, вторые выходы со 16единены с управляющими входами блоков прямой-инверсной передачи процессоров обработки линейных и угловых координат вектора, а первый вход подключен ко входу задания типа операции устройства, о т л ичающееся тем, что, сцельюповышения быстродействия устройства и сокращения оборудования, оно содержит блоки ,управляемого переменного сдвига информа ции в каждом процессоре обработки линейных координат вектора, счетчик итераций, триггер переполнения счетчика итераций и дешифратор сдвига, первый выход которого соединен с первым входом: блока формирования адреса, второй выход соединен с уп- равляющими входами блоков управляемого переменного сдвига информаций, включенными между выходами и входами одноименньм блоков прямой инверсной передачи и 20 приемных регистров, а вход подключен кпервому выходу счетчика итераций, вход ко-, :торого соединен со вторым выходом распре)делителя тактовых импульсов, а второй вы-ход-со входом триггера переполнения счетчика итераций, выход которого соединен совторым входом блока формирования адреса и соответствующими входами блоков постоянного сдвига информации процессоров обработки линейньм координат вектора, пер- ЗО вые выходы выходных регистров каждогоиз которых соединены с информационными входами блоков прямой-инверсной передачи противоположного процессора обработки линейных координат вектора, вторые выходы 35 выходных регистров процессоров обработкилинейных и угловых координат вектора соединены со вторым входом блока управле- ния инвертированием.Подс редприятие Патент, Москва, Г, Бережковская наб., 24 Заказ 3)Ю Изд, М Я У, ТиРаж ЦНИИПИ Государственного комитета Совета Министров ССС П

СмотретьЗаявка

1747760, 15.02.1972

ЛЕНИНГРАДСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ МОРСКОЕ УЧИЛИЩЕ ИМ. АДМ. С. О. МАКАРОВА

САЗОНОВ АНАТОЛИЙ ЕФИМОВИЧ, КУЗИН ЗОТИК СЕМЕНОВИЧ, ЛУГИНИН ВАЛЕРИЙ ДАНИЛОВИЧ, ВЛАСОВ БОРИС МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 17/16

Метки: вычислительное, информации, мультипроцессорное, обработкой, параллельной

Опубликовано: 25.11.1975

Код ссылки

<a href="https://patents.su/9-492880-multiprocessornoe-vychislitelnoe-ustrojjstvo-s-parallelnojj-obrabotkojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Мультипроцессорное вычислительное устройство с параллельной обработкой информации</a>

Предыдущий патент: Многоканальный регистратор

Следующий патент: Устройство для вычисления спектра временного ряда

Случайный патент: Дросселирующее устройство