Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

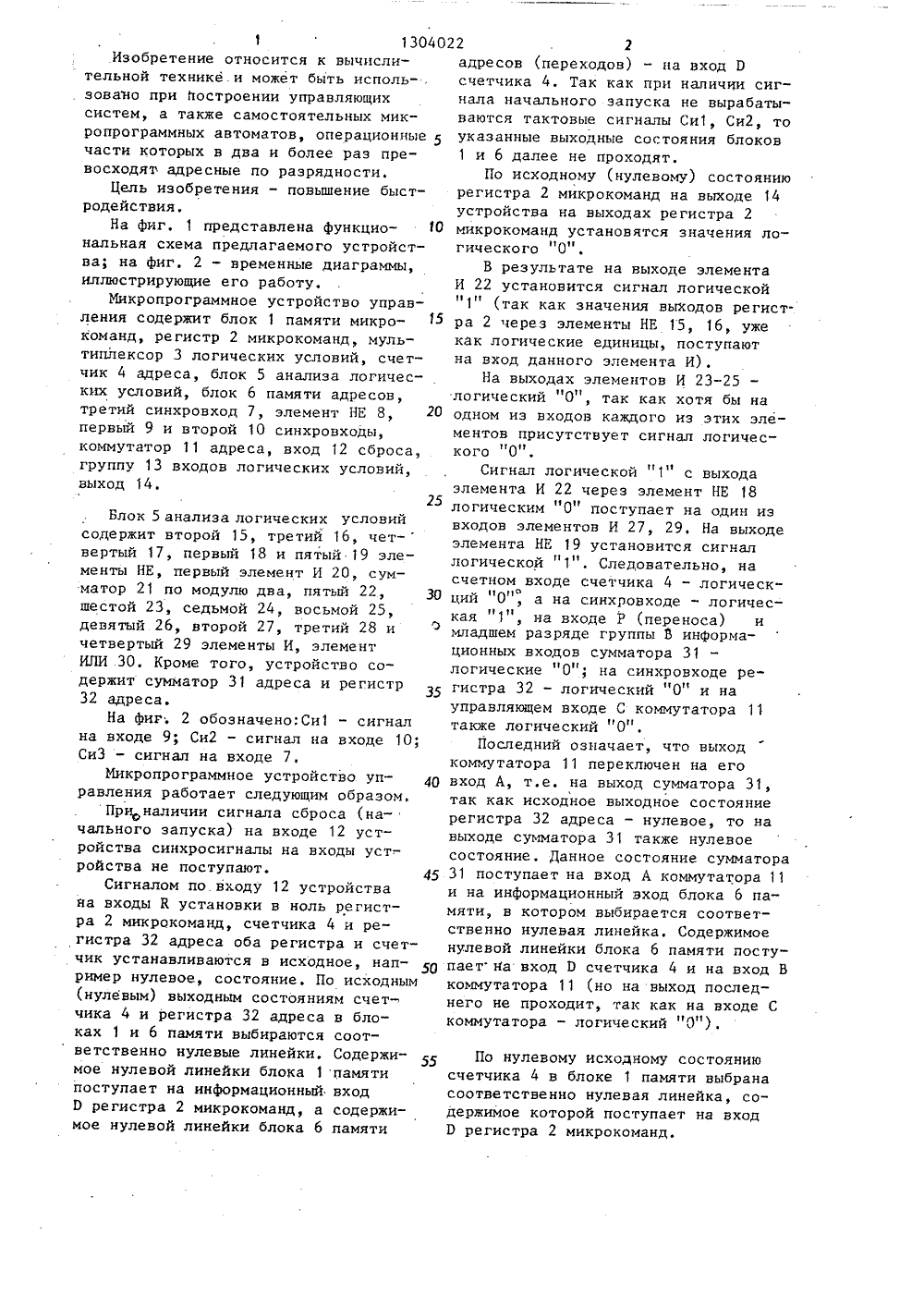

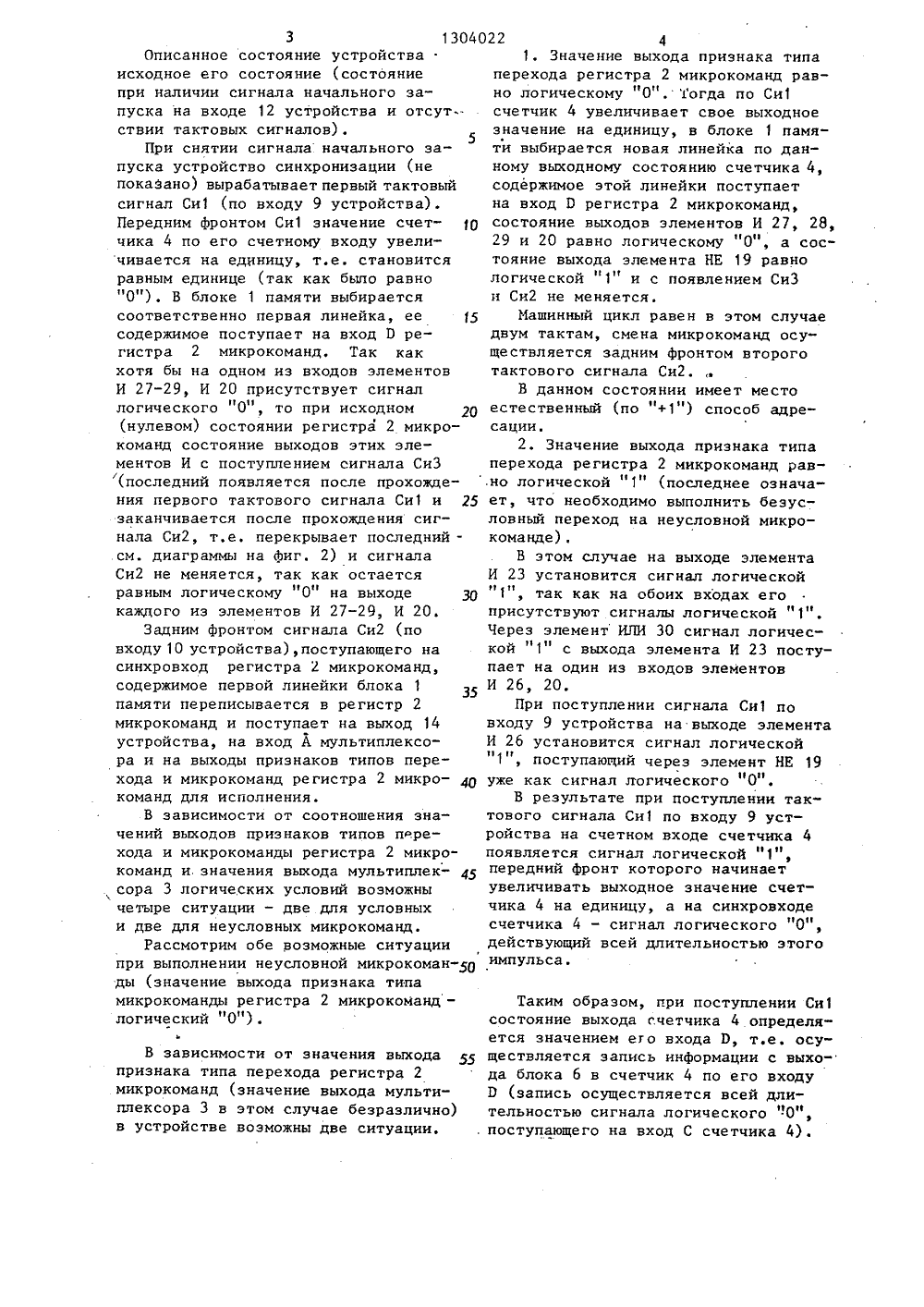

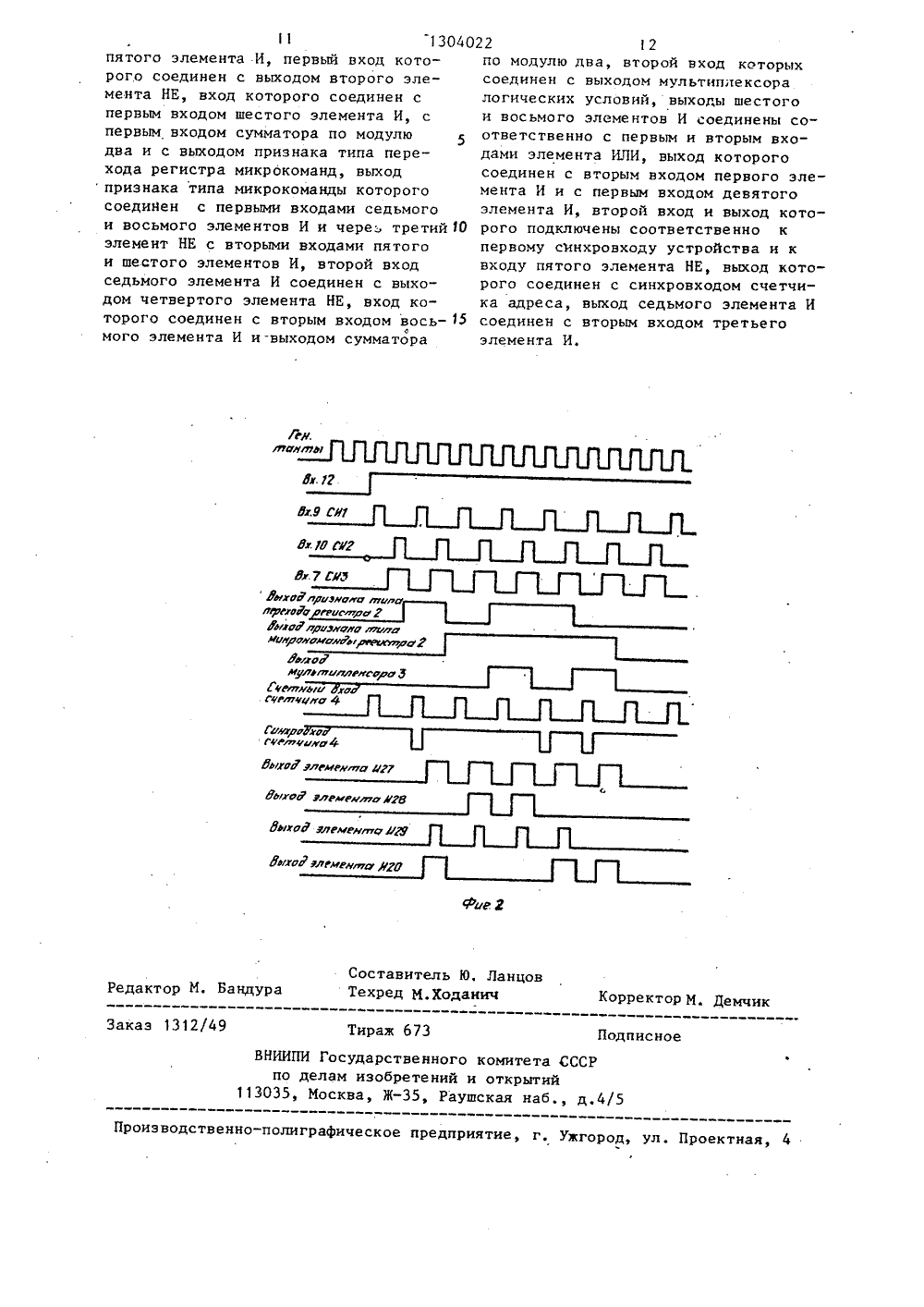

(50 30 РЕТЕНИ ВТОРСНОМ к вычисыть исправляюя - повыйство 24-24 кий,анд, 4 ад ч ски Г.И. Принашин. Л.:5-216,со реса р 32 амяк ят опер а во вт оля 2УДАРСТВЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ ВИДЕТЕЛЬСТВУ(57) Изобретение относится лительной технике и может б пользовано при построении у щих систем. Цель изобретени шение быстродействия. Устро содержит блок 1 памяти микр регистр 2 микрокоманд, счет ;реса, блок 5 анализа логиче условий, блок 6 памяти адре мент НЕ 8, коммутатор 1 1 ад сумматор 31 адреса и регист реса. Использование двух бл ти, в одном из которых хра ционные части микрокоманд, ром - адреса переходов, по достигнуть цели изобретени130402Изобретение относится к вычислительной технике.и может быть использовано при построении управляющихсистем, а также самостоятельных микропрограммных автоматов, операционные 5части которых в два и более Раз превосходят адресные по разрядности.Цель изобретения - повышение быстродействия,На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы,иллюстрирующие его работу.Микропрограммное устройство управления содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, мультиплексор 3 логических условий, счетчик 4 адреса, блок 5 анализа логических условий, блок 6 памяти адресов,третий синхровход 7, элемент НЕ 8, 20первый 9 и второй 10 синхровходы,коммутатор 11 адреса, вход 12 сброса,группу 13 входов логических условий,выход 14.25Блок 5 анализа логических условийсодержит второй 15, третий 16, чет-вертый 17, первый 18 и пятый 19 элементы НЕ, первый элемент И 20, сум -матор 21 по модулю два, пятый 22, 30шестой 23, седьмой 24, восьмой 25,девятый 26, второй 27, третий 28 ичетвертый 29 элементы И, элементИЛИ 30. Кроме того, устройство содержит сумматор 31 адреса и Регистр32 адреса.На фиг; 2 обозначено:Си 1 - сигнална входе 9; Си 2 - сигнал на входе 10;Си 3 - сигнал на входе 7,Микропрограммное устройство управления работает следующим образом.При наличии сигнала сброса (начального запуска) на входе 12 устройства синхросигналы на входы устройства не поступают, 45Сигналом по.входу 12 устройстваяа входы К установки в ноль регистра 2 микрокоманд, счетчика 4 и регистра 32 адреса оба регистра и счетчик устанавливаются в исходное, например нулевое, состояние. По исходным(нулевым) выходным состояниям счетчика 4 и регистра 32 адреса в блоках 1 и 6 памяти выбираются соот ветственно нулевые линейки. Содержимое нулевой линейки блока 1 памятипоступает на информационный входР регистра 2 микрокоманд, а содержимое нулевой линейки блока 6 памяти 2 2адресов (переходов) - на вход Рсчетчика 4. Так как при наличии сигнала начального запуска не вырабатываются тактовые сигналы Си 1, Си 2, тоуказанные выходные состояния блоков1 и 6 далее не проходят.По исходному (нулевому) состояниюрегистра 2 микрокоманд на выходе 14устройства на выходах регистра 2микрокоманд установятся значения логического ОВ результате на выходе элементаИ 22 установится сигнал логической"1" (так как значения выходов регистра 2 через элементы НЕ 5, 16, ужекак логические единицы, поступаютна вход данного элемента И),На выходах элементов И 23-25логический "0", так как хотя бы наодном из входов каждого из этих элементов присутствует сигнал логического 0Сигнал логической "1" с выходаэлемента И 22 через элемент НЕ 18логическим 0 поступает на один извходов элементов И 27, 29, На выходеэлемента НЕ 19 установится сигналлогической " 1". Следовательно, насчетном входе счетчика 4 - логическций "0", а на синхровходе - логическая "1", на входе Р (переноса) имладшем разряде группы В информационных входов сумматора 31логические "0"; на синхровходе регистра 32 - логический "0" и науправляющем входе С коммутатора 11также логический "0".Последний означает, что выходкоммутатора 11 переключен на еговход А, т.е. на выход сумматора 31,так как исходное выходное состояниерегистра 32 адреса - нулевое, то навыходе сумматора 31 также нулевоесостояние. Данное состояние сумматора31 поступает на вход А коммутатора 11и на информационный вход блока 6 памяти, в котором выбирается соответственно нулевая линейка. Содержимоенулевой линейки блока 6 памяти поступает на вход Р счетчика 4 и на вход Вкоммутатора 11 (но на выход последнего не проходит, так как на входе Скоммутатора - логический "О"). По нулевому исходному состоянию счетчика 4 в блоке 1 памяти выбрана соответственно нулевая линейка, содержимое которой поступает на вход Р регистра 2 микрокоманд.1304022 3Описанное состояние устройства . исходное его состояние (состояние при наличии сигнала начального запуска на входе 12 устройства и отсут ствии тактовых сигналов).При снятии сигнала начального запуска устройство синхронизации (не показано) вырабатывает первый тактовый сигнал Си 1 (по входу 9 устройства). Передним фронтом Си 1 значение счет чика 4 по его счетному входу увеличивается на единицу, т.е. становится равным единице (так как быпо равно "0"). В блоке 1 памяти выбирается соответственно первая линейка, ее 15 содержимое поступает на вход П регистра 2 микрокоманд. Так как хотя бы на одном из входов элементов И 27-29, И 20 присутствует сигнал логического 0, то при исходном 20 (нулевом) состоянии регистра 2 микро- команд состояние выходов этих элементов И с поступлением сигнала Си 3 (последний появляется после прохождения первого тактового сигнала Си 1 и 25 заканчивается после прохождения сигнала Си 2, т.е. перекрывает последнийсм. диаграммы на фиг. 2) и сигнала Си 2 не меняется, так как остается равным логическому 0 на выходе 30 каждого из элементов И 27-29, И 20.Задним фронтом сигнала Си 2 (по входу 10 устройства),поступающего на синхровход регистра 2 микрокоманд, содержимое первой линейки блока 1 памяти переписывается в регистр 2 микрокоманд и поступает на выход 14ьустройства, на вход А мультиплексора и на выходы признаков типов перехода и микрокоманд регистра 2 микро команд для исполнения.В зависимости от соотношения значений выходов признаков типов перехода и микрокоманды регистра 2 микро- команд и. значения выхода мультиплек сора 3 логических условий возможны четыре ситуации - две для условных и две для неусловных микрокоманд.Рассмотрим обе возможные ситуации при выполнении неусловной микрокоманды (значение выхода признака типа микрокоманды регистра 2 микрокоманд - логический 0) .ЬВ зависимости от значения выхода признака типа перехода регистра 2 микрокоманд (значение выхода мультиплексора 3 в этом случае безразлично) в устройстве возможны две ситуации. 41, Значение выхода признака типаперехода регистра 2 микрокоманд равно логическому "0", Тогда по Си 1счетчик 4 увеличивает свое выходноезначение на единицу, в блоке 1 памяти выбирается новая линейка по данному выходному состоянию счетчика 4,содержимое этой линейки поступаетна вход Р регистра 2 микрокоманд,состояние выходов элементов И 27, 28,29 и 20 равно логическому "0", а состояние выхода элемента НЕ 19 равнологической " 1" и с появлением Си 3и Си 2 не меняется.Машинный цикл равен в этом случаедвум тактам, сиена микрокоманд осуществляется задним фронтом второготактового сигнала Си 2.В данном состоянии имеет местоестественный (по "+1") способ адресации.2. Значение выхода признака типаперехода регистра 2 микрокоманд равно логической "1" (последнее означает, что необходимо выполнить безусловный переход на неусловной микрокоманде),В этом случае на выходе элементаИ 23 установится сигнал логической"1", так как на обоих входах егоприсутствуют сигналы логической " 1",Через элемент ИЛИ 30 сигнал логической "1" с выхода элемента И 23 поступает на один из входов элементовИ 26, 20,При поступлении сигнала Си 1 повходу 9 устройства на выходе элементаИ 26 установится сигнал логическойи ц1 , поступающий через элемент НЕ 19уже как сигнал логического 0.В результате при поступлении тактового сигнала Си 1 по входу 9 устройства на счетном входе счетчика 4появляется сигнал логической "1",передний фронт которого начинаетувеличивать выходное значение счетчика 4 на единицу, а на синхровходесчетчика 4 - сигнал логического "0",действующий всей длительностью этогоимпульса. Таким образом, при поступлении Си 1 состояние выхода счетчика 4 определяется значением его входа П, т.еосуществляется запись информации с выхо- да блока 6 в счетчик 4 по его входу Э (запись осуществляется всей длительностью сигнала логического 0, поступающего на вход С счетчика 4).5 13040Так как к моменту появления тактового сигнала Си 1 значения входа Ри младшего разряда группы входов В сумматора 31 равны логическому "О", на выходе блока 6 памяти присутствует содержимое линейки этого блока, выбранной в нем по адресу - выходному состоянию регистра 32 адреса.Кроме того, сигнал логической " 1"с выхода признака типа перехода регистра 2 микрокоманд через элементыНЕ 15, И 22 и НЕ 18 поступает на одиниз входов элементов И 27, 29, На одном из входов элемента И 28 присутст"вует сигнал логического 0 с выхода 15элемента И 24, а на одном из входовэлемента И 20 - сигнал логической "1"с выхода элемента ИЛИ 30,С поступлением сигнала СиЗ (навходе 7 устройства) на выходе элемента И 27 устанавливается сигнал логической "1", который поступает навход Р сумматора 31 и увеличивает егосодержимое на единицу относительновыходного состояния регистра 32 адреса, По полученному выходному состоя-.нию сумматора 31 в блоке 6 выбираетсяследующая линейка, содержимое которойпоступает на вход В коммутатора 11,на управляющий вход С которого поступает сигнал лонической "1" с выходаэлемента И 20 (на первом его входелогическая " 1" с входа 7, а на втором - логическая "1" с выхода элемента ИЛИ 30). Таким образом, на выходе коммутатора 11 устанавливаетсязначение выхода блока 6,При поступлении переднего фронтасигнала Си 2 по входу 1 О устройствана выходе элемента И 29 появляется 40сигнал логической "1", так как теперьна обейх его входах присутствуют сигналы логической "1".Сигнал логической "1" с выходаэлемента И 29 поступает на синхровход регистра 32 и передним фронтомзаписывает содержимое выхода блока 6в регистр 32 адреса,Данное выходное состояние регистра. 32 является новым адресом для блока 6 50после безусловного перехода по микропрограмме в блоке 1. Таким образом,за счет изменения значения счетчика 4по сигналу Си 1 осуществляется безусловный переход на неусловной микрокоманде: по Си 1 в счетчик 4 записыватеся содержимое линейки блока 6памяти адресов (переходов), выбраннойпо адресу - выходному состоянию ре 22 6гистра 32 адреса, проходящему черезсумматор 31 без изменения и представляющему собой адрес безусловного перехода, по которому в блоке 1 памятивыбирается соответствующая линейка,затем по СиЗ выходное значение сумматора 31 увеличивается на единицу ичерез коммутатор 11 (по входу В его)содержимое следующей линейки блока 6(по переднему фронту Си 2) перепишетсяв регистр 32 адреса, представляя собой адрес рпя выбора следующей линейки в блоке 6 памяти адресов (перехо"дов) .Рассмотрим далее две возможныеситуации в устройстве в случае выполнения условной микрокоманды (выходпризнака типа микрокоманды регистра 2микрокоманд. - логическая "1"). В этомслучае значение выхода признака типаперехода регистра 2 микрокоманд может иметь значение логического О"или логической "1", а значение выхода мультиплексора 3 логических условий определяется (как обычно) условиями, поступающими на его информационные входы по группе входов 13 устройства.Выбор пути формирования адресаследующей микрокоманды микропрограммыопределяется соотношением значенийвыхода признака типа перехода регистра 2 микрокоманд и выхода мультиплексора 3,Пусть значение выхода признака типа перехода регистра 2 - логический"О", значение выхода мультиплексоца 3условий - также логический ноль, т.есовпадают (.однозначны).В этом случае на выходе сумматора21 по модулю два присутствует сигналлогического "О", так как сигналы навходах сумматора 21 однозначны.Через элемент НЕ 17 этот сигнал,уже как сигнал логической единицы,поступает на один из входов элементаИ 24, на втором входе этого элементаприсутствует сигнал логической "1" свыхода признака типа микрокоманды регистра 2 микрокоманд (так как рас-сматриваем случай выполнения условий .:микрокоманды), На выходе элементаИ 24 - сигнал логической " 1", которыйпоступает на первый вход элементаИ 28. С выхода элемента НЕ 18 сигналлогической "1" поступает на первыевходы элементов И 27, 29 (на выходахэлементов И 22, 23 25 присутствуютсигналы логического "0"), 7 13 О 4 ОПри поступлении переднего фронта тактового сигнала Си 1 по входу 9 устройства на счетный вход счетчика 4 значение выхода его увеличивается на единицу. В блоке 1 памяти по дан - ному адресу (полученное выходное состояние счетчика 4) выбирается следую - щая линейка, содержимое которой (следующая микрокоманда микропрограммы) поступает на вход П регистра 2 микро-О команд (но до поступления тактового сигнала Си 2 не переписывается в регистр 2 микрокоманд).При поступлении переднего фронта управляющего сигнала Си 3 на выходах элементов И 27, 28 появляются сигналы логической "1", поступающие соответственно на вход Р (переноса) и младший разряд группы В информационных входов сумматора 31, В результате 20 на выходе сумматора устанавливается значение, увеличенное на два по сравнению с предыдущим, равным выходному значению регистра 32.адреса.При поступлении переднего фронта тактового сигнала Си 2 на второй вход элемента И 29 (на первом входе которого - сигнал логической "1" с выхода элемента НЕ 18) на выходе последнего появляется сигнал логической "1" дли тельностью, равной длительности Си 2. Этот сигнал поступает на синхровход регистра 32 адреса, записывая передним фронтом по его входу 0 информацию, поступающую с выхода сумматора 35 31 через коммутатор 11 (по его входу А), так как на входе С последнего присутствует сигнал логического 0.В результате выходное состояние сумматора 31, отличающееся от преды дУщего на два, по переднему фронту тактового сигнала Си 2 переписано в регистр 32 адреса, а по заднему фронту Си 2. следующая микрокоманда (выб-, ранная в блоке 1 памяти по адресу - 45 выходному состоянию счетчика 4 при поступлении Си 1) с входа 0 регистра 2 микрокоманд переписывается в последний. Так осуществляется естественный способ адресации при выполнении ус ловной микрокоманды. При единичном значении (логическая " 1") выходов мультиплексора 3 логических условий и выхода признака типа 55 перехода регистра 2 микрокоманд работа устройства аналогична описанной, т,е, осуществляется естественный способ адресации: в блоке 1 памяти по 22 8"+1", а в блоке 6. памяти адресов (пе - реходов) - по "+2".Рассмотрим вторую ситуацию для случая выполнения условной микрокоманды,Пусть значения выходов мультиплексора 3 логических условий и выхода признака типа перехода регистра 2 микрокоманд неоднозначны, т.е. когда один имеет на выходе логическую 1 второй - логический "О, и наоборот.В этом случае на выходе сумматора 21 по модулю два установится сигнал логической "1" (так как сигналы на входах сумматора 21 неравнозначны). Этот сигнал логической "1" поступает на один из входов элемента И 25, на втором входе которого присутствует сигнал логической "1" с выхода приз- яака типа микрокоманды регистра 2 микрокоманд. Следовательно, на выходе элемента И 25 устанавливается сигнал логической 1, который через элемент ИЛИ 30 поступает на один из входов элементов И 26 и 20.При поступлении переднего фронта тактового сигнала Си 1 по входу 9 устройства на счетный вход счетчика 4 состояние последнего начинает изменяться.Одновременно (при поступлении Си 1) на выходе элемента И 26 устанавливается сигнал логической " 1", так как на обоих его входах присутствуют сигналы логической единицы (на одном входе Си 1, на втором - сигнал логической "1" с выхода сумматора 21 через элементы И 25 и ИЛИ 30). В результате на выходе элемента НЕ 19 устанавливаетСя сигнал логического "0" длительностью Си 1. Этот сигнал, поступая на синхровход счетчика 4, осуществляет запись информации с выхода блока 6 памяти (по входу О счетчика 4), значение выходов элементов И 27-29, И 20 при наличии Си 1 равно логическому "0 В результате на выходе счетчика 4 устанавливается содержимое линейки блока 6 памяти адресов, выбранной в последнем по адресу - выходному состоянию регистра 32 адреса (сумматор 31 изменений не вносит, так как на его входах Р и В при наличии сигнала Си 1 присутствуют сигналы логического 0) . По полученному таким образом адресу - выходному состоянию счетчика 4 в блоке 1 памяти выбирается9 13040линейка, содержимое которой поступаетна вход Р регистра 2 микрокоманд(но до поступления тактового сигналаСи 2 не переписывается в регистр 2) .При поступлении сигнала СиЗ повходу 7 устройства на выходе элементаИ 21 появится сигнал логической "1",поступающий на вход Р переноса сумматора 31. Длительность этого сигналаравна длительности сигнала СиЗ. 10В результате на выходе сумматора31 установится значение, равное выходному значению регистра 32 адресаплюс единица и представляющее собойадрес, по которому в блоке 6 памяти 15выбирается следующая линейка. Содержимое этой линейки с выхода блока 6памяти поступает на вход 0 счетчика 4и на вход В (второй информационный.вход) коммутатора 11.20Одновременно (с момента поступления сигнала СиЗ) на выходе элементаИ 20 устанавливается сигнал логической "1", поступающий на вход С (управляющий вход) коммутатора 11, переключающий его выход на собственныйвход В. С поступлением переднегофронта тактового сигнала Си 2 по входу 10 устройство на выходе элементаИ 29 установится сигнал логической 30"1",. так как на обоих входах его присутствуют сигналы логической "1" (наодном входе - с выхода элемента НЕ 18,на втором " с входа 10 устройства).Сигнал логической "1" с выходаэлемента И 29 поступает на синхровход региСтра 32 адреса. Переднимфронтом этого сигнала осуществляетсязапись информации с входа В коммута-,тора 11, через последний - в регистр32 адреса (по его входу О),По данному адресу (по выходномусостоянию регистра 32) в блоке 6памяти будет выбрана новая линейка,содержимое которой является адресом 45следующего безусловного перехода наусловной или неусловной микрокомандеданного устройства.Формула из обретения50Микропрограммное устройство управления, содержащее блок памяти микро- команд, регистр микрокоманд, счетчик адреса, мультиплексор логических условий и элемент НЕ, причем входы сброса регистра микрокоманд и счетчика адреса подключены к входу сброса устройства, информационный вход ре 22 1 Огистра микрокоманд соединен с выходомблока памяти микрокоманд, адресныйвход которого соединен с информационным выходом счетчика адреса, счетный вход которого подключен к первомусинхровходу устройства, синхровходрегистра микрокоманд подключен черезэлемент НЕ к второму синхровходу устройства, выходы поля микрооперацийи поля проверки Логических условийрегистра микрокоманд подключены соответственно к выходу устройства и куправляющему входу мультиплексоралогических условий, группа информационных входов которого подключенак группе входов логических условийуатройства, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия оно содержит блок памятиадресов, регистр адреса, сумматорадреса, коммутатор адреса и блок анализа логических условий, содержащийпять элементов НЯ, сумматор по модулю два, девять элементов И и элемент ИЛИ, причем вход сброса регистраадреса подключен к входу сброса устройства, информационный вход счетчикаадреса соединен с выходом блока памяти адресов и с первым информационнымвходом коммутатора адреса, второйинформационный вход которого соединен с адресным входом блока памятиадресов и с выходом сумматора адреса,первая группа информационных входовкоторого соединена с группой выходоврегистра адреса, информационный входкоторого соединен с выходом коммутатора адреса, управляющий вход которого соединен с выходом первого элемента И, первый вход которого соединенс первыми входами второго и третьегоэлементов И и подключен к третьемусинхровходу устройства, выходы второго, третьего и четвертого элементовИ соединены соответственно с входомпереноса сумматора адреса, с информационным входом младшего разрядавторой группы информационных входовсумматора адреса и с синхровходомрегистра адреса, информационный входстарших разрядов второй группы информационных входов, сумматора адресаподключен к шине нулевого потенциалаустройства, первый вход четвертогоэлемента И подключен к второму синхровходу устройства, вторые входывторого и четвертого элементов И соединены с выходом первого элементаНЕ, вход которого соединен с выходомЬ.У ГО Ю.7 Гн Вииад яриэнано тилолрююда ееиатри 2Заадлриэнана гщгламинрвичюжЬрюиира 2 Ьааамилетилленжро а1 ююыи хаеетнина Ф Гиюра .югиетиина 4. двчод элемента игг аыхад элемента йгВ дикад элемент Щ бякаа элемента И 20 Фие Я Составитель Ю. ЛанцовТехред М.Ходанич Редактор М. Бандура Корректор М. немчик Заказ 1312/49 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж, Раушская наб., д.4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4Ъ 1 3040 пятого элемента И, первый вход которого соединен с выходом второго элемента НЕ, вход которого соединен с первым входом шестого элемента И, с первым входом сумматора по модулю два и с выходом признака типа перехода регистра микрокоманд, выходпризнака типа микрокоманды которого соединен с первыми входами седьмого и восьмого элементов И и через третий 10 элемент НЕ с вторыми входами пятого и шестого элементов И, второй вход седьмого элемента И соединен с выходом четвертого элемента НЕ, вход которого соединен с вторым входом вось мого элемента И и-выходом сумматора 22 2по модулю два, второй вход которых соединен с выходом мультиплексора логических условий, выходы шестого и восьмого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и с первым входом девятого элемента И, второй вход и выход которого подключены соответственно к первому синхровходу устройства и к входу пятого элемента НЕ, выход которого соединен с синхровходом счетчика адреса, выход седьмого элемента И соединен с вторым входом третьего элемента И.

СмотретьЗаявка

3803328, 17.10.1984

ПРЕДПРИЯТИЕ ПЯ А-1736

КАТАШЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, МИХАЦКИЙ АЛЬБЕРТ ТИМОФЕЕВИЧ, ПАНГА АЙВАР ВИЛЬФРИДОВИЧ, ПЕТРАКОВ ВЛАДИМИР НИКОЛАЕВИЧ, ЦВЕТКОВ ЯН ЯНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.04.1987

Код ссылки

<a href="https://patents.su/7-1304022-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Загрузочно-ориентирующее устройство