Устройство для суммирования двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1264164

Авторы: Домбровский, Дуда, Узлова

Текст

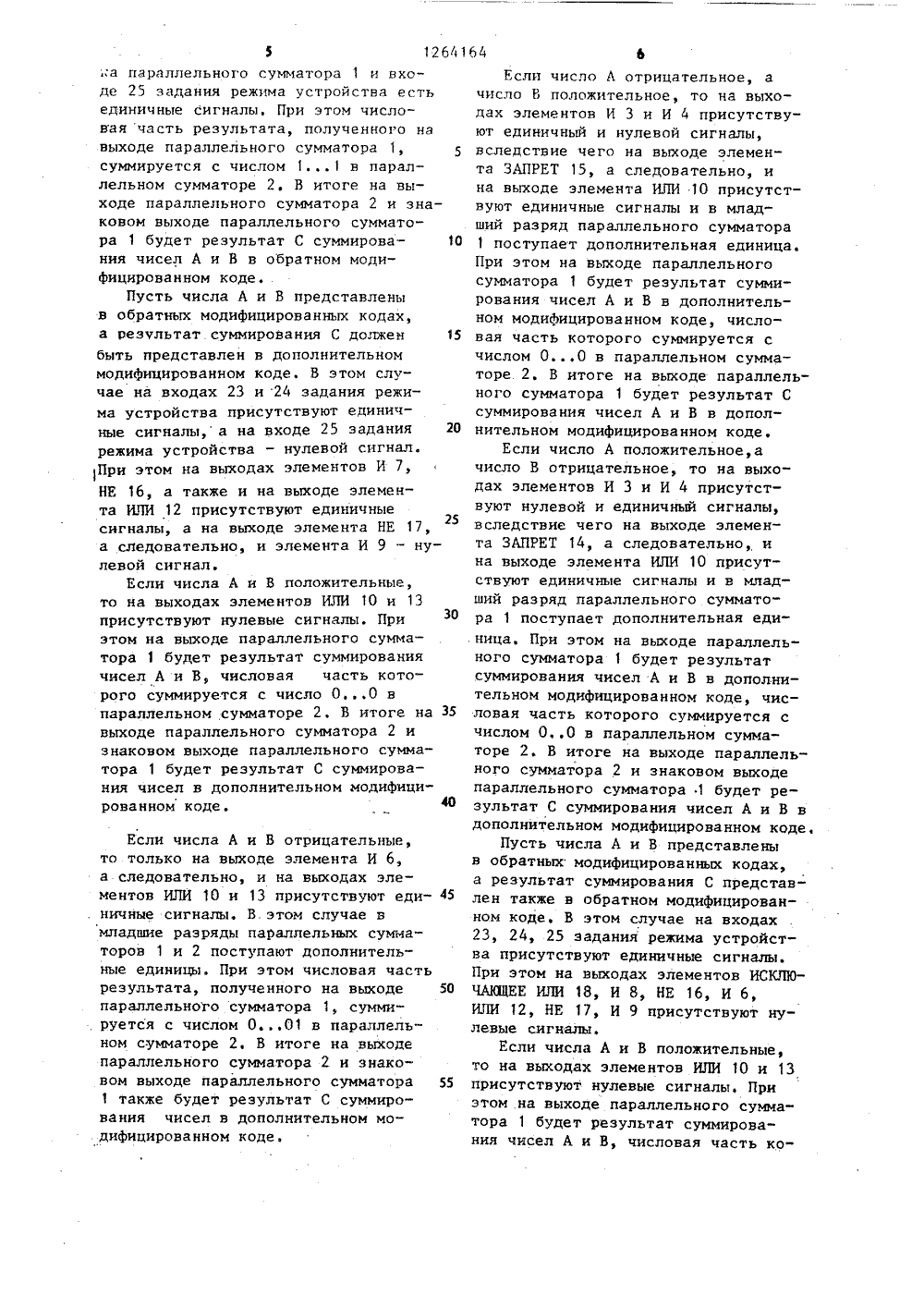

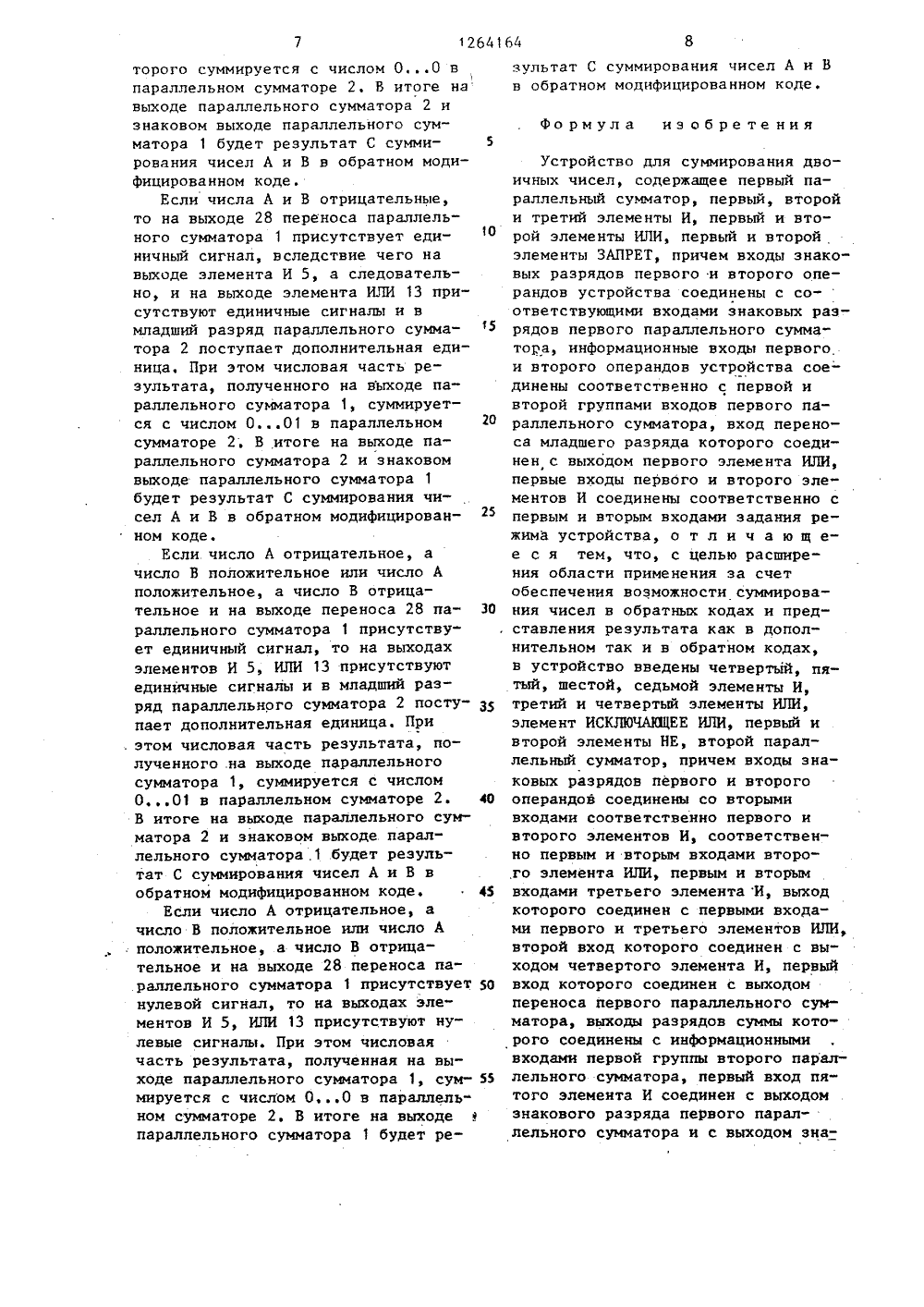

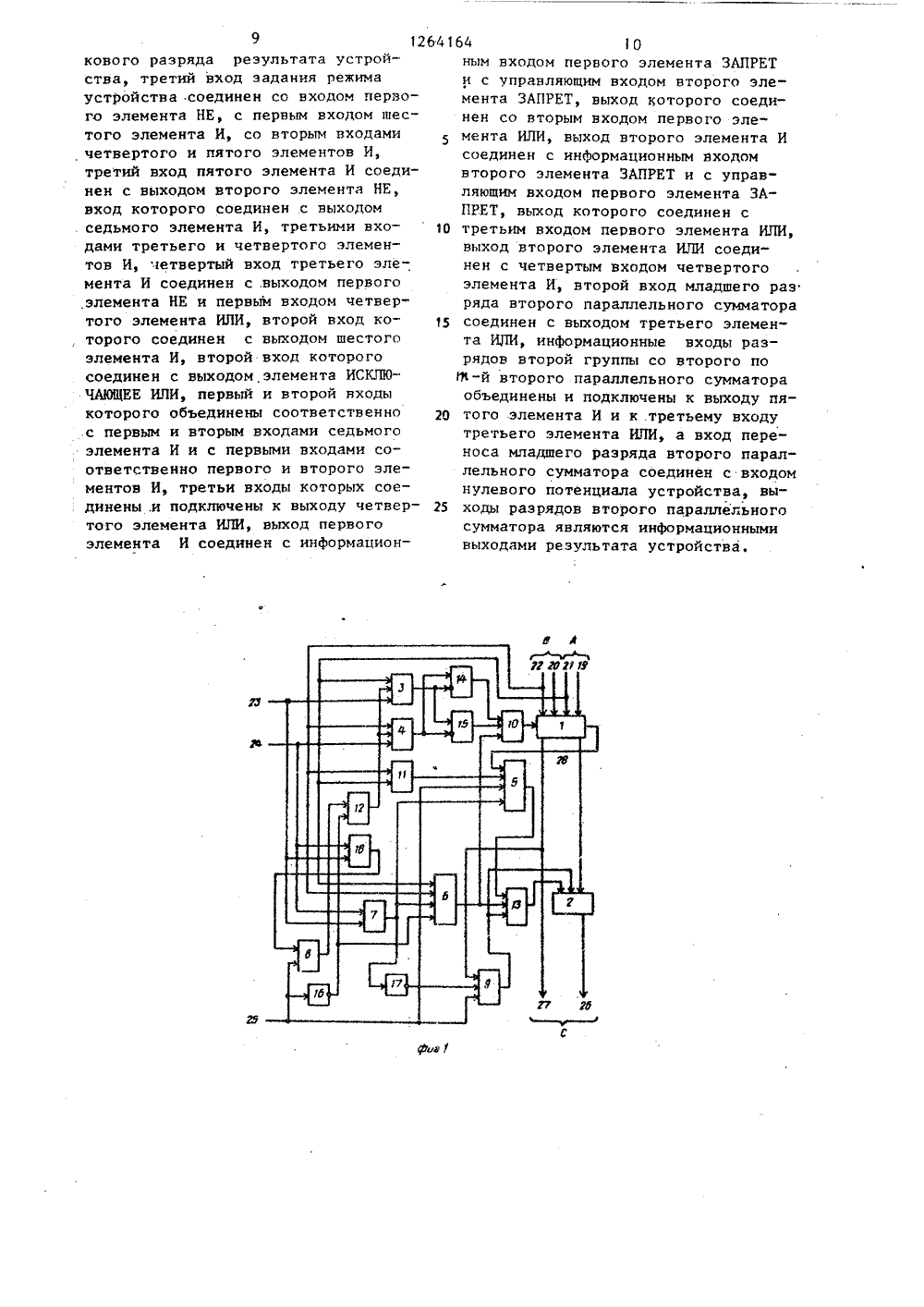

ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(71) Тернопольский финансовмический институт(56) Самофалоз К. Г., КорнейТарасенко В.П, Электронныевычислительные машины. Киевшкола, 1976, с. 167, рис. 1Авторское свидетельствоУ 1193665, кл, С 06 Р 7/50,(54) УСТРОЙСТВО ДЛЯ СУ 1 ФЯРОВАНИЯДВОИЧНЫХ ЧИСЕЛ(57) Изобретение относится к области автоматики и вычислительной техники, Цель изобретения - расширениеобласти применения за счет обеспечения возможности суммирования чисел в обратньм кодах и представлениярезультата суммирования как в дополнительном, так и обратном коде.Устройство для суммирования двоичныхчисел содержит первый параллельный сумматор, три элемента И, дваэлемента ЗАПРЕТ и первый элемент ИЛИ,причем разряды первого числового входа первого параллельного сумматорасоединены с первой входной числовойшиной устройства, разряды второго числового входа соединеяы со второйвходной числовой шиной устройства,разряды первого и второго входовзнака первого параллельного сумматора соединены с соответствукщимивходными шинами знака устройства ипервым и вторым входами первого элемента И, выход которого соединен спервым входом первого элемента ИЛИ,а вьмод первого элемента ИЛИ соединен со входом переноса младшего разряда первого параллельного сумматора, первый вход задания режимаустройства соединен с первым входомвторого элемента И, второй входзадания режима устройства соединенс первым входом третьего элемента И,прямой вход элемента ЗАПРЕТ соединен с инверсным входом второго элемента ЗАПРЕТ, а инверсный вход первого элемента ЗАПРЕТ соединен спрямым входом второго элемента ЗАПРЕТ, Новым в устройстве является введение второго параллельного сумматора, четвертого,пятого,шестого и седьмого элементов И,второго, третьего и четвертого элементов ИЛИ, элемента ИСКЛЮЧАКЩЕЕ ИЛИпервого и второго элементов НЕ, ко"торые соответствунщим образом соединены между собой и с соответст"вущцими другими элементами, входамии выходами устройства. 2 ил.изобретение относится к автоматике и вычислительной технике.Цель изобретения - расширение области применения за счет обеспечения воэможности суммирования чисел вобратных кодах и представления результата как н обратном, так и вдополнительном кодах.На фиг. 1 представлена блок-схемаустройства для суммирования двоичных чисел, на фиг.2 - блок-схемапараллельного сумматора 2,Устройство содержит (фиг.1) параллельные сумматоры 1 и 2 элементы И 3-9, ИЛИ 10-13, ЗАПРЕТ 14 и 15,НЕ 16 и 17, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ18, информационные входы 19 и 20слагаемых и входы 21 и 22 знаков,входы задания режима 23, 24 и 25,информационные выходы результата 26,выход знакового разряда 27 результата, ввиод 28 переноса параллельного сумматора 1 еПараллельный сумматор (фиг.2)содержит последовательно соединенные одноразрядные сумматоры 29-32.Устройство для суммировании двоичных чисел работает следующим образом,Числа А и В, поступающие на соответствующие входы 19, 21 и 20 и 22устройства, представлены г числовыми и двумя знаковыми разрядами, арезультат С на выходах 26 и 2 устройства представлен также 1 числовыми и двумя знаковыми разрядами.Если число А, поступающее на входы 19 и 21, представлено н дополнительном модифицированяом коде, тона входе 23 задания режима устройст -на должен быть нулевой сигнал, а если нобратном модифицированном коде,то на входе 23 задания режима уст- .ройства должен быть единичньй сигнал, Если число В, поступающее навходи 20, 22, представлено в цояолнительном модифицированном коде, тона.входе 24 задания режима устройства должен быть нулевой сигнал, аесли н обратном модифицированномкоде, то яа входе 24 задания режимаустройства должен быть единичныйсигнал, Если результат суммирования С должен быть представлен и до"полнительном модифицированном кодето на нходе 25 задания режима устройства должен быть нулевой сигнал,а если н обратном модифицированном коде, то на входе 25 задания режимаустройства должен быть единичныйсигнал,Пусть числа А и В представлены ндополнительных модифицированных кодах, а результат суммирования представлен н дополнительном модифицированном коде. В этом случае на входах 23, 24 и 25 задания режима устройства присутствуют нулевые сигналы.При этом на выходе элемента НЕ 16,атакже на выходах элементов И 9,ИЛИ 10 и 13 присутствуют нулевые сигналы. В этом случае на выходе параллельного сумматора 1 будет результат суммирования чисел А и В вдополнительном модифицированном коде, числовая часть которого суммируется числом 00 в параллельномсумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковомвыходе параллельного сумматора 1 будет результат С суммирования чиселА и В - в дополнительном модифицированном коде.Пусть числа А и В представлены в дополнительных модифицированных кодах, а результат суммирования С представлен в обратном модифицированномкоде. В этом случае на входах 23,24задания режима устройства присутствуют нулевые сигналы, а на входе25 задания режима устройства присутствует единичный сигнал. При этомна выходе элемента ИЛИ 10 присутствует нулевой сигнал.Если на выходе параллельного сумматора 1 есть положительный результат суммирования чисел А и В,представленный в дополнительном модифицированном коде, то числовая частьэтого результата суммируется с числом ОО в параллельном сумматоре 2. Если на выходе параллельногосумматора 1 есть отрицательный результат суммирования чисел А и В,представленный в дополнительном модифицированном коде, то на выходеэлемента И 9 присутствует единичнвй сигнал, так как на выходе элемента НЕ 17, выходе знака параллель"ного сумматора 1 и входе 25 заданиярежима устройства присутствуют единичные сигналы. При этом числоваячасть результата, полученного навыходе параллельного сумматора 1,суммируется с числом 11 в параллельном сумматоре 2. В итоге навыходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат суммирования чисел А и В в обратном модифицированном коде5Пусть число А представлено в обратном модифицированном коде, число В - в дополнительном модифицированном коде, а результат суммиро 1 О вания С представлен в дополнительном модифицированном коде. В этом случае на входе 23 задания режима устройства присутствует единичный сигнал, а на входах 24, 25 задания15 режима устройства присутствуют нулевые сигналы элементов. При этом на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18 и НЕ 16, а следовательно, и на выходе элемента ИЛИ 12 присутствуют еди 20 ничные сигналы. Если число А отрицательное, а число В положительное или отрицательное, то на выходе элемента И 3 присутствует единичный сигнал, а на выходе элемента И 4 - ну 25 левой сигнал, вследствие чего на выходе элемента ЗАПРЕТ 15, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший оазояп параллельного сумматора 1 поступает дополнительная еди-ница, Если числа А и В положительные или число А положительное, а число В отрицательное, то в младший разряд сумматора 1 дополнительная единица не поступает, При этом на 35 выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом 00 в парал лельном сумматоре 2.В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В 45 в дополнительном модифицированном коде.Пусть число А представлено в дополнительном модифицированном коде, число В - в обратном модифицирован ном коде, а результат суммирования С представлен в дополнительном модифицированном коде. В этом случае на входе 24 задания режима устройства присутствует единичный сигнал, 55 а на входах 23 и 25 задания режима устройства присутствуют нулевые сигналы. При этом на выходе элемен та ИСКЛЮЧАК 61 ЕЕ ИЛИ 18, выходах элементов НЕ 16 и ИЛИ 12 присутствуют единичные сигналы. Если число В отрицательное, а число А положительное или отрицательное, то на выходе элемента И 4 присутствует единичный сигнал, а на выходе элемента И 3 - нулевой сигнал, вследствие чего на выходе элемента ЗАПРЕТ 14, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший разряд параллельного сумматора 1 поступает дополнительная единица. Если числа (сумматора 1) А и В положительные или число А положительное, а число В отрицательное, то в младший разряд сумматора 1 дополнительная единица не поступает. При этом на выходе параллельного сумматора будет резуль" тат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом 00 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированномкоде.Если число А представлено.в обратном модифицированном коде, а число В - в дополнительном модифицированном коде или число А представлено в дополнительном модифицированном коде, а число В - в обратном модифицированном кодр и результат суммирования должен быть представлен в обратном модифицированном коде, то процессы формирования результата суммирования чисел А и В в дополнительном модифицированном коде на выходе параллельного сумматора 1 аналогичны описанному. Если на выходе параллельного сумматора 1 есть положительный результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, то числовая этого результата сумми- . руется с числом 00 в параллельном сумматоре 2. Если на выходе паралельного сумматора 1 есть отрицательный результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, то на выходе элемента И 9 присутствует единичный сигнал, так как на выходе элемента НЕ 17, выходе зна 1264164а параллельнога сумматора 1 и входе 25 задания режима устройства естьединичные сигналы, При этом числовая часть результата, полученного навыходе параллельного сумматора 1,5суммируется с числом 11 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммиравания чисел А и В в обратном модифицированном коде.Пусть числа А и В представленыв обратных модифицированных кодах,а результат суммирования С должен 15быть представлен в дополнительноммодифицированном коде, В этом случае на входах 23 и 24 задания режима устройства присутствуют единичные сигналы, а на входе 25 задания 02режима устройства - нулевой сигнал.При этом на выходах элементов И 7,НЕ 16, а также и на выходе элемента ИЛИ 12 присутствуют единичные25сигналы, а на выходе элемента НЕ 17,а следовательно, и элемента И 9 - нулевой сигнал.Если числа А и В положительные,то на выходах элементов ИЛИ 10 и 13присутствуют нулевые сигналы. При30этом на выходе параллельного сумматора 1 будет результат суммированиячисел А и В, числовая часть которого суммируется с число 00 впараллельном сумматоре 2. В итоге на 35выходе параллельного сумматора 2 изнаковом выходе параллельного сумматора 1 будет результат С суммирования чисел в дополнительном модифицированном коде,Если числа А и В отрицательные, та только на выходе элемента И 6, а следовательно, и на выходах элементов ИЛИ 10 и 13 присутствуют еди ничные сигналы, В, этом случае в младшие разряды параллельных сумматоров 1 и 2 поступают дополнительные единицы. При этом числовая часть результата, полученного на выходе 50 параллельного сумматора 1, суммируется с числом 001 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 55также будет результат С суммирования чисел в дополнительном модифицированном коде. Если число А отрицательное, а число В положительное, то на выходах элементов И 3 и И 4 присутствуют единичный и нулевой сигналы, вследствие чего на выходе элемента ЗАПРЕТ 15, а следовательно, и на выходе элемента ИЛИ 1 О присутствуют единичные сигналы и в младший разряд параллельного сумматора 1 поступает дополнительная единица. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом 00 в параллельном сумматоре. 2. В итоге на выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде.Если число А положительнае,а число В отрицательное, то на выходах элементов И 3 и И 4 присутствуют нулевой и единичный сигналы, вследствие чего на выходе элемента ЗАПРЕТ 14, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший разряд параллельного сумматора 1 поступает дополнительная единица. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модиФицированном коде, числовая часть которого суммируется с числом 0,.0 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде.Пусть числа А и В представлены в обратных модифицированных кодах, а результат суммирования С представлен также в обратном модифицированном коде. В этом случае на входах 23, 24, 25 задания режима устройства присутствуют единичные сигналы. При этом на выходах элементов ИСКЛЮЧАКЩЕЕ ИЛИ 18, И 8, НЕ 16, И 6, ИЛИ 12, НЕ 17, И 9 присутствуют нулевые сигналы.Если числа А и В положительные, то на выходах элементов ИЛИ 1 О и 13 присутствуют нулевые сигналы. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В, числовая часть ко 126416420 торого суммируется с числом 00 впараллельном сумматоре 2, В итоге навыходе параллельного сумматора 2 изнаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном модифицированном коде,Если числа А и В отрицательные,то на выходе 28 переноса параллельного сумматора 1 присутствует единичный сигнал, вследствие чего навыходе элемента И 5, а следовательно, и на выходе элемента ИЛИ 13 присутствуют единичные сигналы и вмладший разряд параллельного сумматора 2 поступает дополнительная единица. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, суммируется с числом 001 в параллельномсумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковомвыходе параллельного сумматора 1будет результат С суммирования чисел А и В в обратном модифицированном коде.Если число А отрицательное, ачисло В положительное или число Аположительное, а число В отрицательное и на выходе переноса 28 параллельного сумматора 1 присутствует единичный сигнал, то на выходахэлементов И 5, ИЛИ 13 присутствуютединичные сигналы и в младший разряд параллельного сумматора 2 поступает дополнительная единица. При. этом числовая часть результата, полученного .на выходе параллельногосумматора 1, суммируется с числомО01 в параллельном сумматоре 240В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В вобратном модифицированном коде. 45Если число А отрицательное, ачисло В положительное или число Аположительное, а число В отрицательное и на выходе 28 переноса параллельного сумматора 1 присутствует 50нулевой сигнал, то на выходах элементов И 5, ИЛИ 13 присутствуют нулевые сигналы. При этом числоваячасть результата, полученная на выходе параллельного сумматора 1, суммируется с числом 00 в параллель"ном сумматоре 2. В итоге на выходепараллельного сумматора 1 будет результат С суммирования чисел А и Вв обратном модифицированном коде.фо рмул а иэ об ре те нияУстройство для суммирования двоичных чисел, содержащее первый параллельный сумматор, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй элементы ЗАПРЕТ, причем входы знаковых разрядов первого и второго операндов устройства соединены с соответствующими входами знаковых разрядов первого параллельного сумматора, информационные входы первого и второго операндов устройства соединены соответственно с первой и второй группами входов первого параллельного сумматора, вход переноса младшего разряда которого соединен с выходом первого элемента ИЛИ, первые входы первого и второго элементов И соединены соответственно с первым и вторым входами задания режима устройства, о т л и ч а ю щ ее с я тем, что, с целью расширения области применения за счет обеспечения возможности суммирования чисел в обратных кодах и представления результата как в дополнительном так и в обратном кодах, в устройство введены четвертый, пятый, шестой, седьмой элементы И, третий и четвертый элементы ИЛИ, элемент ИСКЛЮЧАКЩЕЕ ИЛИ, первый и второй элементы НЕ, второй параллельный сумматор, причем входы знаковых разрядов первого и второго операндов соединены со вторыми входами соответственно первого и второго элементов И, соответственно первым и вторым входами второго элемента ИЛИ, первым и вторым входами третьего элемента И, выход которого соединен с первыми входами первого и третьего элементов ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом переноса первого параллельного сумматора, выходы разрядов суммы которого соединены с информационными входами первой группы второго параю- лельного сумматора, первый вход пятого элемента И соединен с выходом знакового разряда первого параллельного сумматора и с выходом зна 9 12641 кового разряда реэультата устройства, третий вход задания режима устройства соединен со входом первого элемента НЕ, с первым входом шестого элемента И, со вторым входами четвертого и пятого элементов И, третий вход пятого элемента И соединен с выходом второго элемента НЕ, вход которого соединен с выходом седьмого элемента И, третьими входами третьего и четвертого элементов И, четвертый вход третьего элемента И соединен с,выходом первого элемента НЕ и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого объединены соответственно 2 О с первым и вторым входами седьмого элемента И и с первыми входами соответственно первого и второго элементов И, третьи входы которых соединены .и подключены к выходу четвер того элемента ИЛИ, выход первого элемента И соединен с информационб 4 Оным входом первого элемента ЗАПРЕТ и с управляющим входом второго элемента ЗАПРЕТ, выход которого соединен со вторым входом первого элемента ИЛИ, выход второго элемента И соединен с информационным входом второго элемента ЗАПРЕТ и с управляющим входом первого элемента ЗАПРЕТ, выход которого соединен с третьим входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с четвертым входом четвертого элемента И, второй вход младшего раз ряда второго параллельного сумматора соединен с выходом третьего элемента ИДИ, информационные входы разрядов второй группы со второго по Ф-й второго параллельного сумматора объединены и подключены к выходу пятого элемента И и к третьему входу третьего элемента ИЛИ, а вход переноса младшего разряда второго параллельного сумматора соединен с входом нулевого потенциала устройства, выходы разрядов второго параллельного сумматора являются информационными выходами результата устройства.1264164 Вац од лцраллельноао сулгмалюра У ставитель М. Есенинахред М.Ходанич Корректор Е, Сирохман тор Т. Митей Заказ 5562/48 ктная,4 ужгород, ул графическ едприяти Производственно Тирак 671 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж, Раушская наб., д. 4/

СмотретьЗаявка

3862640, 04.03.1985

ТЕРНОПОЛЬСКИЙ ФИНАНСОВО-ЭКОНОМИЧЕСКИЙ ИНСТИТУТ

ДОМБРОВСКИЙ ЗБЫШЕК ИВАНОВИЧ, ДУДА МИХАИЛ АЛЕКСЕЕВИЧ, УЗЛОВА ЛЮДМИЛА АНАТОЛЬЕВНА

МПК / Метки

МПК: G06F 7/50

Метки: двоичных, суммирования, чисел

Опубликовано: 15.10.1986

Код ссылки

<a href="https://patents.su/7-1264164-ustrojjstvo-dlya-summirovaniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования двоичных чисел</a>

Предыдущий патент: Сумматор по модулю три

Следующий патент: Накапливающий сумматор

Случайный патент: Вывод энергии приборов свч