Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

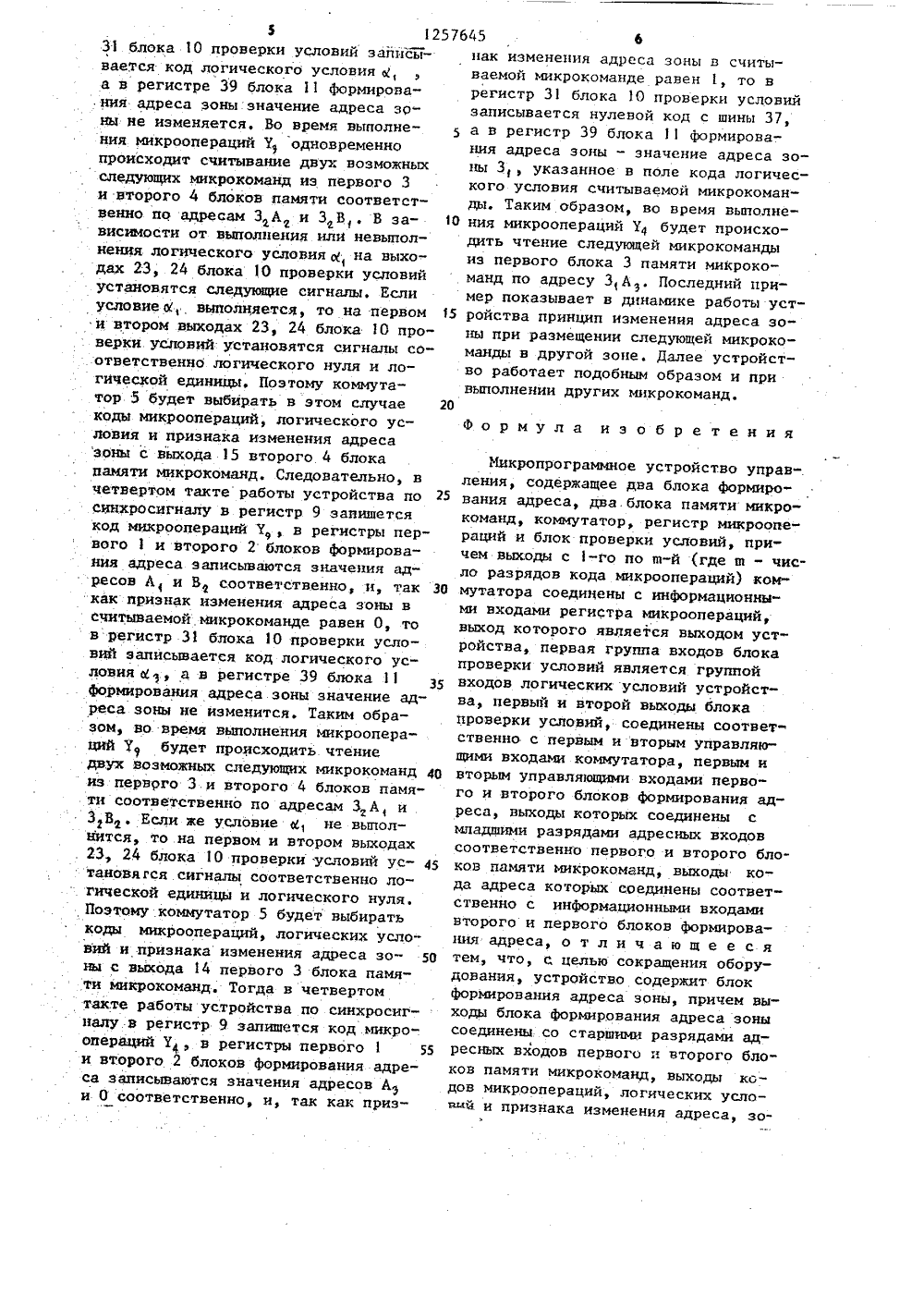

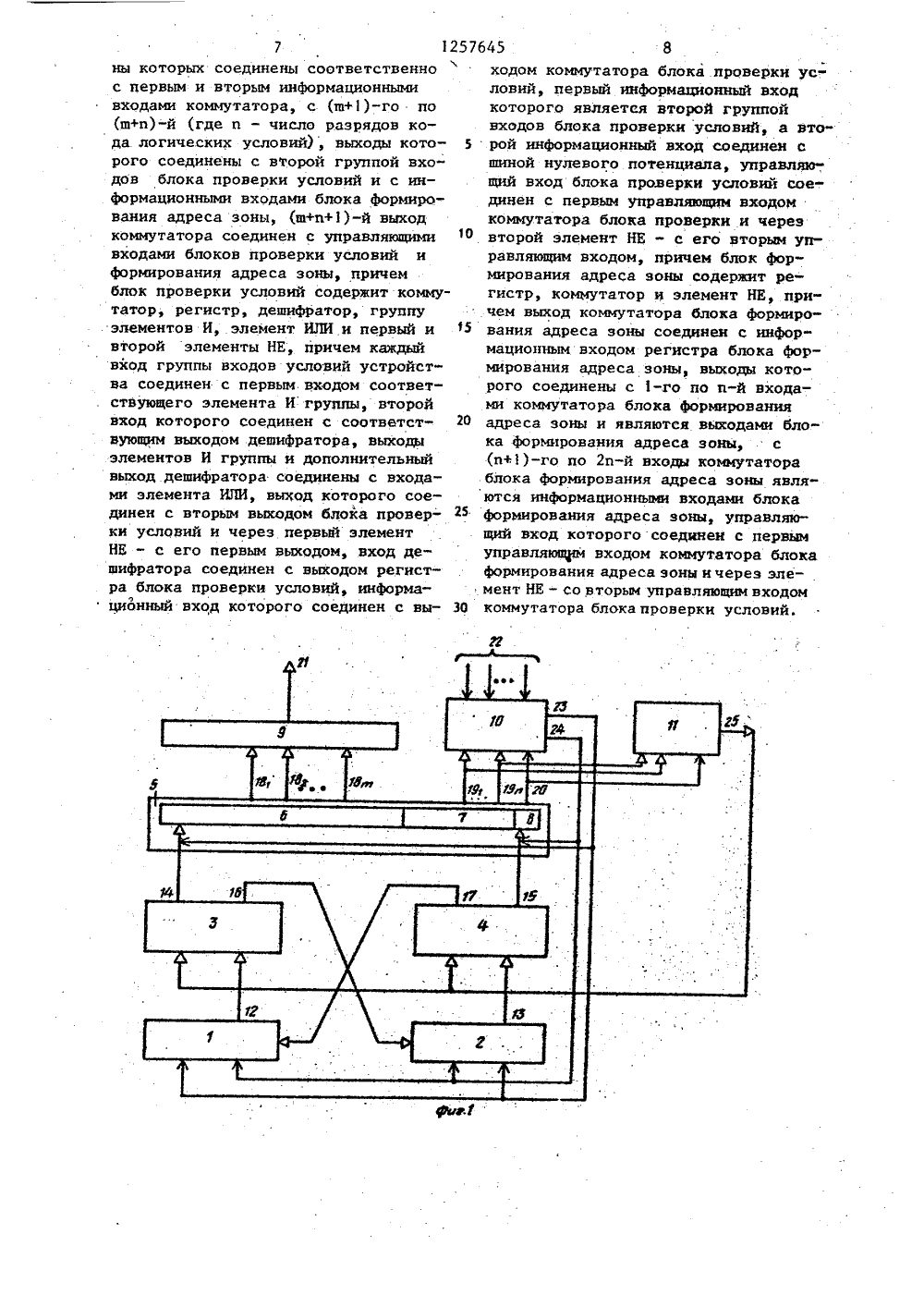

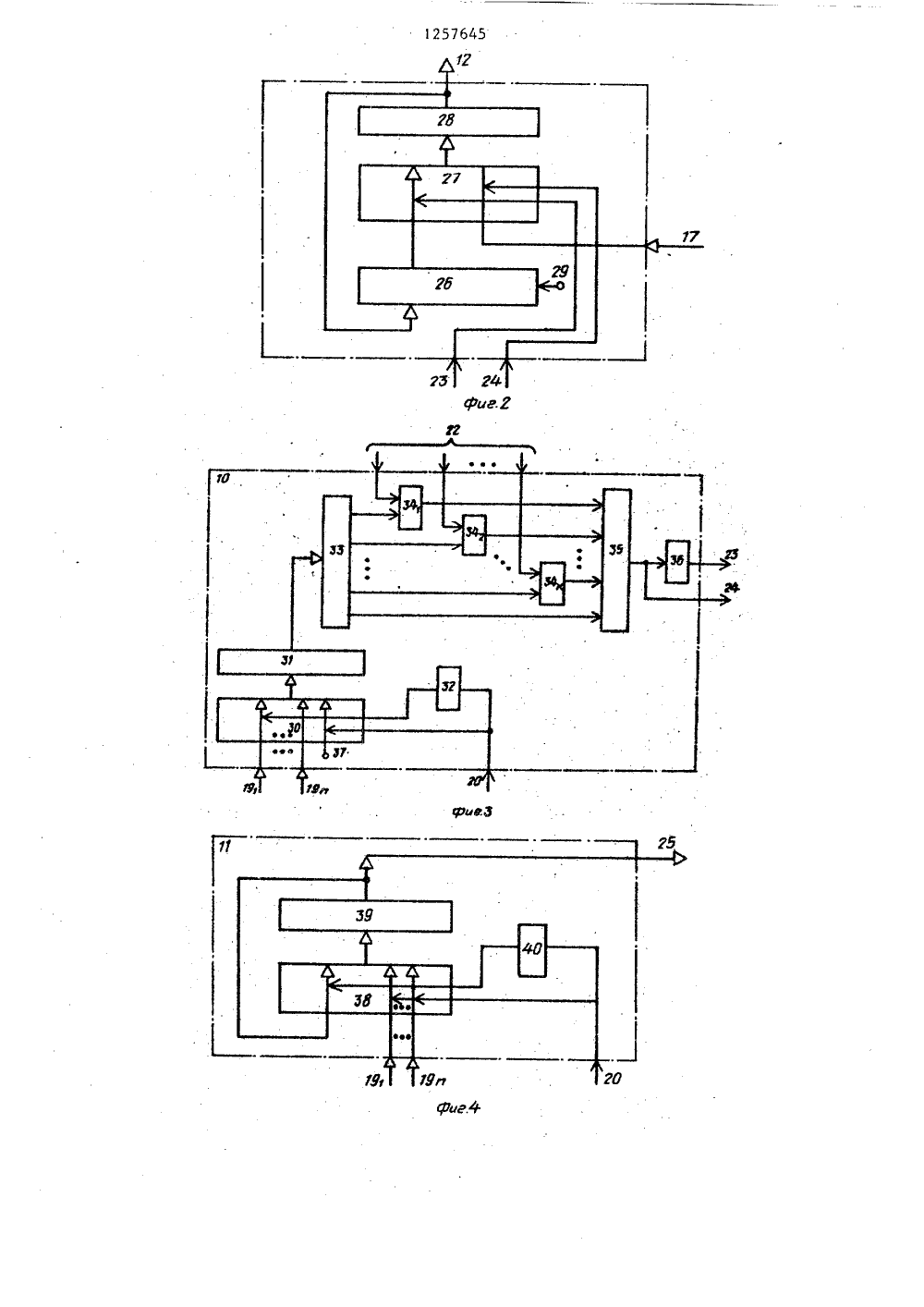

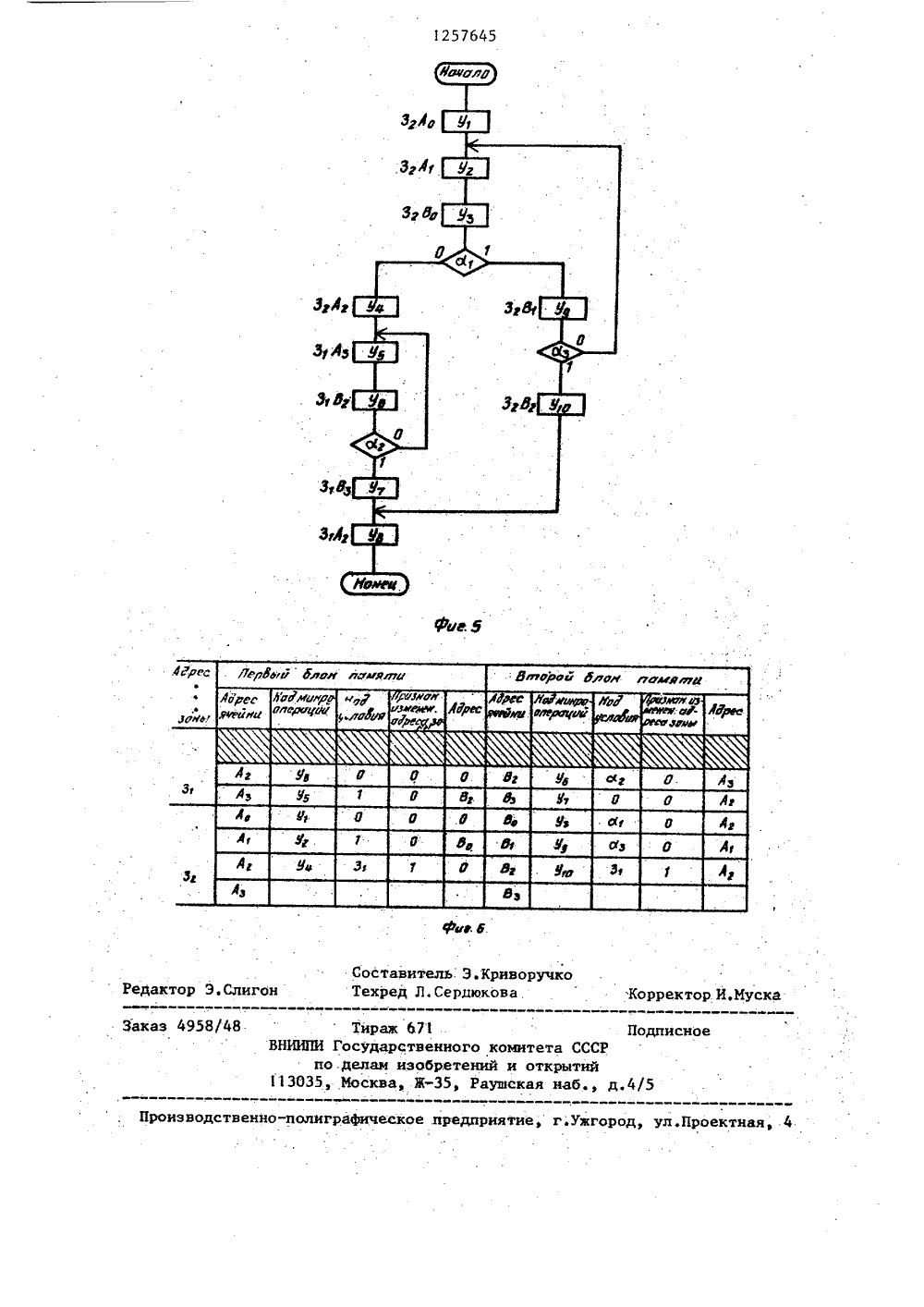

(191 б 94 С 06 Г 9 ОПИСАНИЕ ИЗОБРЕТЕН ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРГЮ ЛЕЛАМ ИЭОБРЕТЕНИй И ОТНРЩТЮ Н АТОРСОМУ СВИДЕТШСТ(56) 1. Путков,В.Н., Обросов И,И., Бекетов С.В, Электронные вычислительнме устройства. Минск,: Вьааейная школа 1981, с.225, рис.9,14.2. Авторское свидетельство СССР . Э 964640, кл.О 06 Р 922, 1981.Э. Авторское свидетельство СССР . Э 115.1962, 1983.(57) Изобретение относится к вычислительной технике и может быть использовано при построении управляющих автоматов. Целью изобретения является сокращение количества используемого оборудования. Устройство содеркит два блока формирования адреса, два блока памяти микрокоманд,коммутатор, регистр микрооперацнй,блок проверки условий и блок 4 юрми-.рования адреса зоны, Цель достигнутаэа счет введения блока формированияадреса зоны 6 илф 12Изобретение относится к вычислительной технике и может быть исполь-зовано при построении управляющих автоматов,Целью изобретения является сокраЩение оборудования.На Фиг. 1 приведена структурнаясхема микропрограммного устройства.,Управления; на Фиг. 2,3,4 изображеныФункциональные схемы соответственноблока формирования адреса, блока про"верки условий и блока Формированияадреса зоны; на Фиг.5, 6 показанысоответственно граф-схема микропрограимй и принцип ее размещения в блоках.памяти устройства.Микропрограммное устройство управления (Фиг.1) содержит первый 1 ивторой 2 блоки формирования адреса,первый 3 и второй 4 блоки памяти микрокоманд, коммутатор 5, состоящий изполя 6 кода микроопераций, поля 7логического условия и поля 8 признака изменения адреса зоны, регистр 9ищкроопераций, блок 10 проверки условий и блок 11 Формирования адресазоны. Выходы 12,13 первого 1 и второго 2 блоков формирования адреса соединены с младшими разрядами адресныхвходов соответственно первого 3 ивторого 4 блоков памяти микрокоманд,Выходы 14,15 кодов микроопераций,логических условий и признака изменения. адреса зоны первого 3 и второго 4 блоов памяти микрокоманд соединены соответственно с первыми ивторым информационными входами коммутатора 5,. Высоды 16,17 кода адреса первого 3 и второго 4 блоковсоединены соответственно с информационными входами второго 2 и перво го 1 блоков формирования адреса.Выходы 18 - 18, кода микрооперацийкоммутатора 5 соединены с информациоцнымн входасщ регистра 9 микроопераций Выходы 19-19, кода логического условия коммутатора 5 соединеиы с второй группой входов блока1 О проверки условий и с информационными входами блока 11 Формированияадреса зовы, а выход 20 признака изменения адреса зоны цоьмутатора 5соединен с управляющими входами блоов 10, 11 проверки условий и Форми. рования адреса зоны соответственно.Выход 21 регистра 9 микроопераций.является выходом устройства. Группавходов 22 логических условий уст 576455 0 5 20 25 30 35404550 ройства является первой группой входов блока 10 проверки условий, выходы 23, 24 являются первым и вторым выходами блока 1 О проверки условий. Выход 25 является выходом блока 11 формирования адреса зоны.На Фиг. 2 представлена одна из возможных реализаций первогоблока формирования адреса (второй 2 блок Формирования адреса по построению полностью идентичен). Он содержит комбинационный сумматор 26, коммутатор 27 и регистр 28. На входереноса сумматора 26 заведен с шины 29 сигнал логической единицы.На фиг.З представлена функциональная схема одной из возможньпс реализаций блока 10 проверки условий.Блок 10 содержит коммутатор 30, регистр 31, второй элемент НЕ 32, де. - шифратор ЗЗ, группу из К элементов И 34 (К - число логических условий), элемент ИЛИ 35 и первый элемент НЕ Зб. Второй информационный вход коммутатора 30 соединен с шиной 37 нулевого потенциала.На фиг.4 представлена функциональ" ная схема одной из возможных реализаций блока 11 формирования адреса зоны. Он содержит коммутатор 38, регистр 39 и элемент НЕ 40.Работу устройства рассмотрим на примере выполнения микропрограммы, блок-схема которой изображена на фиг.5, Размещение рассматриваемой микропрограммы в блоках 3,4 памяти устройства показано на фиг.б. На рисунках адреса ячеек памяти, в которых размещены микрокоманды, иэображаются в виде старших и младшихразрядов. Старшие разряды обозначаются через Зк(с к с 2), и в дальнейшем будут называться адресами эон, а младшие разряды обозначаются ецуз А , и В(0 ш 43, 0- л й 3)соответственно для первого 3 и второго 4 блоков памяти микрокоманд и в дальнейшем будут называться адресами внутри зоны для соответствующегоблока памяти. Здесь предполагается,что отличие значений 3от ЗкА, от А, и В от Всоставляет единицу, Через У -Т, обозначены коды микроопераций, а черезк, - ккоды логических условий соответствующих микрокомаид. При размещении микрокоманд в блоках памяти устройст" ва предполагалось, что эоны этих55 блоков состоят из четырех ячеек ичто предыдущая размещенная микропрограмма заняла две ячейки из зоны 3,первого 3 и второго 4 блоков памяти.В устройстве адрес следующей микрокоманды Формируется двумя способами. При Формировании адреса первым спосо-. бом предполагается, что следующаямикрокоманда будет находиться в тойже зоне, что и предыдущая. Поэтомуадрес зоны следующей микрокомандыне изменяется, Адрес же внутри зоныможет формироваться или путем увеличения на единицу адреса внутри зоны щая микрокоманда размещается в соседнем блоке памяти, что и предыдущая, или определяется полем када адреса предыдущей микрокоманды, еслиследующая микрокоманда размещаетсяв соседнем блоке памяти. При формировании адреса вторым способом предполагается, что следующая микрокоманда находится в какой-то другой зоне. Тогда адрес этой зоны указывается в поле кода логического условия предыдущей микрокоманды, а адрес внутри зоны формируется таким же образом, как и при нервом способе,ПУстройство работает следующим образом.В исходном состоянии регистр 9 микроопераций и регистр 31 блока О проверки условий обнуляется, в регистр 39 блока 11 формирования адреса зоны записывается адрес зоны З, в которой находится первая микрокоманда выполняемой микропрограммы, а в регистр первого 1 блока формирования адреса записывается ее адрес А внутри зоны Зг. (Цепи синхронизации,обнуления и занесения начальных адресов в соответствующие регистры устройства на рисунках с целью упрощения не показаны). Таким образом, из первого 3 блока памяти считывается микрокоманда по адресу ЗгА . Так как ются сигналы соответственно логичес" кой единицы и логического нуля. Поэтому коммутатор 5 будет выбирать коды микроопераций, логического условия и признака изменения адреса зо-. ны с выхода 14 первого 3 блока памя 1 ти микрокоманд. Следовательно, впервом такте работы устройства по синх-25 30 35 40 росигналу в регистр 9 запишется кодиикроопераций У 1, в регистры первого 1 и второго 2 блоковформированияадреса записываются соответственнозначения адресов А . и О,так как признакизменения адреса зоны в считываемоймикрокоманде равен О,то в регистр 3блока 10 проверки условий записывается нулевой код логического условия(на фиг. 6 обозначен как "0"), а врегистре 39 блока 11 формированияадреса зоны значение адреса зоны неизменяется. Во время выполнения микроопераций У, происходит чтениеследующей микрокоманды по адресуЗгА, из первого 3 блока памяти. Таккак в регистре 31 блока 10 проверкиусловий остается нулевой код, тозначения сигналов на выходах 23, 24этого блока не изменятся, Поэтомуво втором такте работы устройствапо синхросигналу в регистр 9 запишется код микроопераций У , в регистры первого 1 и второго 2 блоков формирования адреса записываются значения адресов А г и В соответственно,и так как знак изменения адреса зоны в считываемой микрокоманде равентакже О, то в регистр 31 блока 10проверки условий записывается единичный код логического условия считываемой микрокоманды (на фиг.6 обозначен как "1"), а в регистре 39 блока 11 формирования адреса зоны значение адреса зоны не изменится. Вовремя выполнения микроопераций Упроисходит чтение информации по адресам зглг и Згво соответственно иэпервого 3. и второго 4 блоков памяти. Но, так как в регистре 31 блока1 О проверки условий находится единичный код, то на выходах 23, 24этого блока устанавливаются сигналысоответственно логического нуля и логической единицы. Поэтому коммутатор5 будет выбирать коды микроопераций,логического условия и признака изменения адреса зоны с выхода 15 второго 4 блока памяти микрокоманд, Следовательно, в третьем такте работыустройства.по синхросигналу в регистр 9 запишется код микрооперацийУ, в регистры первого 1 и второго 2блоков Формирования адреса записываются соответственно значения адресов Аг и В, и, так как признак изменения адреса зоны в считываемоймикрокоманде равен О, то в регистр5 1257 б 31 блока 1 О проверки условий зайисывается код логического условия Ы, а в регистре 39 блока 11 Формирования адреса зоны значение адреса зоны не изменяется. Во время выполнения микроопераций У одновременно происходит считывание двух возможных следующих микрокоманд из первого 3 и второго 4 блоков памяти соответственно по адресам 3 А и 3 В, В за- О висимости от выполнейия или невыполнения логического условия с на выходах 23, 24 блока 10 проверки условий установятся следующие сигналы. Если условие М, выполняется, то на первом 15 и втором выходах 23, 24 блока О проверки условий установятся сигналы со. ответственно логического нуля и логической единицы. Поэтому коммутатор 5 будет выбирать в этом случае 20 коды микроопераций, логического условия и признака изменения адреса зоны с выхода 15 второго 4 блока памяти микрокоманд. Следовательно, в четвертом такте работы устройства по 25 сннхросигналу в регистр 9 запишется код микроопераций У , в регистры первого 1 и второго 2 блоков Формирования адреса записываются значения адресов А и В соответственно, и, так ЭО как признак изменения адреса зоны в считываемой микрокоманде равен О, то и Регистр 31 блока 10 проверки условий записываетая код логического условия сз, а в регистре 39 блока 11 Фюрмирования адреса зоны значение адреса зоны не изменится. Таким образом, во время выполнения микроопераций У будет происходить чтение двух возможных следующих микрокоманд ,1 О из перврго 3 и второго 4 блоков памяти соответственно но адресам ЗА, и 33. Если же условие , не выполнйтся, то на первом и втором выходах . 23, 24 блока 1 О проверки условий ус тановягся.сигналы соответственно логической единицы и логического нуля. Поэтому коммутатор 5 будет выбирать коды микроопераций, логических условий и признака изменения адреса зо ны с выхода 14 первого 3 блока памяти микрокоманд. Тогда в четвертом такте работы устройства по синхросигналу в регистр 9 запишется код микро- операций 71, в регистры первого 1 55 и второго 2 блоков Формирования адреса записываются значения адресов А 5 и О соответственно, и, так как приз 45 6нак изменения адреса зоны в считываемой микрокоманде равен 1, то врегистр 31 блока 10 проверки условийзаписывается нулевой код с шины 37,а в регистр 39 блока 1 Формирования адреса зоны - значение адреса зоны 3, указанное в поле кода логического условия считываемой микрокоманды. Таким образом, во время выполнения микроопераций У будет происходить чтение следующей микрокомандыиз первого блока 3 памяти микрокоманд по адресу 3 А. Последний пример показывает в динамике работы устройства принцип изменения адреса зоны при размещении следующей микрокоманды в другой зоне. Далее устройство работает подобным образом и привыполнении других микрокоманд. Формула изобретения Микропрограммное устройство управ-. ления, содержащее два блока формирования адреса, два блока памяти микро- команд, коммутатор, регистр микроопераций и блок проверки условий, причем выходы с 1-го по ш-й (где ш - число разрядов кода микроопераций) коммутатора соедицены с информационнымн входами регистра микроопераций, выход которого является выходом устройства, первая группа входов блока проверки условий является группой входов логических условий устройства, первый и второй выходы блока проверки условий, соединены соответственно с первым и вторым управляющими входами коммутатора, первым и вторым управляющими входами первого и второго блоков формирования адреса, выходы которых соединены с младшими разрядами адресных входов соответственно первого и второго блоков памяти мнкрокоманд, выходы кода адреса которых соединены соответственно с информационными входами второго и первого блоков формирования адреса, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, устройство содержит блок формирования адреса зоны, причем выходы блока Формирования адреса зоны соединены. со старшими разрядами адресных входов первого и второго блоков памяти микрокоманд, выходы кодов микроопераций, логических условый и признака изменения адреса, зо12 ны которых соединены соответственно с первым и вторым информационными входами коммутатора, с (ш+1)-го по (ш+и)-й (где п - число разрядов кода.логических условий), выходы которого соединены с второй группой входов блока проверки условий и с информационными входами блока Формирования адреса зоны, (а+и+1)-й выход коммутатора соединен с управляющими входами блоков проверки условий и формирования адреса зоны, причем блок проверки условий содержит коммутатор, регистр, дешифратор, группу элементов И, элемент ИЛИ и первый и второй элементы НЕ, причем каждый вход группы входов условий устройства соединен с первым входом соответствующего элемента И группы, второй вход которого соединен с соответствующим выходом дешифратора, выходы элементов И группы и дополнительный выход дешифратора соединены с входами элемента ИЛИ, выход которого соединен с вторым выходом блока провер- ки условий и через первый элемент НЕ - с его первым выходом, вход дешифратора соединен с выходом регистра блока проверки условий, информа ционный вход которого соединен с вы 57645 8ходам коммутатора блока .проверки условий, первый инфориационньй входкоторого являетея второй группойвходов блока проверки условий, а вто" Ь рой информационный вход соединен сшиной нулевого потенциала, управляю-,щий вход блока проверки условий соединен с первым управляющим входомкоммутатора блока проверки и черезвторой элемент НЕ - с его вторым управляющим входом, причем блок Формирования адреса зоны содержит регистр, коммутатор и элемент НЕ, причем выход коммутатора блока Формиро вания адреса зоны соединен с информационным входом регистра блока формирования адреса зоны, выходы которого соединены с 1-го но и-й входами коммутатора блока формирования 20 адреса зоны и являются вйходами блока Формирования адреса зоны, с(и+1)-го по 2 п-й входы коммутатораблока Формирования адреса зоны являются информационными входами блока 2 формирования адреса зоны, управляющий вход которого соединен с первымуправляющим входом коммутатора блокаформирования адреса эоны и через элемент НЕ - со вторым управляющим входом ЗО коммутатора блокапроверки условий.1257645 и оставитель Э.Криворучкоехред Л,Сердюкова ек тор И.Муска Редакто он 4 исно 4 ра 4 жческое .предприятие, г.ужгород,оектная роизводственн тир ж аП ВНИИПИ Государственного по . делам изобретении 113035, Москва, Ж, Рамитета СС открытии кая иаб.

СмотретьЗаявка

3840823, 07.01.1985

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

СОЛОВЕЙ АЛЕКСАНДР ВЛАДИМИРОВИЧ, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.09.1986

Код ссылки

<a href="https://patents.su/7-1257645-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для управления многоканальной измерительной системой

Следующий патент: Многоканальное устройство для подключения абонентов к общей магистрали

Случайный патент: Бесконтактный индуктивный переключатель