Линейно-круговой интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

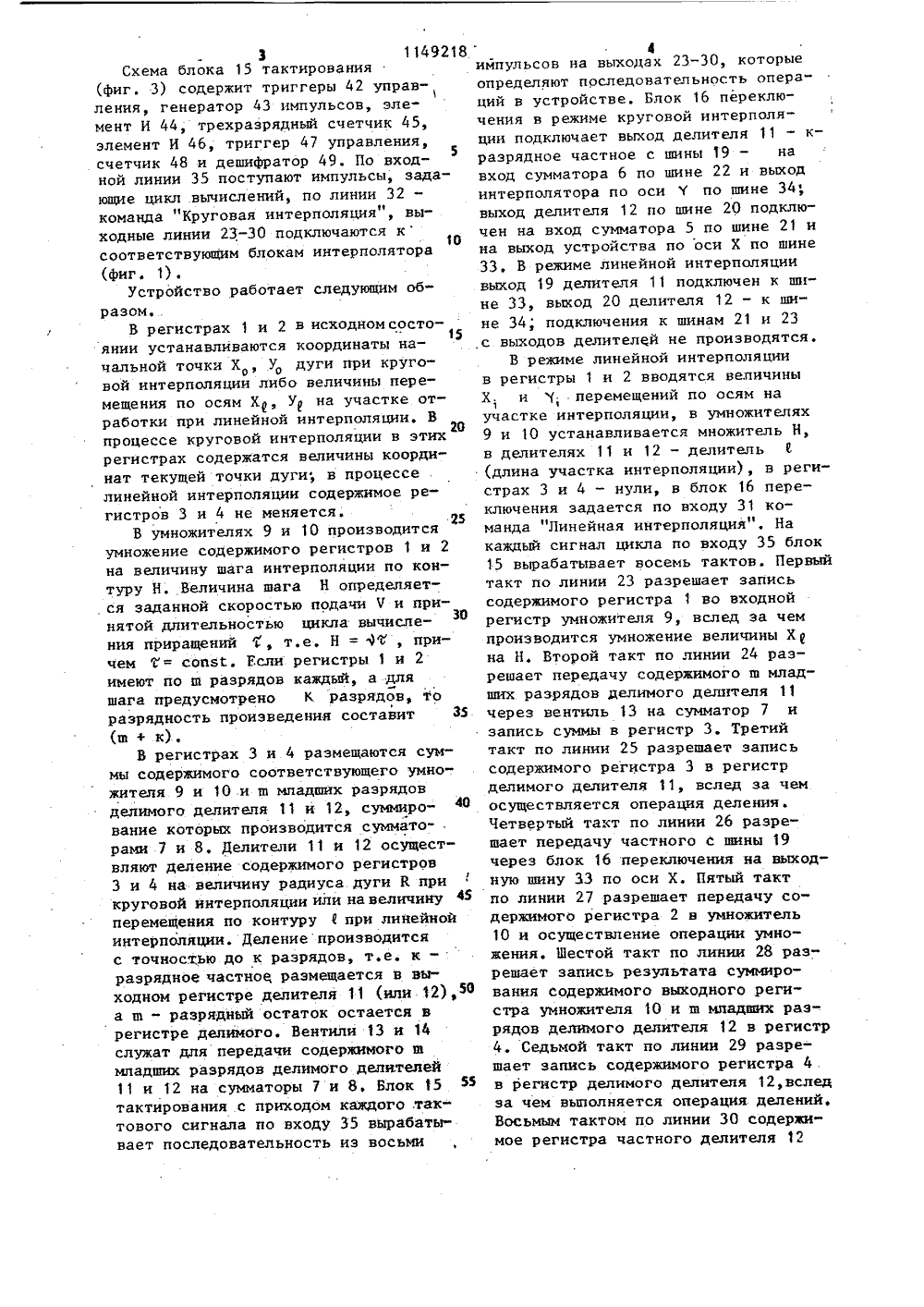

.(ц С 05 В 19/1 ТЕ САН ИЗОБ АВТОРСНО 9 13 Ю.А, Раисо Сухер на Ленина пот им. В.И,Ленина детельство СССР19/18, 1974,тельство СССР19/18, 1977 триг такт ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(71) Харьковский орделитехнический институ(прототип),(54)(57) 1. ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР, содержащий в каждом координатном канале последовательно соединенные первый регистр и делитель.,подключенный первым выходом к первому входу группы вентилей, о т л ич а ю щ и й с я тем, что, с цельюповышения точности отработки заданной скорости перемещений и точностиинтерполяции по контуру дуги, онсодержит блок тактирования, блокпереключения и в каждом координатном канале последовательно соединенные первый сумматор, второй регистр,умножитель и второй сумматор, выход которого соединен с первым входомпервого регистра, а второй вход - свыходом группы вентилей, второй вход которои соединен с вторым входом первого регистра и с первым выходом блока тактирования, второй выход которого подключен к второму входу умножителя, третий выход - к второму входу делителя, а четвертый выход - к первому входу второго регистра друтого канала и к первому входу блока переключения, соединенного выходом с первым входом первого сумматора, второй вход которого подключен к выходу второго регистра, блок переключения соединен вторым входом с вторым выходом делителя, третий вход которого подключен к входу устройства.2. Интерполятор по п. 1, о т л и ч а ю щ и й с,я тем, что блок такти- фЛ рования содержит генератор импульсов, выходом соединенный с первым С входом первого элемента И, второй вход которого через первый триггер соединен с выходом первого счетчика, а также последовательно соединенные второй элемент И, второй триггер,ев 4второй счетчик и дешифратор, выходы . которого соединены свыходами блока файф ;тактирования, выход первого элементаИ соединен с входом первого счетчика и входом второго счетчика входы фф /У второго элемента И и 8-вход первого 00 гера подключены к входам блока ирования.11492Изобретение относится. к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками,Известны линейно-круговые интер 5 поляторы с многоразрядными приращениями, построенные на основе цифровых дифференциальных анализаторов (ЦДЛ) 1.Недостатками данных устройств являются большая разрядность вычислений, 10 необходимая для получения достаточной точности, и, как следствие, высокая сложность.Наиболее близким к изобретению по технической сущности являетсялинейно-, круговой интерполятор, содержащий общий делитель и в каждом координатном канале последовательно соединенные первый вентиль, регистр, делитель и второй вентиль, причем первый выход делителя соединен с входом регистра этого же канала, второй выход делителя - с входом первого вентиля другого канала, выход общего делителя - с первыми входами вторыхвеити 25 лей, выходы которых соответственно подключены к входам делителей координатных каналов 2.Недостатком известного устройства является низкая точность отработки30 заданной скорости перемещений (ошибка в скорости может достигать 50/), Кроме того, устройству свойственна, хотя и уменьшена по сравнению с другими интерполяторами, вычислительная погрешность.35Целью изобретения является повышение точности отработки заданной скорости перемещений и точности интерполяции по контуру дуГиПоставленная цель достигается тем, ,что линейно-круговой интерполятор, содержащий в каждом координатном канале последовательно соединенные первый регистр и делитель, подключенный первым выходом к первому вхо 45 ду группы вентилей, содержит блок тактирования, блок переключения и в каждом координатном канале последовательно соединенные первый сумматор, второй регистр, умножитель и второй сумматор, выход которого соединен с ,первым входом первого регистра, а второй вход - с выходом группы вентилей, второй вход которой соединен с вторым входом первого регистра и с 55 первым выходом блока тактирования, второй выход которого подключен к второму входу умножителя, третий 18 1выход - к второму входу делителя, ачетвертый выход - к первому входу второго регистра другого канала и кпервому входу блока переключения,соединенного выходом с первым входом,первого сумматора, второй вход кото-,рого подключен к выходу второго регистра, блок переключения соединейвторым входом с вторым выходом делителя, третий вход которого подключен к входу устройства.Кроме того, блок тактированиясодержит генератор импульсов, выходом соединенный с первым входомпервого элемента И, второй вход которого через первый триггер управления соединен с выходом первогосчетчика, а также последовательносоединенные второй элемент И, второй триггер управления, второй счетчик и дешифратор, выходы которого соединены с выходами блока тактирования, выход первого элемента И соединен с входом первого счетчика и входом второго счетчика, входы второгоэлемента И и Я-вход первого триггераподключены к входам блока тактирования,На фиг. 1 приведена структурнаясхема предлагаемого интерполятора;на фиг. 2 - схема выполнения блокапереключения на фиг, 3 - схема блока активирования. Интерполятор содержит вторые 1 и 2 и первые 3 и 4 регистры, первые 5 и 6 и вторые 7 и 8 сумматоры, умно- жители 9 и 10, делители 11 и 12, вентили 13 и 14, блок 15 тактирования, блок 16 переключения, первые 17 и 18 и вторые 19 и 20 выходы (шины) делителей 11 и 12 соответственно,:выходы (шины) 21 и 22 блока 16.переключения, выходы (линии) 23-30 блока 15 тактирования, входы (линии) 31 и 32 блока 16 переключения, выходные шины (линии) 33 и 34 блока 16, вход (линия) 35 блока 15 тактирования.Схема блока 16 переключения (фиг.2) содержит четыре группы вентилей 36-39 и две группы элементов ИЛИ 40 и 41. Связи, показанные на схеме, обеспечивают требуемое для правильной работы интерполятора подключение шин 19 и 20 (выходы блоков делителей 11 и 12) на выходные шины 33 и 34 и в режиме круговой интерполяции на шины 21 и 22 для передачи в сумматоры 5 и 6 соответственно(фиг. 3) содержит триггеры 42 управления, генератор 43 импульсов, элемент И 44, трехразрядный счетчик 45,элемент И 46, триггер 47 управления,счетчик 48 и дешифратор 49, По входной линии 35 поступают импульсы, задающие цикл вычислений, по линии 32команда "Круговая интерполяция , выходные линии 23-30 подключаются ксоответствующим блокам интерполятора(фиг. 1),Устройство работает следующим образом.В регистрах 1 и 2 в исходномсосто 15янин устанавливаются координаты начальной точки Х , Ур дуги при кругоовой интерполяции либо величины перемещения по осям Х, У на участке отработки при линейной интерполяции. Впроцессе круговой интерполяции в этихрегистрах содержатся величины координат текущей точки дуги; в процесселинейной интерполяции содержимое регистров 3 и 4 не меняется.35В умножителях 9 н 10 производитсяумножение содержимого регистров 1 и 2на величину шага интерполяции по контуру Н. Величина шага Н определяется заданной скоростью подачи Ч и приЗОнятой длительностью цикла вычисления приращений , т,е, Н = 1 Ф , причем= сопзс. Если регистры 1 и 2имеют по ш разрядов каждый, а дляшага предусмотрено К разрядов, торазрядность произведения составит З 5(в + к),В регистрах 3 и 4 размещаются суммы содержимого соответствующего умно-.жителя 9 и 10 .и в младших разрядовделимого делителя 1 1 и 12, суммиро Ованне которых производится суммато- .рами 7 н 8. Делители 11 и 12 осуществляют деление содержимого регистров3 и 4 на величину радиуса дуги К прикруговой интерполяции или на величину 45перемещения по контуру 1 при линейнойинтерполяции, Деление производитсяс точностью до к разрядов, т.е. кразрядное частноЕ размещается в выходном регистре делителя 11 (или 12),5 Оа в - разрядный остаток остается врегистре делимого, Вентили 13 и 14служат для передачи содержимого вмладших разрядов делимого делителей11 и 12 на сумматоры 7 и 8. Блок 15тактирования .с приходом каждого .тактового сигнала по входу 35 вырабатывает последовательность из восьми 4импульсов на выходах 23.-30, которые определяют последовательность опера" ций в устройстве. Блок 16 переключения в режиме круговой интерполяции подключает выход делителя 11 - кразрядное частное с шины 19 - на вход сумматора 6 по шине 22 и выход интерполятора по оси У по шине 34, выход делителя 12 по шине 20 подключен на вход сумматора 5 по шине 21 и на выход устройства по оси Х по шине 33. В режиме линейной интерполяции выход 19 делителя 11 подключен к шине 33, выход 20 делителя 12 - к шине 34; подключения к шинам 21 и 23 с выходов делителЕй не производятся,В режиме линейной интерполяции в регистры 1 и 2 вводятся величины Х. и 1 перемещений по осям на1участке интерполяции, в умножителях 9 и 10 устанавливается множитель Н, в делителях 11 и 12 - делитель (длина участка интерполяции), в регистрах 3 и 4 - нули, в блок 16 переключения задается по входу 31 команда "Линейная интерполяция", На каждый сигнал цикла по входу 35 блок 15 вырабатывает восемь тактовПервый такт по линии 23 разрешает запись содержимого регистра 1 во входной регистр умножителя 9, вслед за чем производится умножение величины Хо на Н, Второй такт по линии 24 разрешает передачу содержимого в младших разрядов делимого делителя 11 через вентиль 13 на сумматор 7 и запись суммы в регистр 3. Третий такт по линии 25 разрешает запись содержимого регистра 3 в регистр делимого делителя 11, вслед за чем осуществляется операция деления .Четвертый такт по линии 26 разрешает передачу частного с шины 19 через блок 16 переключения на выходную шину 33 по оси Х. Пятый такт по линии 27 разрешает передачу содержимого регистра 2 в умножитель 10 и осуществление операции умножения. Шестой такт по линии 28 разрешает запись результата суммирования содержимого выходного регистра умножителя 10 и в младших разрядов делимого делителя 12 в регистр 4. Седьмой такт по линии 29 разрешает запись содержимого регистра 4 в регистр делимого делителя 12,вслед за чем выполняется операция делений.Восьмым тактом по линии 30 содержимое регистра частного делителя 12149218 811 и 12 - по (ш + к) разрядов, регистры частного делителей - по к разрядов, сумматоры 5 и 6 при параллельном суммировании - по (к + 1) раз.Рядов, сумматоры 7 и 8 - по (ш + 1)разрядов. Типичные значения в=20-24,к=7-10. Тогда максимальная раэрядность регистров не превысит 34, Прииспользовании интегрирования с дробными числами, что обычно делается вЦДА, вычисления ведутся с точностью10 ф, что соответствует максимальной разрядности чисел 44-48 при практически такой же функциональной сложности устройства.Высокая точность вычислений приращений ЬХ и аУобеспечивает высокую точность отработки заданной скорости перемещений, так как в устройстве составляющие скорости по осямИ ь- ЧХ у- и 25 7 1В режиме круговой интерполяции по линии 32 открывается элемент И 46, через который проходят на триггер 47 импульсы цикла. Если начальная установка триггера 47 "0", то с приходом каждого нечетного импульса цикла счетчик 48 сбрасывается в нуль и порядок прохождения сигналов на выходах дешифратора 49 остается таким же, как в режиме линейной интерполяции. С приходом каждого четного импульса цикла выходной сигнал триггера 47 устанавливает третий разряд счетчика 48 в "1" (состояние счетчика 100), что определяет последовательность прохождения сигналов на выходах дешифратора в порядке 27-28- 29-30-23-24-25-2 б при прохождении восьми импульсов генератора 43,Благодаря чередованию циклов методическая ошибка интерполяции носит периодический характер с амплиту. дой УЕ= Н /2 К. При линейной интерполяций методическая ошибка не превосходит одной дискретности,В предлагаемом устройстве все вычисления ведутся с целыми числами, округлений нет и вычислительные погрешности не появляются. Кроме того, уменьшается разрядность блоков. Так, если регистры 3 и 4 имеют по ш разрядов, а множитель Н - к-разрядов, то регисгры умножителей 9 и 10 должны иметь по (ш + к) разрядов, регистры произведения умножителей 9 и 10 и регистры делимого делителей и скорость подачи по контуру Ч Ч +Ч = - ДХ+ЬУ2. 1 Й 2х г1 а величина Н=4, участвующая в вычислениях приращений, задается точно, 30По сравнению с известным предлагаемое устройство позволяет повысить скорость вычерчивания на координатографе при контроле геометрии деталей до 40 маймин (т.е. в 20 раэ) и скорость записи программ на магнитную 35 ленту до 800 мм/с (т.е. в 16 раэ)

СмотретьЗаявка

3525052, 20.12.1982

ХАРЬКОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. ЛЕНИНА

ПРОСТАКОВ ОЛЕГ ГЕОРГИЕВИЧ, РАИСОВ ЮРИЙ АБРАМОВИЧ, СЕРЕДКИН АЛЕКСАНДР ГЕОРГИЕВИЧ, СУХЕР АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G05B 19/4103

Метки: интерполятор, линейно-круговой

Опубликовано: 07.04.1985

Код ссылки

<a href="https://patents.su/7-1149218-linejjno-krugovojj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Линейно-круговой интерполятор</a>

Предыдущий патент: Устройство для управления исполнительным органом

Следующий патент: Устройство для контроля программ на координатографе

Случайный патент: Способ получения водоразбавляемого пленкообразующего